### Magnetoelastic NanoMagnet Logic Circuits

BY

DAVIDE GIRI B.S., Politecnico di Torino, Turin, Italy, 2012

### THESIS

Submitted as partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2015

Chicago, Illinois

Defense Committee:

Wenjing Rao, Chair and Advisor Zhichun Zhu Mariagrazia Graziano, Politecnico di Torino

This thesis is dedicated to my family and to my beloved grandparents.

### ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisors Prof. Graziano and Prof. Zamboni, for their guidance throughout this work. Without their constant support it would have been impossible for me to accomplish my research goals. My deepest gratitude goes also to my advisor at UIC, Prof. Wenjing Rao, who gave me the possibility to undertake this research work. I take this opportunity to express my gratitude to Dr. Marco Vacca and Giovanni Causapruno for their assistance and dedication. A special thanks goes to my mates at VLSI Laboratory. Eventually, I want to thank from the bottom of my heart my family and my friends for the unwavering support they always gave me during this experience in the United States.

$\mathbf{DG}$

# TABLE OF CONTENTS

## **CHAPTER**

| 1        | INTRO   | DUCTION                             |

|----------|---------|-------------------------------------|

|          | 1.1     | CMOS scaling                        |

|          | 1.2     | Quantum-Dot Cellular Automata (QCA) |

|          | 1.3     | Magnetic QCA                        |

| <b>2</b> | NML B.  | ACKGROUND                           |

|          | 2.1     | QCA basics                          |

|          | 2.1.1   | Logic Gates                         |

|          | 2.1.2   | Signal propagation and Clock        |

|          | 2.2     | Nano-Magnets Logic (NML) 14         |

|          | 2.2.1   | Logic Gates                         |

|          | 2.2.2   | Magnetic Clock NML                  |

|          | 2.2.2.1 | Snake Clock Layout                  |

|          | 2.2.2.2 | Working frequency                   |

|          | 2.2.3   | Magnetoelastic Clock NML (ME-NML)   |

|          | 2.2.3.1 | Circuit Layout                      |

|          | 2.2.4   | Intrinsic Pipeline                  |

|          | 2.2.4.1 | Interleaving                        |

| 3        | VHDL    | MODEL FOR THE MAGNETOELASTIC NML 33 |

| -        | 3.1     | Standard Cell Library               |

|          | 3.2     | VHDL of the Standard Cells   38     |

|          | 3.2.1   | Generic parameters                  |

|          | 3.2.2   | Register plus logic function   40   |

|          | 3.2.3   | Area and Energy                     |

|          | 3.2.3.1 | Area information                    |

|          | 3.2.3.2 | Energy information                  |

|          | 3.2.4   | Hierarchical model                  |

|          | 3.3     | Circuit layout                      |

|          | 0.0     |                                     |

| 4        | CASE S  | TUDY I: GALOIS FIELD MULTIPLIER     |

|          | 4.1     | Galois Fields arithmetic            |

|          | 4.1.1   | Galois Field Multiplier scheme      |

|          | 4.2     | CMOS Pipelined Implementation       |

|          | 4.2.1   | Timing analysis                     |

|          | 4.2.2   | Circuit simulation                  |

|          | 4.3     | ME-NML Implementation               |

# TABLE OF CONTENTS (Continued)

## **CHAPTER**

|   | 4.3.1                                         | Circuit design                                 |  |  |  |  |  |  |

|---|-----------------------------------------------|------------------------------------------------|--|--|--|--|--|--|

|   | 4.3.1.1                                       | Basic blocks                                   |  |  |  |  |  |  |

|   | 4.3.1.2                                       | 4-bit GFM                                      |  |  |  |  |  |  |

|   | 4.3.1.3                                       | 4-bit GFM with synchronization circuitry       |  |  |  |  |  |  |

|   | 4.3.2                                         | VHDL description and circuit simulation        |  |  |  |  |  |  |

|   | 4.4                                           | Magnetic Clock NML Implementation              |  |  |  |  |  |  |

|   | 4.4.1                                         | Galois Multiplier scheme                       |  |  |  |  |  |  |

|   | 4.4.2                                         | Timing analysis                                |  |  |  |  |  |  |

| 5 | CASE STUDY I: GFM RESULTS COMPARISON          |                                                |  |  |  |  |  |  |

|   | 5.1                                           | CMOS Results                                   |  |  |  |  |  |  |

|   | 5.1.1                                         | Occupied area                                  |  |  |  |  |  |  |

|   | 5.1.2                                         | Power consumption                              |  |  |  |  |  |  |

|   | 5.2                                           | Magnetoelastic NML Results                     |  |  |  |  |  |  |

|   | 5.2.1                                         | Upper synchronization network                  |  |  |  |  |  |  |

|   | 5.2.2                                         | Lower synchronization network                  |  |  |  |  |  |  |

|   | 5.2.3                                         | Occupied area                                  |  |  |  |  |  |  |

|   | 5.2.4                                         | Power consumption                              |  |  |  |  |  |  |

|   | 5.3                                           | Magnetic Clock NML Results                     |  |  |  |  |  |  |

|   | 5.3.1                                         | Number of clock zones and magnets              |  |  |  |  |  |  |

|   | 5.3.2                                         | Occupied area                                  |  |  |  |  |  |  |

|   | 5.3.3                                         | Power consumption                              |  |  |  |  |  |  |

|   | 5.4                                           | Results Comparison                             |  |  |  |  |  |  |

| 6 | CASES                                         | CASE STUDY II: MULTIPLY ACCUMULATE UNIT (MAC). |  |  |  |  |  |  |

| U | 6.1                                           | Parallel Implementation                        |  |  |  |  |  |  |

|   | 6.1.1                                         | Array Multiplier and Ripple Carry Adder        |  |  |  |  |  |  |

|   | 6.1.2                                         | Full Adder and Half Adder                      |  |  |  |  |  |  |

|   | 6.1.2<br>6.1.3                                | Basic blocks                                   |  |  |  |  |  |  |

|   | 6.1.3                                         | VHDL description and circuit simulation        |  |  |  |  |  |  |

|   | 6.1.4                                         | Timing Analysis                                |  |  |  |  |  |  |

|   | 6.2                                           | Serial-Parallel Implementation                 |  |  |  |  |  |  |

|   | $0.2 \\ 6.2.1$                                | Circuit scheme                                 |  |  |  |  |  |  |

|   | 6.2.1<br>6.2.2                                | ME-NML implementation                          |  |  |  |  |  |  |

|   | 6.2.2<br>6.2.3                                | Timing analysis                                |  |  |  |  |  |  |

|   | $\begin{array}{c} 0.2.3 \\ 6.3 \end{array}$   | Serial Implementation                          |  |  |  |  |  |  |

|   | $0.3 \\ 6.3.1$                                | Serial MAC scheme                              |  |  |  |  |  |  |

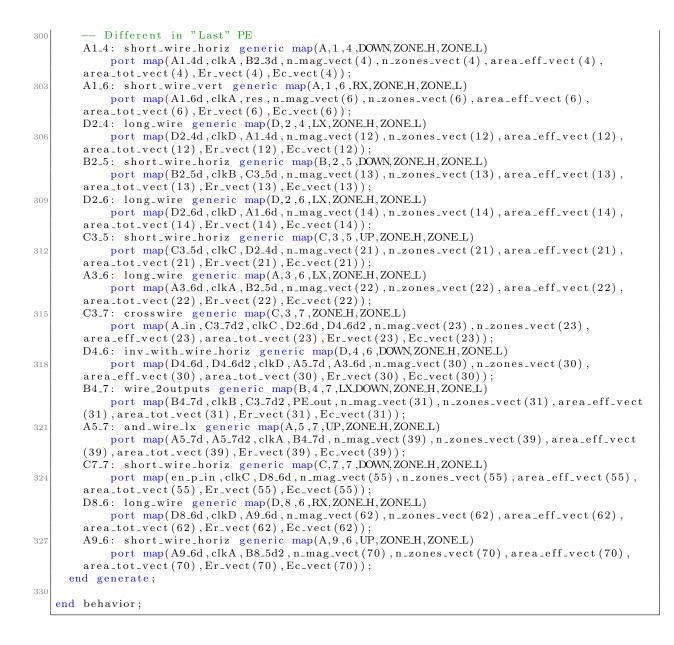

|   | 6.3.1                                         | Multiplier                                     |  |  |  |  |  |  |

|   | 6.3.1.1<br>6.3.1.2                            | Adder                                          |  |  |  |  |  |  |

|   | 6.3.1.2<br>6.3.1.3                            | Adder                                          |  |  |  |  |  |  |

|   | 0.3.1.3<br>6.3.2                              | Serial MAC with shared Accumulator             |  |  |  |  |  |  |

|   | $\begin{array}{c} 0.3.2 \\ 6.3.3 \end{array}$ |                                                |  |  |  |  |  |  |

|   | 0.3.3                                         | ME-NML implementation                          |  |  |  |  |  |  |

# TABLE OF CONTENTS (Continued)

## **CHAPTER**

|   | 6.3.4   | Timing analysis                         | 130 |

|---|---------|-----------------------------------------|-----|

| 7 | CASE ST | TUDY II: MAC RESULT COMPARISON          | 131 |

|   | 7.1     | Parallel MAC Results                    | 131 |

|   | 7.2     | Serial-Parallel MAC Results             | 133 |

|   | 7.3     | Serial MAC Results                      | 134 |

|   | 7.4     | Results Comparison                      | 136 |

|   | 7.4.1   | Comparison conditions                   | 137 |

|   | 7.4.1.1 | Interleaving                            | 137 |

|   | 7.4.1.2 | Equal throughput                        | 137 |

|   | 7.4.2   | Results exploiting interleaving         | 138 |

|   | 7.4.3   | Results without exploiting interleaving | 141 |

|   | 7.4.4   | Final considerations                    | 142 |

| 8 | CONCLU  | USIONS                                  | 144 |

|   | 8.1     | Future work                             | 146 |

|   | APPENI  | DIX                                     | 148 |

|   | CITED I | LITERATURE                              | 205 |

|   | VITA    |                                         | 210 |

## LIST OF TABLES

| TABLE |                                                                                                                    | PAGE    |

|-------|--------------------------------------------------------------------------------------------------------------------|---------|

| Ι     | ADDITION AND MULTIPLICATION FOR GF(2)                                                                              | 52      |

| II    | POLYNOMIAL MAPPING AND MULTIPLICATION TABLE FOR GF(8). PRIMITIVE: $X^3 + X + 1$ .                                  | ₹<br>53 |

| III   | TIMING PERFORMANCE OF THE CMOS GFM                                                                                 | 60      |

| IV    | POLYNOMIAL MAPPING FOR GF(16). PRIMITIVE: $X^4 + X + 1$                                                            | . 62    |

| V     | MULTIPLICATION TABLE FOR GF(16). PRIMITIVE: $X^4 + X + 1$                                                          | 63      |

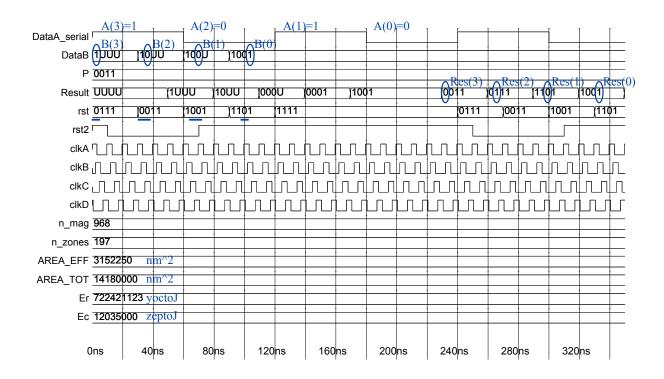

| VI    | TIMING PERFORMANCE OF THE ME-NML GFM                                                                               | 72      |

| VII   | TIMING PERFORMANCE OF THE MAGNETIC NML GFM .                                                                       | 77      |

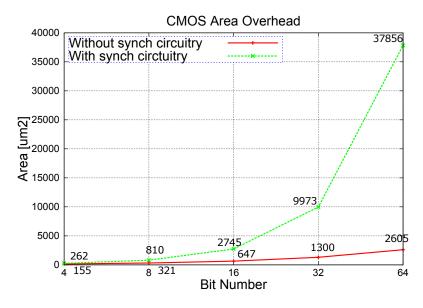

| VIII  | AREA OCCUPATION OF CMOS GFM BOTH WITH AND WITH-<br>OUT SYNCHRONIZATION CIRCUITRY.                                  | 80      |

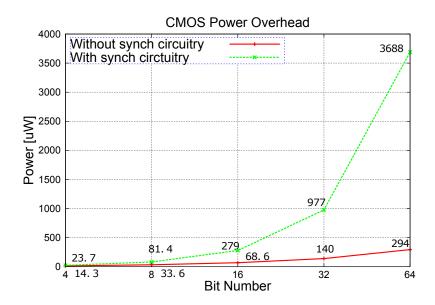

| IX    | POWER CONSUMPTION OF THE CMOS GFM BOTH WITH<br>AND WITHOUT SYNCHRONIZATION CIRCUITRY                               | 81      |

| Х     | NUMBER OF CELLS AND MAGNETS OF THE BASIC BLOCKS<br>FOR THE UPPER INTERCONNECTIONS                                  | 84      |

| XI    | NUMBER OF MAGNETS AND CELLS OF ME-NML GFM BOTH WITH AND WITHOUT SYNCHRONIZATION CIRCUITRY                          | 86      |

| XII   | OCCUPIED AREA OF ME-NML GFM BOTH WITH AND WITH-<br>OUT SYNCHRONIZATION CIRCUITRY.                                  | 87      |

| XIII  | POWER CONSUMPTION OF ME-NML GFM BOTH WITH AND WITHOUT SYNCHRONIZATION CIRCUITRY                                    | 89      |

| XIV   | DIMENSIONS AND NUMBER OF MAGNETS OF THE MAG-<br>NETIC NML GFM BOTH WITH AND WITHOUT SYNCHRO-<br>NIZATION CIRCUITRY | 90      |

# LIST OF TABLES (Continued)

## TABLE

| XV    | AREA OF THE MAGNETIC NML GFM BOTH WITH AND WITHOUT SYNCHRONIZATION CIRCUITRY                                                                                 | 90  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| XVI   | POWER OF THE MAGNETIC NML GFM, BOTH WITH AND WITHOUT SYNCHRONIZATION CIRCUITRY                                                                               | 92  |

| XVII  | RATIO BETWEEN RESULTS FOR ME-NML AND THOSE FOR<br>CMOS AND MAGNETIC NML. THE THIRD TABLE SHOWS<br>THE INTERCONNECTION OVERHEAD TRENDS OF EACH<br>TECHNOLOGY. | 93  |

| XVIII | TIMING PERFORMANCE OF THE PARALLEL MAC                                                                                                                       | 112 |

| XIX   | TIMING PERFORMANCE OF THE SERIAL-PARALLEL MAC                                                                                                                | 121 |

| XX    | TIMING PERFORMANCE OF THE SERIAL MAC                                                                                                                         | 130 |

| XXI   | PARALLEL MAC PERFORMANCE RESULTS                                                                                                                             | 132 |

| XXII  | SERIAL-PARALLEL MAC PERFORMANCE RESULTS                                                                                                                      | 134 |

| XXIII | SERIAL MAC PERFORMANCE RESULTS                                                                                                                               | 135 |

| XXIV  | COMPARISON OF THE 3 MAC IMPLEMENTATIONS, WITH<br>THE THROUGHPUT BEING EQUAL.                                                                                 | 136 |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                                                                                                        | PAGE |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | Possible states of a QCA cell: Stable states '0' and '1' and unstable NULL state                                                                                                                                                                                                                                       | 3    |

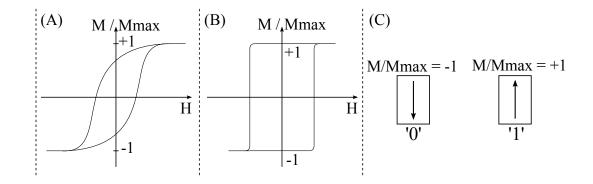

| 2      | A) Hysteresis cycle of a multidomain magnetic material. B) Hysteresis cycle of a single domain magnetic signal. C) The two stable states of the NML base cell.                                                                                                                                                         | 6    |

| 3      | Signal propagation through a 3 cells QCA wire. II) The first cell is forced to '1'. III) The second cell switches to '1' due to electrostatic interaction. IV) The third cell switches.                                                                                                                                | 8    |

| 4      | Logic gates of QCA. A) Wire. B) Crosswire. C) Inverter. D) Major-<br>ity Gate                                                                                                                                                                                                                                          | 9    |

| 5      | Clock mechanism. A) Clock zones. B) Clock signals                                                                                                                                                                                                                                                                      | 12   |

| 6      | Simplest clock phases layout, the circuit's area is partitioned in ver-<br>tical stripes                                                                                                                                                                                                                               | 13   |

| 7      | A) Horizontal wire. B) Inverter. C) Vertical wire. D) Majority<br>Voter. E) AND port. F) OR port. G) Crosswire                                                                                                                                                                                                         | 16   |

| 8      | NML with Magnetic Clock mechanism. The magnetic field $H$ is generated by the current $I$ flowing through the copper wire, which is placed under the magnets plane.                                                                                                                                                    | 18   |

| 9      | The clock phase sequence is RESET, SWITCH, HOLD. A) Func-<br>tioning in space (horizontally) and time (vertically) of a horizontal<br>NML wire. B) The 3 clock signals. They are applied to different<br>zones in space and they are repeated over time. They are the same<br>in magnitude but with a 120 phase shift. | 19   |

| 10     | Snake-clock. (A) Top 2-D layout. (B) 3-D layout. The nanomagnets are placed between the two planes. Magnets cannot be placed where wires 2 and 3 are twisted                                                                                                                                                           | 20   |

## **FIGURE**

| 11 | Example of a simple circuit based on the <i>Snake-Clock</i> system. Different background colours refer to different clock zones. The arrows show the signal flow direction.                                                                                                                                               | 21 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 12 | Magnetoelastic NML clocking mechanism. A) No voltage applied.<br>B) Voltage applied to the electrodes. The PZT substrate induces<br>a strain on the nanomagnets forcing their magnetization to their<br>intermediate state.                                                                                               | 24 |

| 13 | Clock zones of the ME-NML. A) Clock zone with AND logic function.<br>B) Clock zone with OR logic function. C) Circuit layout example.<br>D) Placement grid for ME-NML Cells                                                                                                                                               | 26 |

| 14 | NML signal synchronization. The three inputs must arrive to the two AND ports simultaneously. To do so the input wires must pass through the same number of clock zones. (A) Not working routing. (B) Correct routing                                                                                                     | 29 |

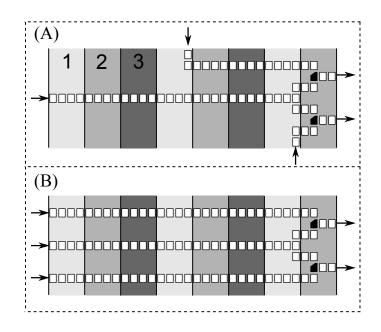

| 15 | Data interleaving. In this example 3 operations are executed in par-<br>allel: $A + B + C$ , $D + E + F$ , $G + H + I$ . At every clock cycle the<br>input data comes from a different operation. Since the feedback loop<br>is 3 registers long, data from the same operation are fed with 3 clock<br>cycles of delay.   | 30 |

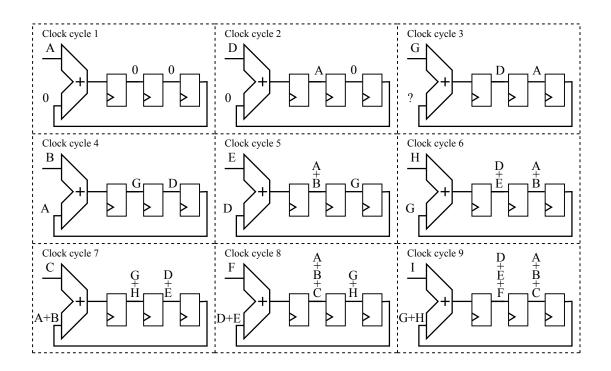

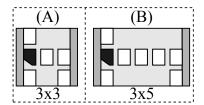

| 16 | ME-NML cells. A) $3 \times 3$ size. B) $3 \times 5$ size                                                                                                                                                                                                                                                                  | 34 |

| 17 | Full $3 \times 3$ Standard Cell Library for ME-NML                                                                                                                                                                                                                                                                        | 35 |

| 18 | Detailed measures of the ME-NML $3 \times 3$ cell                                                                                                                                                                                                                                                                         | 42 |

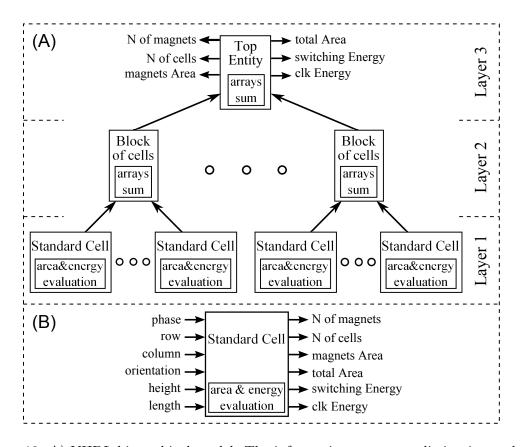

| 19 | A) VHDL hierarchical model. The information on energy dissipation<br>and area occupation are propagated hierarchically toward the top<br>entity. B) generic inputs and outputs of a Standard Cell                                                                                                                         | 47 |

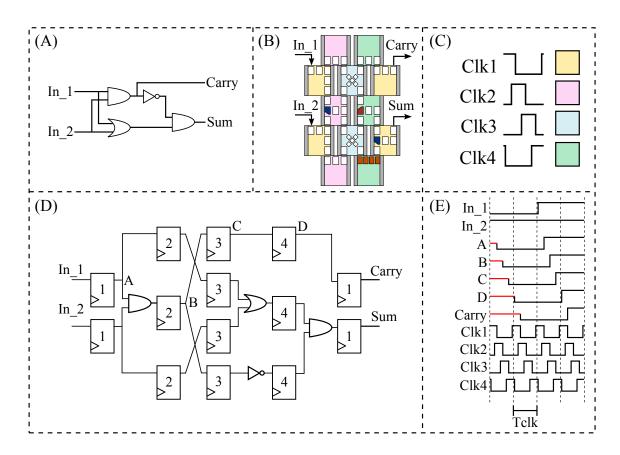

| 20 | A) CMOS Half Adder. B) ME-NML Half Adder. C) Waveforms for<br>the 4-phase overlapped clock system. A color is associated to each<br>clock signal. D) VHDL counterpart of the ME-NML circuit, it is<br>the circuit described by the VHDL model. E) Timing diagram of an<br>example of signal propagation through the adder | 49 |

| 21 | Scheme of a 4-bit bit-serial Galois Field Multiplier $(GF(2^4))$                                                                                                                                                                                                                                                          | 56 |

## **FIGURE**

| 22 | Scheme of the 4-bit fully pipelined Galois Field Multiplier                                                                                                                                      | 57 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

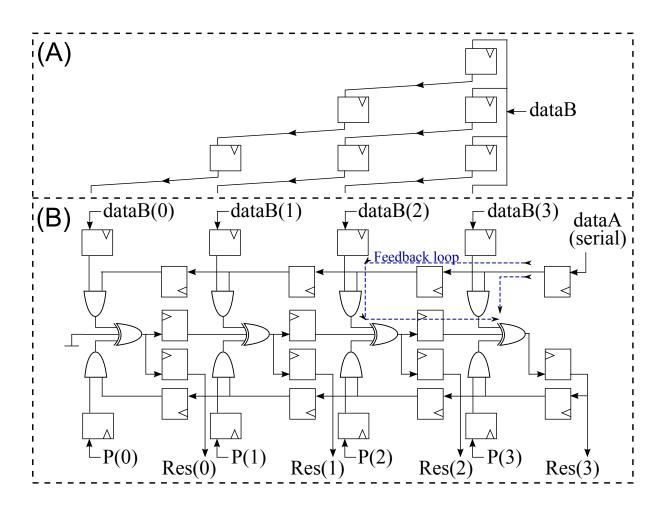

| 23 | CMOS implementation of the 4-bit fully pipelined GFM. (A) Preskew circuitry for <i>dataB</i> . (B) Circuit body.                                                                                 | 58 |

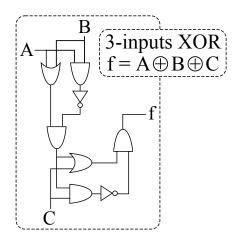

| 24 | 3-inputs XOR function constructed with AND, OR and Inverter gates.                                                                                                                               | 65 |

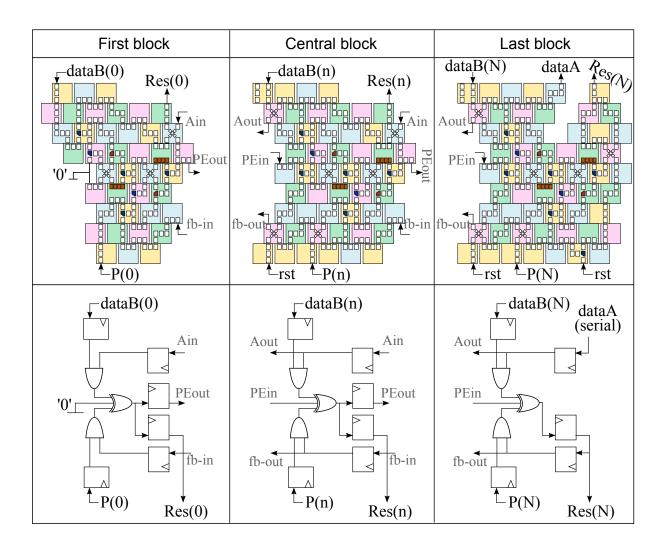

| 25 | Basic blocks of the GFM. ME-NML blocks on top are matched with the correspondent CMOS blocks.                                                                                                    | 66 |

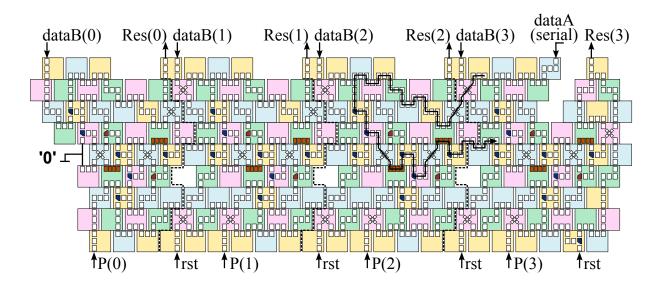

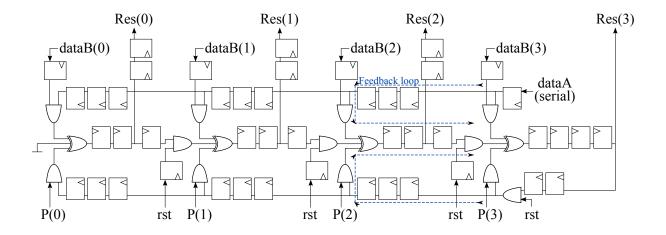

| 26 | Magnetoelastic NML implementation of a 4-bit Galois Multiplier                                                                                                                                   | 67 |

| 27 | Equivalent circuit for the ME-NML GFM.                                                                                                                                                           | 68 |

| 28 | ME-NML Galois Multiplier with additional preskew and deskew net-<br>works.                                                                                                                       | 69 |

| 29 | Timing diagram of the operation $9 \times 10$ with the ME-NML 4-bit Galois Multiplier.                                                                                                           | 73 |

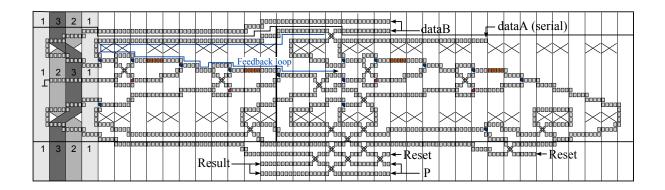

| 30 | The 2-bit Magnetic NML Galois Multiplier, comprehensive of preskew and deskew networks.                                                                                                          | 74 |

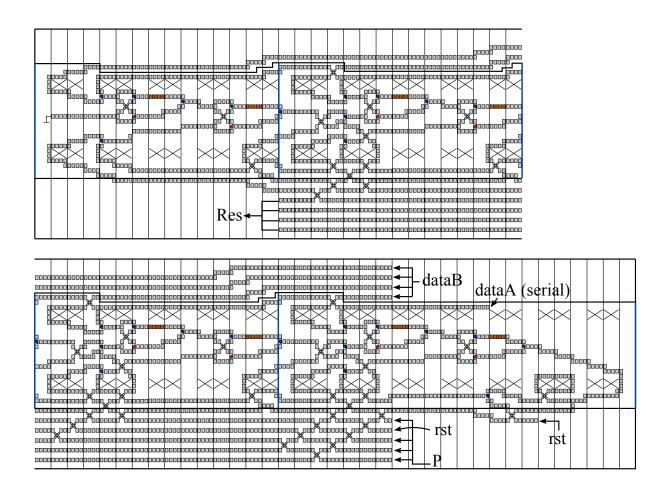

| 31 | The 4-bit Magnetic NML Galois Multiplier, comprehensive of preskew<br>and deskew networks. The circuit is split in left part (on top) and<br>right part (below), to facilitate its comprehension | 76 |

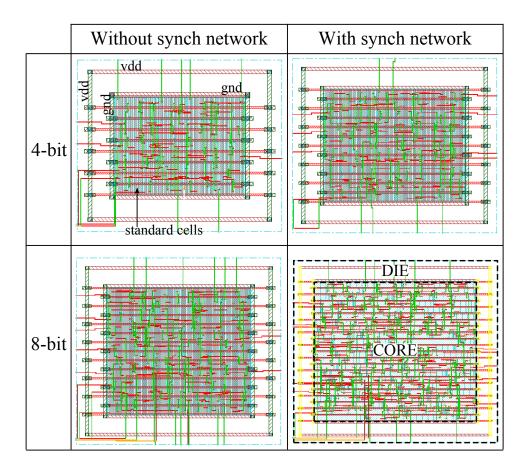

| 32 | Post-route layout of the GFM in its CMOS implementation                                                                                                                                          | 79 |

| 33 | Comparison of area occupation for the CMOS GFM both with and without synchronization circuitry.                                                                                                  | 80 |

| 34 | Comparison of power consumption for the CMOS GFM both with<br>and without synchronization circuitry.                                                                                             | 82 |

| 35 | Basic blocks for the upper interconnections                                                                                                                                                      | 83 |

| 36 | Layout of the upper interconnections for the 8-bit GFM. The second table is the optimized layout.                                                                                                | 84 |

| 37 | Basic blocks for the lower interconnections                                                                                                                                                      | 85 |

## **FIGURE**

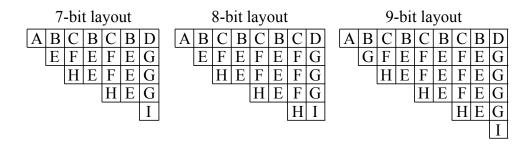

| 38 | Layout of the lower interconnections for the 7-bit, 8-bit and 9-bit GFM.                                                      | 86  |

|----|-------------------------------------------------------------------------------------------------------------------------------|-----|

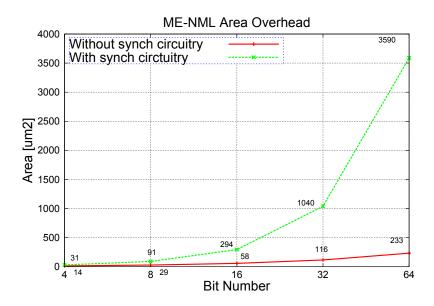

| 39 | Comparison of area occupation for the ME-NML GFM both with<br>and without synchronization circuitry.                          | 88  |

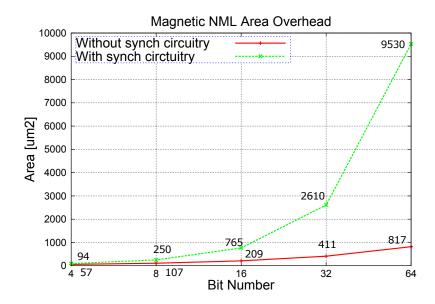

| 40 | Comparison of area occupation for the Magnetic NML GFM both with and without synchronization circuitry.                       | 91  |

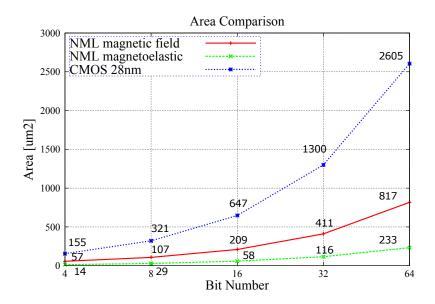

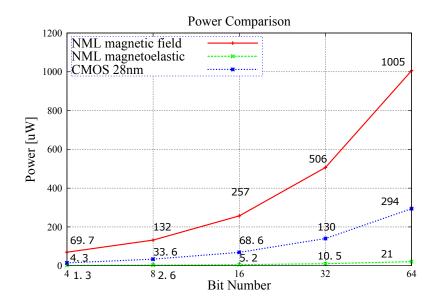

| 41 | Area comparison between the three GFM implementations without synchronization networks.                                       | 95  |

| 42 | Power comparison between the three GFM implementations without synchronization networks.                                      | 96  |

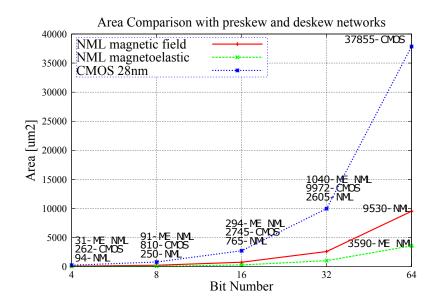

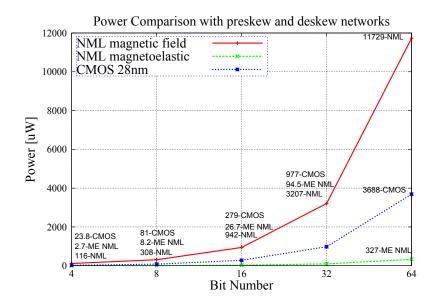

| 43 | Area comparison between the three GFM implementations with syn-<br>chronization networks.                                     | 97  |

| 44 | Power comparison between the three GFM implementations with synchronization networks.                                         | 98  |

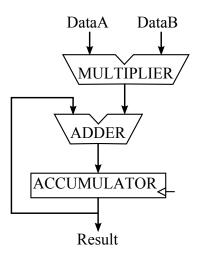

| 45 | Multiply Accumulate unit scheme.                                                                                              | 100 |

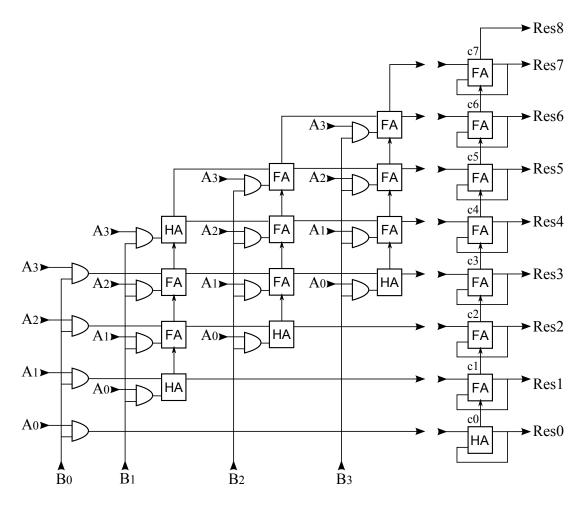

| 46 | 4-bit MAC scheme. Array Multiplier on the left and Ripple Carry<br>Adder on the right.                                        | 102 |

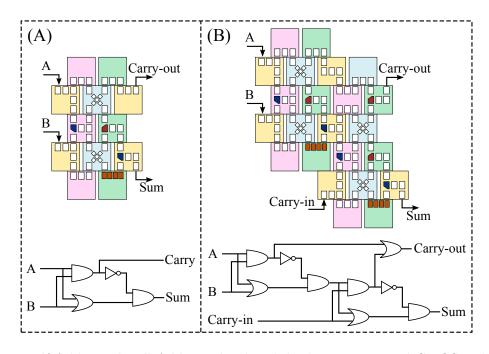

| 47 | Half Adder and Full Adder realized with both ME-NML and CMOS technologies. (A) Half Adder. (B) Full Adder                     | 104 |

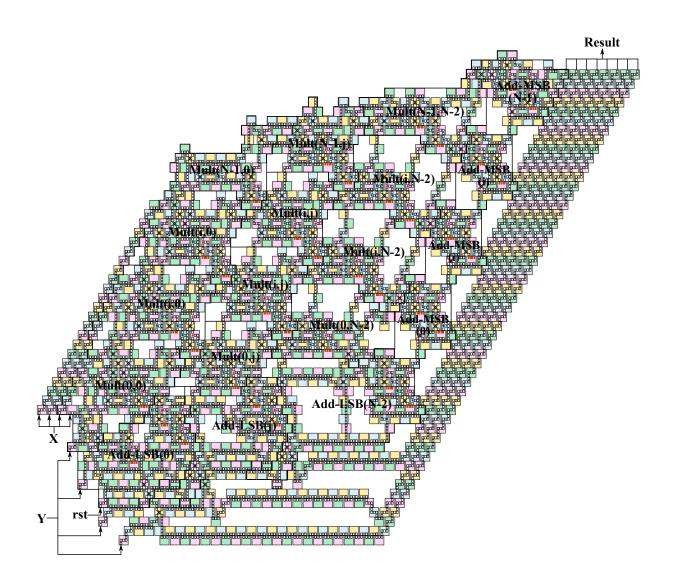

| 48 | 4-bit parallel ME-NML MAC unit. Labels identify the base blocks<br>of Multiplier and Adder.                                   | 105 |

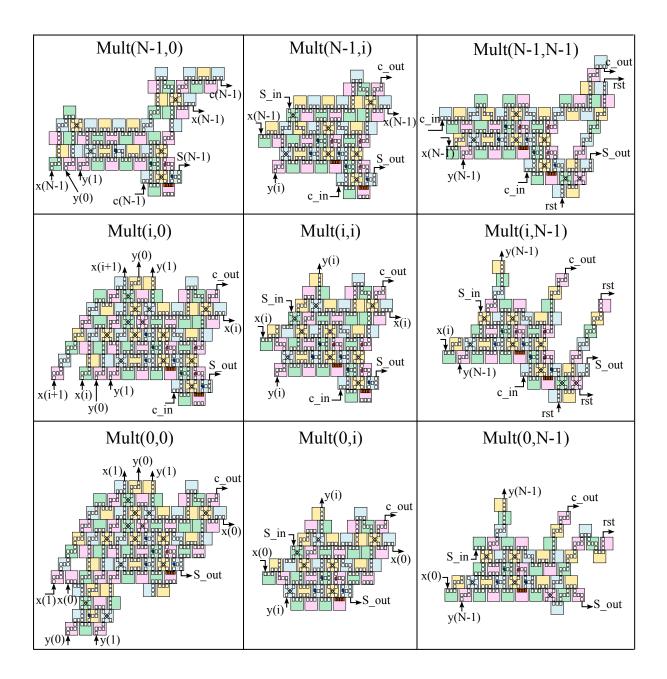

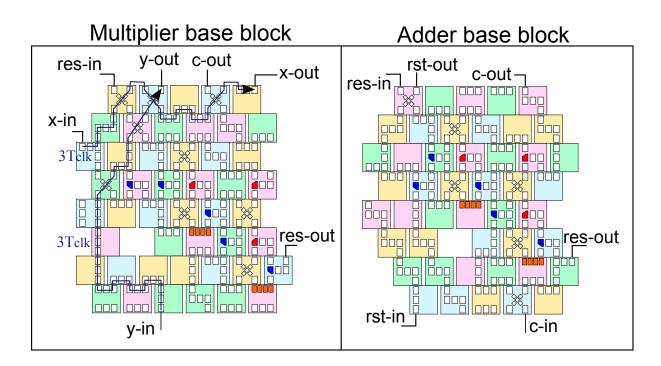

| 49 | Base blocks of the Array Multiplier for the parallel MAC                                                                      | 107 |

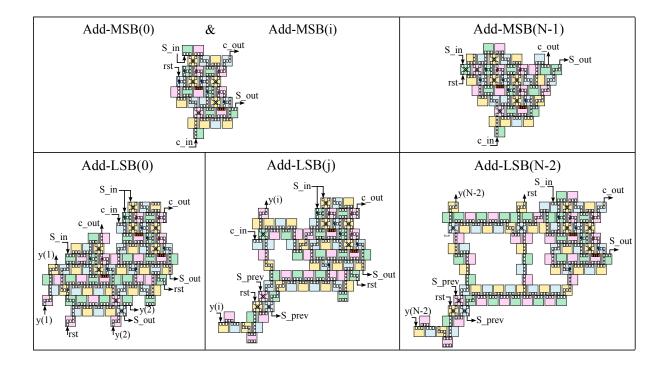

| 50 | Base blocks of the Ripple Carry Adder for the parallel MAC $\ldots$                                                           | 108 |

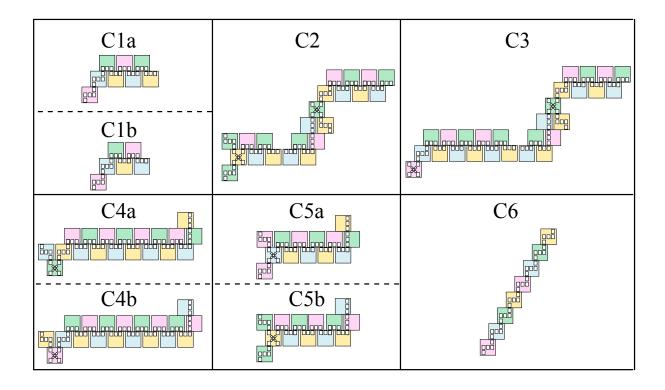

| 51 | Base blocks for the interconnections of the parallel MAC implemen-<br>tation                                                  | 110 |

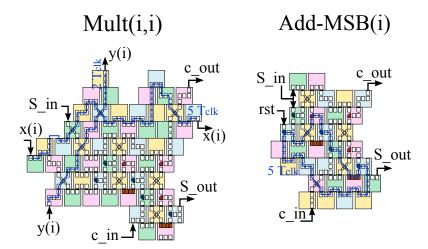

| 52 | Critical paths of the parallel MAC. (A) Critical paths of multiplier's base blocks. (B) Feedback loop of adder's base blocks. | 112 |

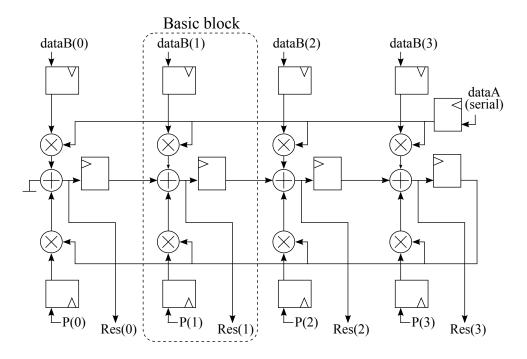

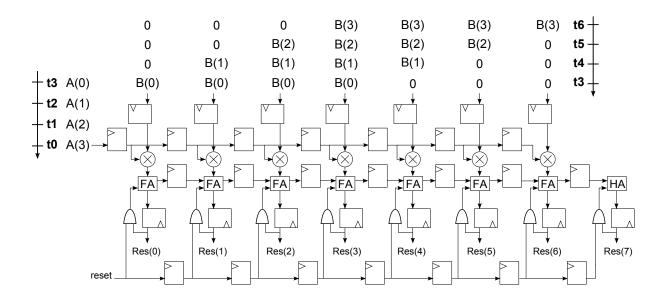

| 53 | Body of the 4-bit serial-parallel MAC                                                                                         | 114 |

## **FIGURE**

| 54 | Full scheme of the 4-bit serial-parallel MAC.                                                                                        | 115 |

|----|--------------------------------------------------------------------------------------------------------------------------------------|-----|

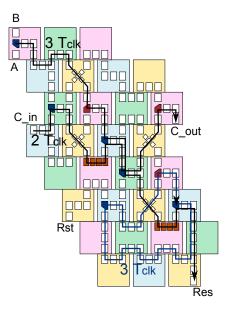

| 55 | Full Adder block for the serial-parallel MAC. Three patterns under-<br>line horizontal crossing, vertical crossing and feedback loop | 117 |

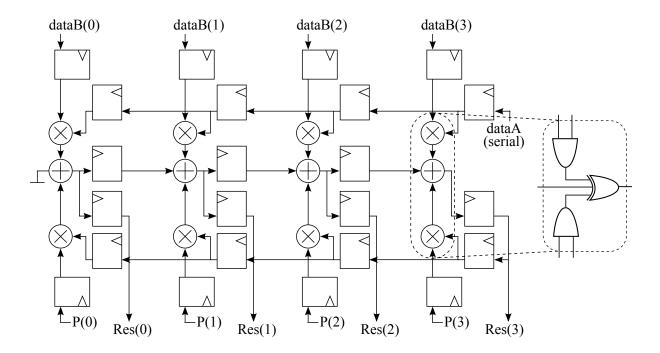

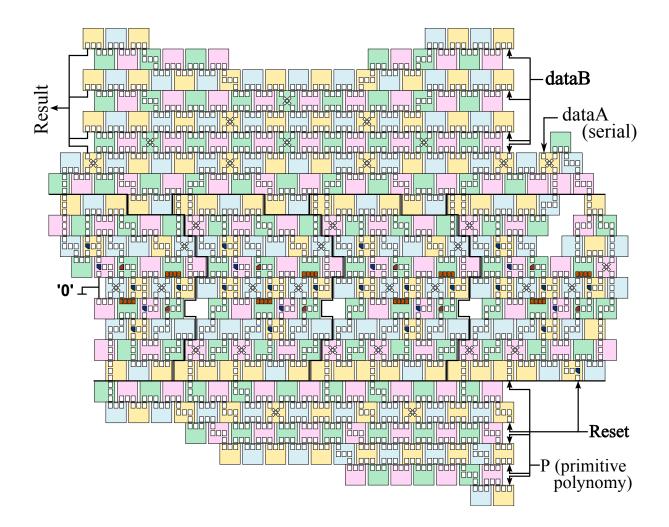

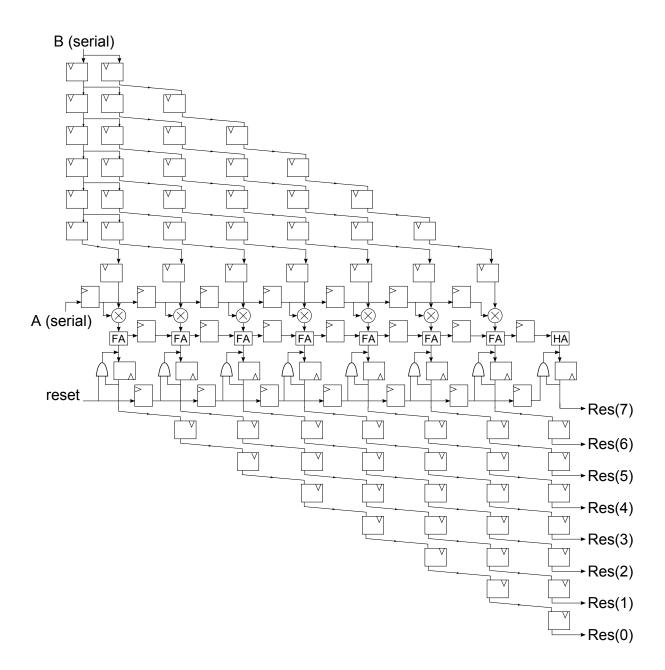

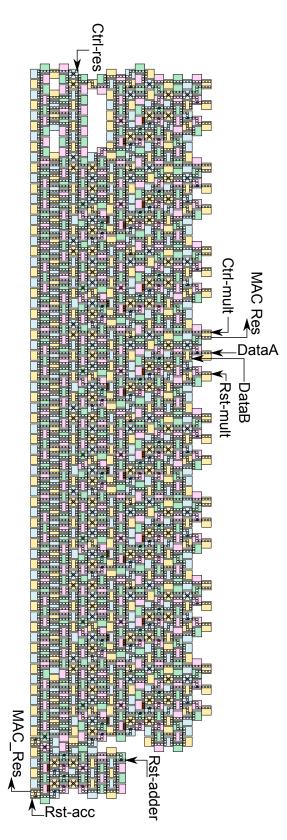

| 56 | ME-NML implementation of the serial-parallel MAC                                                                                     | 118 |

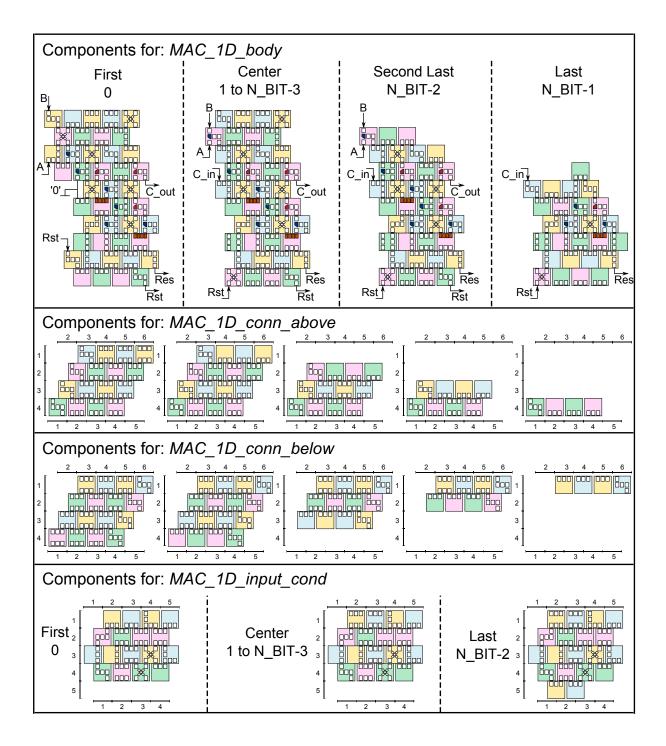

| 57 | Basic blocks for each region of the serial-parallel MAC                                                                              | 120 |

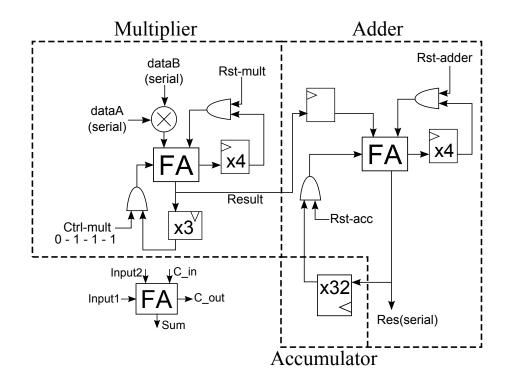

| 58 | Scheme of the 4-bit serial MAC (preliminary implementation)                                                                          | 122 |

| 59 | Handmade 4-bit multiplication algorithm                                                                                              | 123 |

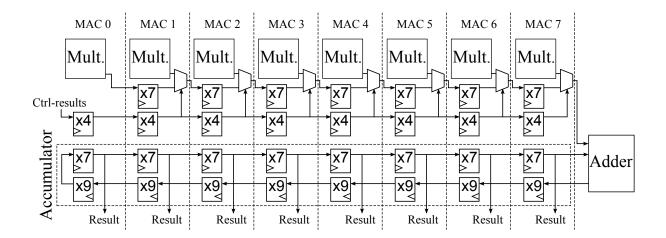

| 60 | Scheme of the 8-bit serial MAC with shared Accumulator and Adder.                                                                    | 127 |

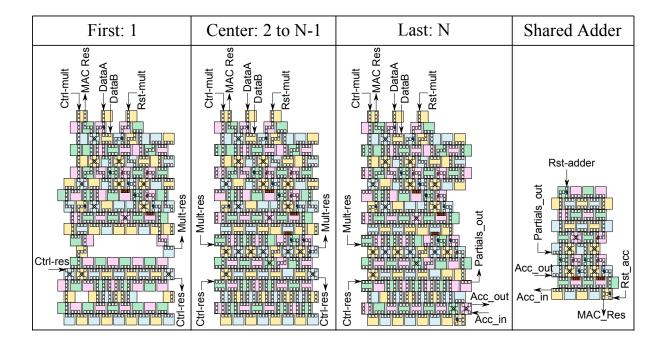

| 61 | Base blocks of the 8-bit serial MAC with shared Accumulator and Adder.                                                               | 128 |

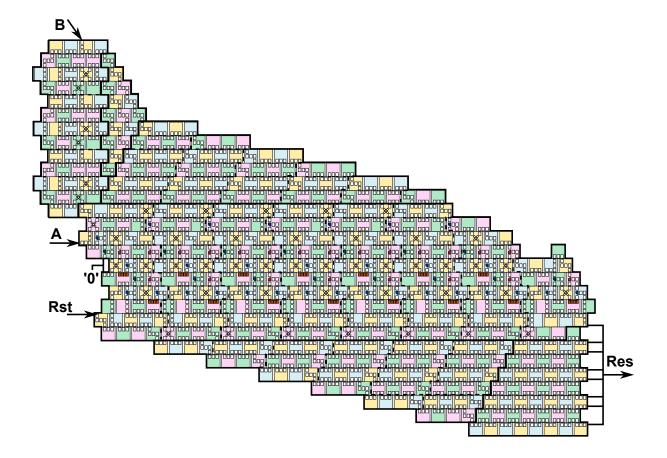

| 62 | ME-NML implementation of the 8-bit serial MAC with shared Ac-<br>cumulator and Adder                                                 | 129 |

| 63 | Central blocks of Multipler and Adder for an optimized version of<br>the Parallel MAC.                                               | 133 |

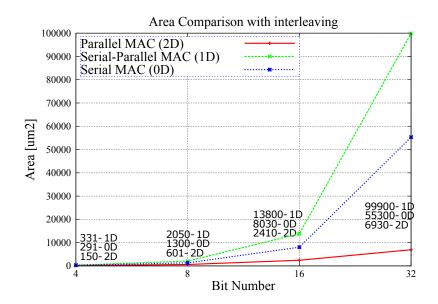

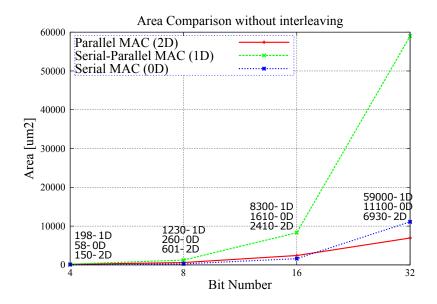

| 64 | Area comparison of the three MAC implementations exploiting in-<br>terleaving and with the throughput being equal                    | 139 |

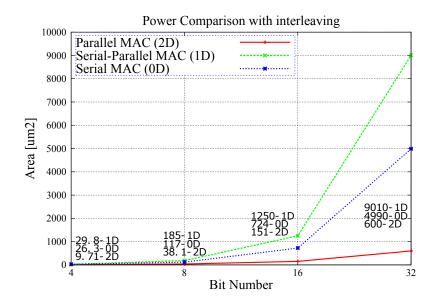

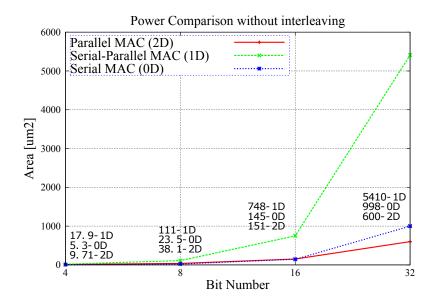

| 65 | Power comparison of the three MAC implementations exploiting in-<br>terleaving and with the throughput being equal                   | 140 |

| 66 | Area comparison of the three MAC implementations without inter-<br>leaving and with the throughput being equal                       | 141 |

| 67 | Power comparison of the three MAC implementations without inter-<br>leaving and with the throughput being equal                      | 142 |

### SUMMARY

Among the several alternative technologies proposed for the post-CMOS scenario, Quantumdot Cellular Automata (QCA) is one of most promising for its high level of integration and low power consumption. The magnetic based implementation of QCA, named NanoMagnet Logic (NML), is the only one that can both work at room temperature and is feasible with current fabrication processes. Also, its magnetic nature opens up to new possibilities, like developing logic circuits with an intrinsic memory ability.

The base cells of NML technology are nanomagnets, which can be arranged on a plane to create any logic circuit. There is no standby power consumption and the energy required for magnets switching is several orders of magnitude lower than latest CMOS transistors. However the network for controlling the cells' magnetization can nullify the advantages in terms of power losses. This is the case of the Magnetic Clock NML [1], which has been extensively and thoroughly studied in literature. A novel implementation of NML technology, the Magnetoelastic NML (ME-NML), drives the nanomagnets through an electric field instead of a magnetic field, highly reducing the power consumption. This solution has already been proved theoretically and experimentally, however up to now only elementary circuits have been studied.

The Magnetoelastic NML is the subject of this work. To fully understand its potential it is mandatory to analyze complex architectures keeping into account all the physical constraints related to the fabrication process.

### SUMMARY (Continued)

First of all, because of the absence of a tool for design and simulation, we developed a RTL model for handling ME-NML circuits. The model also embeds the capability of evaluating area occupation and power consumption. Due to the strong regularity of the ME-NML circuits layout, we were able to define a Standard Cell library, which is a big step toward the creation of an aided design tool.

Secondly, through a case study we developed an accurate comparison of ME-NML with the Magnetic Clock NML and the state of the art CMOS transistor. ME-NML performances were excellent, enough to largely overcome both the other technologies. This was also the first approach to ME-NML from the architectural level, so it provided general information on circuit design. Nonetheless we could generalize the behavior of our case study to serial-parallel architectures.

Once the validity over other technologies was proven, it was mandatory to understand which kind of architectural organization maximizes the performance of the ME-NML. Therefore through a second case study we performed the first step of this investigation, comparing three different versions of a MAC unit: parallel, serial-parallel and serial. The parallel approach guarantees the best results, but it requires a certain level of interleaving.

In addition to attaining their specific goal, each one of the two case studies has been very resourceful in other fields. In fact they both helped identifying, from an architectural point of view, the major limitations of ME-NML technology as well as its strengths. Therefore this work also provides the first general guidelines for ME-NML design.

### CHAPTER 1

### INTRODUCTION

### 1.1 CMOS scaling

Over the past three decades the inexorable evolution of electronics had as foundation the ever-smaller device dimensions of silicon-based CMOS technology, which has been exponentially improving in both performance and density of integration. Today, however, the conventional physical scaling is experiencing asperities and, as forecasted in the International Technology Roadmap for Semiconductors [2], it is expected to reach its boundaries soon.

This decay counts several factors [3], physical and material limits above all. Basically, due to both electrostatics and tunneling mechanisms, ultra-small MOSFETs leakage currents begin to be comparable to the drain current. The increased leakage current, due to downsizing, forbids the threshold and supply voltages reduction, denying a speed increase. Correspondingly the higher electric field and the high concentration of dopants deeply impact electronic transport. These are some of the well known effects of down scaling: Drain Induced Barrier Lowering (DIBL), Short Channel Effect (SCE), Punch-Through and subthreshold inversion, mobility degradation, band-to-band tunneling [4][5]. Another challenge involves power consumption and thermal dissipation: The power density has been growing, as the supply voltage did not scale as much as the channel length. Furthermore some constraints come from economical aspects and the lithography-based fabrication techniques. Due to all these factors, keeping up with the Moore's Law will most probably be a challenge that will not be answered by Silicon CMOS nanoelectronics. A lot of research on alternative technologies has been carried out to preserve the same rate of performance improvements. The efforts have been focused toward two main directions [2]:

- Innovation of CMOS materials and structures. Demonstrated examples are: SOI (Silicon On Insulator) transistors, with an insulator layer between substrate silicon body, and FinFET, where a multigate structure heavily reduces short channel effects.

- Creation of completely new nanoelectronic devices, called "Beyond CMOS Devices", able to replace CMOS technology. One of the most promising architectures is the Quantumdot Cellular Automata (QCA). Nanotechnologies like QCA offer very high integration density, but they are still in a premature stage: A reliable and functional realization still requires extended study from the device up to the architectural level.

Current transistors exploit electronic charge to store information, therefore switching between logic levels involves charge movement, thus requiring a current flow and a consequent Joule dissipation. Energy losses are then an intrinsic characteristic of charge based electronics and, as explained before, highly scaled transistors will not be able to preserve the charge due to significant leakage. It is clear that charge based devices do not seem to be able to maintain the cost per function improvements of the last decades. The idea is to replace the charge with a new kind of information token such as for instance: Polarization of nanomagnets, change in molecular configuration, electron spin or position of a micromechanical object.

### 1.2 Quantum-Dot Cellular Automata (QCA)

Ever since the introduction of the Cellular Automata idea in 1993 [6], Quantum-Dot Cellular Automata (QCA) has been attracting an increasing interest. It is a valuable candidate for the post-CMOS era, because it effectively addresses the problems of device density and power dissipation.

| 0         | ۲ |   | 0  | 0  | 0   |

|-----------|---|---|----|----|-----|

| 0         | 0 | 0 | 0  | •  | •   |

| $\bullet$ | 0 | 0 |    | 0  | 0   |

| '0'       |   | 1 | 1' | NU | ILL |

Figure 1. Possible states of a QCA cell: Stable states '0' and '1' and unstable NULL state.

QCA technology foundation is a bistable base cell; properly organized arrays of these cells can realize logic functions. The first proposed implementation used a square cell with 4 quantum dots in the corners. Since electrons repel each other, if two electrons are available for each cell, at equilibrium they will be found in two diagonal dots. Since there are only two diagonals, only two states are possible: '0' and '1' [7]. To allow a correct signal propagation we will see in Chapter 2 that a third unstable state (NULL state) is necessary, therefore two more dots need to be added (Figure 1). This is just the generic base cell, but the theoretical principle of the QCA can be realized in other ways, depending on the technology used. Up to now the literature contains five physical implementations, while the first two present strong limitations, the others are way more promising.

- Metal QCA [8][9]. This was the first physical implementation and it had a purely demonstrative purpose. In fact it can work only at temperatures close to the absolute zero, unless the cell size is downscaled to atomic values. The base cell is composed by metallic structures on a SiO<sub>2</sub> substrate and the quantum dots are basically aluminum islands. The links between dots are made of Al<sub>2</sub>O<sub>3</sub> tunnel junctions.

- Semiconductor QCA [10][11]. This approach exploits common electronic devices' structures, the cells and their dots are realized with GaAs and Si-Ge heterostructures. The electrons behavior is driven by a voltage applied to metal contacts. Compared to Metal QCA the operation temperature can be higher, but still it does not work at room temperature. Another limitation concerns the available fabrication processes, which cannot meet the requirement of very small and identical cells.

- Magnetic QCA or NanoMagnet Logic (NML) [12]. The base cell is a single-domain nanomagnet with dimensions lower than 100nm, its two possible magnetizations correspond to '0' and '1' logic values [13]. About speed (hundreds of *MHz*) and dimensions this implementation is less interesting than the Molecular QCA, it is also slower than CMOS systems. What makes Magnetic QCA attractive lies in its magnetic nature, it has exceptionally low power consumption and a strong logic-in-memory predisposition [1][14][15]. But the most relevant advantage is the physical realization feasibility with current technol-

ogy, it allows to study and experiment on QCA based architectures on a higher abstraction than the single cell, facing directly design problems common to any QCA implementation.

- Molecular QCA [16]. The fundamental states of the Molecular QCA cell correspond to different charge distributions in a complex molecule, the charge movement can be triggered by electrons reacting with the oxide-reduction center of the molecule. Using molecules every QCA cell would be identical to the others and would have the very competitive dimension of a few nanometers. Moreover molecules reactions work perfectly at room temperature and are extremely fast, the expected switching speed of this implementation is of the order of THz [17][18][19]. This is the most promising approach, even though a functioning realization is still far: Current technology cannot manipulate single molecules as required yet. Another delicate issue is the transduction of electrical signals from and to information understandable by the molecule, up to now there is not any valid solution to this.

- Silicon Atomic QCA [20]. The QCA principle is implemented using atoms as quantumdots. It has been proved that the dangling bond (DB) state of silicon atoms can be exploited as a quantum dot. Up to now the experimental results are promising and the electrostatic control over the charge within DB assemblies has been verified [21].

### 1.3 Magnetic QCA

Magnets have already been used in electronics for memory applications, the innovation of Magnetic Quantum dot Cellular Automata (MQCA), also called NanoMagnetic Logic (NML), is to use magnets to implement logic functions. The result are digital circuits with intrinsic

Figure 2. A) Hysteresis cycle of a multidomain magnetic material. B) Hysteresis cycle of a single domain magnetic signal. C) The two stable states of the NML base cell.

memory capability [22]. The current fabrication techniques allow to produce the NML base cells [23], which are nanomagnets with dimensions between 50nm and 100nm. Magnets so small behave differently than bigger ones, they have only one magnetic domain, which means that the magnetization does not vary across the magnet, and the hysteresis cycle gets as in Figure 2.B. Hence nanomagnets smaller than 100nm can have two stable states only, which will be used to represent '0' and '1' values. The hysteresis cycle describes how magnetization (M) changes as a function of the magnetic field (H) applied.

As already anticipated there are several reasons that make the NML study worthy, even if the working frequency is limited:

• NML is the only QCA implementation that works at room temperature and it can be fabricated with current technology [23].

- Magnets do not dissipate static power and a single magnet switching absorbs around  $30k_BT$ . Therefore NML potentially has an extremely low power consumption.

- Since the difference between QCA and CMOS technologies is bottomless, to fully comprehend the potential of QCA, it is mandatory to investigate complex architectures, also considering all the working and fabrication constrains. Fortunately most of the architectural study on NML could probably be applied to other implementations like the molecular QCA, which seems far more promising than Magnetic QCA but it is still not supported by current technology.

### CHAPTER 2

### NML BACKGROUND

#### 2.1 QCA basics

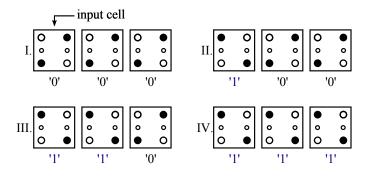

Figure 3. Signal propagation through a 3 cells QCA wire. II) The first cell is forced to '1'. III) The second cell switches to '1' due to electrostatic interaction. IV) The third cell switches.

The QCA base cell described in Section 1.2 contains six quantum dots, allowing to represent the '0' and '1' logic values and the NULL state (Figure 1). Placing cells one next to the other on the same plane it is possible to construct digital circuits, where the signal propagation through cells is due to electrostatic interaction. A series of adjacent cells is called wire, Figure 3 represents step by step the information propagation through a 3 cells wire. Forcing the first cell to '1' causes the switch of the nearby cell, due to electrons repulsion. In the same way the second cell, after switching to '1', will influence the last one. We can say that information propagates with a Domino-like effect.

#### 2.1.1 Logic Gates

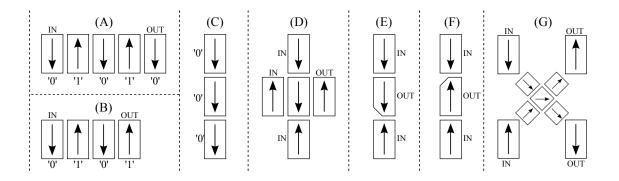

Figure 4. Logic gates of QCA. A) Wire. B) Crosswire. C) Inverter. D) Majority Gate.

QCA technology counts four basic logic blocks, they are depicted in Figure 4, where *IN* and *OUT* identify inputs and outputs. The blocks are: The wire (Figure 4.A), the crosswire (Figure 4.B), the inverter (Figure 4.C), the majority gate, also called majority voter (Figure 4.D). These are the standard gates of the theoretical QCA, keep in mind that each different QCA implementation has a slightly different ports set, even if the basic concepts remain unchanged.

#### Crosswire

The crosswire allows two independent signals to cross each other on the same plane

without interference. The one in Figure 4.B is just one example of crosswire, its actual realization strongly depends on the QCA implementation adopted. An alternative that has been proposed is to use multilayer structures, just like with CMOS technology. Even though it seems that this solution would be suitable for Magnetic QCA, unfortunately at the current time a multilayer structure is still not feasible due to fabrication complexity.

### Inverter

Its logic function is a simple inversion, obtained through a diagonal coupling of cells. Notice that the signal gets duplicated before the inversion to strengthen the diagonal electrostatic interaction, which is weaker than the horizontal or vertical ones. Based on the QCA implementation employed, there are other possible configurations that provide inversion.

### Majority Gate

This logic block is a peculiarity of QCA circuits, together with the inverter it allows to design any logic function. It is a three input port, where the output is equal to the majority of the input values. Referring to Figure 4.D, notice that the central cell is subject to the influence of the top, left and bottom cells. The output will be '1' if that is the value of at least two inputs, and the same works for '0'. The majority gate ( or majority voter) logic function is:

$$F = AB + BC + AC.$$

#### 2.1.2 Signal propagation and Clock

Despite what said above, the electrostatic interaction is not strong enough for a signal to propagate through a wire. The switching of a cell requires as much energy as the barrier between its two stable states, that is the energy keeping electrons trapped in the dots. Of course this amount of energy  $E_k$  (Kink Energy) is strictly related to the QCA implementation used, the cell size and the operating temperature. However this value is generally high enough not to allow autonomous data propagation. For this reason there is the need for an external mean able to control the signal propagation by acting on the energy barrier between the two stable states. Such barrier can be lowered by applying an electric field, as a consequence the electrons will be forced into the central dots leaving the cell in an unstable state, which is referred to as NULL state. Once removed the external field the cell will stabilize either at '0' or '1', depending on the state of neighbor cells.

So the main idea is that if we want a cell to assume the same value as its neighbor, we force such cell in an unstable state through an external electric field, and then we simply release the field. This control field is called *clock*. In principle this technique could work with an infinite number of cascaded cells, but practically the number has to be small. Otherwise there will be propagation errors mainly due to thermal noise [24]. Therefore a spatial flow control system is mandatory.

From the remarks above it is clear that a signal cannot pass through a whole circuit at once, the cells pattern would be too long. The solution is to break the circuit in small sections and let signals go over one section at a time, in a pipelined manner. So circuits are partitioned in

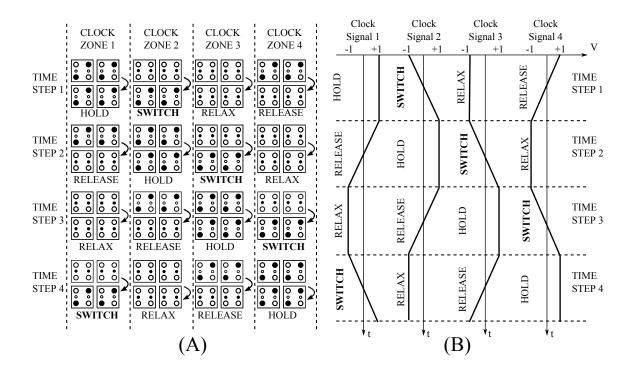

Figure 5. Clock mechanism. A) Clock zones. B) Clock signals.

small areas, where each area counts a limited number of cascaded cells; this areas will be called *clock zones*. In the classical scheme the spatial and timing control of the circuit is conferred to a four phases clocking system. There are then four clock signals with the same waveform but different phase. The  $2^{nd}$ ,  $3^{rd}$  and  $4^{th}$  clocks will have respectively  $90^{\circ}$ ,  $180^{\circ}$ ,  $270^{\circ}$  phase shift with respect to the  $1^{st}$  clock. Each of the partitioned section will receive one of the four clocks, a correct assignment of the clocks will assure a correct circuit functioning.

Figure 5 shows the clock waveforms on the right and the functioning of a wire divided into four clock zones on the left. As explained we need a clock that can force cells in their unstable

Figure 6. Simplest clock phases layout, the circuit's area is partitioned in vertical stripes.

state before the switching phase. The clock waveform has got four phases, as clearly pointed out by Figure 5.B:

- Hold phase. The potential barrier is kept high by a high clock voltage. The cell cannot be influenced by neighbors.

- **Release phase.** The clock voltage goes from high to low and so does the energy barrier. At the end of this phase the cell reaches its NULL state.

- **Relax phase.** The potential barrier is kept low, so the barrier between stable states stall at its minimum. The cell is in the NULL state.

- **Switch phase.** The clock voltage goes from low to high and so does the potential barrier. The cell will stabilize in one of the two states, depending on the neighbor cells.

In Figure 5.A the signal goes from left to right. When a clock zone is switching it is influenced by nearby cells. Cells on the left are in HOLD, they act as input, while cells on the right are in the RELAX phase, so they have no influence on the switching cells. In between of HOLD and RELEASE, the cells are either relaxing or latching. This metodology assures data propagation in a specific direction, it is thus fundamental to arrange the clock zones properly. For a correct functioning a signal must pass through the clock zones in order from 1 to 4 and then 1 again.

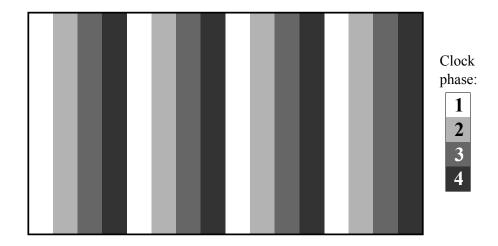

At this point the last issue is to decide how to arrange the clock zones. In principle the circuit area can be subdivided in clock zones with any shape, but of course technological limitations due to the clocking network must be always kept in mind. A straightforward arrangement of clock zones is represented in Figure 6, the circuit is divided in columns. The four shades of grey correspond to the different clock phases. The simple subdivision in columns has the strong disadvantage of allowing signal propagation in one direction only, following the clock phases order: 1,2,3,4,1,2... To be able of dealing with any kind of circuit, the structure has to be more complex, it must allow propagation in any direction.

### 2.2 Nano-Magnets Logic (NML)

The most recent advancements in fabrication techniques, especially the lithography, allow to build logic circuits using magnets. While magnets have already been used in electronics for memory applications, the innovation of this implementation is to use magnets to implement logic functions. As a result NML circuits are digital circuits with intrinsic memory capability. The base element of NML is a very small bistable magnetic cell. Since it is not a permanent magnet, its magnetization can be influenced by external means. Therefore nanomagnets placed side by side will arrange themselves in an antiferromagnetic manner, because of the attraction between opposite poles.

The nanomagnets dimensions must be between 50nm and 100nm. The upper limit assures that the magnets only have one magnetic domain, which means that the magnetization does not vary across the magnet and the hysteresis cycle gets as in Figure 2.B. The two saturation values M = +1 and M = -1 are the only stable states, therefore they are associated to logic values '0' and '1'. The lower bound of 50nm is, instead, crucial to avoid the superparamagnetic effect, which would cause the magnetization to vary together with thermal fluctuations. To assure thermal stability the energy barrier between the two stable states must be at least  $30k_BT$ . As from Figure 2.C the two states have magnetizations in opposite directions, so they both lie on the same axis. At the equilibrium, if one side of the magnet is longer than the other, thanks to shape anisotropy, the magnetization will be forced along the longer axis (easy axis). Therefore it is important that in NML the ratio between the magnets dimensions (aspect ratio) is within the 1 : 1.2 range. For a correct signal propagation it is mandatory that every base cell is equal in shape to the others. Consequently, the more troublesome is the production, the higher will be the fault probability. That is why the rectangular and elliptical shapes are the most used, as they assure the best precision in the fabrication process.

The main advantage of Magnetic QCA is to be realizable with current technology ()electron beam lithography or high end optical lithography) together with its ability to operate at room temperature. The fabrication feasibility was first proven by researchers of the University of Notre Dame in Indiana (US). They built horizontal wires, vertical wires and majority gates [25]. A Magnetic QCA horizontal wire was also created by researchers of Politecnico di Torino.

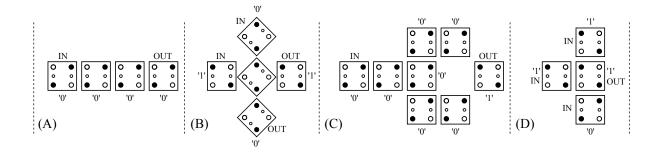

Figure 7. A) Horizontal wire. B) Inverter. C) Vertical wire. D) Majority Voter. E) AND port. F) OR port. G) Crosswire.

Even though the set of logic gates for the NML circuits recalls the generic QCA basic blocks (Figure 4), there are some differences and improvements. It is understandable that, moving from the general idea to the physical implementation, the general ports can be optimized based on the actual technology features. Figure 7 shows the complete set of logic blocks for NML circuits. The main difference with generic QCA is the horizontal coupling: Horizontally magnets align themselves antiferromagnetically, each magnet has inverted polarization with respect to the neighbors. So the inverter can be simplified to a simple horizontal wire with an even number of

magnets as in Figure 7.A. On the other hand an odd number of adjacent magnets would result in a buffer function, that is a simple wire (Figure 7.B). Vertically the coupling is ferromagnetic, so no inversion is possible (Figure 7.C). The majority voter, depicted in Figure 7.D, is pretty much the same as for general QCA.

Another disparity comes from the possibility of obtaining specific logic gates modifying the shape of a magnet: By making magnets with slanted edges it is possible to create *AND* and *OR* logic functions [26]. QCA would generally need a three inputs majority gate to obtain AND and OR logic ports, while only two inputs are needed for non-majority based gates, considerably optimizing area occupation and layout entanglements. The different-shaped magnets acquire a preferential state, which they will leave only when both inputs, from above and below, are up or down, implementing as a consequence an AND or OR logic function (Figure 7.E, Figure 7.F).

At the current time the NML crosswire realization does not have experimental proof of reliability yet. A possible implementation is the one represented in Figure 7.G, the crossing is made of five square cells (50nm - 100nm of edge) that have four stable states instead of two. In this way they can let pass through two signals simultaneously.

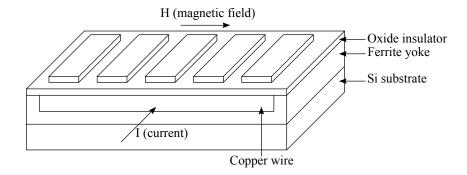

#### 2.2.2 Magnetic Clock NML

One solution for controlling the nanomagnets magnetization in NML circuits is the Magnetic clock, as proposed in [12] and verified experimentally in [23]. The magnetic field is generated by a current flowing through a wire positioned under the magnets plane (Figure 8). The material for the wire is copper, buried in a ferrite yoke envelope for field confinement. The wire's

Figure 8. NML with Magnetic Clock mechanism. The magnetic field H is generated by the current I flowing through the copper wire, which is placed under the magnets plane.

thickness must be enough to generate a magnetic field able to force cells to the intermediate state (NULL state) [27].

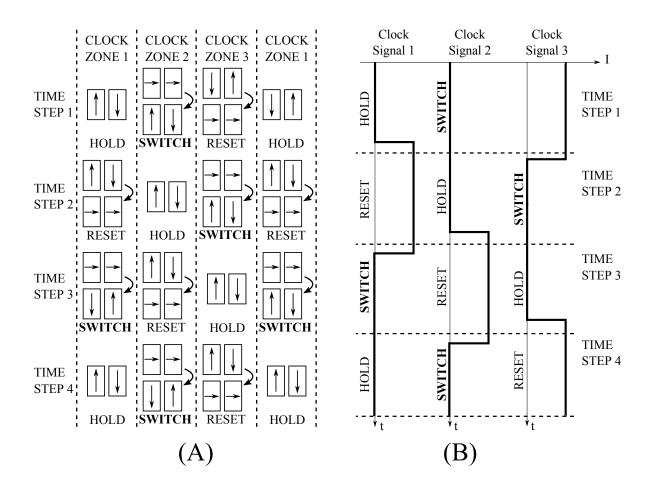

As explained in Section 2.1.2 a multiphase clock system is required. The classic scheme has 4 phases, but also a 3-phase clock is feasible [28][29][30]. The Magnetic NML normaly exploits a 3 phase clock system is normally exploited. Figure 9 shows the functioning of the 3-phase clock of a horizontal wire over time (vertical axis), just like in Figure 5 for the generic QCA.

Each clock zone undergoes three phases in the following temporal sequence: RESET, SWITCH and HOLD. The RESET (clock = 1) erases the information, leading cells to an intermediate state. In the SWITCH phase the clock goes to zero, so cells can assume a magnetic orientation. The orientation is influenced by the nearby cells being in HOLD state, as cells in the RESET state cannot affect the neighbors. When a group of cells, in the same clock zone, is in the HOLD phase, they have a stable magnetization.

Figure 9. The clock phase sequence is RESET, SWITCH, HOLD. A) Functioning in space (horizontally) and time (vertically) of a horizontal NML wire. B) The 3 clock signals. They are applied to different zones in space and they are repeated over time. They are the same in magnitude but with a 120 phase shift.

To assure a correct signal propagation the RESET phase applied to different zones must overlap in time as in Figure 9.B, where the RESET state lasts slightly more than  $2\pi/3$ . The reason lies in the fact that when a zone is in the SWITCH phase, the two neighbor zones must be respectively in HOLD and RESET phase. However if the field of the SWITCH zone is removed and the field is applied to the RESET zone at the same time, a back propagation phenomenon could take place. Initially, when the field is removed from the SWITCH zone, the RESET zone would still be in the HOLD state, as magnets need a finite time to switch from a stable polarization to the intermediate state. In Figure 9.A we can see how the value in *Time step 1* on the left is propagated step by step to magnets in the clock zone on the right.

### 2.2.2.1 Snake Clock Layout

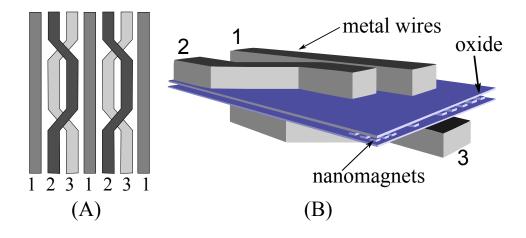

The generic QCA is based on a 4-phase clock system, however it is also possible to use a 3-phase clock [12], given that the signals are overlapped. The clock network for Magnetic NML is a 3-phase overlapped system, called Snake-clock; its layout and 3D structure are depicted respectively in Figure 10.A and Figure 10.B.

Figure 10. Snake-clock. (A) Top 2-D layout. (B) 3-D layout. The nanomagnets are placed between the two planes. Magnets cannot be placed where wires 2 and 3 are twisted.

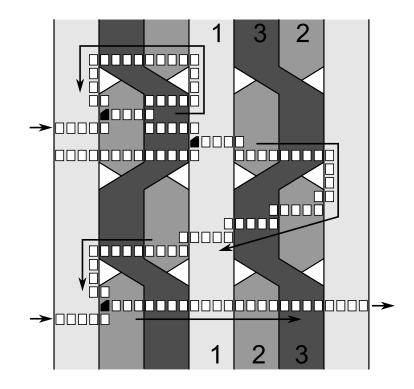

Figure 11. Example of a simple circuit based on the *Snake-Clock* system. Different background colours refer to different clock zones. The arrows show the signal flow direction.

The Snake-clock is based on the scheme in Figure 6, but with three phases only and with an expedient that allows propagation in both directions: left-right, right-left. The clock wires are basically simple metal wires parallel to the magnets plane, two positioned above and one below [28]. Two thin oxide layers provide separation between clock wires and nano-magnets. One clock wire is straight (number 1), while the other two have a complementary zig-zag shape. They are like twisted wires, but they do not display any interference, as they are on different planes. In the case in Figure 10.B the wires 1 and 2 are routed on the same plane, while the clock 3 is on the other one.

Considering now the top view in Figure 10.A, it is straightforward to understand that magnets cannot be placed on areas corresponding to the wires twisting, as they would be affected by both clock wires 2 and 3. Moreover, in those regions, wires are not parallel to the magnets long side, hence the generated magnetic field would force them in the wrong state.

Figure 11 shows a very simple circuit based on the Snake-Clock system. The direction of the information flow is highlighted by arrows, signals propagate through clock zones in the order 1, 2, 3 and so on. The clock wires twisting divides the circuit area in horizontal stripes with alternate propagation directions. Furthermore, as required by this clock mechanism, there are no magnets placed over the twisting areas. The magnets with a slanted edge required for the AND logic function are highlighted in black.

# 2.2.2.2 Working frequency

The main limitation of NML technology is the maximum working frequency, which is intrinsically bounded. To obtain the highest possible clock frequency the clock zone width should be equal to that of a single magnet. However the usual width is 3-5 [24] because of several factors: fabrication limitations, thermal noise, latency, throughput. The more are the consecutive magnets in a clock zone the lower will be the clock frequency. The constraints on the clock frequency are mainly related to the clock mechanism chosen and the fall and rise time of the adiabatic switching of clock signals, mandatory to reduce power consumption. Less critical is instead the bound derived from the switching time of nanomagnets from the intermediate (NULL) state to a stable one and viceversa. The NML circuit speed is expected to be of the order of 10 - 100MHz [31][32][33].

In the beyond-CMOS scenario, NML technology is a good solution but it cannot aim to completely substitute CMOS. Despite the clear benefits for what concern occupied area, power consumption and memory ability, NML's clock frequency cannot keep up with CMOS.

### 2.2.3 Magnetoelastic Clock NML (ME-NML)

Recently a valuable alternative to the Magnetic Clock NML has been proposed and studied: the Magnetoelastic Clock NML, also referred to as ME-NML [1][34].

In the previous section (2.2.2) the proposed external mean, responsible for the magnets switching, was the Magnetic Clock with a Snake-clock layout. The idea was to position clock wires below or above the magnets plane. A current flowing through the wires would generate a magnetic field able to control the cells magnetization. The generated field is then along the magnets' short side of the magnets, forcing cells in an intermediate unstable state.

The interest in Magnetic QCA is mainly due to the very low power consumption, several times lower than the latest CMOS transistors. While this is true for the magnets switching, unfortunately it does not apply to the clock generation system:  $1\mu m$  copper wires with a required current of 545mA [35]. Due to Joule losses the power dissipation of the clocking system is very high, nullifying the advantage of a low-power magnets switching.

To solve this problem an alternative solution has been recently proposed [35][34], it is based on the Magnetoelastic effect: the magnetization of magnetic materials undergoing mechanical stress is bonded. Applying a mechanical stress with proper intensity and direction magnetic cells

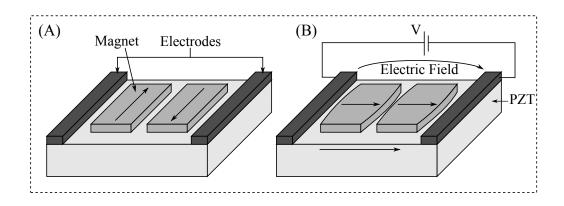

Figure 12. Magnetoelastic NML clocking mechanism. A) No voltage applied. B) Voltage applied to the electrodes. The PZT substrate induces a strain on the nanomagnets forcing their magnetization to their intermediate state.

can be forced into the RESET state. The magnetic cells (10nm thick) are coupled with a 40nm thick PZT layer (Figure 12.A). To maximize the mechanical coupling, magnets are deposited directly onto the piezoelectric material. For a proper strain transfer, the PZT substrate has to be much thicker than the magnets. The magnetic material is then controlled by applying a voltage (few mW) to the piezoelectric. When the voltage is applied, the strain induced by the piezoelectric material, forces the magnetization of the magnets layer to the intermediate position, parallel to the short edges (see Figure 12.B).

The electrodes are deposited on top of the PZT, while the wires that drive the electrodes can be placed in additional layers, just as for CMOS. This makes this NML implementation compatible with CMOS fabrication. This approach comes from a previous idea based on multiferroic structures instead of simple magnets [33][36]. The performances of the pure multiferroic structure are better, but there are two major fabrication problems. The aspect ratio is critical, there are only 2nm of difference between the length of the two cell's sides. Such a low resolution is hardly achieved with the Electron Beam Lithography. Moreover the electrodes should be only a few nanometers thick, a request that does not comply with the current technology. A pair of them is necessary for every element, to apply the required voltage. The advantage of the solution with the simple magnets is the feasibility with current fabrication techniques. Even if its performances are slightly worse than the multiferroic solution, they are anyway remarkably better than the previous NML solutions.

Since the clock system exploits a voltage instead of a current, the power consumption is extremely low, meeting the unmatched expectations for the initial Magnetic QCA concept. In [1], after a detailed analysis, the selected magnetic material is Terfenol, an alloy of Terbium, Disprosium and Iron. The choice is mainly based on three parameters:

- maximum stress that can be applied to avoid permanent damage on the magnets;

- maximum value of electric field that can be tolerated by the piezoelectric material, since it is an insulator;

- minimum stress to force magnets in the RESET state;

- assure shape anisotropy equal of at least  $30K_bT \approx 1.24 \cdot 10^{-19}J$ , to have negligible effects of the thermal noise on the magnets stability;

- minimum aspect ratio for fabrication feasibility;

• tolerance to process variation of  $\pm 20\%$ , remaining within the working range.

#### 2.2.3.1 Circuit Layout

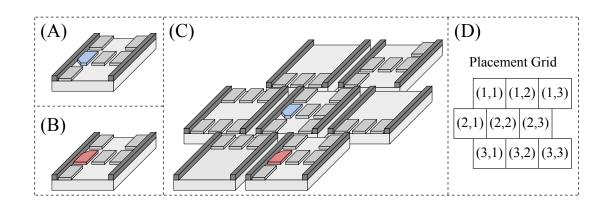

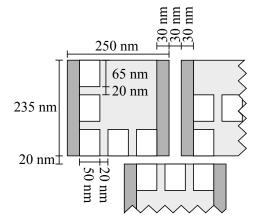

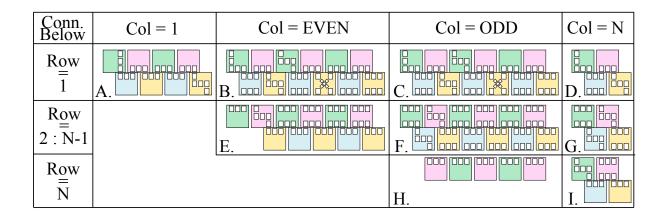

Figure 13. Clock zones of the ME-NML. A) Clock zone with AND logic function. B) Clock zone with OR logic function. C) Circuit layout example. D) Placement grid for ME-NML Cells

Starting from the structure just described in Section 2.2.3, MagnetoElastic clock NML (ME-NML) circuits are composed by mechanically isolated islands, like the one in Figure 13. Each island corresponds to a clock zone and it is driven by one of the clock signals, applied as a voltage on the Platinum electrodes. Notice that the electrodes position on top of the PZT is compatible with CMOS fabrication and leads to a uniform electric field distribution on the magnets plane. The presence of the electrodes makes the clock zones communication on those sides impossible. The signal propagation among cells is allowed only through the top and bottom sides, which are free from electrodes. For this reason the Majority Voter port cannot be constructed. Therefore the basic logic gates exploited are inverter, AND (Figure 13.A) and OR (Figure 13.B) [26], so that any logic circuit can be implemented.

Figure 13.C shows how to put together the clock zones to create a circuit. As already said, the communication among cells can take place only through the top and bottom corners, because of the electrodes. For this reason the cells in a row are shifted with respect to the adjacent ones, to assure a correct signal propagation. In fact the cells are placed on a grid as in Figure 13.D, where the coefficients identify row and column of the cell's positioning within the circuit.

In the example of Figure 13.C the clock zones have both height and width equal to three nanomagnets. This is the solution adopted throughout the whole work, it has been chosen over the five magnets version. Thermal noise [24] and fabrication constraints allow cells dimensions to vary only between 3 and 5 nanomagnets. Small dimensions lead to smaller electrodes and cells, requiring then a very high resolution fabrication process. The minimum size feasible with current technology is 3. Bigger dimensions will relax the technology constraints, but will increase the error probability due to thermal noise and decrease the maximum circuit speed. If two many cascaded magnets are present in a clock zone, the signal propagation will be error prone.

The size of the electrodes varies according to the clock zones dimensions. They are 30-40nm for the three magnets cells, while 70-100nm for the five magnets case. This kind of electrodes are already available for CMOS technology.

Figure 13 does not highlight how and which clock signals are routed to the clock zones. It will be clarified later on in Section 3.3, where it will also be explained which kind of multi-phase clock system best suits the Magnetoelastic NML implementation.

## 2.2.4 Intrinsic Pipeline

In a N-phase clock system, signals need a clock period to propagate through N clock zones. As a consequence the delay of a signal depends on how many clock zones it has to cross. This is quite different from CMOS where wires with different lengths have very similar delays. Each clock zone crossed by a signal can be modelled as a register, as a result it is easy to understand that NML circuits (just like QCA) are intrinsically pipelined. Every group of N adjacent clock zones has an overall delay of a clock cycle.

For this reason signal synchronization is a very delicate issue in NML circuits. Figure 14 is useful for clarifying the problem, the input wires routing is correct in part B, while incorrect in part A. For a proper circuit functioning the three input signals must reach the two AND ports simultaneously, to do so the routing must assure that the input wires cross the same amount of clock zones. The example was presented for the Magnetic NML case, but the same concept applies to ME-NML as well as any QCA implementation.

The problem gets more complex when dealing with feedback signals, see for example the feedback in Figure 11 at the top left corner. While the external input of the AND port arrives

Figure 14. NML signal synchronization. The three inputs must arrive to the two AND ports simultaneously. To do so the input wires must pass through the same number of clock zones. (A) Not working routing. (B) Correct routing.

at every clock cycle, the second one (the feedback) arrives later. The output of the AND port needs two clock cycles to be fed back. Therefore at every clock cycle the AND operation is performed between the new input and the output result obtained 2 cycles before. The proper result will arrive at the next time step. Notice that the longer the feedback wire, the longer the delay. The input must then be delayed long enough to match the length of the feedback loop. In conclusion the inputs have to be fed with a delay equal to the feedback length, reducing then the throughput, particularly in case of long loops. If, for instance, a circuit has a feedback 5 cycles long, only an input every 5 cycles can be fed. Therefore the throughput is 1/5 of what it could be if the input was continuous. In fact, at any time, only 1/5 of the magnets will contain useful data.

## 2.2.4.1 Interleaving

Figure 15. Data interleaving. In this example 3 operations are executed in parallel: A + B + C, D + E + F, G + H + I. At every clock cycle the input data comes from a different operation. Since the feedback loop is 3 registers long, data from the same operation are fed with 3 clock cycles of delay.

The problem of pipelining in CMOS sequential circuits is very complex and delicate. Unfortunately it is even worse for the NML (QCA) technology, as it is not possible to control the pipeline level. Since the pipeline is intrinsic to the technology, it cannot be eliminated, it can only be reduced by optimizing the circuit layout.

The usual improvement techniques for CMOS pipelining are jump prediction and instruction reordering, but for NML (QCA) they can only reduce the problem, they are not able to solve it. A radical solution is the *Data Interleaving* [22], which allows to reach the maximum throughput. The idea is to have a continuous flow of input data. Multiple non correlated set of operations are executed in parallel, so that the delay time between an input and the next is filled with other operations.

Figure 15 shows an example of data interleaving mechanism. Three operations are executed in parallel: A + B + C, D + E + F, G + H + I. At clock cycle 1 the first data of the first operation, A, is given as input. For a correct synchronization, B has to be fed when A reaches the end of the feedback loop, which is 3 clock cycles long. Therefore we give A, B and C as inputs respectively at clock cycles 1, 4 and 7. In the intermediate time steps we can execute in parallel the other two operations, to reach the maximum throughput. This is possible only if the three operations are uncorrelated. So at clock cycle 2 the input is not the number data of operation 1, but D: the first data of operation 2. And in the same way we will input G, the first data of operation 3, at clock cycle 3. The same goes for the next time steps; the input order is the following: A, D, G, B, E, H, C, F, I. That is: OP.1 DT.1, OP.2 DT.1, OP.3 DT.1, OP.1 DT.2, OP.2 DT.2, OP.3 DT.2, OP.1 DT.3, OP.2 DT.3, OP.3 DT.3 (where OP. stands for operation and DT. for data). Data interleaving is a simple expedient that can solve the deep pipelineg problems, but if the required number of operations to execute in parallel is too high then it might not be a feasible solution anymore. The number of required parallel operations is equal to the delay ( in terms of clock cycle) of the longest loop inside the circuit. During the circuit design phase for NML circuits it is then extremely important to keep loops as short as possible.

# CHAPTER 3

# VHDL MODEL FOR THE MAGNETOELASTIC NML

The main purpose of this work is to study for the first time the Magnetoelastic Clock NML (ME-NML) from the architectural point of view, taking into account physical and technological constraints. The work directly concerns ME-NML, but some aspects could be easily generalized to other QCA implementations. The Magnetoelastic clock system has been verified [1], but no design and architectural study is present in literature. As for now there is no automated tool for properly simulating and synthesizing NML circuits. For this reason researchers at Politecnico di Torino developed a VHDL model (preliminary done in [37][38][39]) and a design tool, named ToPoliNano [40]. This tool is specifically constructed for the Magnetic clock NML.

Based on this idea we developed a RTL model in VHDL language which allows to:

- easily simulate any ME-NML circuit, verifying its functioning;

- hierarchically estimate the circuit performance in terms of area occupation and power consumption.

The model keeps consideration of all the relevant technology constraints. The result will be a circuit with an embedded evaluation function for power and area. Thanks to the clock network, each clock zone samples one data per clock cycle, therefore it can be modeled with a register as they have the same behavior.

### 3.1 Standard Cell Library

In Section 2.2.3.1 Figure 13 shows that the ME-NML layout is based on mechanically isolated islands, which will be referred to as cells or clock zones, as they receive their own clock signal. It has been already mentioned that, for fabrication and physical limitations, the height and width of a cell can be of either 3 or 5 magnets. For this work we chose the  $3 \times 3$  cell dimension, as it is the smallest size feasible with current lithographic resolution. Compared to bigger cells, it has a shorter critical pattern (number of cascaded magnets) leading to both an higher working speed and a better signal propagation reliability. Based on our choice all the drawings and circuits from now on will exploit  $3 \times 3$  clock zones, but the VHDL model is generalized for any cell size.

Figure 16. ME-NML cells. A)  $3 \times 3$  size. B)  $3 \times 5$  size.

We noticed that, due to the small size of this ME-NML cells, there is a limited number of possible magnets configurations. Hence the totality of the conceivable clock zones is reasonably small. This interesting feature of ME-NML triggered the idea of designing a finite set of standard cells: a Standard Cell Library, where each element is described in VHDL language. The result is that, assembling cells from the library, any digital circuit can be designed. This standard cell approach confers to ME-NML a propensity for design automation, making this technology very much suitable for having its own simulation and synthesis tool.

| Standard Cells |           |           |                    |     |     |  |  |  |  |

|----------------|-----------|-----------|--------------------|-----|-----|--|--|--|--|

|                | '0'       | '1'       | Crosswire          |     |     |  |  |  |  |

|                |           |           | Inverter           | '0' | '1' |  |  |  |  |

| Wire           |           |           |                    |     |     |  |  |  |  |

| VV IIC         |           |           |                    |     |     |  |  |  |  |

|                | "00" "01" | "10" "11" | Double<br>Inverter |     |     |  |  |  |  |

|                |           |           | AND                |     |     |  |  |  |  |

| Double<br>Wire |           |           | OR                 |     |     |  |  |  |  |

Figure 17. Full  $3 \times 3$  Standard Cell Library for ME-NML.

The full  $3 \times 3$  Standard Cell Library is tabulated in Figure 17. The logic gates are basically the same as for the Magnetic clock NML (Figure 7): Wire, Crosswire, Inverter, AND, OR. But here they must be distinguished also by layout and orientation, not only by their logic function. The main reason is that the whole library is thought in the perspective of a future automated tool for circuit design.