# 2D-Materials: Synthesis and Investigation of Electrical and Thermal Properties

BY

Amirhossein Behranginia B.S., Science and Research Branch of Azad University, Tehran, Iran, 2010 M.S., University of Illinois at Chicago, Chicago, IL, USA, 2016

#### THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Mechanical Engineering to the Graduate College of the University of Illinois at Chicago, 2018

Chicago, Illinois

Defense Committee:

Amin Salehi-Khojin, Chair and Advisor Alan Feinerman, Electerical and Computer Engineering Robert F Klie, Physics Reza Shahbazian-Yassar Jeremiah Abiade

*To parents and to my friends.*

### ACKNOWLEDGMENTS

This thesis paper could not be written without the help and support of Prof. Amin Salehi-Khojin, who served as my supervisor, gave me support and assistance, and provided me with motivation and encouragement throughout the entire period of my research thus far at the Nanomaterials and Energy Systems Laboratory. My deepest gratitude goes also to my family and friends for their moral support. I also wish to particularly thank Mohammad Asadi, Poya Yasaei, Zahra Hemmat and all my collaborators who helped me to complete this thesis.

### **CONTRIBUTION OF AUTHORS**

Main parts of the results and discussions in this thesis are taken from my published or submitted papers with written permission from the journals (see Appendix). Below, the contributions of all the co-authors are listed:

Authors' contributions in chapter 2 (taken from reference [1]): A.Salehi-Khojin and A.Behranginia conceived the idea. A.Salehi-Khojin led the material synthesis, device fabrications, electrical measurements and device characterizations. A.Behranginia synthesized the MoS<sub>2</sub>-graphene lateral heterostructure and performed electrical experiments. A.Behranginia and P.Yasaei carried out device fabrications and characterizations. P.Yasaei and T.Foroozan synthesized the CVD graphene. A.K.Majee performed band structure alignment, mobility, and interfacial resistance calculations. V.K.Sangwan performed 1/f noise and breakdown measurements and analysis. C.J.Foss carried out DFT and transmission coefficient calculations. Z.Aksamija conceived and supervised the calculations. M.C.Hersam supervised the 1/f noise and breakdown measurements and analysis. F.Long performed KPFM measurements and R.Shahbazian-Yassar supervised him. S.Fuladi helped in DFT calculations. M.R.Hantehzadeh helped in CVD MoS<sub>2</sub> and graphene synthesis.

Authors' contributions in chapter 3 (Accepted in ACS Applied Materials & Interfaces): A.S.K. and A.B. conceived the idea. A.S.K. led the fabrication and experiments. Z.A. developed the BTE model and led the first principles calculations. A.B. developed the fabrication process, experimental setup, and thermal analyses. A.B. and Z.H. fabricated all the devices. A.B., P.Y. and Z.H. performed Raman thermometry measurements and thermal analysis. C.J.F. performed the numerical calculations and A.K.M. derived phonon interaction rates. All authors contributed to the write up of the manuscript.

Authors' contributions in chapter 4 (taken from reference [2]): A.Salehi-Khojin and P.Yasaei conceived the idea. A.Salehi-Khojin led the synthesis, fabrication, characterization, and experiments. C.D.Foster led the FE modeling. P.Yasaei, A.Behranginia, and Z.Hemmat synthesized the graphene flakes. P.Yasaei fabricated all the devices and performed the experiments. A.El-Ghandour developed the FE model and carried out the parameter optimization and data extraction process (with P.Yasaei). All authors contributed to the write up of the manuscript.

## SUMMARY

This dissertation presents a study of (1) the growth of in-plane  $MoS_2$ -graphene heterostructure together with its electrical characterizations, (2) the power dissipation of the  $WSe_2$  FET as a representative of 2D-material FETs (Field effect transistors), and (3) thermal dissipation across monolayer CVD graphene, as a representative of 2D-materials, on different technologically-viable substrates.

First, the in-plane MoS<sub>2</sub>-graphene heterostructure is grown by the CVD method for large-scale applications. Electrical characterizations and 1/f noise measurements of this heterostructure reveal an order of magnitude higher electron mobility and lower noise amplitude for this heterostructure compared to conventional metal-contact MoS<sub>2</sub> devices. The KPFM (Kelvin Probe Force Microscop) study is performed to map the surface potential distribution across the MoS<sub>2</sub>-graphene interface and visualizes the reduction of the MoS<sub>2</sub>-graphene interface resistance at positive gate voltages. The DFT (Density Functional Theory) calculations demonstrate that the role of this interface resistance is less than 1% of the overall device resistance at gate voltages above 60 V. Similar failure modes and electrostatic breakdown fields for MoS<sub>2</sub>-graphene and MoS<sub>2</sub>-metal devices are also observed by electrostatic breakdown measurements.

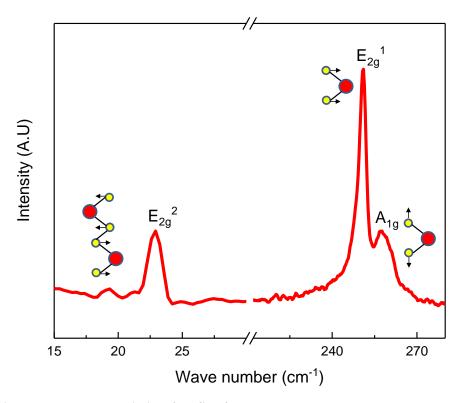

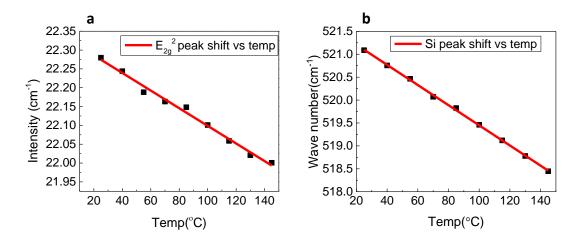

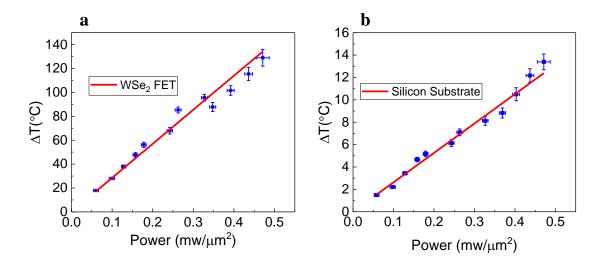

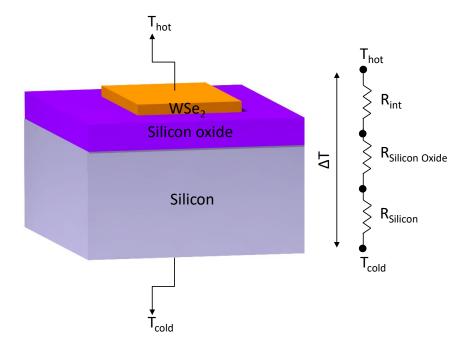

Second, the power dissipation of the WSe<sub>2</sub> FET, as a representative of the 2D-materials, is investigated by the Raman thermometry method. The low-frequency  $E_{2g}^2$  peak of WSe<sub>2</sub> material is used to measure the temperature rise of the device versus different the applied electrical powers. The interface resistance measurement between WSe<sub>2</sub> and SiO<sub>2</sub>/Si substrate reveals that their interface TBC (Thermal Boundary Conductance) is in the low range of the solid-solid interfaces, proving the importance of the interface resistances for thermal dissipation of 2D-FETs.

Finally, to shed light on the role of the interface resistance of 2D-materials with different substrates, thermal dissipation of CVD graphene on different technologically-viable

substrates is investigated. The interface resistances between graphene and different tested substrates reveal that the overall thermal dissipation performance on AlN is better than on diamond substrate, although the thermal conductance of the AlN is significantly lower than that diamond material. These results confirm that the thermal conductance of the substrate is not the only key factor which is important for thermal dissipation of the 2D-material devices and that the role of the boundary resistance between 2D-material and substrate is very crucial.

# **TABLE OF CONTENTS**

## **CHAPTER**

## PAGE

| CHAPTER 1 INTRODUCTION1                                                              | _ |

|--------------------------------------------------------------------------------------|---|

| 1.1. The Importance of Two-Dimensional Materials and their Heterostructures 1        |   |

| 1.2. Preparation of 2D-materials and their heterostructures                          |   |

| 1.3. Potential application of 2D-materials and their heterostructures                |   |

| 1.3.1. Field effect transistors                                                      | ; |

| 1.3.2. Optoelectronic Devices                                                        | ) |

| 1.3.3. Sensor Devices                                                                | ) |

| 1.4. Thermal transport of 2D-materials                                               |   |

| CHAPTER 2 Direct Growth of High Mobility and Low Noise Lateral MoS2-                 |   |

| Graphene Heterostructure Electronics18                                               | ; |

| 2.1. Introduction                                                                    | , |

| 2.2. RESULTS and DISCUSSION                                                          | ) |

| 2.3. Details of Material Synthesis, Characterization, Device Fabrication, KPFM       |   |

| Measurement, Noise measurement and DFT Calculation                                   | , |

| 2.3.1. Graphene Growth Procedure                                                     | ; |

| 2.3.2. MoS <sub>2</sub> -Graphene Growth Procedure                                   | ) |

| 2.3.3. Fabrication of MoS <sub>2</sub> -Graphene Field Effect Transistor             |   |

| 2.3.4. KPFM Measurement                                                              | • |

| 2.3.5. 1/f Noise and Breakdown Measurements                                          | , |

| 2.3.6. Raman Mapping                                                                 | , |

| 2.3.7. DFT Calculation                                                               | - |

| 2.4. Summary and Conclusion                                                          | ) |

| CHAPTER 3 Power Dissipation of WSe <sub>2</sub> FET using Low-Frequency Raman Peak58 |   |

| 3.1. Introduction                                                                    | ; |

| 3.2. Results and Discussion                                                          |   |

| 3.3. Summary and conclusion                                                          | ) |

| CHAPTER 4 QUANTIFYING THE LIMITS OF THROUGH-PLANE THERMAL                            |   |

| DISSIPATION IN 2D-MATERIAL-BASED SYSTEMS81                                           |   |

| 4.1. Introduction                                                                    |   |

| 4.2. Results and Discussion                                               | 83  |

|---------------------------------------------------------------------------|-----|

| 4.3. Details of Material Synthesis, Device Fabrication and FE Simulations | 103 |

| 4.3.1. Graphene growth procedure                                          | 103 |

| 4.3.2. Device Fabrication                                                 | 103 |

| 4.3.3. FE Simulation                                                      | 104 |

| 4.4. Summary and Conclusion                                               | 104 |

| CHAPTER 5 CONCLUSIONS AND FUTURE WORKS                                    | 106 |

| CITED LITERATURE                                                          | 110 |

| APPENDIXES                                                                | 129 |

# LIST OF TABLES

Table 1. Uncertainty analysis for the TBC of Au/Ti/Gr/SiO<sub>2</sub>/Si stack at 85K......94

# LIST OF FIGURES

| Figure 1. CVD Setup                                                                                                      | 21    |

|--------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 2. Optical and SEM characterization images of MoS <sub>2</sub> -Graphene heterostructure                          | 23    |

| Figure 3. AFM Characterization of MoS <sub>2</sub> -Graphene junction                                                    | 24    |

| Figure 4. Raman Characterization of MoS <sub>2</sub> -Graphene junction                                                  | 25    |

| Figure 5. Colorful SEM image of the MoS <sub>2</sub> -Gr and MoS <sub>2</sub> -Metal FET structures                      | 26    |

| Figure 6. Optical image of the cryogenic system                                                                          | 27    |

| Figure 7. Two-probe current-voltage $(I_d-V_{ds})$ characterization at different temperatures.                           | 28    |

| Figure 8. Linear Regression of I <sub>d</sub> -V <sub>sd</sub>                                                           | 29    |

| Figure 9. Two-probe $I_d$ - $V_{ds}$ characterization at different applied gate biases                                   | 30    |

| Figure 10. Two-Probe Electrical Transfer characteristic at different temperatures                                        | 31    |

| Figure 11. Two-Probe Electrical Transfer characteristic at Vg=80V                                                        | 32    |

| Figure 12. Mobility measurements:                                                                                        | 33    |

| Figure 13. Arrhenius characterization for different applied source-drain biases:                                         | 34    |

| Figure 14. Slope of the Arrhenius graph as a function of the $V_{ds}$ at gate bias of 40 V                               | 35    |

| Figure 15. Extracted Schottky barrier height:                                                                            | 36    |

| Figure 16. KPFM measurements:                                                                                            | 37    |

| Figure 17. Noise spectral density measurements                                                                           | 39    |

| Figure 18. Noise amplitude measurements                                                                                  | 43    |

| Figure 19. Breakdown test:                                                                                               | 44    |

| Figure 20. DFT calculations:                                                                                             | 46    |

| Figure 21. Optical and SEM Characterization of the graphene flakes                                                       | 50    |

| Figure 22. Optical characterization of the MoS <sub>2</sub> film next to the graphene flakes                             | 51    |

| Figure 23. KPFM setup:                                                                                                   | 53    |

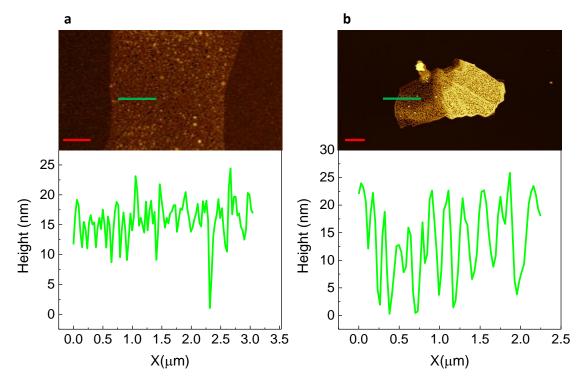

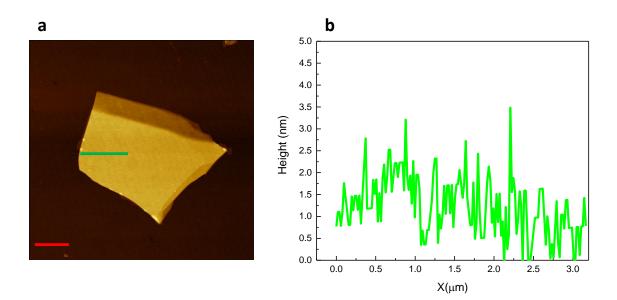

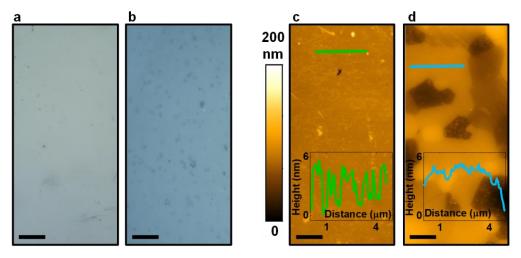

| Figure 24. AFM Characterization                                                                                          | 61    |

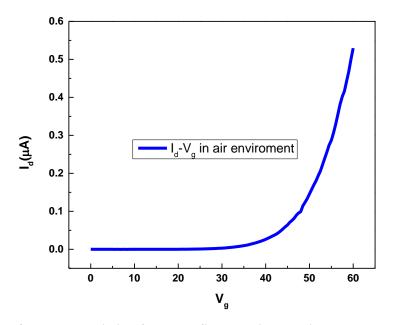

| Figure 25. Optical and electrical characterizations of WSe <sub>2</sub> FET                                              | 64    |

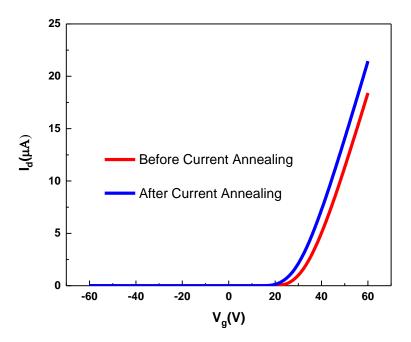

| Figure 26. Transfer characteristic of bare WSe <sub>2</sub> FET in the air                                               | 65    |

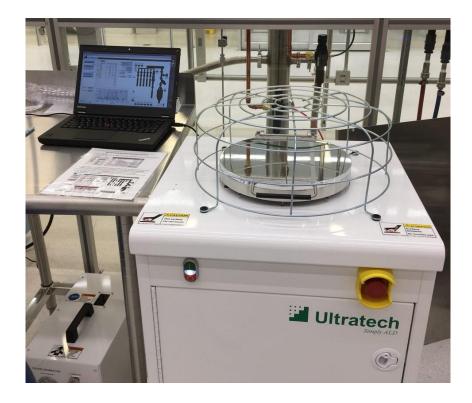

| Figure 27. Savannah standard ALD System:                                                                                 | 66    |

| Figure 28. AFM characteristic of Al <sub>2</sub> O <sub>3</sub> deposited on WSe <sub>2</sub>                            | 67    |

| Figure 29. AFM characteristic of Al <sub>2</sub> O <sub>3</sub> deposited on WSe <sub>2</sub> with 1nm SiOx seeding laye | er 68 |

| Figure 30. Transfer Characteristic of WSe <sub>2</sub> FET in the air environment                                        | 70    |

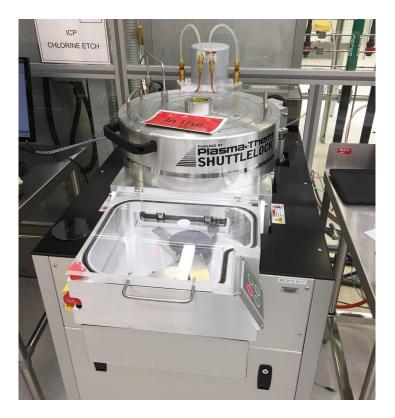

| Figure 31. Plasma-Therm ICP Chlorine Etch System                                                                         | 71    |

| Figure 32. Raman characteristic of WSe <sub>2</sub> flake                                                                | 72    |

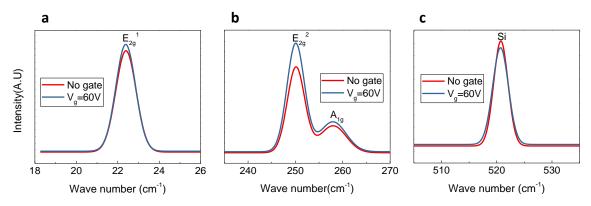

| Figure 33. Raman peak shifts because of applied gate bias                                                                | 73    |

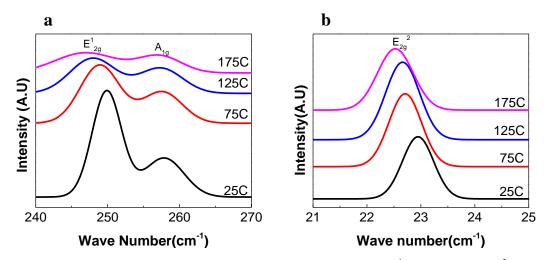

| Figure 34. Raman peak shifts VS temp                                                   | 74  |

|----------------------------------------------------------------------------------------|-----|

| Figure 35. Extracted Raman shift VS temp                                               | 75  |

| Figure 36. Optical image of the Keithley source meter                                  | 76  |

| Figure 37. Applied Power VS temp rise                                                  | 77  |

| Figure 38. Thermal resistances between hot and cold zone                               | 79  |

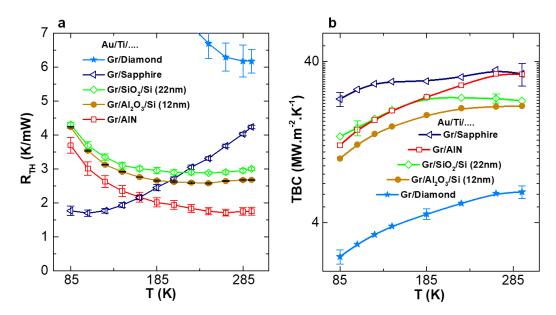

| Figure 39. Characterization of Diamond and AlN Substrates                              | 84  |

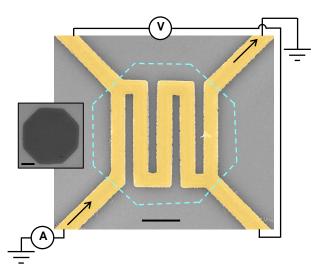

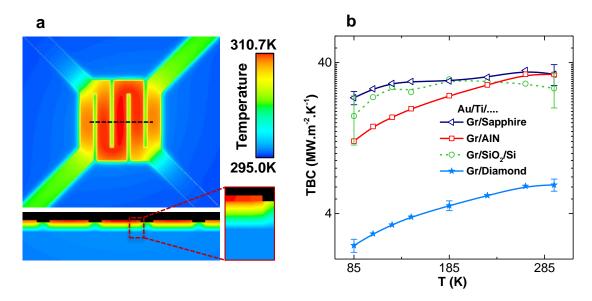

| Figure 40. SEM image of the electrical thermometry platform                            | 85  |

| Figure 41. Thermometry measurements on different substrates                            | 87  |

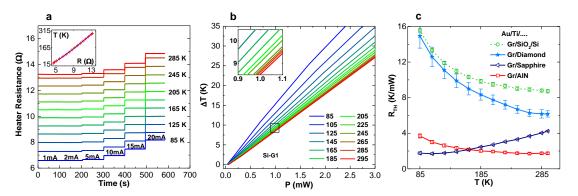

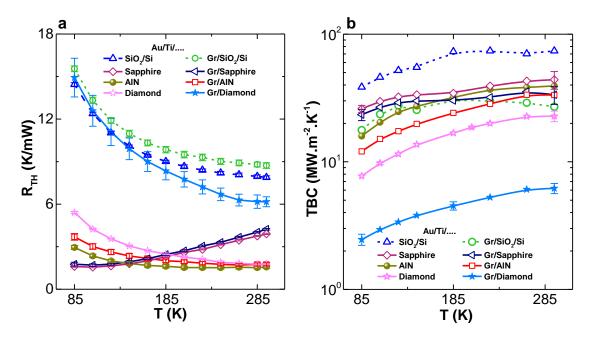

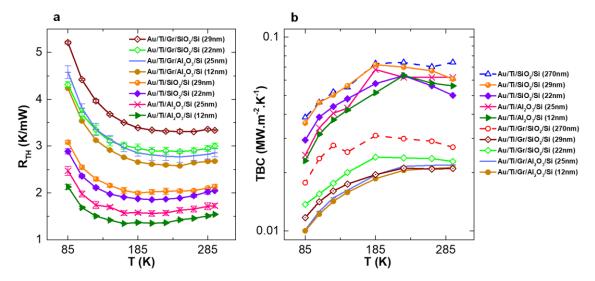

| Figure 42. Experimental data for the Rth and TBC of tested substrates                  | 89  |

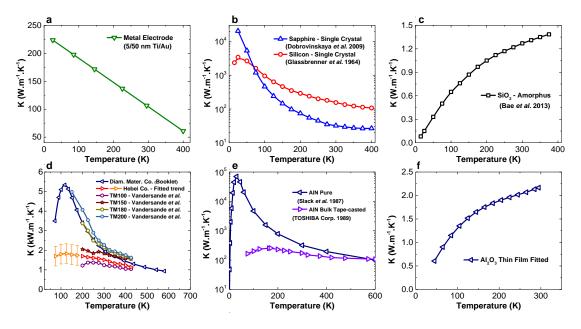

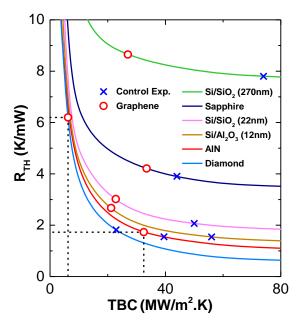

| Figure 43. Thermal conductivities of the materials vs. temperature                     | 91  |

| Figure 44. FE Analysis                                                                 | 93  |

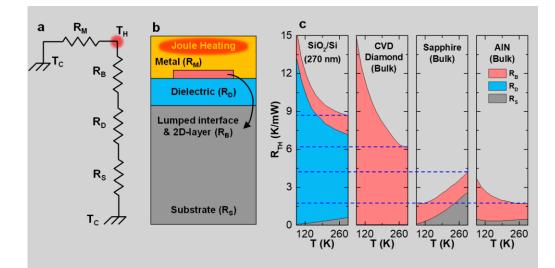

| Figure 45. Thermal circuit analyses for the tested substrates                          | 96  |

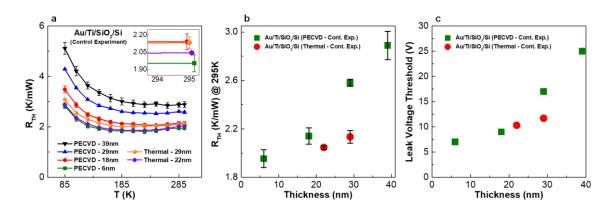

| Figure 46. control experiments for thinner oxide layers:                               | 98  |

| Figure 47. Thermometry measurements of graphene stacks on silicon substrate with       |     |

| different oxide thicknesses:                                                           | 100 |

| Figure 48. The full dataset for the thermometry measurements on silicon substrate with | h   |

| different oxide thicknesses                                                            | 101 |

| Figure 49. Dependence of the R <sub>TH</sub> on the TBC for all the tested structures  | 102 |

# LIST OF ABBREVIATIONS AND NOMENCLATURE

| $\Delta T$                     | temperature rise                                 |

|--------------------------------|--------------------------------------------------|

| 2D                             | two-dimensional                                  |

| 3ω                             | 3-Omega                                          |

| AFM                            | atomic force microscopy                          |

| Al <sub>2</sub> O <sub>3</sub> | aluminum oxide                                   |

| ALD                            | atomic layer deposition                          |

| AlN                            | aluminum nitride                                 |

| AP-CVD                         | atmospheric pressure chemical vapor deposition   |

| Ar                             | argon                                            |

| Au                             | gold                                             |

| BeO                            | beryllium oxide                                  |

| BP                             | black phosphorus                                 |

| BTE                            | Boltzmann transport equation                     |

| CI                             | charged-impurity                                 |

| CLS                            | classical least square                           |

| Cu                             | copper                                           |

| CVD                            | chemical vapor deposition                        |

| DFT                            | density functional theory                        |

| EBL                            | electron beam lithography                        |

| FDTR                           | frequency domain thermoreflectance               |

| FE                             | finite element                                   |

| FET                            | field-effect transistor                          |

| FFT                            | fast Fourier transform                           |

| G/A                            | thermal conductance per unit area                |

| GB                             | grain boundary                                   |

| GNR                            | graphene nano-ribbon                             |

| h-BN                           | hexagonal boron nitride                          |

| HOPG                           | highly ordered pyrolytic graphite                |

| HRTEM                          | high-resolution transmission electron microscopy |

| I <sub>2D</sub>                | intensity of the 2D Raman peak in graphene       |

| Id                             | drain current                                    |

| I <sub>G</sub>                 | intensity of the G Raman peak in graphene        |

| 0                              | r                                                |

| IPA                 | isopropyl alcohol                   |

|---------------------|-------------------------------------|

| IR                  | infra-red                           |

| Κ                   | bulk thermal conductivity           |

| K/mW                | Kelvin per milliwatt                |

| KPFM                | Kelvin probe force microscopy       |

| MD                  | molecular dynamics                  |

| MoO <sub>3</sub>    | molybdenum trioxide                 |

| $MoS_2$             | molybdenum disulfide                |

| NEMD                | non-equilibrium molecular dynamics  |

| rms                 | root mean square                    |

| R <sub>square</sub> | linear regression                   |

| R <sub>TH</sub>     | thermal resistance                  |

| RWM                 | Rayleigh wave mode                  |

| SAED                | selected area electron diffraction  |

| SEM                 | scanning electron microscopy        |

| Si                  | silicon                             |

| SiN                 | silicon nitride                     |

| SiO <sub>2</sub>    | silicon dioxide                     |

| SJEM                | scanning Joule expansion microscopy |

| SO                  | surface optical                     |

| SThM                | scanning thermal microscopy         |

| STM                 | scanning tunneling microscopy       |

| TBC                 | thermal boundary conductance        |

| TBR                 | thermal boundary resistance         |

| TDTR                | time domain thermoreflectance       |

| TEM                 | transmission electron microscopy    |

| Ti                  | titanium                            |

| TMD                 | transition metal dichalcogenides    |

| V <sub>ds</sub>     | drain-source voltage                |

| $V_g$               | gate voltage                        |

| ZA                  | flexural (out-of-plane) acoustic    |

| $\Phi_{\rm B}$      | Schottky barrier height             |

#### **CHAPTER 1**

### **INTRODUCTION**

#### **1.1.** The Importance of Two-Dimensional Materials and their Heterostructures

Since conventional bulk materials have reached their geometrical limitation, miniaturization of the electronic devices has faced a formidable challenge. There are substantial efforts over the last decades to explore new materials as a subsequent of bulk materials for future electronic/optoelectronic devices. Using Two-dimensional (2D) materials, which are one atom thick, as channel and electrodes of the future electronic devices provide the chance of controlling the thickness of these devices at the atomic scale. These materials have shown astonishing electronic, optical and mechanical properties which make them proper candidates for future applications. For instance, it is possible to simply tune their electronic properties by changing the number of their layers[3], [4]. Or their outstanding mechanical bendability makes them applicable for flexible electronic applications[5], [6]. Their ultrahigh optical transparency makes them auspicious for transparent electronic systems[7], [8]. Also, one of the important effects of utilizing these novel materials in ultrathin electronic devices is reducing the issue of the short-channel effect[9].

Rediscovery of the 2D-materials has ignited by the Exfoliation of the graphene, a zero bandgap semiconductor, from bulk graphite at 2004 by the Manchester group[9]– [11]. This material has shown a semi-metallic behavior with high carrier mobility at room temperature, admirable thermal and mechanical properties. However, the absence

of the bandgap in graphene makes it inapplicable for transistor applications. Hence, semiconducting materials like transition metal dichalcogenides (TMDs) are needed to be able to make field effect transistors (FETs), with high current on/off ratio, from 2Dmaterials. These materials have a hexagonal crystal structure consisting of transition metal atoms and chalcogen atoms which have a strong covalent intralayer and weak van der Waals interlayer bonding[12]. Based on the dimension of the metal atom and chalcogen atom, the bonding length between these atoms is from 3.15  $A^{\circ}$  to 4.03  $A^{\circ}$  and the TMDs single layer thickness is around 6 to 7 A°[13], [14]. One of their astonishing advantages is the ability of tuning their bandgap by changing the number of their layers, making different compositions between transition metal atoms and chalcogen atoms as well as applying mechanical strain to them[9], [15], [16]. To build all 2D circuitries, it is also needed to have insulating materials like hexagonal boron nitride (h-BN) which can be used as a gate dielectric for nanoelectronics devices. Therefore, 2D-materials will cover a wide range of material types from insulators with large bandgaps to metals[15]-[20] which are very promising for future industry.

As it is mentioned in previous paragraphs, 2D-materials have wide variety of properties and they behave notably different from each other. Each of these materials has some disadvantages which could limit the performance of its device. For example, Molybdenum disulfide (MoS<sub>2</sub>) which is a famous member of the TMDs, has shown high on/off ratio making it a promising candidate to be used as a channel of the transistor in future devices. However, it has also shown that there is a Schottky barrier formation at its

interface with metal electrodes downgrading its performance significantly[21]. Or some of the 2D-materials like WTe<sub>2</sub> are instable at ambient conditions[22] and they need to be combined with other 2D-materials to be applicable for the industry applications. Thus, making the heterostructures of 2D-materials will open a plenty of opportunities to combine the advantage of each 2D-material together and eliminate its disadvantages. These heterostructures can be made by stacking or growing the 2D-materials on top of each other or next to each other. For instances, stacking a layer of graphene on top of h-BN substrate results in almost an order of magnitude higher mobility, less doping and enhanced chemical stability due to almost absence of the charge trappings at the surface of the h-BN and its atomically flat surface [23], [24]. Also in another work, Behranginia et al. have grown three dimensional(3D)  $MoS_2$  on top of the graphene films and demonstrated that the charge transferred to 3D structured MoS<sub>2</sub> grown on top of the graphene film has improved significantly compared to 3D structured MoS<sub>2</sub> grown on top of the bare glassy carbon substrate[25]. In addition, there has been a huge demand in recent years for flexible electronic devices and manufacturing all-2D circuitries can make it possible to achieve this dream. For example, Lee et al. [26] fabricated a flexible and transparent FET by stacking 2D-materials on top of 127 µm thick polyethylene naphthalate (PEN) substrate. In this work, MoS<sub>2</sub>, h-BN and graphene materials have been used as a channel of the transistor, gate dielectric and gate electrode respectively. This vertical heterostructure has been made by mechanical stacking method and its performance has not changed up to 1.5 % induced strain. They could achieve a high

mobility of 29 cm<sup>2</sup>/V.S and operating gate voltage of 5V before bending the device. In another work, Das et al. [27] have made all-2D WSe<sub>2</sub> transistor on top of the flexible polyethylene terephthalate (PET) substrate with the mobility of 45 cm<sup>2</sup>/V.S and current on/off ratio of  $10^7$ . In this work, WSe<sub>2</sub> and h-BN have been used as a transistor channel and gate dielectric respectively. Also, graphene material has been used as both gate electrode and source-drain electrode. The device performance did not change up to 2% applied strain and it was remarkably stable over wide range of temperature from 77 K to 400 K.

### **1.2.Preparation of 2D-materials and their heterostructures**

There are different methods to make 2D-materials. Mechanical exfoliation method is the first method which has been used for fundamental studies about physical and chemical properties of these materials. In this method 2D-materials exfoliates from their bulk crystals by using scotch tapes[10]. The yields of this method to achieve large single layer flakes are low, but the flakes exfoliated by this method are pristine and almost free of defects. So, due to inapplicability of this method for mass production, other methods like chemical exfoliation and chemical vapor deposition (CVD) techniques have been used to produce single and few-layer of 2D-Materials for large-scale production. To chemically exfoliate 2D-materials, scientists have used different approaches like electrochemical exfoliation[28], [29] and liquid exfoliation techniques[30], [31]. These various approaches can produce 2D nanosheets with different qualities from almost defect free nanosheets to completely degraded nanoflakes[32]. These methods of 2D- material production could be very cost-effective and simple. For example, Varrla et al.[33] have used Kitchen blender and household detergent to produce high quality graphene flakes. Also, preparing 2D-materials via chemical exfoliation technique brings the opportunity of making 2D-material inks for low-cost printed electronic circuits[34]. However, controlling the uniformity, lateral size and thickness of the flakes produced by these approaches are very challenging[23]. Till now, different techniques have been used by scientists for in situ measurement of the thickness and size of the 2D-material-nanosheets dispersed in the solution to have a better control on the uniformity of the exfoliated flakes[32], [35], [36]. There are an extensive range of liquids which can be used for chemical exfoliation of 2D-matrials resulting in having 2D materials with wide range of lateral sizes from 100 nm to 100  $\mu$ m and thicknesses from monolayer to few layers. The dispersed liquid could be quite stable and have variety range of concentrations[32].

CVD method is another technique for large-scale production of 2D-Materials. Generally, there are two different approaches for the growth of the 2D-matrials by CVD technique. In the first approach, a thin layer of the metal atom will be deposited on top of the substrate by the means of metal evaporation technique or sputtering one. Then, the chalcogen atom will react with the deposited layer at elevated temperatures. Zhan et al. and Kong et al. were the scientists who used this approach to synthesize atomically thin  $MoS_2$  film and vertically aligned  $MoS_2$  layers respectively[37], [38]. Reaching uniform layers with very thin thicknesses is one of the difficult challenges of this approach[14].

The second approach is the reaction of the metal atom with the chalcogen atom at the vapor phase at elevated temperatures. Basically, in this method, people use a noble gas as a carrier gas inside the CVD chamber and a metal oxide source and a chalcogen precursor is used as the sources of the metal and chalcogen atom for the reaction respectively. Some scientists also used hydrogen gas as an reducing agent for the growth of the TMDs too [39], [40]. The temperature of the growth is from 500  $^\circ C$  to ~ 1000  $^\circ C$ depends on the melting temperature of the metal oxide precursor and the quality of the crystallinity of the grown material which is needed for that specific application. The growth could be done in both atmospheric pressure and low pressure. It was at 2012 and 2013 that different groups have started to grow CVD MoS<sub>2</sub> flakes by sulfurization of the MoO<sub>3</sub> precursor at high temperatures[38], [41], [42]. It is possible to grow single layer  $MoS_2$  flakes on arbitrary substrates by using this approach and substrate treatment is one of the key factors in the growth of the TMDs by this method. For instance, performing an oxygen plasma treatment on the  $SiO_2$  substrate, making it a hydrophilic substrate, before the growth will result in the growth of the MoS<sub>2</sub> flakes with larger flake sizes and better uniformity on top of the  $SiO_2$  substrate[1]. There are many reports on the growth of the different TMDs by CVD approach[25], [40], [43]–[49] which shows that it is an auspicious approach for the large scale production of TMDs. For example, Eichfeld et al. [50] have reported the first scalable synthesis method of mono and few-layer WSe<sub>2</sub> material via metal-organic CVD method. In this work, they have used tungsten hexacarbonyl (W(CO)6) as a source of the tungsten material and dimethylselenium

((CH3)2Se) as a source of the selenium material and the growth happened at a wide range of temperatures from 600 °C to 900 °C. A mixture of the hydrogen and nitrogen gas has been used as a carrier gas and the reaction happened in a vertical cold-wall reactor system. The WSe<sub>2</sub> material has been grown on top of the four different substrates including epitaxial graphene, CVD graphene, sapphire and amorphous boron nitride and the results of the growth were distinct for all these substrates from the point of the morphologies and thicknesses of the grown WSe<sub>2</sub> material. They could have achieved lateral size of 5-8 µm for WSe<sub>2</sub> flakes grown on top of the sapphire substrate. Or on the other work by Kang et al.[51], wafer scale multilayer films of MoS<sub>2</sub> and tungsten sulfide  $(WS_2)$  material have been grown directly on top of the SiO<sub>2</sub> substrate with the excellent uniformity over the entire film. They have used Molybdenum hexacarbonyl (MHC), tungsten hexacarbonyl (THC) and diethyl sulphide (DES) as a source of molybdenum, tungsten and sulfur respectively. These precursors purged into the reaction tube in a gasphase condition. H<sub>2</sub> and Ar gases have also been used as carrier gases during the growth procedure and the growth time and temperature were 26 hr and 550 °C respectively. They could have achieved to the high mobility of 30  $\text{cm}^2/\text{V.S}$  for the grown MoS<sub>2</sub> film with 99% device yield.

#### 1.3. Potential application of 2D-materials and their heterostructures

The unique properties of 2D-materials and their heterostructures such as transparency, mechanical flexibility, high surface to volume ratio and high electrical and thermal conductivity make them good candidates for wide variety of applications. Field effect transistors, light emitting diodes, transparent electronics devices, sensors, and energy conversion/storage systems are the devices [23], [34], [52], [53] which can be revolutionized by 2D-materials and their heterostructures. Some of these applications for 2D-materials are briefly discussed in the following subsections.

#### **1.3.1. Field effect transistors**

Graphene was one of the first 2D-material which was used for transistor application due to its high carrier mobility. However, future FETs needs the on/off ratio of larger than  $10^{4}$ [9] and the absence of the band gap in graphene results in having very low on/off current ratio and large off current. Scientists have tried to improve this disadvantage by using bilayer graphene[54], [55], graphene nanoribbons[56] and nanostructures[57], but it results in lowering the mobility of graphene [58]. Therefore, scientists tried to use other 2D-materials like TMDCs which mostly have a band gap between 1-2 eV. These materials have low off currents resulting in lowering the power consumption when the system is in the standby mode [9].  $MoS_2$  was one of the 2D-materials which has been used as the channel of the transistor and shows high on/off ratio[42]. However, due to the Schottky barrier formation at the metal electrode junction, it shows lower extrinsic mobility value than the theoretically estimated one[9]. Das et al. [59] have shown the formation of the Schottky barrier at the interface of the MoS<sub>2</sub> with four different low work function metals. In this study, scandium has shown the lowest Schottky barrier height (30 meV) and platinum has shown the highest Schottky barrier height (230 meV) at its interface with MoS<sub>2</sub>. They claim that fermi level pining has a strong impact on the

interface of the metal and MoS<sub>2</sub>. Hence to reduce the Schottky barrier height at the interface of the 2D-materials with metals, have high on/off ratio and high mobility, scientist have tried to develop in-plane and vertical heterostructures of 2D-materials. One of the ideas was to open a band gap in graphene by making a vertical heterostructure of GR/hBN/GR or Gr/MoS<sub>2</sub>/GR which was developed by Britnell et al.[60]. The on/off ratio of this tunneling transistor at room temperature was almost an order of magnitude larger than previous graphene FETs[61]-[65], but still it was not enough for future applications. Then, Georgiou et.al.[66] came up with the idea of using WSe<sub>2</sub> as a barrier instead of hBN material for vertical graphene heterostructure. This heterostructure could switche between tunneling and thermionic transport behavior and shows high on/off ratio  $(\sim 10^6)$ [58]. Roy et al. [58] reported all-2D FET in which the graphene is utilized as source/drain as well as top gate electrodes, hBN as the gate dielectric and MoS<sub>2</sub> as a channel of the transistor. This heterostructure shows the on/off ratio of  $>10^6$  and the mobility of 33 cm<sup>2</sup>V<sup>-1</sup>S<sup>-1</sup>. Also, Behranginia et al. [1] have reported in-plane heterostructure of GR/MoS<sub>2</sub> for future transistor applications. This heterostructure shows higher mobility and lower noise metric compared to metal/MoS<sub>2</sub> transistors.

#### **1.3.2.** Optoelectronic Devices

Photoresponsivity and light absorption are the critical parameters for optoelectronic devices. Combination of the TMDC materials, which have direct band gap and high absorption coefficient, with graphene, which has high mobility, can provide fast response time and strong light absorption for the optoelectronic devices which are made out of the

Gr/TMDCs heterostructures[23], [58]. Zhang et al.[67] reported a photogain larger than  $10^8$  by stacking a layer of graphene on top of the layer of MoS<sub>2</sub>. In this vertical heterostructure, in contradiction to the conventional metal/MoS<sub>2</sub> contact, the excited photoelectrons in the MoS<sub>2</sub> layer are injected to the graphene layer rather than trapping into the MoS<sub>2</sub> layer in the presence of the perpendicular electric field across the heterostructure [67]. Also, sandwiching a  $WS_2$  material, as a light absorber, between two graphene layers, as a carrier separators, results in achieving the photoresponsivity of 0.1 AW<sup>-1</sup> and quantum efficiency of above 30%[68]. The optoelectronic devices can also be made from p-n junctions. Lee et al.[69] reported the electronic and optoelectronic characteristic of the p-type WSe<sub>2</sub> and n-type MoS<sub>2</sub> vertical heterostructure. Their results exhibit diode-like current rectification behavior and photovoltaic response across WSe<sub>2</sub>/MoS<sub>2</sub> junction. Their calculated diffusion time for the majority carriers to leave the junction was ~1µs resulting in almost high interlayer recombination losses. To improve this diffusion time, they have sandwiched the junction between two graphene electrodes to directly collect the charge carriers in the vertical direction resulting in increasing the collection rate of the charge carriers generated by the light absorption.

#### **1.3.3. Sensor Devices**

2D-materials have been used for different sensor applications such as humidity sensors[70], biosensors[71], [72] and etc. due to their high sensitivity and large surface to volume ratio[23]. Yasaei et al. have reported ultrahigh sensitivity of the black phosphorus(BP) film to the humidity. They have coated the BP nanoflakes in the form of

stacked films on top of the hydrophilic polytetrafluoroethylene (PTFE) filter papers and their results shows almost 4 orders of magnitude change in the drain current by changing the relative humidity from 10% to 85%. They have explored that the modulation in the leakage ionic current is the operation principle of their sensors. MoS<sub>2</sub> is the other 2Dmaterial which has been used for DNA detection, but due to its sensitivity to moisture and oxygen its application is restricted for aqueous solution. To overcome this challenge, Loan et al. [73] stacked a layer of graphene on top of the MoS<sub>2</sub> layer providing ultrasensitive structure for detection of the DNA hybridization. Stacking graphene layer on top of the MoS<sub>2</sub> layer brought two benefits for this sensor. First, biocompatibility of the graphene with DNA makes graphene a suitable host for the DNA[73]. Second, the presence of the graphene on top of the MoS<sub>2</sub> layers results in protecting the MoS<sub>2</sub> layer from the moisture[23].

#### **1.4.** Thermal transport of 2D-materials

Due to the small size of the 2D-material electronic devices, these devices can suffer from sophisticated thermal challenges which could significantly limit their practical applications[74], [75]. The temperature distribution in these devices can be significantly non-uniform across the channel of the transistor resulting in creating hot spots with temperatures noticeably higher than the average temperature of the channel[75], [76]. Without having a considerable progress in electronic circuit cooling technology, the power density of the new electronic devices could reach the level resulting in unreliable operation of these devices. This phenomena makes the thermal management of the

individual nanoscale-transistors a formidable challenge for future device designers[76]. Higher operation temperature of thin-film transistors with the channel thicknesses lower than phonon mean free path could also reduce the efficiency of these devices significantly. This phenomena is due to the phonon confinement and boundary scattering which results in increasing the thermal resistance of these devices[76]. Electron-phonon scattering is the main scattering mechanism which results in the heating of this devices. In more detail, absorbing the energy of the electron by lattice results in increasing the temperature of these devices and affecting the electron mobility of them[76].Hence, complete understanding of the thermal properties of 2D-materials and their interfaces is needed to be able to design and fabricate 2D-material deices with higher efficiency and better performances. Various thermal measurement techniques such as  $3\omega$ [77], timedomain thermoreflectance (TDTR)[52], suspended micro-bridge[78] and optothermal Raman[79] methods have been developed during passed decades to investigate thermophysical properties of 2D-material devices. The first two methods are appropriate for cross-plane thermal transport measurement and the last two ones are developed for intrinsic in-plane thermal transport measurement[74].

Basically, in  $3\omega$  method the material will be suspended with four electrical contacts. The Ac current with  $1\omega$  angular frequency will apply between the two farthest electrodes and the voltage drop will be measured between the two closest ones. Applying  $1\omega$ sinusoidal current will results in temperature variation at  $2\omega$  frequency and voltage drop with a  $3\omega$  component. Finally, thermal conductivity and thermal time constant can be calculated based on the measured voltage drop. The specific heat and diffusivity of the material can also be measured by this method[80].

TDTR technique is based on measuring the thermoreflected signals from the material as a result of the localized temperature increase. Generally, in this technique, the material will be heated by the pulse laser which results in increasing the temperature of the material locally and inducing the thermal stress to the sample. The acoustic strain pulses will be generated because of this thermal stress. Finally, the thermoreflected signals will be measured by photodiode and will be amplified by a RF lock-in amplifier. Then, the thermal conductivity of the material will be extracted from the ratio of the in phase and out of phase of the lock in amplifier signal[80]–[82].

The micro-bridge method has been used by many scientists to measure thermal conductivity and seebeck coefficient of the different materials including 2D-materials[83]–[89]. Basically, in this method, heater and sensor electrodes are fabricated on top of the silicon nitride membrane and the desire material is suspended between the heater and sensor. So, the huge part of the generated heat at the heater is conducted to the sensor electrodes through the suspended material by joule heating mechanism. And finally, the heat will be dissipated through the silicon nitride beams to the heat sinks. By knowing the amount of the generated heat at the heater and measuring the temperature of the two ends of the sample ( $T_{hot}$  and  $T_{cold}$ ), it is possible to measure the thermal conductivity of the desired material. To perform this measurement, the sample will be loaded inside the vacuum chamber to be able to ignore the heat transfer through the

convention and radiation. Transferring the desired material to this platform and sophisticated fabrication process are the challenges which limit the implication of this method for thermal measurements. There are two methods to transfer the low dimensional materials to this platform. The first is using the sharp tip to pick up the material and transfer it to the platform which has been found very challenging for the materials with the thicknesses less than the 50 nm[74], [87]. Another method is to use the polymer-assisted transfer process which could leave the residue on the sample resulting in changing its thermal properties [90] and damaging the device. Also, having a correct evaluation of the interface thermal resistance between 2D-materials and silicon nitride membrane is another challenge of this method to extract the correct value of the thermal conductivity of the 2D-material[74]. Shi et al.[78] were the first group who used this technique to measure the thermal conductivity of the carbon nanotube (CNT) material. They deposited platinum electrodes as a heater and sensor on top of the silicon nitride membrane. They have used two different methods to transfer their material on top of the platform. In the first one, they spun the solution containing the CNT material on the substrate with many suspended structures and then anneal the device at 300 °C to improve the contact between the platinum electrode and the deposited material. In the second one, they spun coat the solution containing the precursors for the CVD growth of the CNT material and then placed the substrate into the CVD furnace. They used the methane gas as the source of the carbon material and the temperature of the growth was 900 °C. Their measurements reveal that the thermal conductivity of the single-wall CNT

is lower than individual multi-wall CNT which could be due to the scatterings at the defects. Lee et al. [91] also used the same method to measure the thermal conductivity of the few layer black phosphorus. They have shown that there is a large anisotropy in the thermal conductivity of the black phosphorus nanoribbons and their thermal conductivity reduces by decreasing the thickness of the nanoribbons. Temperature and thickness dependent thermoelectric properties of bismuth telluride (Bi<sub>2</sub>Te<sub>3</sub>) is also investigated by Pettes et al. [86] by using the micro-bridge platform. Their results exhibit that the seebeck coefficient of Bi<sub>2</sub>Te<sub>3</sub> will significantly reduce by decreasing the thickness of this material.

Optothermal Raman technique is another approach with simple sample fabrication and measurement process for investigation of the thermal properties of 2D-materials. This method has been used by many groups during the past decades[4], [34], [79]. By using this method, it is possible to measure the thermal conductivity of 2D-materials and the temperature of their devices under the operation at different applied powers. Basically, in this method, the fabricated sample will be placed on the stage which has the temperature control and can heat/cool the device in a wide range of temperatures. Then, the temperature coefficient of the Raman peaks of the material will be extracted by acquiring Raman spectra of the sample at various temperatures. To find out the thermal conductivity of the sample, the laser light with a desirable wavelength will be focused on the middle of the 2D-material, which is suspended over a trench, to heat the device. Next, the generated heat will be dissipated through the 2D-material to the heat sinks. Finally,

the thermal conductivity of the sample can be calculated by knowing the laser power, thickness of the sample and temperature gradient of the sample. Inaccuracy in measuring the absorbed laser power and the Raman peak shift are the challenges of this measurement method. Also, this method is not applicable for the 2D-materials which have Raman peaks with weak intensity and temperature independency[74]. This method was used by Balandin et al.[79] to measure the thermal conductivity of the suspended graphene for the first time. They extracted the temperature coefficient of the G Raman peak of the graphene and heated the graphene by using the 488 nm wavelength laser. Faugeras et al.[92] were another group which measured the thermal conductivity of the graphene by Raman thermometry technique. They have reported the thermal conductivity of the 630  $Wm^{-1}K^{-1}$  for graphene which was lower than 5300  $Wm^{-1}K^{-1}$  value reported by Balandin et al[79]. The reason that Faugeras reported lower value than Balandin was that they considered lower value for the absorption of the laser power by graphene based on the latest results on the transmission and reflectivity of the graphene. It is also worth mentioning that, Faugeras used the ratio of the stokes to anti-stokes Raman signal instead of considering the Raman peak shift at different temperatures. There were also other reports on the thermal conductivity of the graphene ranging from 600  $Wm^{-1}K^{-1}$  to 2500 Wm<sup>-1</sup>K<sup>-1</sup> [93]–[95]. Pop et al.[96] also use Raman thermometry technique to investigate the energy dissipation of  $MoS_2$  transistors under the operation. They used both CVD MoS<sub>2</sub> and mechanically exfoliated MoS<sub>2</sub> as a channel of the transistor for this measurement. Their study revealed that the average temperature rises for both Mechanically exfoliated and CVD grown MoS<sub>2</sub> is almost the same resulting in showing the same behavior in energy dissipation. Their temperature mapping measurements also shows that the nonuniformity in the MoS<sub>2</sub> layer would not cause significant self-heating in the small bilayer region. Their measurement also disclosed that the thermal boundary conductance between MoS<sub>2</sub> layer and its SiO<sub>2</sub> substrate is an order of magnitude larger than previously reported values[97]–[99]. On the other work, Engel et al. [100] used the anti-stokes-to stokes Raman peak intensity ratio to measure the temperature rise of the 50 nm black phosphorus transistor under the applied bias. Their measurement shows the breakdown temperature of the 757 K for this material.

### **CHAPTER 2**

#### Direct Growth of High Mobility and Low Noise Lateral MoS2-Graphene

#### **Heterostructure Electronics**

(Most parts of this chapter are taken from the published paper with the following citation:

Amirhossein Behranginia, Poya Yasaei, Arnab K. Majee, Vinod K. Sangwan, Fei Long, Cameron J. Foss, Tara Foroozan, Shadi Fuladi, Mohammad Reza Hantehzadeh, Reza Shahbazian-Yassar, Mark C. Hersam, Zlatan Aksamija, Amin Salehi-Khojin "Direct Growth of High Mobility and Low Noise Lateral MoS<sub>2</sub>-Graphene Heterostructure Electronics" Small, 2017.

Please refer to the authors' contributions in page iv in the beginning of this document for details of the contributions)

#### **2.1. Introduction**

According to Moore's law, the transistor count per chip doubles every two years[101]. The continuing shrinkage in size is pushing the silicon-based industry toward its physical limitations. Numerous efforts are now being dedicated to the development of two-dimensional (2D) materials for future electronic/optoelectronic devices[20], [31], [39], [102]–[105]. Transition metal dichalcogenides (TMDs) are a family of layered crystals that are opening the possibility of developing systems with reduced dimensionality and a range of unique properties[105]. The most abundant member of this family is molybdenum disulfide (MoS2), which shows interesting semiconducting properties[106], [107] that make it a promising candidate for digital electronic circuitry applications. On the downside, the electrical performance of MoS2 field-effect transistors

(FETs) has been limited by the performance of the MoS2 junction with the metal contact electrodes[21]. In particular, due to Fermi level pinning, nearly all metals form a Schottky barrier upon contact with MoS2, which results in large contact resistances on the extrinsic (2-probe) performance of MoS2-based devices[21]. Additionally, metals do not possess sufficient mechanical bendability for use in flexible structures. Thus, significant research has been invested in finding a replacement for conventional metal electrodes that will allow the fabrication of intrinsically 2D devices with improved device metrics [108]–[113]. Du et al. [114] have been fabricated the first Gr/Metal heterocontact MoS<sub>2</sub> FET to improve the electron coupling between the metal and MoS<sub>2</sub>. In this work, mechanically exfoliated MoS<sub>2</sub> has been used as the channel of the transistor and monolayer graphene is transferred on top of the  $MoS_2$  layer before deposition of the source and drain metal electrodes. They have measured the extrinsic field effect mobility of 32.3 cm<sup>2</sup>/V.S and on/off current ratio of 10<sup>7</sup> for this hetero-contact device. Their contact resistance has improved significantly (3.3 times) compared to conventional metal/MoS<sub>2</sub> FET. They claimed that this improvement is because of the gate-enhanced electron injection from graphene into the conduction band of the MoS<sub>2</sub>.

In this section, I present the seed-free consecutive CVD processes to synthesize lateral MoS2-graphene interfaces with large crystal domain sizes and high interface quality. Device-level experiments reveal that the extrinsic mobility of MoS2-graphene FETs is improved by an order of magnitude compared with the MoS2-metal FETs because of energy band rearrangement and smaller Schottky barrier height at the

contacts, especially in the accumulation region (large positive gate voltages). For direct verification of the device-level measurements and to gain more insight into the role of the interface on the overall resistance of the device, Kelvin probe force microscopy (KPFM) is employed to map the surface potential distribution of a biased MoS2-graphene heterojunction under applied gate potentials. Low frequency 1/f noise metrics of the MoS2-graphene FETs are also extensively studied in both subthreshold and accumulation regions to identify the origins of signal fluctuations in lateral MoS2-graphene devices. The results show that the mobility fluctuations are the dominant origin of the noise in the accumulation region, while the overall noise amplitude is an order of magnitude lower than MoS2-metal FETs. Additionally, electrostatic breakdown measurements are performed on both MoS2-graphene and MoS2-metal devices to study the failure modes of the devices under high-power operation. To gain insight into the physics of the observed improvements, the interfacial resistance is modeled using a combination of first-principles band structure calculations, followed by calculation of the transmission coefficient and interfacial conductance in the Landauer formalism. Overall, this work establishes the superlative electronic properties of directly grown MoS2-graphene lateral heterostructures.

#### **2.2. RESULTS and DISCUSSION**

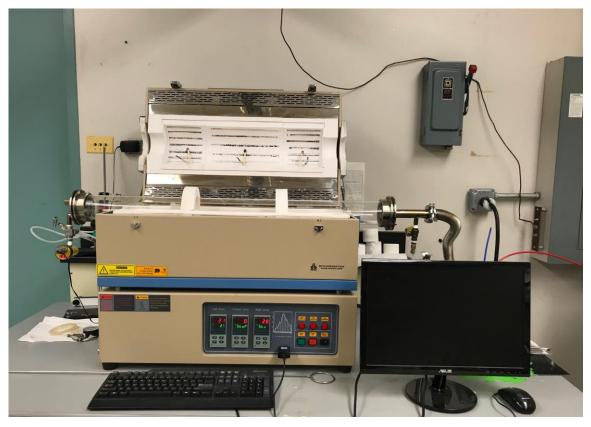

In our method, a graphene film with partial (or full) coverage is initially synthesized on a copper substrate in an atmospheric pressure chemical vapor deposition (AP-CVD) process and then transferred to a silicon (SiO<sub>2</sub>/Si) substrate, similar to our previous reports[115], [116]. Figure 1 shows our CVD setup for the growth of the graphene and MoS<sub>2</sub> material.

**Figure 1. CVD Setup:** three zones CVD furnace which is used for the growth of the graphene and MoS<sub>2</sub> materials.

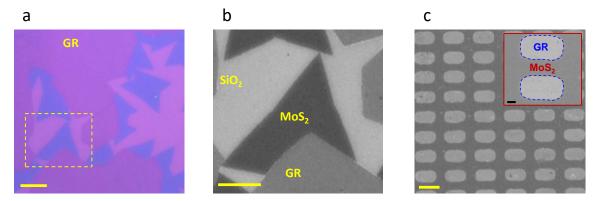

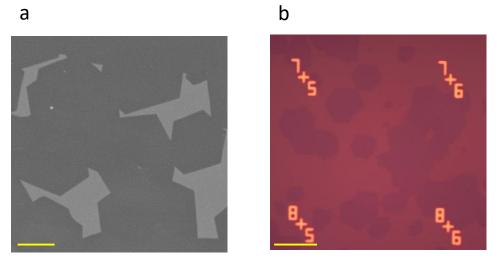

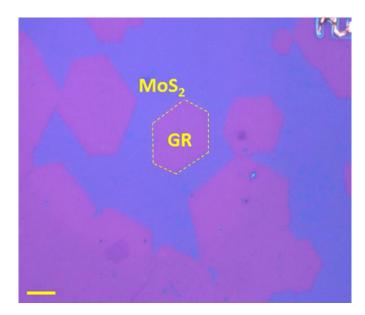

The samples are then transferred to another AP-CVD chamber to synthesize  $MoS_2$ through the reaction of sulfur and molybdenum trioxide (MoO<sub>3</sub>) precursors. **Figure 2a-b** shows the CVD-grown  $MoS_2$  triangular single crystalline flakes making a lateral junction with graphene domains. We note that even without any specific surface treatment (e.g., use of seed promoters), the growth of  $MoS_2$  is more favorable on a bare oxide substrate compared to graphene films. This observation may be explained by the relative scarcity of nucleation sites on graphene compared to SiO<sub>2</sub>. The preferential deposition on SiO<sub>2</sub> causes the growth of MoS<sub>2</sub> to stop right at the edge of the graphene film, resulting in a lateral (in-plane) heterojunction. We note that due to the lattice mismatch between graphene and MoS<sub>2</sub>, an atomically sharp interface is not likely to form, but due to the self-limiting growth process (deposition selectivity), the overlapped region remains quite small (2 to 30 nm) [117]. Next, to investigate the scalability of this method, we have increased the growth time of the graphene flakes to grow a continuous graphene film on top of the cupper substrate. Then, uniform grown graphene film was transferred to the SiO<sub>2</sub> substrate by PMMA assisted transfer method. The graphene film is patterned to small squares by using photolithography process and the unwanted areas are etched a way by using 5 minutes oxygen plasma. Finally, the patterned graphene films are loaded into the MoS<sub>2</sub> CVD furnace to grow uniform films of MoS<sub>2</sub> on the bare area of SiO<sub>2</sub> substrate. We found that a uniform MoS<sub>2</sub> film can fill arbitrary-shaped patterns in the graphene films and form lateral interfaces (Figure 2c). This process shows that it is possible to grow MoS<sub>2</sub>-graphene in-plane heterostructures in large scales for future industry applications.

Figure 2. Optical and SEM characterization images of  $MoS_2$ -Graphene heterostructure: (a) Optical image of the partially covered  $MoS_2$  triangular flakes next to the graphene flakes (scale bar 10 µm). (b) SEM image of the  $MoS_2$ -graphene in-plane heterostructure from the selected area in (a) (scale bar 5 µm). (c) SEM image of a large scale patterned  $MoS_2$ -graphene in-plane heterostructure (scale bar 10 µm) the inset magnifies the same image (Scale bar in inset 2 µm).

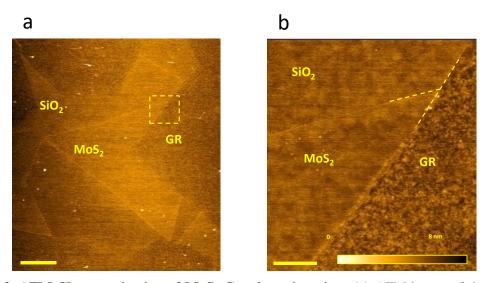

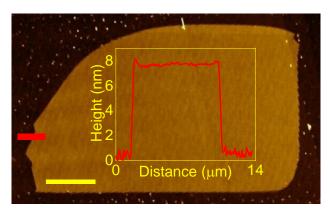

Atomic force microscopy (AFM) characterization (Figure 3) also shows an overlapped region between  $MoS_2$  and graphene domains which is smaller than 30 nm over the entire interface length.

**Figure 3. AFM Characterization of MoS<sub>2</sub>-Graphene junction:** (a) AFM image of the MoS<sub>2</sub>-graphene in-plane heterostructure. (b) Higher magnification AFM image of the MoS<sub>2</sub>-graphene interface.

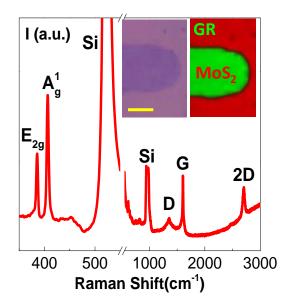

Raman point spectroscopy on a patterned MoS<sub>2</sub>-graphene interface shows the characteristic peaks of MoS<sub>2</sub> and graphene next to the silicon peaks from the substrate (Figure 4).  $E_g^2$  and  $A_g^1$  peaks are the in-plane and out-of-plane Raman representative peaks of MoS<sub>2</sub> respectively and the G peak and 2D peaks are the Raman representative peaks of graphene. The inset of Figure 4 shows the spatial distributions of the graphene and MoS<sub>2</sub> Raman peaks, which reveal the formation of a lateral interface without a noticeable gap or overlap. The classical least-square (CLS) fitting was used to analyze the obtained hyper-spectra, including the  $E_g^2$  and  $A_g^1$  peaks of the MoS<sub>2</sub> (coded as green in Figure 4) and the G peak of the graphene (coded as red).

Figure 4. Raman Characterization of  $MoS_2$ -Graphene junction: A representative Raman point spectrum from the  $MoS_2$ -graphene interface area. The inset shows optical image and Raman mapping of a patterned  $MoS_2$ -graphene heterostructure. The scale bar is 2  $\mu$ m.

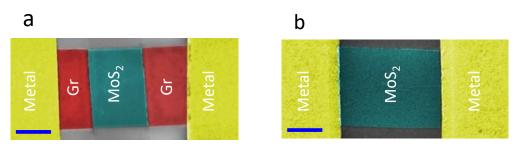

To make MoS<sub>2</sub>-Gr and MoS<sub>2</sub>-metal field-effect transistors (FETs), We first transferred the MoS<sub>2</sub>-Gr heterostructure and MoS<sub>2</sub>-metal structure from the grown substrate to the new SiO<sub>2</sub>/Si substrate. For this process, we coated a Poly (methyl methacrylate) (PMMA) layer on top of the substrate and let it dry in the air for four hours. Then, we floated the coated substrate on the diluted Potassium hydroxide (KOH) etchant till the PMMA layer detach from the old substrate. The detached layer floated on top of two bath of water for four hours and then transferred to new SiO<sub>2</sub>/Si substrate. The reason of transferring the structures from the old substrate to the new one is the leakage of the gate oxide due to the reaction of the sulfur with SiO<sub>2</sub> layer during the growth process. Next, the transferred structures are etched to the desire shape by electron-beam

lithography (EBL) process followed by oxygen plasma etching. Finally, the metal electrodes deposited by metal evaporation process after patterning the electrodes by EBL process (Figure 5a-b).

Figure 5. Colorful SEM image of the MoS<sub>2</sub>-Gr and MoS<sub>2</sub>-Metal FET structures: (a-b) SEM images of the MoS<sub>2</sub>-graphene and MoS<sub>2</sub>-metal FETs, respectively (scale bars 2  $\mu$ m and 1  $\mu$ m, respectively).

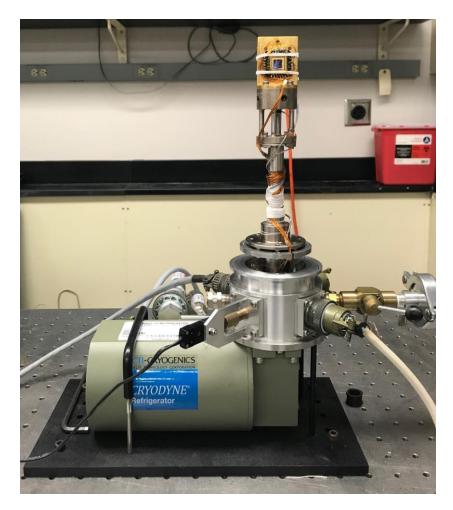

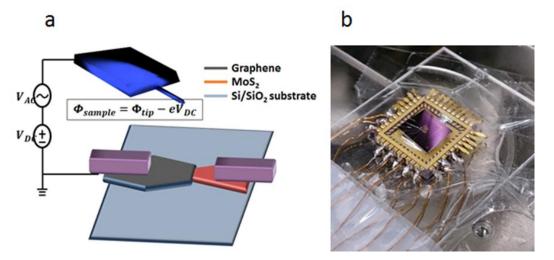

An optical cryogenic refrigerator (from Janis, model: CCS-450) was used to carry out our electrical measurements at different temperatures (Figure 6). The operation temperature range of the system is from 10 K to 500 K and a closed loop Helium compressor is used to bring down the temperature of the device to the lower temperatures. The temperature controlling unit (Lakeshore 335) is also used to precisely control the temperature of the system. To reduce the heat losses by convection heat transfer mechanism and eliminating the effect of the moisture on the performance of the device, a turbo pump is connected to the system to pump down the pressure of the unit to ultra-high vacuum pressures (~10<sup>-7</sup> mbar). The electrical connections are established through a chip-carrier to the device and the chip-carrier is mounted on top of the cold finger. Prior to mounting the chip carrier on top of the cold finger, enough vacuum compatible thermally conductive grease is applied to it to make sure about the proper heat conduction from the cold finger to the device. A keithley 2612A source meter is also used to apply bias between the source and drain of the device and measure the current across the MoS<sub>2</sub>-Gr transistor channel.

**Figure 6. Optical image of the cryogenic system.** Cryogenic system which is used for temperature study of the electrical performance of the MoS<sub>2</sub>-Gr device.

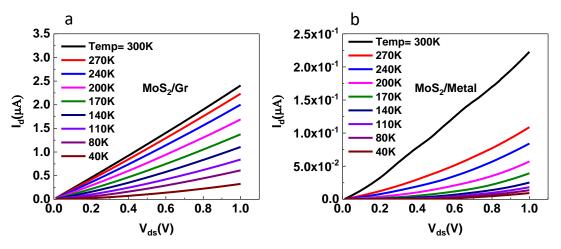

Figure 7 shows the two-probe current-voltage  $(I_d-V_{ds})$  measurements at the back gate bias  $(V_g)$  of 60 V for different temperatures.

**Figure 7. Two-probe current-voltage (Id-Vds) characterization at different temperatures:** Output characteristic at different temperatures for (**a**) MoS<sub>2</sub>-Gr (**b**) MoS<sub>2</sub>-Metal FETs.

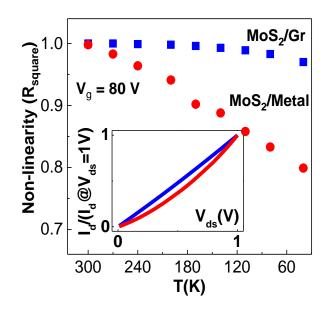

To compare the linearity of the I<sub>d</sub>-V<sub>ds</sub> trends in the MoS<sub>2</sub>-graphene and MoS<sub>2</sub>-metal FETs, the normalized I<sub>d</sub>-V<sub>ds</sub> trends (Y axis: I<sub>d</sub>/I<sub>d@Vsd=1V</sub>) at temperature 270 K are shown as an inset to Figure 8. Unlike the MoS<sub>2</sub>-metal device, the MoS<sub>2</sub>-graphene FET shows a linear behavior. The correlation coefficient of the linear regression ( $R_{square}$ ) in the I<sub>d</sub>-V<sub>ds</sub> is also calculated for both devices at different temperatures (see Figure 8). The R<sub>square</sub> of the MoS<sub>2</sub>-graphene FET starts from 1 at room temperature and goes to 0.970 at 40 K. However, the R<sub>square</sub> of the MoS<sub>2</sub>-metal transistor shows greater temperature dependence (0.998 to 0.799). The larger non-linearity in the I<sub>d</sub>-V<sub>ds</sub> curve of the MoS<sub>2</sub>-metal device compared to the MoS<sub>2</sub>-graphene device – especially at low temperatures – suggests that a larger Schottky barrier is present for the metal-contacted MoS<sub>2</sub> device.

**Figure 8. Linear Regression of I**<sub>d</sub>-V<sub>ds</sub> : The linear regression ( $R_{square}$ ) of the I<sub>d</sub>-V<sub>sd</sub> at different temperatures for the MoS<sub>2</sub>-graphene and MoS<sub>2</sub>-metal FETs (The inset shows normalized I<sub>d</sub>-V<sub>sd</sub> characteristics of the both devices – normalized with their respective I<sub>d</sub> at V<sub>sd</sub>=1V).

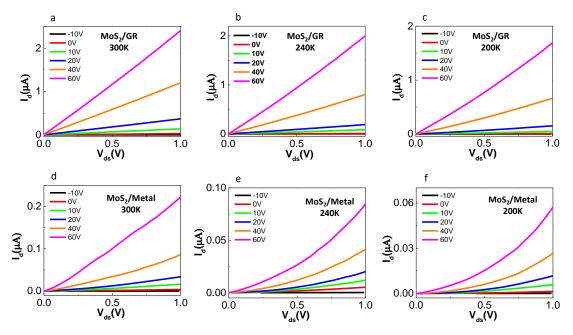

The output characteristics for both devices at different gate biases for different temperatures are also shown in Figure 9. For this measurement, the temperature of the cryogenic setup kept constant at a specific temperature and then  $I_d$ - $V_{ds}$  measurements are performed for different applied gate voltages. The measurement is done at vacuum pressure of ~ 10<sup>-6</sup> Torr. These measurements show that MoS<sub>2</sub>-graphene FET almost keep its linearity at the three different measured temperatures (300K, 240K and 200K) under different applied gate biases. While, MoS<sub>2</sub>-metal FET show significant non-linearity for temperatures lower than the room temperature at different applied gate biases.

Figure 9. Two-probe  $I_d$ - $V_{ds}$  characterization at different applied gate biases :(a-f)  $I_d$ - $V_{ds}$  measurements under different applied gate voltages for MoS2/Gr and MoS2/Metal FETs at 300 K, 240 K, and 200 K respectively.

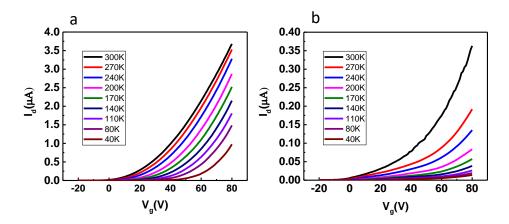

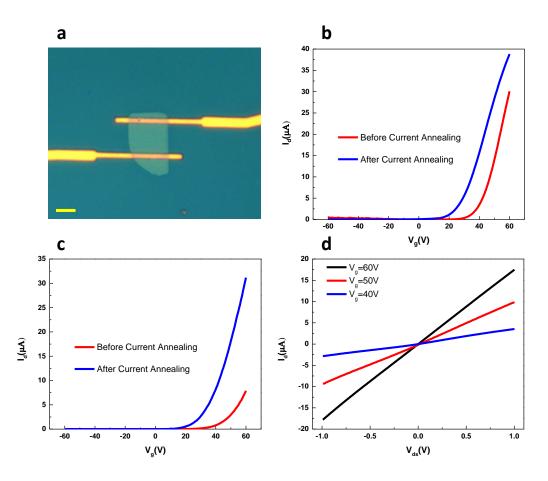

Moreover, the electrical transfer characteristics  $(I_d-V_g)$  were measured at different temperatures (Figure 10) and a typical n-type semiconducting behavior was obtained for both devices.

Figure 10. Two-Probe Electrical Transfer characteristic at different temperatures:  $I_d-V_g$  measurements at different temperatures for (a)  $MoS_2/Gr$  and (b)  $MoS_2/Metal$  FETs.

The I<sub>d</sub>-V<sub>g</sub> results at 270 K (Figure 11) indicate that the current density (I<sub>d</sub>× $\frac{L}{W}$ ) at V<sub>g</sub> = 80 V for the MoS<sub>2</sub>-graphene FET is 20 times higher than the MoS<sub>2</sub>-metal FET. This ratio becomes even larger at low temperatures and approaches ~74 times at 40 K (Figure 11 inset), which is attributed to a smaller barrier for thermally induced charge carriers in the MoS<sub>2</sub>-graphene in-plane heterostructure. These measurements also performed at cryogenic setup and the vacuum pressure of ~ 10<sup>-6</sup> Torr. It is worth mentioning that performing the measurements in the ambient conditions results in lowering the current density of the FETs significantly which is due to the high sensitivity of the MoS<sub>2</sub> to the humidity.

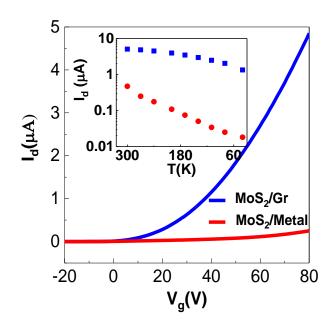

Figure 11. Two-Probe Electrical Transfer characteristic at Vg=80V:  $I_d$ -Vg characteristics of the MoS<sub>2</sub>-graphene and MoS<sub>2</sub>-metal FETs at 270 K (the inset shows the drain current at Vg=80V with respect to temperature).

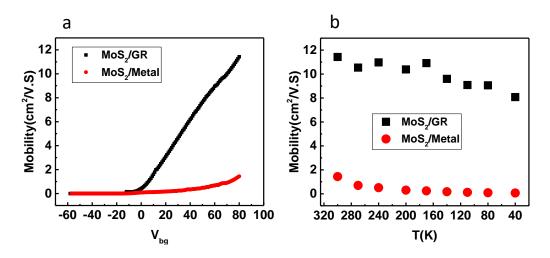

The extrinsic field-effect mobility is also calculated for both structures at room temperature and different back gate voltages (Figure 12a). Both transistors are completely turned OFF at large negative gate biases and turned ON at a threshold voltage of 55 V and 40 V with an ON/OFF ratio of  $10^4$  and  $10^5$  for MoS<sub>2</sub>-metal and MoS<sub>2</sub>-graphene, respectively. The linear field-effect mobility is calculated as ~11.5 cm<sup>2</sup>/V.S for MoS<sub>2</sub>-graphene and ~1.5 cm<sup>2</sup>/V.S for MoS<sub>2</sub>-metal at V<sub>g</sub> = 80 V. It should be noted that the field-effect mobility of the MoS<sub>2</sub>-metal devices is consistent with the previously reported mobility of monolayer CVD MoS<sub>2</sub> without top-gate dielectrics.[109] However, higher extrinsic mobility values can be achieved by using multilayer MoS<sub>2</sub>[118] or using

high-k dielectric substrates/overcoats.[119] Our temperature-dependent measurements show that the mobility of the MoS<sub>2</sub>-metal FET is reduced by 95% as the temperature is decreased to 40 K, while the MoS<sub>2</sub>-graphene FET shows almost constant mobility down to 160 K and then 30% reduction in the mobility at 40 K (Figure 12b). This temperature dependence is also demonstrated in the inset of Figure 4h in which the drain current of the MoS<sub>2</sub>-graphene device reduces by ~4 times, while that of the MoS<sub>2</sub>-metal device decreases by ~26 times.

Figure 12. Mobility measurements: mobility vs. (a) gate voltage at T = 300 K, and (b) the temperature at  $V_g = 80$  V.

To study the Schottky barrier height of the devices, a 2D thermionic equation

$$I_{d} = AT^{3/2} exp\left(\frac{-q(\Phi_{B} - \frac{V_{ds}}{n})}{K_{B}T}\right)$$

is used in which  $I_{d}$  is source-drain current, T is temperature, q

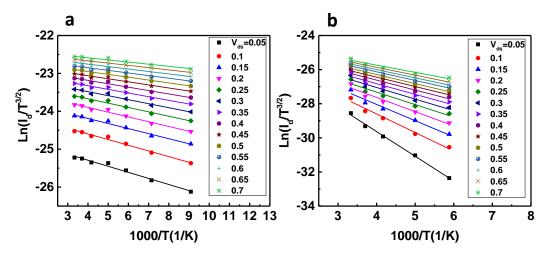

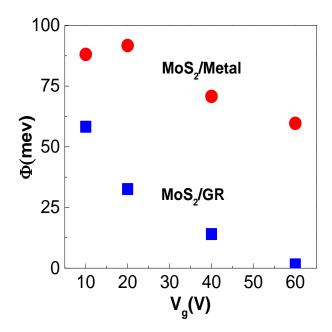

is electron charge,  $K_B$  is Boltzmann constant,  $\Phi_B$  is Schottky barrier height,  $V_{ds}$  is Source-drain current, n is Schottky diode non-ideality factor, and A is Richardson's constant[120], [121]. Figure 13a and b shows the logarithmic plots of  $(I_d/T^{3/2})$  versus (1000/T) for the MoS<sub>2</sub>-graphene and MoS<sub>2</sub>-metal interfaces at different V<sub>ds</sub>.

Figure 13. Arrhenius characterization for different applied source-drain biases: Arrhenius measurements for (a),  $MoS_2/Gr$  (b),  $MoS_2/Metal$  transistors at  $V_g=40V$  for different applied  $V_{ds}$ . (c) Slope of the Arrhenius graph as a function of the  $V_{ds}$  at gate 40 V.

The slope of figure 10a  $\left(\frac{-q(\Phi_{\rm B} - \frac{V_{\rm ds}}{n})}{K_{\rm B}T}\right)$  at each source-drain bias for V<sub>g</sub>=40 V is derived

and plotted in Fig 14 for the MoS<sub>2</sub>/Gr in-plane heterostructure.

Figure 14. Slope of the Arrhenius graph as a function of the  $V_{ds}$  at gate bias of 40 V.

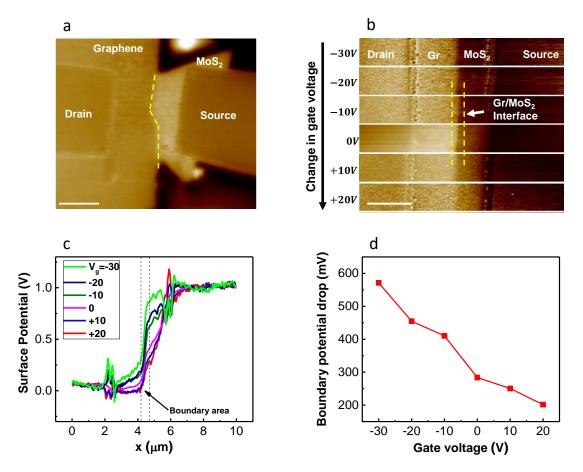

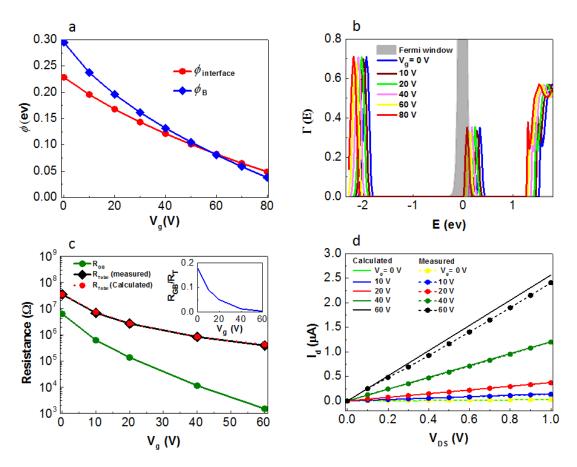

The Schottky barrier height ( $\Phi_B$ ) is calculated at the intercept of Fig. 14 with the Y axis, where the V<sub>ds</sub> is zero[120]. Figure 15 further shows the derived Schottky barrier height of both structures at room temperature for different applied gate voltages. The Schottky barrier height for the MoS<sub>2</sub>-metal structure is about 88 meV at V<sub>g</sub> = 10 V and decreases to 60 meV for V<sub>g</sub> = 60 V, while the MoS<sub>2</sub>-graphene in-plane heterostructure starts at ~58 meV at V<sub>g</sub> = 10 V and fades to zero at V<sub>g</sub> = 60 V. The presence of the schottky barrier height for MoS<sub>2</sub>-metal structure even at high gate biases shows the importance of the choosing of appropriate metal contact for 2D-material semiconductors. This huge Schottky barrier results in decreasing the extrinsic mobility of these semiconductors and downgrading their performance for future applications significantly.

Figure 15. Extracted Schottky barrier height: extracted Schottky barrier height from Arrhenius measurements as a function of  $V_g$  for the MoS<sub>2</sub>-graphene and MoS<sub>2</sub>-metal FETs.

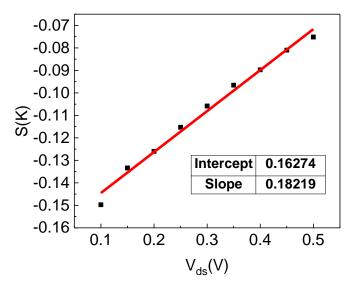

We also performed Kelvin probe force microscopy (KPFM) experiments to map the surface potential distribution across the MoS<sub>2</sub>-graphene interface under applied sourcedrain and gate voltages. This technique enables us to spatially map the local potential drops in the MoS<sub>2</sub>-graphene lateral heterojunction and in the MoS<sub>2</sub> and graphene films under device operational conditions to gain insight into their relative contributions to the overall resistance of the device. Figure 16a shows the KPFM mapping of the device at  $V_{ds} = 0 V$  and  $V_g = 0 V$ . We also mapped the change in the surface potential along the entire length of the device at  $V_{ds} = 1V$  and at different gate voltages (Figure 16b-c). As the gate voltage increases from -20 V to +20 V, the potential drop across the interface decreases from 455 mV to 201 mV (Figure 16d). This observation implies that the contribution of the resistive potential drop across the interface relative to the total resistance of the device decreases as one increases the gate voltage. In other words, the MoS<sub>2</sub>-graphene contact resistance has a negligible contribution to the overall device resistance at larger gate voltages.

Figure 16. KPFM measurements: (a) KPFM mapping of the MoS<sub>2</sub>-graphene transistor with  $V_{gate} = 0 V$  and  $V_{sd} = 0 V$ . The interface between graphene and MoS<sub>2</sub> is highlighted with yellow dashed line (scale bar 2 µm). (b) KPFM mapping of the interface area from a selected region shown in (a) by keeping  $V_{sd} = 1 V$  and changing  $V_{gate}$  from -20 V to +20 V with 10 V increments (Scale bar 2 µm). The dashed lines show the interface area. (c) Corresponding surface

potential profiles across the interface area. (d) The potential drop at the interface area as a function of the applied gate voltages.

Next, a systematic study of 1/f noise was performed in the MoS<sub>2</sub>-graphene and MoS<sub>2</sub>metal devices in a vacuum (pressure  $< 10^{-5}$  Torr). Low frequency 1/f noise has the potential to severely limit the performance of nanoscale materials because 1/f noise increases with decreasing number of carriers (i.e., device size). Recently, it has been shown that metal contacts can play a significant role in 1/f noise in CVD-grown MoS<sub>2</sub>. Thus, 1/f noise is an important metric to gauge the quality and viability of lateral graphene-MoS<sub>2</sub> heterojunctions. Regardless of the fundamental sources of 1/f noise (i.e., mobility fluctuation versus carrier number fluctuation), the noise power spectral density S<sub>1</sub> can be described empirically as:

$$S_I = \frac{AI^{\gamma}}{f^{\beta}}$$

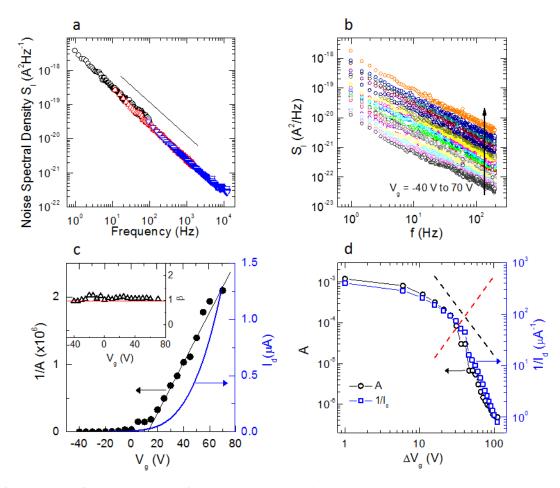

where I is mean drain current, f is frequency, A is noise amplitude, and exponents  $\beta$ and  $\gamma$  are expected to be close to ideal values of 1 and 2, respectively. Figure 17a shows  $1/f^{\beta}$  dependence of noise spectral density for a MoS<sub>2</sub>-graphene device with  $\beta = 1.02 \pm 0.002$  over four decades of frequency.

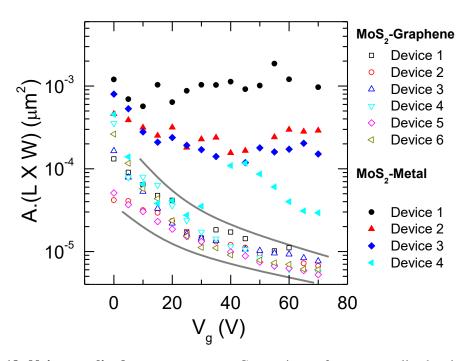

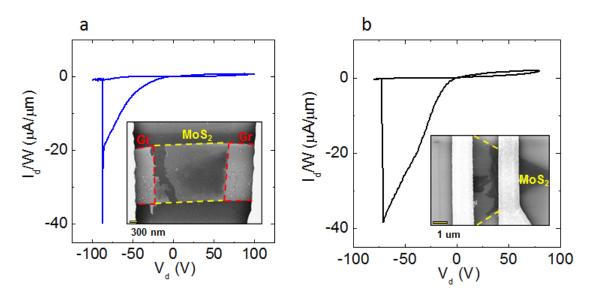

Figure 17. Noise spectral density measurements: (a) Noise spectral density ( $S_1$ ) as a function of frequency for a MoS<sub>2</sub>-graphene FET at  $V_g = 60$  V and  $V_d = 4$  V showing  $1/f^{\beta}$  behavior with  $\beta =$  $1.02 \pm 0.002$ . The black line shows ideal 1/f behavior. (b)  $S_1$  versus frequency of the device at  $V_g$ varying from -40 V to 70 V at  $V_d = 2$  V. (c) Inverse of noise amplitude (1/A) versus  $V_g$  compared with transfer characteristics (device current ( $I_d$ ) versus  $V_g$ ) from the data in (c). The inset shows  $\beta$ as a function of  $V_g$ . (d) Log-Log plot of A and  $1/I_d$  versus  $\Delta V_g$  (=  $V_g + 41$ ) where  $V_g$  is ranging from -40 to 70 V. Black and red dashed lines show  $V_g^{-2}$  and  $V_g^2$  dependence for purely channel and purely contact effects on 1/f noise, respectively.

We also studied the gate-dependence of 1/f noise characteristics to understand the origins of the low frequency fluctuations and the relative role of contacts in MoS<sub>2</sub>-

graphene and MoS<sub>2</sub>-metal devices. Figure 17b shows 1/f behavior of a MoS<sub>2</sub>-graphene device for V<sub>g</sub> = -40 to 70 V. Noise spectral density shows  $1/f^{\beta}$  behavior ( $\beta = 0.97 - 1.2$ ) with no clear dependence on Vg over the entire range (see inset of Figure 17c). Transfer characteristics  $(I_d - V_g)$  of this device show a threshold voltage  $V_{th} = 40$  V (Figure 17c), and thus measurements cover both accumulation (V >  $V_{g}$  -  $V_{\text{th}})$  and sub-threshold regions (V < V<sub>g</sub> - V<sub>th</sub>). The noise amplitude A was extracted from the plots of  $I^2/S_I$ versus frequency with the  $V_g$  dependence analyzed in Figure 17c,d. First, 1/A varies linearly with V<sub>g</sub> in the accumulation region (Figure 17c), even though I<sub>d</sub> follows a superlinear behavior with V<sub>g</sub> in accumulation. Note that I ~ V<sub>g</sub><sup>m</sup> (m = 1 - 2) behavior arises from reduced screening effect in a two-dimensional material with parabolic band structure and has been described in experimental findings[122] and in analytical calculations [123]. Within Hooge's mobility fluctuation model, the noise amplitude A is related to the carrier number (N) according to  $A = \alpha_H/N$ , where  $\alpha_H$  is Hooge's parameter and N =  $C_g/(V_g \, - \, V_{th})/q$  in the accumulation region, where  $C_g$  is total gate oxide capacitance and q is electronic charge. Thus, the linear 1/A  $\sim$  V  $_g$  dependence in the accumulation regime in Figure 17c and strong correlation between noise amplitude and current throughout the whole range of Vg suggests mobility fluctuation or correlated mobility-number fluctuation as the dominant source of current fluctuations in the accumulation region, in agreement with previous 1/f noise studies conducted on exfoliated  $MoS_2$  transistors[124]. The number fluctuation model predicts the correlation between A and  $(g_m/I)^2$ , where  $g_m$  is the transconductance. [125]–[128] In the absence of such correlation in these devices, we rule out the number fluctuation model. The Hooge parameter for this device was extracted as  $\alpha_{\rm H} = 0.21$ , which is comparable to previous CVD-grown MoS<sub>2</sub>[129] but larger than high quality exfoliated MoS<sub>2</sub> by up to 2 orders of magnitude[124]. Indeed, the average Hooge parameter of six measured devices is 0.33 ± 0.08.

Now we consider the role of contacts in the 1/f noise behavior in graphene-MoS<sub>2</sub> and metal-MoS<sub>2</sub> devices. In the case of significant Schottky barriers at the contacts, fluctuations in both channel resistance (R<sub>ch</sub>) and contact resistance (R<sub>c</sub>) can contribute to the overall noise in the transistor. Thus, the normalized noise spectral density can be written as: