### Cookie-Cutter: Achieving Defect/Fault Tolerance For Large-Scale Systems with Highly

**Unreliable Components**

$\mathbf{B}\mathbf{Y}$

SOUMYA BANERJEE B.Tech., West Bengal University of Technology, 2011 M.S., University of Illinois at Chicago, 2016

### THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2017

Chicago, Illinois

Defense Committee:

Wenjing Rao, Chair and Advisor Miloš Žefran Zhichun Zhu Amit Ranjan Trivedi John Lillis, Computer Science Copyright by

Soumya Banerjee

2017

To my parents...

### ACKNOWLEDGMENTS

Over the last 6 years of my PhD program, I've had the opportunity to come into contact with some amazing people, many of whom positively influenced my research, directly and indirectly.

First of all, I would like to thank my adviser, Prof. Wenjing Rao, for her constant and unwavering support. When I started off with my PhD, my perception was that, as a PhD, my only job is to do research and obtain results. Prof. Rao taught me in addition to the aforementioned goal, how important it also is to present my research to the scientific community. Her emphasis on critical thinking for reviewing various papers has helped me in both research and other aspects of my life.

I would also like to thank Prof. Milos Zefran for agreeing to be a part of my PhD committee and helping me out of certain difficult situations I faced as a PhD student. I extend my gratitude to Prof. Zhichun Zhu for serving as a member of my PhD committee, as well as for the interesting and informative classes she taught on Computer Architecture. I thank Prof. Amit Trivedi and Prof. John Lillis for agreeing to serve in my PhD committee.

Working with Soroush, Jian and Paolo at UIC for the last 5 years have been an amazing experience. You guys are awesome!

As a PhD student, there comes numerous challenges, both academic as well as personal. So, thank you Ketaki, Riddha, Adita, Nirupam, Satabdi for being there for me during my most difficult times. Most importantly, thanks to Raika for cheering me up!

### **ACKNOWLEDGMENTS (Continued)**

Last but not the least, without my family's support, I couldn't have achieved this milestone. So, Ma (my mother), Baba (my father), Didi (my elder sister), Pakhi (my niece) and everyone in my family who has stood by me over the years: I dedicate my work to all of you!

### PREFACE

This body of work is an intellectual property of Soumya Banerjee. The works discussed here was conducted at the University of Illinois at Chicago. The work has been presented and published in (Banerjee and Rao, 2016), (Banerjee and Rao, 2017a), (Banerjee and Rao, 2015), (Banerjee and Rao, 2017b). The research work was funded by NSF Grant CNS-1149661.

Soumya Banerjee September 6, 2017

### **CONTRIBUTION OF AUTHORS**

The contents of Chapter 2 was published in (Banerjee and Rao, 2016), (Banerjee and Rao, 2017a). Prof. Wenjing Rao was the PI for this part of the work. I was responsible for conceptualizing the idea, performing the experiments and writing the papers.

The contents of Chapter 3 was published in (Banerjee and Rao, 2015), (Banerjee and Rao, 2017b). Prof. Wenjing Rao was the PI for this part. I was responsible to coming up with the idea, formalizing the problem, proving all the lemmas and theorems, designing the algorithms, as well as performing the experiments and composing the papers.

# TABLE OF CONTENTS

# **CHAPTER**

### PAGE

| 1 | INTROD       | PUCTION                                                            | 1  |

|---|--------------|--------------------------------------------------------------------|----|

|   | 1.1          | Defect Tolerance and Design Space Exploration via Sparsity in Par- |    |

|   |              | allel Prefix Adders                                                | 2  |

|   | 1.2          | Formalization of Basic Replacement Chain Algebra to Arbitrary      |    |

|   |              | Many-Processor System                                              | 3  |

|   | 1.3          | Organization                                                       | 5  |

| 2 | GENERA       | ALIZATION OF KOGGE-STONE ADDER GROUP SEGREGA-                      |    |

|   |              | ROPERTY                                                            | 7  |

|   | 2.1          | Introduction to Parallel Prefix Adders                             | 7  |

|   | 2.2          | Kogge-Stone Adders and Group Segregation Property                  | 9  |

|   | 2.3          | Defect Tolerant Parallel Prefix Adders                             | 13 |

|   | 2.3.1        | Motivations and Previous Works                                     | 13 |

|   | 2.3.2        | The Proposed Defect Tolerant Design                                | 15 |

|   | 2.3.3        | Experimental Results                                               | 18 |

|   | 2.3.3.1      | Reliability Analysis                                               | 20 |

|   | 2.3.3.2      | Expansion of Reliable PPA Design Space Choices                     | 22 |

|   | 2.3.3.3      | Delay Variation in the Proposed Scheme                             | 24 |

|   | 2.4          | Sparse Parallel Prefix Adders                                      | 25 |

|   | 2.4.1        | Motivations and Previous Works                                     | 25 |

|   | 2.4.2        | Design Approach for Sparse Parallel Prefix Adders                  | 27 |

|   | 2.4.2.1      | Examples                                                           | 27 |

|   | 2.4.2.2      | Group-Segregation designs for k-Sparse PPA's                       | 29 |

|   | 2.4.2.3      | Residual GP Restoration designs for k-Sparse PPA's                 | 30 |

|   | 2.4.2.4      | Overall Design                                                     | 31 |

|   | 2.4.3        | Associated Metrics                                                 | 33 |

|   | 2.4.4        | Experimental Results                                               | 35 |

| 3 | FORMA        | LIZATION OF REPLACEMENT CHAIN ALGEBRA IN ARBI-                     |    |

|   | <b>TRARY</b> | MANY-PROCESSOR SYSTEMS                                             | 39 |

|   | 3.1          | Previous Works and Motivations                                     | 39 |

|   | 3.2          | Introduction to the Proposed 2-Layered Task-PE Model               | 44 |

|   | 3.2.1        | Formal Definition of the Task-PE Model                             | 45 |

|   | 3.3          | Necessary and Sufficient Conditions for Guaranteed k-FT            | 48 |

|   | 3.3.1        | Repalcement Graph Changes after a Successful Repair: Replace-      |    |

|   |              | ment Chain Algebra                                                 | 48 |

|   | 3.3.2        | Repair Chain Independence of Task-PE Model                         | 51 |

|   |              |                                                                    |    |

# TABLE OF CONTENTS (Continued)

# **CHAPTER**

# PAGE

|   | 3.3.3   | Illustration of the Conditions                                    | 55  |

|---|---------|-------------------------------------------------------------------|-----|

|   | 3.3.4   | Discussion                                                        | 57  |

|   | 3.4     | Physical Implementation of Task-PE Model                          | 57  |

|   | 3.4.1   | Repair Strategy and Reliability Analysis                          | 62  |

|   | 3.4.2   | Reliability Enhancement                                           | 63  |

|   | 3.4.3   | Experimental Results                                              | 66  |

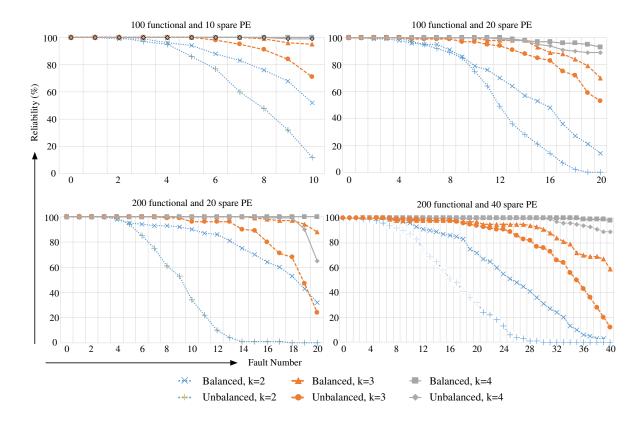

|   | 3.4.3.1 | Reliability Comparisons                                           | 66  |

|   | 3.4.3.2 | Reliability Enhancement Type 2: by Enlarged Coverage              | 69  |

|   | 3.4.3.3 | Hardware and Interconnect Overhead                                | 71  |

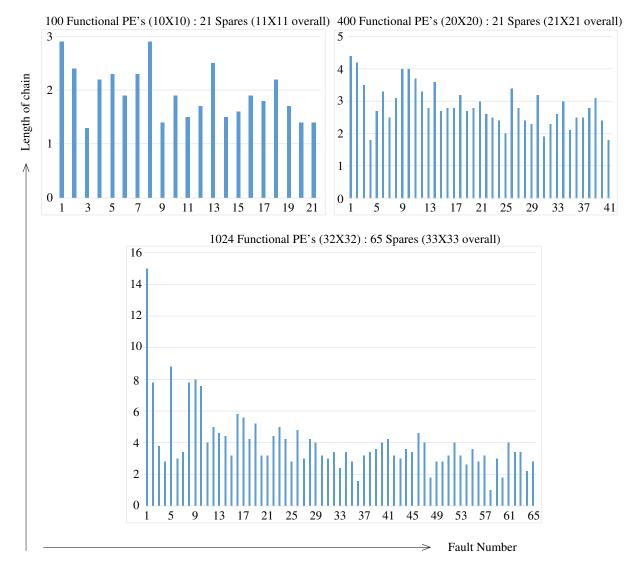

|   | 3.4.3.4 | Average Lengths of Replacement Chains                             | 71  |

|   | 3.4.4   | Discussion                                                        | 73  |

|   | 3.5     | Future Work: Construction of k Fault Tolerant Systems             | 73  |

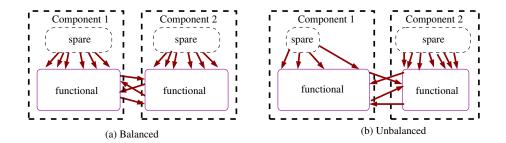

|   | 3.5.1   | Design of Balanced System                                         | 76  |

|   | 3.5.2   | Design of Unbalanced System                                       | 80  |

|   | 3.5.3   | Experimental Results                                              | 80  |

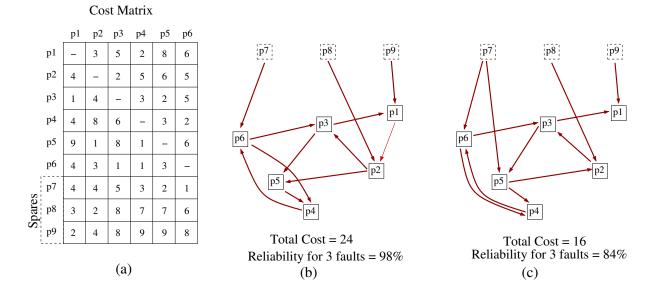

|   | 3.5.3.1 | Reliability-Cost Trade-offs                                       | 81  |

|   | 3.5.3.2 | Replacement Chain Selection                                       | 83  |

| 4 | CONCLU  | USIONS AND FUTURE WORKS                                           | 86  |

|   | 4.1     | Generalization of Group Segregation Property in Kogge-Stone Adder | 87  |

|   | 4.2     | Fault Tolerant Many-Processor Systems                             | 88  |

|   | APPEND  | DIX                                                               | 91  |

|   | CITED L | JTERATURE                                                         | 96  |

|   | VITA    |                                                                   | 102 |

# LIST OF TABLES

| <b>TABLE</b> | Ē                                                                                                                    | <u>PAGE</u> |

|--------------|----------------------------------------------------------------------------------------------------------------------|-------------|

| Ι            | PARAMETERS FOR THE THREE DESIGNS SHOWN IN FIGURE 9, NORMALIZED TO THE 1-SPARSE DESIGN ©IEEE 2017                     | 27          |

| Π            | REDUNDANT INTERCONNECT COMPLEXITY COMPARISONS AMO<br>VARIOUS APPROACHES ©IEEE 2017                                   | NG<br>70    |

| III          | COST AND MEAN AVERAGE DISTANCE (MAD) FOR THE COV-<br>ERAGE DISTRIBUTION CORRESPONDING TO THE SYSTEMS IN<br>FIGURE 37 | 83          |

# LIST OF FIGURES

| <b>FIGURE</b> |                                                                                                                                                      | PAGE |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

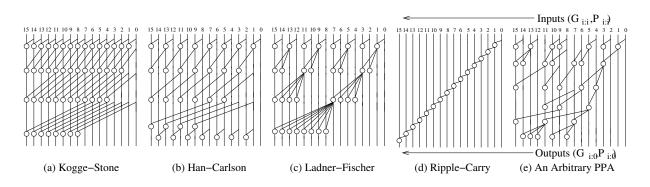

| 1             | The GP computation stages of various 16-bit PPA's ©IEEE 2017                                                                                         | 8    |

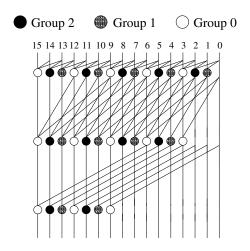

| 2             | The defect tolerant KSA design in (Ndai et al., 2007) ©IEEE 2016                                                                                     | 9    |

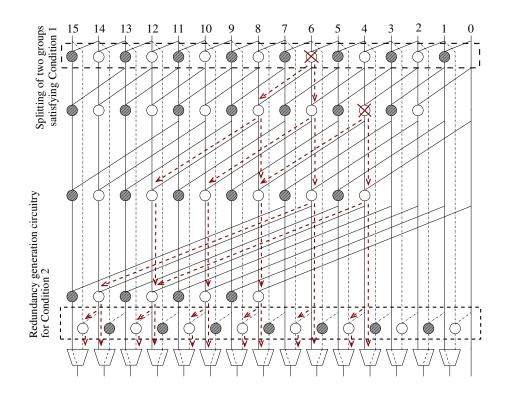

| 3             | Group Segregation Property of KSA and corresponding approaches for defect tolerant and sparse PPA design ©IEEE 2016 and ©IEEE 2017                   | 10   |

| 4             | A 16-bit Radix-3 KSA ©IEEE 2016                                                                                                                      | 16   |

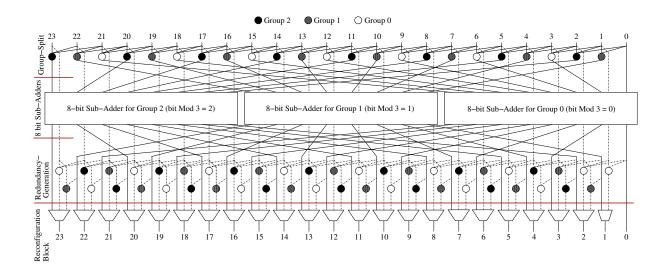

| 5             | An example of the proposed adder design approach with 24-bits and 3 groups ©IEEE 2016                                                                | 16   |

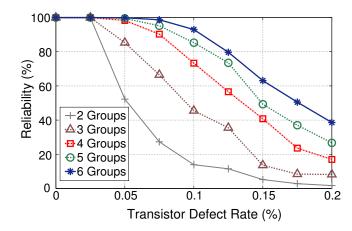

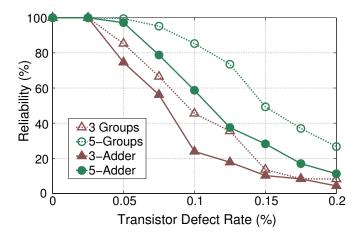

| 6             | Reliability Analysis for the proposed design with 64-bit Brent-Kung Adder ©IEEE 2016                                                                 | 21   |

| 7             | Reliability comparison between the proposed design versus the N-Adder approach with 64-bit Brent-Kung Adder ©IEEE 2016                               | 22   |

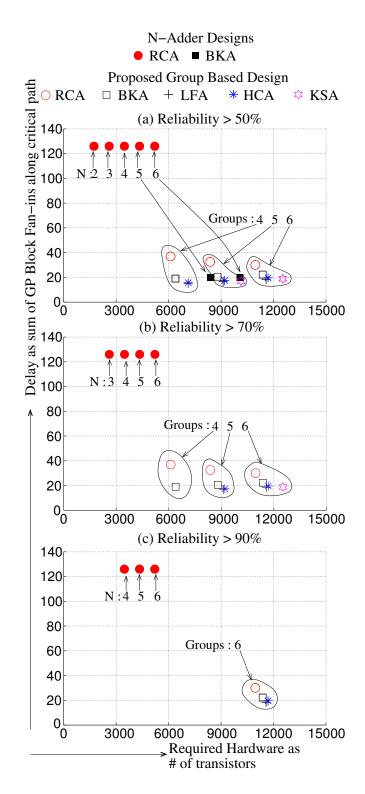

| 8             | Design trade-off points for various 64-bit adders at 0.1% defect rate ©IEEE 2016                                                                     | 23   |

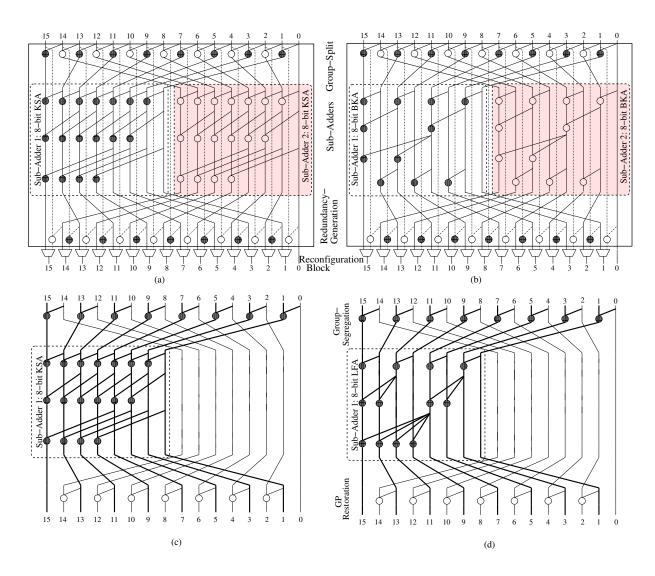

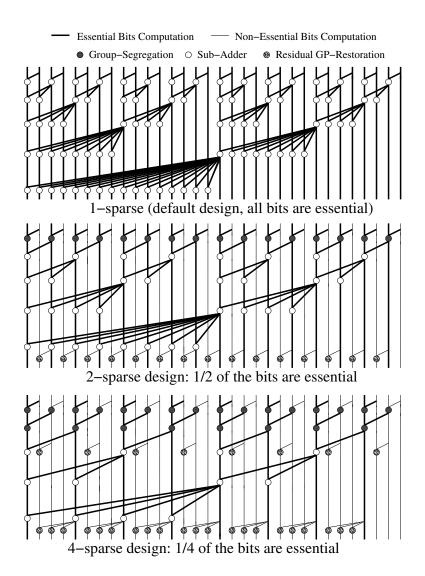

| 9             | Various designs for 32-bit LFA's with changing sparsity $\bigcirc$ IEEE 2017                                                                         | 28   |

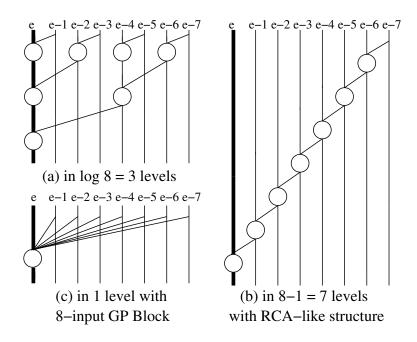

| 10            | A variety of Group-Segregation Block structures ©IEEE 2017                                                                                           | 29   |

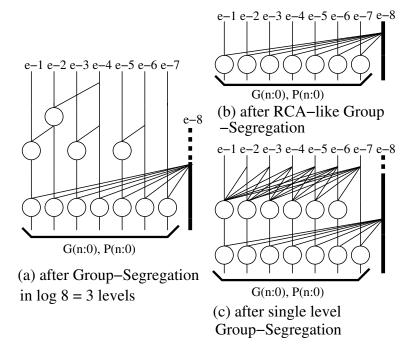

| 11            | Various Residual GP Restoration options ©IEEE 2017                                                                                                   | 31   |

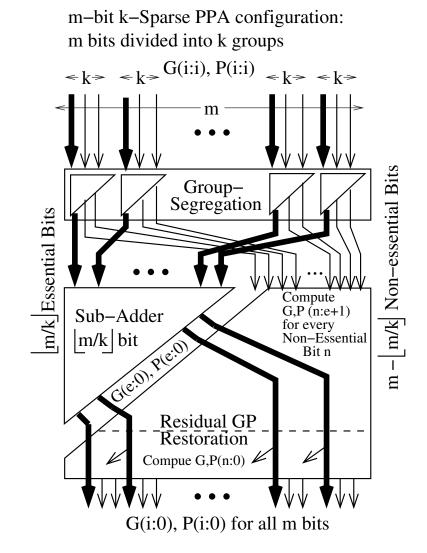

| 12            | Overall design structure of an <i>m</i> -bit <i>k</i> -Sparse PPA ©IEEE 2017                                                                         | 32   |

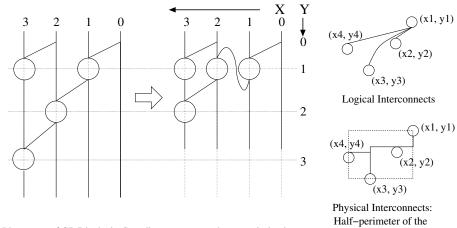

| 13            | Representing an arbitrary PPA in a 2D space using Cartesian Coordinates, and estimation of interconnect lengths via half-perimeter method ©IEEE 2017 | 34   |

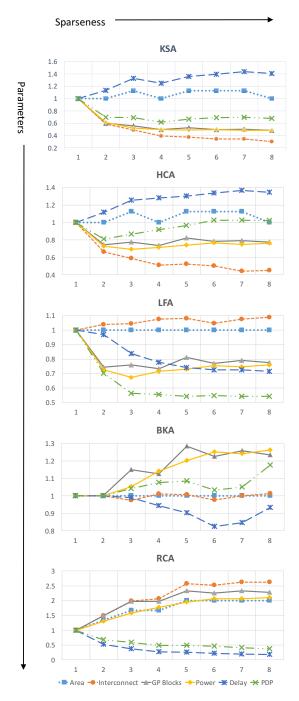

| 14            | Various metrics evaluated on 64-bit Sparse PPA's with changing sparsity on various PPA types ©IEEE 2017                                              | 36   |

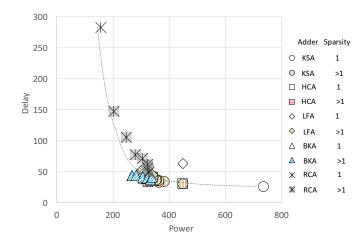

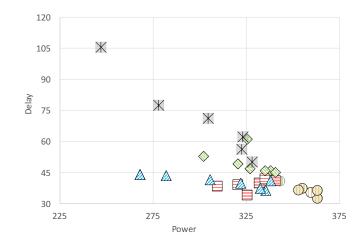

| 15            | The 64-bit Adder Design space in power-delay domain ©IEEE 2017                                                                                       | 37   |

# LIST OF FIGURES (Continued)

| <u>FIGURE</u> |                                                                                                                                                                                                                                               | <b>PAGE</b> |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 16            | A zoomed-in view of Figure 15 ©IEEE 2017                                                                                                                                                                                                      | 37          |

| 17            | Typical approaches for implementing fault tolerance in systems with mul-<br>tiple PE's                                                                                                                                                        | 40          |

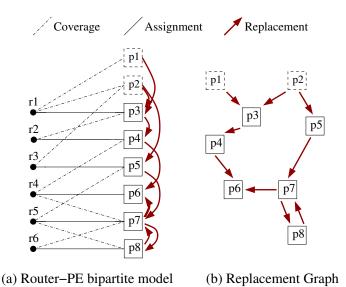

| 18            | a) Task-PE relationships with replacement possibilities augmented for a system with 5 tasks and 7 PE's, b) its Replacement Graph                                                                                                              | 46          |

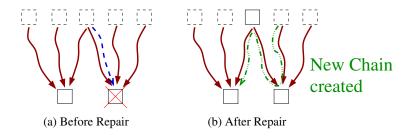

| 19            | After a repair, $p_2$ "inherits" the incoming replacements of $p_3$ , while $p_1$ "inherits" the incoming replacements of $p_2$ .                                                                                                             | 49          |

| 20            | Illustration of Lemma 1: reversal of a replacement chain                                                                                                                                                                                      | 50          |

| 21            | Illustration for Lemma 2, (a) Case 1: $p \in \mathbb{P}(\mathbb{T})$ , (b) Case 2: $p \in GW(\mathbb{T})$ , (c) Case 3: $p \notin \mathbb{P}(\mathbb{T})$ and $P \notin GW(\mathbb{T})$ .                                                     | 52          |

| 22            | Illustration of proof of main claim: (a) $1 \Rightarrow 2$ , (b) $3 \Rightarrow 1$ .                                                                                                                                                          | 53          |

| 23            | Illustration of the Repair Chain Independence: when a PE chooses an arbi-<br>trary chain                                                                                                                                                      | 55          |

| 24            | Illustration of the Repair Chain Independence: effect on a PE when another PE chooses an arbitrary chain                                                                                                                                      | 56          |

| 25            | Effect of choosing of the shared spare by the faulty PE                                                                                                                                                                                       | 56          |

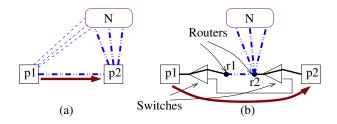

| 26            | (a) Replacement of one PE by another: requiring the latter to be connected to former's neighbors; (b) An alternative implementation using switches and Routers                                                                                | 58          |

| 27            | The proposed Router-PE System with a fault tolerance illustrated                                                                                                                                                                              | 59          |

| 28            | The Router-PE system corresponding to the system in Figure 27, isomorphic to the Task-PE model                                                                                                                                                | 60          |

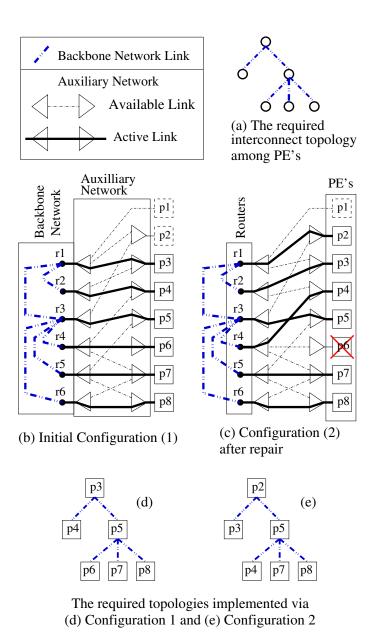

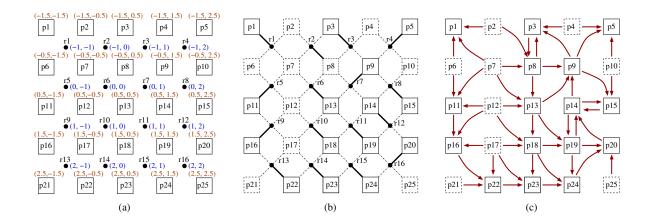

| 29            | a) The $4 \times 4$ 2D Array layout with the corresponding coordinates assigned,<br>b) system with spares distributed around in the system with local coverages,<br>c) Replacement relationships among the PE's from the configuration in (b) | 60          |

|               | ©IEEE 2017                                                                                                                                                                                                                                    | 62          |

# LIST OF FIGURES (Continued)

# **FIGURE**

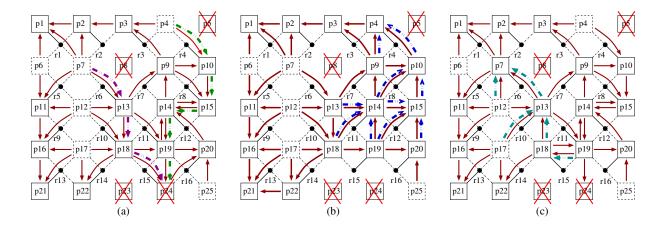

| 30 | An example repair in a $4 \times 4$ Array implemented on a $5 \times 5$ PE Array a)<br>after 3 faults are repaired, b) after the $4^{th}$ fault at $p_{24}$ is repaired through chain<br>$p_{24} \leftarrow p_{19} \leftarrow p_{14} \leftarrow p_{15} \leftarrow p_{10} \leftarrow p_4$ ; and c) using alternate replacement chain<br>of $p_{24} \leftarrow p_{18} \leftarrow p_{13} \leftarrow p_7$ . The changed replacements are also highlighted<br>©IEEE 2017                                           | 63 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

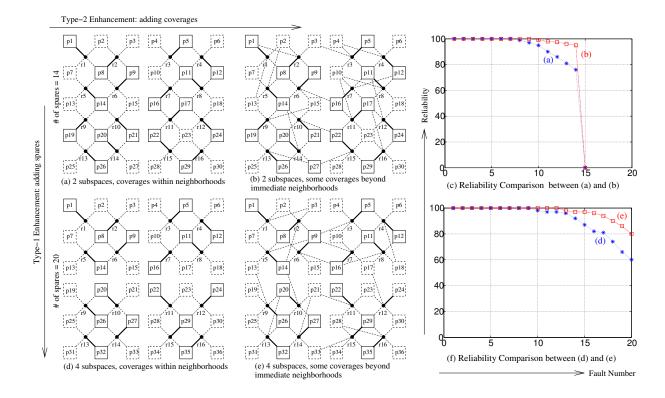

| 31 | a) The 4×4 Router space divided into 2 4×2 spaces, resulting in increase<br>in total number of spares, b) type 2 reliability enhancement by allowing some<br>performance degradation over (a), c) Reliability comparison between (a) and<br>(b), d) same space divided into 4 2×2 spaces, resulting in further increase in<br>total number of spares, and d) type 2 reliability enhancement by allowing more<br>performance degradation over (e), f) Reliability comparison between (d) and<br>(e) ©IEEE 2017 | 64 |

| 32 | Reliability comparison between the previous works and the proposed approach                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

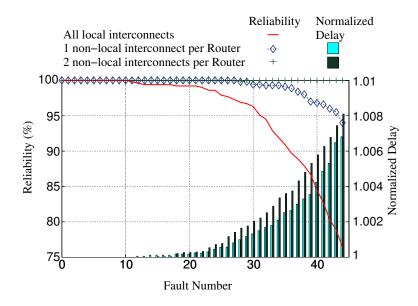

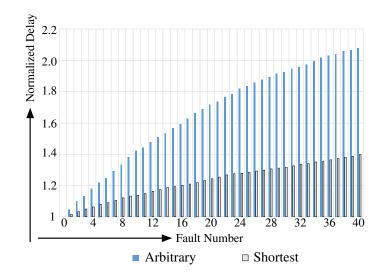

| 33 | Reliability enhancement in the proposed approach by allowing Normalized Delay to increase ©IEEE 2017                                                                                                                                                                                                                                                                                                                                                                                                          | 69 |

| 34 | Average lengths of Replacement Chains for various systems                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72 |

| 35 | Systems with two different cost-reliability trade-offs (reliability obtained through simulation)                                                                                                                                                                                                                                                                                                                                                                                                              | 74 |

| 36 | Balanced and Unbalanced Replacement Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76 |

| 37 | Reliability curves for different systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 81 |

| 38 | System delay increase for shortest vs random chains                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85 |

# List of Algorithms

| 1 | Algorithm to design Balanced Replacement Graphs   | 77 |

|---|---------------------------------------------------|----|

| 2 | Algorithm to design Unbalanced Replacement Graphs | 78 |

# LIST OF ABBREVIATIONS

PPA Parallel Prefix Adder Kogge-Stone Adder KSA HCA Han-Carlson Adder LFA Ladner-Fisher Adder Brent-Kung Adder BKA Ripple-Carry Adder RCA Processing Element PE k-Fault Tolerant k-FT MAD Mean Average Distance University of Illinois at Chicago UIC European Design and Automation Association EDAA Institute of Electrical and Electronics Engineers IEEE

### SUMMARY

The dissertation discusses about defect and fault tolerance in nano-scale systems. With fast shrinking device dimensions, the fabrication equipments have been unable to keep up with the required level of accuracy. As a result, the manufacturing defect rates are on the rise. On the other hand, smaller device dimensions have also resulted in devices being more susceptible to cosmic particle strikes as well as electromigration. Because of the reasons mentioned, defect and fault tolerance mechanisms are necessitated for new nano-scale systems.

The dissertation is divided into two parts: highly defect tolerant Parallel Prefix Adder (PPA) design (and beyond); and highly fault tolerant Many-Processor systems supporting on-the-fly repairs.

For the first part, we point out the unique "Group-Segregation" property of Kogge-Stone Adders (KSA), a particular type of PPA. This property enables the KSA to be divided into two disjoint groups, even and odd bits, such that each can perform the computations independently of each other. If one group is defective, the other group can compute the correct results for the defective group with marginal hardware and computation overhead. In this work, we show how such number of groups can be increased such that more defects can be tolerated. Moreover, we propose a technique to extend the Group-Segregation property to other PPA's as well. The Group-Segregation property also paves the way for designing "sparse" PPA's, where every *k*-th bit computes their results, while the rest of the bits rely on the former. We propose a generalized approach for designing arbitrary *k*-sparse PPA's.

In the second part, we introduce a novel 2-Layered Task-PE model, which facilitates design of highly fault tolerant Many-Processor systems. Such a model contains Processing Elements at one layer

### **SUMMARY** (Continued)

for the execution of the Tasks at another layer. The faults are tolerated on-the-fly, after every fault occurrence through "chain of replacements", where a faulty PE is replaced by a functional PE located nearby; the latter being replaced again by another PE; the chain of replacements continue until a spare is reached. In this dissertation, we show how such a model culminates in the Many-Processor system to be "replacement chain independent", i.e., the reliability is unaffected by the choice of the replacement chain for repair. This independence in choosing the repair choice makes the repairs simple and lightweight. We show the design of such system with strictly local interconnects, making the system highly scalable.

### CHAPTER 1

### **INTRODUCTION**

The dissertation deals with defect and fault tolerance in nano-scale circuits and systems, specifically Parallel Prefix Adders and Many-Processor systems. Scaling down of sizes for current technologies following Moore's Law has resulted in prevalence of the reliability issues in the devices. With the rapid size scaling of devices, the manufacturing procedures have been unable to keep up the accuracy needed for fabricate such devices. As a result, manufacturing **defects** are becoming an important issue. (ITRS, 2015) predicts that the defect rates will increase from current  $10^{-7}$  up to  $10^{-1}$ . Manufacturing defects are not the only issue holding back the future devices. Smaller devices are also more susceptible to external interference, such as cosmic ray particle strikes (Zieglar, 1996) as well as internal issues like electromigration (Lienig, 2013). This does not only result in transient faults, but also has the potential to damage the devices in permanent **faults**.

To formalize, we consider two issues affecting the device reliability:

Defects are due to the manufacturing inaccuracies of the fabrication equipments.

**Faults** are due to the external interference of cosmic particle and internal issues, such as electromigration. They typically occur during normal runtime of the circuit/system. The effects can be transient or permanent.

The dissertation discusses about a defect tolerance approach for Parallel Prefix Adders and a fault tolerance approach in Many-Processor systems.

#### 1.1 Defect Tolerance and Design Space Exploration via Sparsity in Parallel Prefix Adders

Parallel Prefix Adders (PPA) are a class of adders which provide a large variety of choices along performance-power-area paretal front. Kogge-Stone Adder (KSA) is a particular type of PPA, which is perhaps the fastest typical PPA, while using a large amount of hardware. Owing to the design, it performs significant redundant computation. The redundant computation is KSA can be explained by its *Group Segregation* property. In KSA, the bits are divided into two distinct groups: even bits and odd bits. The two bits compute their results independently of each other. Furthermore, a group can compute an additional copy of its result just by using the results of the other group. This *Group Segregation* property can be utilized in two ways:

1. Having a redundant copy of the result available is convenient when the design is used for defect and fault tolerance.

2. Removing all the computing elements of a group will result in half the adder computing the result, while the other half uses the results of the former.

Due to the desirable property of KSA, most of the works on reliable and sparse adders have concentrated on KSA. While there exist approaches suitable for other PPA's, they are mainly ad-hoc and are unsuitable for implementation in a general sense. Furthermore, with only two groups at their disposal, it can guaranteed tolerate only a single defect: one defect at any one of the groups. However, with increasing defect rates, it is unlikely that there will be only one defect circuit wide. To make sure the minimum number of tolerable defects is greater than 1, the dissertation proposes an approach to increase the number of groups to k. With k groups, as long as one of the groups is defect free, the adder functions. Thus, it can tolerate guaranteed (k-1) defects. Moreover, we propose a design methodology to extend the desirable KSA properties onto other PPA's as well, making every PPA able to tolerate defects.

Overall the proposed approach does not only tolerate more defects, but also extends the group segregation property of KSA onto other PPA's. This makes any arbitrary PPA being able to tolerate defects, not only KSA. The defect tolerance is done through post manufacturing reconfiguration.

If we remove all the computing elements of a group and let the other group perform all the computations, following the aforementioned observation 2, the resulting adder is a 2-*sparse* version of KSA, which incidentally is a Han-Carlson Adder (HCA). In this dissertation, we extend the Group Segregation property of KSA onto other PPA's to design any arbitrary sparse PPA. We also increase the number of groups in a similar fashion to come up with *k*-sparse PPA's. Sparse adders provide the designers with more choices in design space to utilize the exact adder fitting the requirements.

### 1.2 Formalization of Basic Replacement Chain Algebra to Arbitrary Many-Processor System

In the consumer market, future processors are expected to contain upto a thousand cores (Borkar, 2007). FPGA's, NoC's, GPU's already contain hundreds of identical unit computing elements. DSP processors have classically contained hundreds, if not thousands, of identical adders and multipliers. In spite of the high performance delivered by the processors, FPGA's, NoC's and GPU's, future reliability issues may keep their capabilities limited (Constantinescu, 2003). As an example, the Power Mac G5 machine at Virginia Tech, in the absence of any Error Correcting Codes (ECC) was so prone to crashing, that it used to crash even before booting (Geist, 2016). The very high fault rate was due to the cosmic particle strikes. Even though adding ECC could alleviate the problem to a certain extent, still ECC cannot detect and correct an unlimited number of faults.

Keeping the issue in mind, lots of work has been done on the issue of Many-Processor reliability. There have been works done on 2D, 3D Grid/hypercube, Tree, Ring topologies of Processors. Their main assumptions are: given a specific topology, how to retain the original topology when *k* Processors are removed through faults. However, two important things missing are: defect and fault tolerance approach for any arbitrary topology and lightweight on-the-fly repairs after every fault manifestation.

As pointed out, most of the previous works concentrated on specific topologies. While they delivered satisfactory reliability for those specific topologies, they cannot be used in other topologies.

On the other hand, lightweight on-the-fly repair capabilities is desired in any many-processor system. After a fault occurs, stopping the system, repairing it and eventually resuming the normal functionalities will result in inconvenience for the user.

In the proposed design technique, we first consider *Replacement Chain* based repair on a novel 2-layered Task-PE model, and derive the underlying properties through *Replacement Chain Algebra*. We will show that the proposed 2-layered model can be extended to work on any arbitrary topology. In repairs via Replacement Chain, a faulty Processing Element (PE) is replaced by a non-faulty functional one in its neighborhood, which in turn, is replaced by another PE. This chain goes on until a spare PE is reached. Using Replacement Chain Algebra, we formalize this process on 2-layered model. We show that such a repair mechanism is able to support lightweight on-the-fly repairs after every fault manifestation. Moreover, the system can guarantee k fault tolerances when certain conditions are fulfilled.

Overall, the proposed approach can deliver the following:

1. Reliability with guarantee.

2. Simple lightweight on-the-fly repairs.

3. Localized interconnects in any arbitrary topology, resulting in scalability.

#### 1.3 Organization

Overall, the dissertation consists of two parts: Chapter 2 discusses about generalizing the Group Segregation property of KSA; Chapters 3 discusses about designing fault tolerant Many-Processor system following the 2-layered model supported by Replacement Chain Algebra. Effectively, the first part deals with extending an specific property of a circuit to others, while the second part deals with formalizing basic properties of any system.

Chapter 2, is divided into two distinct sections: defect tolerant PPA design and sparse PPA design. First we discuss about how PPA's function, followed by discussions about KSA and its Group Segregation property. Following this part, we discuss about generalized defect tolerant PPA design. Finally, we show how sparse adder designs can be generalized by using the Group Segregation property.

The second part is contained in Chapter 3, starting from discussions about the previous works in the fault tolerance in Many-Processor systems and also the motivation behind our proposed design model, followed by the introduction of the proposed 2-layered Task-PE model for designing fault tolerant Many-Processor systems. The conditions of guaranteed k fault tolerances in the proposed 2-layered model are discussed next. This chapter also proves that the repairs in the proposed model are indeed lightweight and simple, and do not need to follow any complex algorithms. Next, we provide a case study of designing the popular 2D Processor Array with fault tolerance capabilities using the proposed 2-layered model. We show that such a design is scalable in terms of the interconnects, as they are always constrained within local neighborhoods. As a result, even with more number of components, the interconnects are not long. Furthermore, the reliability delivered by the approach is compares favor-

ably to other similar approaches. Finally, we show generalized approaches for designing fault tolerant Many-Processor systems with arbitrary topology and placement of components as a future work. This approach also aims to reduce the interconnect lengths by making sure they are as local as possible. Specific placements and topologies (grid, hypercube etc) can act as a special case of the proposed design approach.

We conclude the overall dissertation in Chapter 4.

### **CHAPTER 2**

# GENERALIZATION OF KOGGE-STONE ADDER GROUP SEGREGATION PROPERTY

*This chapter has been partially published as (Banerjee and Rao, 2017a), (Banerjee and Rao, 2016).* ©2017, 2016, IEEE.

### 2.1 Introduction to Parallel Prefix Adders

Parallel Prefix Adders (PPA's) are a class of adders which compute the sum of two *n*-bit numbers by considering two particular parameters: Generate and Propagate (GP). Generate indicates if a carry has been *generated* by a bit, or a *block* of bits. On the other hand, Propagate indicates if a bit or a *block* of bits can *propagate* a carry signal from the previous bits to the next.

PPA's (Parhami, 2010) use three steps to compute the sum bits:

1. **Bit-level Generate and Propagate**: for each input bit pair  $A_i$  and  $B_i$ , the bit-level Generate and Propagate signals  $(G_{i:i}, P_{i:i})$  are computed as:

$$(G_{i:i}, P_{i:i}) = (A_i \cdot B_i, A_i \oplus B_i)$$

2. Block-level Generate and Propagate: this stage derives  $(G_{i:0}, P_{i:0})$  for all the bits *i*. Such results can be computed via the following prefix formulation of sub-blocks:

$$(G_{i:j}, P_{i:j}) = (G_{i:k_1}, P_{i:k_1}) \circ (G_{k_1:k_2}, P_{k_1:k_2}) \circ (G_{k_2:k_3}, P_{k_2:k_3}) \circ \dots \circ (G_{k_n:j}, P_{k_n:j})$$

Figure 1: The GP computation stages of various 16-bit PPA's ©IEEE 2017

The "°" operator is defined as:

$$(G_{i:k}, P_{i,k}) \circ (G_{k,j}, P_{k,j}) = (G_{i:k} + P_{i:k} \cdot G_{k:j}, P_{i:k} \cdot P_{k:j})$$

where  $i \ge k \ge j$ .

3. Carry and Sum computation: the  $G_{i:0}$  and  $P_{i:0}$  of all the bits are used to compute Carry  $C_i$  and Sum  $S_i$  in parallel:

$$C_i = G_{i-1:0}, S_i = P_{i:i} \oplus C_i$$

Obviously, the most critical part of a PPA is stage 2 in terms of area, power and performance. In this crucial stage, the Block-level Generate and Propagate  $(G_{i:0}, P_{i:0})$  is computed for every bit *i*, and each

of these computations relies on the preceding bits from (i-1) to 0. Therefore the entire circuit consists of a large network of Generate and Propagate blocks. Since " $\circ$ " operator is associative, the block-level Generate and Propagate computations can be done in arbitrary order. Various PPAs thus use distinct architectures for this stage. Figure 1 shows this stage 2 structures of various PPA's, including Kogge-Stone (KSA), Han-Carlson (HCA), Ladner-Fischer (LFA), Ripple-Carry (RCA) and an Arbitrary PPA, with each of the circles representing one " $\circ$ " operation, or a *GP Block*.

### 2.2 Kogge-Stone Adders and Group Segregation Property

Figure 2: The defect tolerant KSA design in (Ndai et al., 2007) ©IEEE 2016

Figure 3: Group Segregation Property of KSA and corresponding approaches for defect tolerant and sparse PPA design ©IEEE 2016 and ©IEEE 2017

A typical (radix-2) 16-bit Kogge-Stone Adder (KSA) has its bits divided into two disjoint hardware groups: even (Group 0) and odd (Group 1) bits. As a result, any defect in one group will have their

erroneous results constrained within the same group, thus not contaminating the results of the other group.

Moreover, it turns out that each group can derive a redundant copy of the results of the other group, i.e., the corresponding GP signals with a small extra cost. Such a scheme is proposed in (Ndai et al., 2007), with its structure shown in Figure 2. This design ensures the correct result when all the defects are within one group. In such a case, the defect-free group is used to generate the results for both, with the additional row of extra GP Blocks at the bottom. For example, bit 14 has two copies of ( $G_{14:0}$ ,  $P_{14:0}$ ) generated: one from the regular computation of the even group (which bit 14 belongs to), another by performing ( $G_{14:14}$ ,  $P_{14:14}$ )  $\circ$  ( $G_{13:0}$ ,  $P_{13:0}$ ), obtained from bit 13, part of the odd group. When the defect is in the even group, as is shown in the figure, the first copy will be erroneous. However, the second copy, computed from the odd group, remains correct. This copy of the result is then selected by configuring the MUXes at the output end.

Essentially, the KSA structure satisfies two key conditions, which make it possible to achieve defect tolerance at such a low cost: **Condition 1:** the formation of *hardware disjoint groups*, each carries out half of the GP signal calculations independently; and **Condition 2:** the *replacing capacity* of one group's result for deriving a redundant copy of the other groups' results, thanks to the arrangement of interleaving bits into groups.

Extending the defect tolerance framework to other PPA's such as Brent-Kung (BKA), Ripple-Carry (RCA), shown in Figure 1, is not straightforward, as they do not easily satisfy the two conditions presented in KSA. For this reason, we need to take a careful look into the structure that makes such conditions hold. From Figure 2, it can be observed that Condition 1 for KSA is essentially enabled by the first level of GP Blocks (denoted as *Group-Split*) only. Then, all the communications are strictly contained within each group. Therefore, this first level of GP Blocks of a KSA can in fact be extracted out, to satisfy Condition 1 for other general PPA structures. Condition 2, it turns out, is also not limited to the specific structure of KSA's. As long as the groups are formed by interleaving bits, and an additional level of GP Blocks (denoted as *Redundancy-Generation*) are added at the end, each group can guarantee to generate a redundant copy of results for all the other groups. The structure between those two levels do not really impose any constraints for either Condition 1 or Condition 2, thus are customizable.

Based on these two observations, Figure 3(a) illustrates a radix-2 KSA in a reorganized form, highlighting the three stages, where the two *Sub-Adder* structures in the middle take the form of two 8-bit KSAs. It is worth noting that, the Sub-Adders are only responsible for the computation of GP information for the corresponding bits of the same group. However, each is identical to the form of an 8-bit KSA, except that the interleaved bits (even and odd bits) are taken in each as inputs, instead of the consecutive ones as in a regular 8-bit KSA.

Thus, the two groups of a defect tolerant KSA, (as the two Sub-Adders) being independent from one another, can be replaced in block by another adder structure without affecting the functionality or the defect tolerance ability. As is shown in Figure 3(b), the corresponding Sub-Adders are replaced by Brent-Kung Adders (BKA's). Such a replacement can be done in general with any PPA structure, thus opening up new choices in defect tolerant designs.

On the other hand, due to the presence of two disjoint groups, and the convenience of computing the results of one group using the results of other, the hardwares for a group can simply be eliminated that make the group dependent on the other group of results. This creates the basic idea for *sparse adders*.

Figure 3(c) then shows that the 2-Sparse version of a KSA is achieved in three steps: 1) segregating even and odd bits by the first layer of GP operators; 2) eliminating the computations of one group (the even bits) as Non-Essential Bits; 3) derive the final results of the Non-Essential Bits by adding a layer of GP-blocks at the output end, from the results of Essential Bits.

From the above observations it is then possible to generalize a 2-Sparse KSA with other types of Sub-Adders, as is shown in the example of Figure 3(d). Note that as long as the first layer of GP-blocks (denoted as Group-Segregation) is present, two independent and mutually substitutable groups (even and odd bits) are formed. From then on, one group (the odd bits) can be designated as the Essential Bits, and it can use any form of PPA structure as a Sub-Adder. The associated GP operators for the other group will be eliminated as these even bits now constitute the Non-Essential Bits. Eventually their results will be derived from the Essential Bits via the last layer of GP-blocks at the output side (denoted as Residual GP Restoration).

#### 2.3 Defect Tolerant Parallel Prefix Adders

#### 2.3.1 Motivations and Previous Works

The scaling down of device dimensions into the nanometer range is likely to result in significantly higher defect rates during the manufacturing process of IC's (ITRS, 2015). With significantly increased defect rates, defect tolerance mechanisms are necessitated to guarantee a reasonable yield. Post manufacturing reconfiguration techniques to bypass defects are already applied in memory systems and FPGA's (Shi and Fuchs, 1992) (Hatori et al., 1993). However, such low-cost defect tolerance techniques rely heavily on the relative independence of operations of the homogeneous components, such as LUT and memory cells. Logic systems, on the other hand, usually constitute heterogeneous components

with strong dependencies among each other. This makes it hard to realize fine-grained, low-cost defect tolerance schemes for a high level of defect rate.

In the first part of this chapter, we focus on the design of highly defect tolerant PPA's. Multiple papers have addressed the reliability issues in general adders. For instance, defect tolerant designs are proposed in (Kahng and Kang, 2012), (Ye et al., 2013) where an adder can be configured for its approximate computation, according to the amount of accuracy required in an application. (Townsend et al., 2003) applies quadruple time redundancy for an adder to tolerate error occurrences. The work in (Johnson, 1989) applies Triple-Modular Redundancy with a voter to guarantee the correct result. (Ghosh et al., 2007) uses a mechanism to stretch the clock period to accommodate the critical delay paths, with minor performance sacrifice. Even though these designs have a relatively low hardware cost, they mostly assume a low level of defect occurrences, and cannot scale when defect rates are high.

Among the various adders, PPA provides a general form to represent a wide range of adder design choices (Parhami, 2010). Reliable PPA designs have mostly been done on the particular form of Kogge Stone Adders (KSA), due to its inherent regular structure and hardware redundancy. For performance purposes, the hardware of a typical KSA is divided into two disjoint groups of the even bits and the odd bits. This provides a natural way to make the defects *isolated*: errors caused by the defects in one group will not affect the results produced by the other group. Furthermore, the in-built redundancy in a KSA allows each group to be capable of generating the results for the other group, with a small hardware and time overhead. Based on these features, defect tolerance mechanisms are proposed in (Ndai et al., 2007) (Ghosh et al., 2008) for KSA's, where as long as one of the two groups is defect-free, all the computations are done using the defect-free half of the adder to ensure correctness.

This section of work presents a general approach for defect tolerant PPA that is no longer limited to the special case for KSA. The proposed approach is a scalable solution along two dimensions: the number of disjoint hardware groups (beyond two), and the variety of PPA structures that can be adopted (beyond KSA). This provides enhanced reliability, as well as opens up a large number of design choices for defect tolerant PPA designs.

#### 2.3.2 The Proposed Defect Tolerant Design

Under a high defect rate, chances are exceedingly low that all the defects will be concentrating within only one group out of two. Therefore, the number of groups needs to be increased to enhance the likelihood of having at least one defect free functional group. Such an expansion on the number of groups can be achieved by exploring higher radices (Gurkayna et al., 2000). The radix of a PPA is defined by how many maximum " $\circ$ " operations are done inside a single GP Block. A radix-3 KSA example is shown in Figure 4, with 3 disjoint groups: Group 2 (bit Mod 3 = 2), Group 1 (bit Mod 3 = 1) and Group 0 (bit Mod 3 = 0). Defect tolerance can be achieved in this case, by letting each group generate two additional results for the other two groups. With every bit having 3 copies of the result, at least one defect free group will ensure the success of the defect tolerance mechanism. Overall, increasing the number of disjoint groups raises the level of defect tolerance.

Figure 5 shows a generalized example of the proposed design with 3 groups in a 24-bit PPA. The Group-Split stage resembles the first level of a radix-3 KSA, which guarantees that the computations of the 3 groups will be carried out by disjoint hardware. In the subsequent levels, the three groups (8-bit Sub-Adders) independently carry out the computations of GP signals. Their specific structure can be of any PPA design. In the end, at the Redundancy-Generation stage, two additional GP Blocks are

Figure 4: A 16-bit Radix-3 KSA ©IEEE 2016

Figure 5: An example of the proposed adder design approach with 24-bits and 3 groups ©IEEE 2016

added to each bit for the redundant results for the other two groups. As an example, bit 12 (belonging to Group 0) generates a copy of its result from its own group's hardware. In addition, one redundant copy is derived by:  $(G_{12:12}, P_{12:12}) \circ (G_{11:0}, P_{11:0})$  from the result of Group 2, and another redundant copy  $(G_{12:12}, P_{12:12}) \circ (G_{11:11}, P_{11:11}) \circ (G_{10:0}, P_{10:0})$  is derived from the result of Group 1. As long as one group is defect-free, the correct result for every bit can be guaranteed by configuring the MUXes at the output end.

In the overall design, the extra hardware needed in the Group-Split stage and the final Redundancy-Generation stage is determined by the number of groups in the design. The type of Sub-Adders is determined independent of the group number. The entire defect tolerant PPA structure can thus be characterized by two parameters: the number of groups, and the type of the Sub-Adders.

We can formalize the design approach with k-groups by dividing the framework into the following multiple stages:

**Group-Split:** This stage takes the same form as the first level of a radix-*k* KSA, where bit *i* interacts with bits (i-1), (i-2), (i-3), till (i-k+1) to generate  $G_{i:i-k+1}$  and  $P_{i:i-k+1}$ . Thus each bit  $(i \ge (k-1))$  requires a *k*-input GP Block at this stage. This stage forms the the *k* groups, which will be independent of each other with disjoint hardware.

**Sub-Adders:** Once the groups are formed, all the bits are computed via a corresponding Sub-Adder: bit *i* will be grouped with bits  $(i \pm k)$ ,  $(i \pm 2k)$  and so on, to be processed by the  $(i \mod k)^{th}$  Sub-Adder. For *k* groups, there will be *k* Sub-Adders. At this stage, the Sub-Adders can be of any PPA design. For bit *i* in a group (Sub-Adder), the following operations are performed to compute  $G_{i:0}$  and  $P_{i:0}$ :

$$(G_{i:0}, P_{i:0}) = (G_{i:i-k+1}, P_{i:i-k+1}) \circ (G_{i-k:i-2k+1}, P_{i-k:i-2k+1}) \circ (G_{i-2k:i-3k+1}, P_{i-k:i-3k+1}) \circ \dots$$

$$\circ(G_{i-mk:0}, P_{i-mk:0})$$

In this equation, (i - mk) is any bit where (i - mk) < k and  $(i - mk) \ge 0$ . The bits i, (i - k), (i - 2k), ... (i - mk) belong to the same group, such that (i - mk) < k and  $(i - mk) \ge 0$ , are part of the same group. The corresponding Sub-Adder is responsible for the computation of  $G_{i:0}$  and  $P_{i:0}$ .

**Redundancy-Generation:** At this stage, each bit generates (k - 1) additional results by utilizing the extra GP Blocks. Specifically, bit *i* performs the following operations to generate redundant copies of its results  $i_1$ ,  $i_2$ ,  $i_3$  to  $i_{k-1}$ :

$$i_1 = (G_{i:i}, P_{i:i}) \circ (G_{i-1:0}, P_{i-1:0})$$

$$i_2 = (G_{i:i}, P_{i:i}) \circ (G_{i-1:i-1}, P_{i-1:i-1}) \circ (G_{i-2:0}, P_{i-2:0})$$

...

$i_{k-1} = (G_{i:i}, P_{i:i}) \circ (G_{i-1:i-1}, P_{i-1:i-1}) \circ \dots \circ (G_{i-k+2:i-k+2}, P_{i-k+2:i-k+2}) \circ (G_{i-k+1:0}, P_{i-k+1:0})$

#### 2.3.3 Experimental Results

We carried out the simulation for the proposed defect tolerant PPA design with various instances using a C program. All the analyses are done on 64-bit adders, considering defects at the transistor level. This model assumes that any defective transistor will result in erroneous behavior is on the pessimistic side, and covers most of the interconnect defects as well. We analyze the reliability of various PPA implementation at the Sub-Adder stage, and the associated hardware requirements, with KSA, Han-Carlson (HCA), Ladner-Fischer (LFA), Brent-Kung (BKA) and Ripple-Carry (RCA) as the Sub-Adders.

The proposed PPA design is compared with a standard N-Adder defect tolerance approach: one out of *N* adders is selected by a MUX to be used for defect tolerance. Thus, as long as one of the adders is defect free, the defects can be tolerated. In this way, an N-Adder approach is comparable to an *N*group configuration of the proposed approach, except that the redundancy is organized "externally" in an N-Adder approach, rather than "internally" as in the proposed approach. The N-Adder approach is similar in hardware cost to the N-Modular Redundancy (NMR) approach, However, an NMR approach requires the majority of the adders to function properly for the correct result to be voted out, to deal with dynamically occurring faults. An N-Adder approach, on the other hand, requires only a single adder to be defect free to bypass defects that have been diagnosed.

In both the proposed approach and the N-Adder design, a block of MUXes is needed to select the correct output. The correctness of such a reconfiguration block is crucial for the entire defect tolerance scheme. Thus we assume that in both the cases, it is guaranteed reliable without any defects, possibly by adopting highly reliable devices.

To maintain the generality in the proposed approach for devices with any dimension, we evaluate the quality of the proposed design approach with the following generic parameters:

**Reliability** is calculated by randomly generating a set of defective devices, and determining if the defect can be tolerated in the adder. This is done for 1000 times, and the reliability is determined by *the ratio of the successful cases to the total number of cases* (1000) considered.

**Performance** (and also **Delay**) is indicated by the *sum of fan-ins of the GP Blocks along the critical path.* From (Gurkayna et al., 2000), it is known that an *n*-input GP Block usually has less than n/m times more delay than an *m* input GP Block, when n > m. In this paper, we evaluate the performance of GP Blocks via the lower bound case of their number of inputs. Thus, we consider 2-input GP Block 1.5 times faster than 3-input GP Blocks and 2 times faster than 4-input GP Blocks, etc. In this way, the sum of fan-ins of the GP Blocks along the critical path indicates an upper limit of the delay, or the lower limit of performance. As an example, a 64-bit 1-group RCA has a fan-in sum of the GP-Blocks along the critical path equal to  $126(=63 \times 2)$ , whereas, a 64-bit 4-group RCA has the same fan-in sum of 34 (4 for Group-Split stage and 30 for Sub-Adder stage)+ additional degradation due to Redundancy-Generation stage. The possible values for additional degradation can be either 0 for no defect condition, or 2, 3, or 4 depending upon the number of defective groups. Thus, the fan-in sum along the critical path can be either of these values: 34, 36, 37, or 38.

Required **hardware** is measured by the total number of transistors required for CMOS implementation. Basically, an *i*-input GP Block will require  $(6 \times i) + 2$  number of transistors (including both PMOS and NMOS transistors).

In this section, by an adder with certain number of groups, we mean the type of adder used in the Sub-Adder section of the proposed structure. As an example, by a 64-bit RCA with 4 groups, we mean that the structure has an input of 64-bits, with 4 groups, each of type RCA of 16-bits.

## 2.3.3.1 Reliability Analysis

Figure 37 shows the reliability analysis for various 64-bit BKA's. Each reliability curve is plotted with defect rates at the transistor level, shown for 2 to 6 groups. Reliability (represented in percentage)

Figure 6: Reliability Analysis for the proposed design with 64-bit Brent-Kung Adder ©IEEE 2016

is given by the ratio of the number of instances where the defects are tolerated, to the total number of trials.

Figure 37 verifies the effect of increasing the number of groups, which consistently delivers enhanced reliability. As an example, for BKA with transistor level defect rates of 0.1%, 2 groups can only tolerate the defects for less than 20% of the time. Reliability is increased to more than 70%, when the number of groups is increased to 4. It can be further enhanced to more than 90% if the number of groups is 6. This trend of enhanced reliability due to increased number of groups is generally observed to be true for all types of Sub-Adders.

Figure 7 depicts the reliability comparison between N-Adder and the proposed approach for 64-bit BKA's. The proposed scheme is superior to the N-Adder approach in both cases of N = 3 and 5. This is because for an N-Adder approach, a single defect is enough to deem an adder unusable. In the proposed approach, since the Redundancy-Generation stage is significantly large, any defect there will leave more

Figure 7: Reliability comparison between the proposed design versus the N-Adder approach with 64-bit Brent-Kung Adder ©IEEE 2016

room for the actual adder to perform without any error affecting it. We will show that the reliability gap between N-Adder (and thus NMR) and the proposed approach for higher performance adders to be even greater.

## 2.3.3.2 Expansion of Reliable PPA Design Space Choices

In Figure 8, various designs from the proposed approach is shown together with the N-Adder based approach to illustrate their positions in the design trade-off space. Comparison is done by considering three metrics: reliability, transistor number, and delay (indicated by the sum of fan-ins of the GP Blocks along the critical path).

Figure 8(a), (b) and (c) show the design of PPA's that can meet the reliability requirements of > 50%, > 70%, and > 90%, respectively, under a defect rate of 0.1%.

Figure 8: Design trade-off points for various 64-bit adders at 0.1% defect rate ©IEEE 2016

Overall, for the N-Adder approach, only simple types of adders such as RCA and BKA can meet the reliability requirements, while higher performance adder designs (such as KSA, HCA etc) fail to deliver even > 50% reliability. In fact, no other N-Adder approaches other than RCA can deliver a reliability of > 70%. The proposed scheme, however, can deliver a number of solutions with RCA, BKA, LFA, HCA and KSA that meet various reliability requirements. Overall, the low delay, high performance region is dominated by the proposed design approach, while the N-Adder approach occupies the complementary region where the delay is high and the hardware requirement is low. Overall, the proposed design approach expands the design space by delivering highly reliable PPA's of a variety of types for any given defect rate.

## 2.3.3.3 Delay Variation in the Proposed Scheme

The proposed approach results in some performance variations over a non defect-tolerant single group PPA:

1) An *n*-bit *k*-group design with the same type of adder structure at the (parallelly operating) Sub-Adder stage will have each of the Sub-Adder to be (n/k) bits wide, and effectively reducing the delay due to parallelism, compared to the same adder structure of an original *n*-bit implementation.

2) With the increasing number of groups, the number of inputs to each GP Block in the Group-Split stage increases, thus adding delay to the critical path. In addition, the presence of higher input GP Blocks at the Redundancy-Generation stage also introduces extra delay, particularly for tolerating a higher number of defects.

For lower-performance adders (such as RCA), factor 1 is dominant due to reduction in delay in linear scale, while the performance degradation is negligible in comparison. It is evident from Figure

8, a 4-Adder approach has a delay of > 120, while the comparable 4-group approach has a delay of < 40, effectively delivering 3-fold performance enhancement. For higher performance adders, factor 2 is dominant, since the reduction in the total delay due to factor 1 occurs in a logarithmic scale. However, as is shown in Figure 8, the performance degradation for BKA, LFA, HCA and KSA are negligible with the increasing number of groups, in the proposed approach.

## 2.4 Sparse Parallel Prefix Adders

## 2.4.1 Motivations and Previous Works

With the advent of low-power high-performance design regime, it is important to choose the right component which delivers the most fine-grained optimal design trade-offs. Adders, being one of the most common and important components of any computing platform, are one of the most suitable candidates for such design space explorations. In this section, we provide a unified framework to achieve more design choices by considering *Sparsity* of adders.

A *k*-Sparse adder computes the Block-level GP results (stage 2 of a PPA) only from every  $k^{th}$  bit (denoted as **Essential Bits** thereafter), and use their results to derive results (of stage 2) for the remaining bits (denoted as **Non-Essential Bits**). Sparse adders are useful to explore supplementing designs for the existing PPA's, which differ slightly from the original adder in terms of power-performance-area metrics. Thus, exploration sparsity is important if small fine-tuning is needed in the design.

This section focuses on general Sparse PPA's as an extension of Group Segregation property of KSA discussed in the beginning of the current chapter. A framework is proposed to derive various sparse designs for any existing PPA structure. The resultant approach opens up a large set of available

PPA designs, with various combinations of structures and sparsities, such that a designer can choose among them along the Pareto-front.

Sparse PPA's have been proposed in (Aktan et al., 2015) (Matthew et al., 2003) to explore additional performance-power trade-offs. Sparse PPA's are constructed by allowing only a subset of bits (denoted as "Essential Bits" in this paper) of the entire adder to compute their own results, with the rest of the bits (denoted as "Non-Essential Bits") deriving their results from the Essential Bits. Such a "sparse" design enables more varieties of PPA structures and thus facilitating design space trade-off explorations.

In the field of general PPA design, (Liu et al., 2007) (Roy et al., 2014) propose ILP based approaches to obtain a PPA structure satisfying a given set of constraints such as area, power, and performance. These approaches are able to search within the huge design space of possible structures, to obtain a PPA that meets the specifications. However, the runtime complexity is high, and these approaches do not provide a ready set of PPA's for the designers to choose from.

Among the previous works: (Zlatanovici et al., 2009) proposes Sparse PPA's by considering the radix and lateral fanout at each stage of the adder; (Aktan et al., 2015) focuses on the the optimal sparseness of Koge-Stone and Ladner-Fisher Adders to minimize power; (Matthew et al., 2003) proposed an alternative sparse Ladner-Fischer Adder structure; (Zeydel et al., 2010) evaluated the various parameters (structure, wire length, sparseness etc) to understand the power-performance trade-offs. Other examples of Sparse PPA's include Conditional Sum Adder (Sklansky, 1960) and Carry Select Adder (Bedrij, 1962). Overall, most of the previous work are either limited to a narrow scope or ad-hoc in nature. There lacks a systematic framework of constructing Sparse PPA's in general.

| Sparsity | Number of<br>GP Blocks | Interconnect<br>Length | Power  | Delay |

|----------|------------------------|------------------------|--------|-------|

| 1        | 1                      | 1                      | 1      | 1     |

| 2        | 0.7875                 | 1.0404                 | 0.7527 | 0.65  |

| 4        | 0.8125                 | 1.0699                 | 0.7793 | 0.5   |

TABLE I: PARAMETERS FOR THE THREE DESIGNS SHOWN IN FIGURE 9, NORMALIZED TO THE 1-SPARSE DESIGN ©IEEE 2017

## 2.4.2 Design Approach for Sparse Parallel Prefix Adders

For a 2-Sparse design, the Group-Segregation and Residual GP Restoration are both straightforward in implementation, each consisting of one layer of GP blocks. However, extending from 2 to a *k*-Sparse design will significantly increase the overhead in these two building blocks. In fact, this is a necessary price to pay, when more than half of the bits are made Non-Essential. Moreover, a variety of design options can be explored to realize the functionalities of Group-Segregation and Residual GP Restoration.

## 2.4.2.1 Examples

Figure 9 shows three examples of 32-bit LFA's with 1, 2, and 4 Sparse structures. One can easily observe the reduction of fan-outs with increasing sparsity of the same PPA structure. Table 1 shows the corresponding parameters, normalized with respect to the default 1-Sparse design. The improvements in the number of GP Blocks required, power and delay can be observed with increased sparsity in LFA.

Figure 9: Various designs for 32-bit LFA's with changing sparsity ©IEEE 2017

On the other hand, longer interconnects are needed for LFA's with higher sparsities. The components of the design are discussed in the next subsections.

Figure 10: A variety of Group-Segregation Block structures ©IEEE 2017

## 2.4.2.2 Group-Segregation designs for *k*-Sparse PPA's

The Group-Segregation stage functions to "bootstrap" the Essential Bits, such that when they are sent through the Sub-Adder, no interactions are needed with the Non-Essential Bits. For 2-Sparse design, this means every Essential Bit (every  $2^{nd}$  bit) e needs to compute ( $G_{e:e-1}, P_{e:e-1}$ ) at the Group-Segregation stage. For a k-Sparse adder, every  $k^{th}$  bit e now needs to compute ( $G_{e:e-k+1}, P_{e:e-k+1}$ ), which is identical to a k-bit Block-level GP computation.

To form a *k*-bit block GP computation, design choices range from 1-level (using a *k*-input GP computation),  $\lceil log_2k \rceil$  - level (using 2-input GP computation), to k - 1 level (using Ripple-Carry-Adder fashioned sequential computation). Such choices are shown in Figure 10(a) to (c) for an example of

8-Sparse design. Note that the 1-level design shown in Figure 10(c) essentially employs a high *radix* (Gurkayna et al., 2000) GP Block with 8 inputs, which involves a large overhead internally within each GP operator. In the experimental result section, we choose the form in Figure 10(a), where the Group-Segregation always requires  $\lceil log_2k \rceil$  levels.

## 2.4.2.3 Residual GP Restoration designs for *k*-Sparse PPA's

For each of the Non-Essential Bit *n*, to achieve the final block GP signal of  $(G_{n:0}, P_{n:0})$  without a Sub-Adder, two tasks are required, both related to the nearest Essential Bit *e* to the right of *n* (assuming n > e). First, the Non-Essential Bit *n* needs to compute its *local* block GP signal of  $(G_{n:e+1}, P_{n:e+1})$ , and this can be done without the results from the Essential Bits. Then, once the results of the essential bit e,  $(G_{e:0}, P_{e:0})$  from the Sub-Adder is available, bit *n* will integrate the result of  $(G_{e:0}, P_{e:0})$  with its local  $(G_{n:e+1}, P_{n:e+1})$  to derive its own *global* block GP result of  $(G_{n:0}, P_{n:0})$ .

Figure 11 shows various structure options for *Residual GP Restoration*, corresponding to the Group-Segregation stage given in Figure 10. The design choice of the Residual GP Restoration stage should mirror that of the Group Segregation, so as to maximize the reusability of intermediate results and minimize hardware overhead.

Overall, similar to Group-Segregation, the Residual GP Restoration has various structural options with different complexities and performance. In the experimental result of this paper, we select the structure of Figure 11(a), which matches that of Figure 10(a).

Figure 11: Various Residual GP Restoration options ©IEEE 2017

## 2.4.2.4 Overall Design

An overall design framework of an *m*-bit *k*-Sparse PPA is shown in Figure 12. The structure starts with the **Group-Segregation** stage, which provides the initial block GP signals for all the  $\lfloor m/k \rfloor$  Essential Bits (shown in bold lines), enabling them to carry out their independent computations later on.

Next, all the Essential Bits are channeled to the  $\lfloor m/k \rfloor$  Sub-Adder. This building block will compute (with any choice of PPA structure) the final block-level GP signals for each Essential Bit  $e: (G_{e:0}; P_{e:0}).$

Figure 12: Overall design structure of an *m*-bit *k*-Sparse PPA ©IEEE 2017

In parallel with the Sub-Adder, the  $(m - \lfloor m/k \rfloor)$  Non-Essential Bits (shown in thin lines) are sent to the **Residual GP Restoration** building block. Here, the Non-Essential Bits first produce the local Block GP signals, in parallel with the computation being carried out at the Sub-Adder. Then, the results from the Sub-Adder are taken in to derive the final block GP  $(G_{n:0}, P_{n:0})$  for every Non-Essential Bit *n*.

With increased sparsity, more computations are needed for the Non-Essential Bits, while the necessitated computations for the Essential Bits gradually decrease. As a result, when sparsity increases, the Residual GP Restoration block expands, while the Sub-Adder (with fewer number of input bits) block shrinks.

## 2.4.3 Associated Metrics

We follow the metrics provided by (Liu et al., 2007) for estimation of area, interconnect, power and performance. The estimations given here can be scaled according to any given feature size.

**Area** can be represented by two factors: 1) area required by the adder given in the coordinate system shown in Figure 13; 2) number of GP Blocks in the design.

To estimate the **interconnect** requirements, we model the length of an interconnect to be equal to half of the perimeter of the smallest rectangle encompassing the source and the destinations of the interconnect, as shown in Figure 13.

**Power** (*P*) has two components: static and dynamic power. **Static** ( $P_s$ ) power can be assumed to be fixed for a given GP Block. Thus, the static power consumed by the adder is proportional to the number

Placement of GP Blocks in Coordinate system and area optimizations

Figure 13: Representing an arbitrary PPA in a 2D space using Cartesian Coordinates, and estimation of interconnect lengths via half-perimeter method ©IEEE 2017

smallest rectangle that encompasses all the GP Blocks

of GP Blocks (|GP|). On the other hand, **dynamic** ( $P_d$ ) power is proportional to the fan-outs (fo) of the GP Blocks. Overall, the power can be estimated as:

$$P = P_s + P_d = a \times \sum fo + b \times |GP|$$

Here *a* and *b* are scaling factors, which we assume to be 1 and 0.5 respectively.

To estimate the performance in terms of delay (D), we use the concept of logical effort. (Liu et al., 2007) simplifies it as:

$$D_l = 1.5 \times C + 2.5, D_r = 2 \times C + 2.5$$

Delay is estimated from the critical path in the adder. If a GP Block is located along the critical path and the critical path enters it from right fan-in, then we consider the delay to be  $D_r$ . Otherwise when the fan-in comes from the left, the delay at the GP Block is considered as  $D_l$ . Computation of the overall delay is performed by considering all the GP Blocks along the critical path, and the fan-in paths of the critical path. In the given equations, *C* indicates the load capacitance for the corresponding GP Block, which is proportional to its fan-out. We apply a scaling factor of 0.5 to estimate  $C = 0.5 \times fo$ .

## 2.4.4 Experimental Results

A number of PPA structures including KSA, HCA, LFA, BKA (Brent-Kung Adder) and RCA are explored to evaluate their sparse variations. We evaluated 64-bit adders with sparsity ranging from 1 to 8. The results shown in Figure 14 indicates the results (area, interconnect, GP block number, power, delay, and Power-Delay Product) for each type of PPA when sparsity changes. The simulation was carried out using the metrics described in Section IV and implemented in a C program.

For high performance adders, such as KSA, a general trend is that delay is the only negative impact of increased sparsity. All other metrics show improvement with a more sparse design. For HCA, a design of sparsity 3 provides an optimal case in power, while sparsity of 2 provides an optimal point for the metric of Power-Delay Product (PDP) of all the choices.

For LFA's, which have a high fan-out for GP Blocks, increase in sparsity does not affect significantly area or interconnect. However, delay decreases consistently with increasing sparseness due to the fanouts decreasing. For power, we can observe an optimum point at sparsity of 3. PDP also has a downward trend, but the rate of reduction goes down as the sparsity increases.

Figure 14: Various metrics evaluated on 64-bit Sparse PPA's with changing sparsity on various PPA types ©IEEE

Figure 15: The 64-bit Adder Design space in power-delay domain ©IEEE 2017

Figure 16: A zoomed-in view of Figure 15 ©IEEE 2017

For BKA's, the power and PDP is lower at the typical 1-Sparse over other higher sparsity designs. Nevertheless, we can observe the presence of the fastest possible BKA at sparsity 6.

Finally, for RCA, while area, power, number of GP Blocks and interconnect length increases, there is a big performance improvement with increased sparsity. For instance, 2-Sparse RCA is almost twice as fast as a default 1-Sparse RCA. Furthermore, PDP also has a decreasing trend with increasing sparsity, indicating the presence of an exploitable power-delay trade-off.

Figure 15 shows the design space for the plethora of sparse PPA's, including KSA, HCA, LFA, BKA and RCA in power-delay domain. While KSA and RCA 1-Sparse and 2-Sparse designs are having a large variation between them in terms of power-delay, in most of the cases, the changes can be observed to be rather small. Such small changes have been shown in the zoomed-in plot of Figure 16. Thus sparsity exploration helps in "fine-tuning" the adder parameters as is shown in this region.

## CHAPTER 3

## FORMALIZATION OF REPLACEMENT CHAIN ALGEBRA IN ARBITRARY MANY-PROCESSOR SYSTEMS

*This chapter has been partially published as (Banerjee and Rao, 2015), (Banerjee and Rao, 2017b).* ©2015, 2017, IEEE.

## **3.1 Previous Works and Motivations**

This chapter introduces a k-Fault Tolerant (k-FT) system model supporting decentralized on-thefly repairs. The modeled system consists of n functioning Processing Elements (PE's) and at least kspare PE's. When a fault manifests, the repair is done indirectly by the spares through a "chain of replacements": the faulty PE is replaced by a functional PE in the neighborhood, which in turn is taken over by another functional PE in its neighborhood; these local reconfigurations continue until a spare is reached.

Classically, the fault tolerance problem in Many-PE system has been termed "Structural Fault Tolerance", since the aim is to maintain the original PE topology of the system. The most obvious way of achieving such a goal is via "global task mapping" onto a larger Many-PE network. This problem is essentially identical to a Sub-graph isomorphism problem: a classical *NP*-Complete problem. Thus its application is mostly concentrated in specific graph topologies, or small systems.

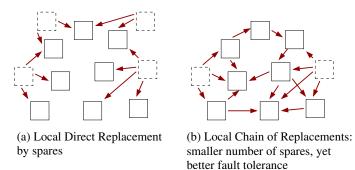

A computationally simpler solution is to replace the faulty PE directly using a spare, such as the one given in Figure 17(b). Although simple to implement, it suffers from a scalability issue: for larger sys-

tems, the number of spare required to maintain the fault tolerance grows significantly. This is because, to make sure every PE is repairable, spares have to be placed on every locality.

Thus, an alternative to this issue is to allow functional PE's, in addition to the spare PE's, to replace any other in the neighborhood, such as the system given in Figure 17(b). Using this approach, the spares, although small in number, can indirectly reach a faulty PE far away inside the system, using the "chain of replacements" approach. Since the reconfigurations are constrained within a neighborhood, it is the most scalable approach compared to others.

In this chapter, we propose a fault-tolerant system model following chain of replacements repair approach to maintain scalability. An additional challenge we address is: how to repair the system following every fault manifestation in a decentralized fashion on-the-fly without significantly affecting the normal operation of the system. This problem is challenging, since without knowing the future fault locations, the system has to do the best job possible to find a repair option to maximize future fault

Figure 17: Typical approaches for implementing fault tolerance in systems with multiple PE's

tolerance possibilities. This is an easier problem compared to the scenario where the system needs to repair k known faults.

To achieve the given goal, we include the following in this chapter:

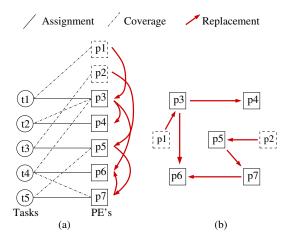

1. A 2-layered Task-PE Model which facilitates lightweight repairs on-the-fly after every fault manifestation for any arbitrary PE topology.

2. Necessary and sufficient conditions for guaranteeing k-FT in such systems.

3. Physical implementation of the model on popular 2D Grid structure.

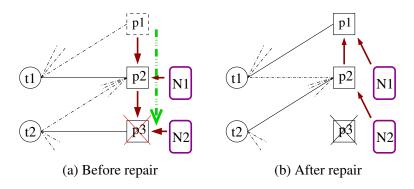

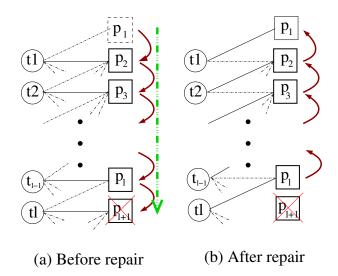

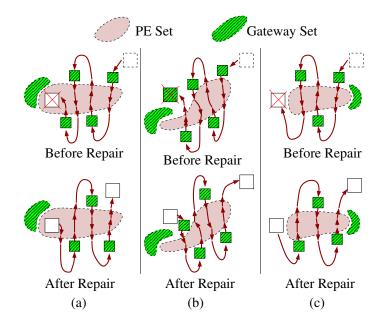

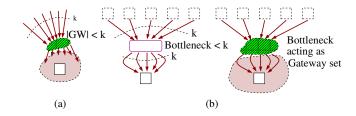

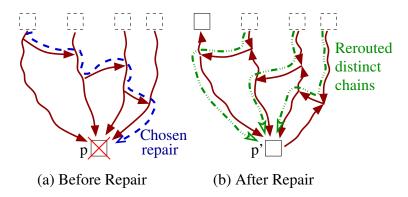

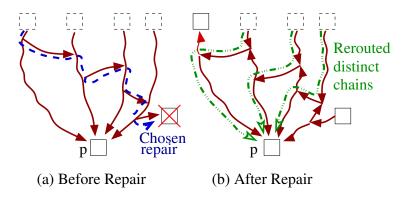

4. Construction of such system following the Task-PE Model.