## Soft-Switched Hybrid-Modulation for an Isolated DC-Link-Capacitor-Less Pulsating-DC-Link Inverter

$\mathbf{B}\mathbf{Y}$

ARASH RAHNAMAEE B.S., University of Tabriz, 2005 M.S., Amirkabir University of Technology (Tehran Polytechnic), 2008

### THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering In the Graduate College of the University of Illinois at Chicago, 2015

Chicago, Illinois

Defense Committee:

Sudip Mazumder, Chair and Advisor Danilo Erricolo Vahe Caliskan Sabri Cetinkut, Mechanical & Industrial Engineering Joydeep Mitra, Michigan State University This thesis is dedicated to my father "Houshang", mother "Flour", and my sister "Niloofar" who always provide me continuous love and support. I would also like to dedicate my thesis to my late grandpa "BabaAkhtari" who passed away during my doctoral study.

## Acknowledgement

I would like to thank my dissertation advisor and committee members—namely Sudip Mazumder, Danilo Erricolo, Vahe Caliskan, Sabri Cetinkut, and Joydeep Mitra—for their invaluable support and guidance throughout my research and study at University of Illinois at Chicago. I would also thank our director of graduate studies—Prof. Milos Zefran—for his unwavering help and support during my doctoral study.

AR

# **TABLE OF CONTENTS**

PAGE

**CHAPTER**

| I.   | INTRODUCTION                                                              |                                                                   |    |  |

|------|---------------------------------------------------------------------------|-------------------------------------------------------------------|----|--|

|      | A.                                                                        | Topology                                                          | 1  |  |

|      | B.                                                                        | Switching Scheme                                                  |    |  |

|      | C.                                                                        | Motivation and Objectives of Research                             |    |  |

| II.  | A DISCONTINUOUS MODULATION SCHEMES OPTIMIZED FOR HFPDCL INVERTERS         |                                                                   |    |  |

|      | A.                                                                        | DC-Modulated PDCL Waveform Discontinuous Modulation               | 14 |  |

|      | B.                                                                        | Hybrid Modulation                                                 | 20 |  |

|      |                                                                           | 1. Front-End DC/AC Converter Modulation                           | 21 |  |

|      |                                                                           | 2. Pulsating-dc/ac Converter                                      | 22 |  |

|      | C.                                                                        | Conclusion                                                        |    |  |

| III. | SOFT-SWITCHED HYBRID MODULATION                                           |                                                                   |    |  |

|      | A.                                                                        | Synthesis of the PDCL waveform                                    | 27 |  |

|      | B.                                                                        | Soft-switched hybrid modulation for the pulsating-dc/ac converter | 31 |  |

|      | C.                                                                        | Modes of Operation                                                |    |  |

|      | D.                                                                        | Conclusion                                                        |    |  |

| IV.  | EXPERIMENTAL RESULTS FOR VALIDATING THE SOFT-SWITCHED HYBRID MODULATION42 |                                                                   |    |  |

|      | A.                                                                        | Output waveforms                                                  | 44 |  |

|      | B.                                                                        | ZVS Operation of the Soft-Switched HM Scheme                      |    |  |

|      | C.                                                                        | Efficiency and THD                                                |    |  |

|      | D.                                                                        | Conclusion                                                        |    |  |

| V.   | Exp                                                                       | ERIMENTAL RESULTS USING COMPACT AND MODULAR HFPDCL INVERTER       | 53 |  |

|      | A.                                                                        | Low-Input Voltage Design                                          | 53 |  |

|      | B.                                                                        | Hard Switched HM Scheme                                           |    |  |

|      | C.                                                                        | High-Input Voltage Design                                         |    |  |

|      | D.                                                                        | Conclusion                                                        |    |  |

| VI.  | SOFT-SWITCHED DISCONTINUOUS PULSE DENSITY PULSE WIDTH MODULATION SCHEME64 |                                                                   |    |  |

|      | A.                                                                        | Experimental Results                                              | 71 |  |

|      | B.                                                                        | Conclusion                                                        |    |  |

| VII. | Conclusion and Future Work                                                |                                                                   |    |  |

|      | A.                                                                        | Conclusion                                                        | 77 |  |

|      | B.                                                                        | Future Work                                                       |    |  |

| are  |                                                                           |                                                                   |    |  |

| CITI | ED LI                                                                     | TERATURE                                                          | 81 |  |

| APP  | END                                                                       | X                                                                 | 86 |  |

| VIT  | A                                                                         |                                                                   | 87 |  |

# LIST OF TABLES

| <u>TABLE</u> |                                                               | PAGE |  |  |  |  |

|--------------|---------------------------------------------------------------|------|--|--|--|--|

| I.           | SWITCHING SIGNALS FOR THE PULSATING-DC/AC CONVERTER.          | 25   |  |  |  |  |

| II.          | THE SPECIFICATIONS AND MAIN COMPONENTS OF THE HFPDCL INVERTER | 43   |  |  |  |  |

| III.         | THE SPECIFICATIONS AND MAIN COMPONENTS OF THE HFLDC INVERTER. | 53   |  |  |  |  |

| IV.          | THE SPECIFICATIONS AND MAIN COMPONENTS OF THE HFLDC INVERTER. | 59   |  |  |  |  |

## LIST OF FIGURES

| FIGURE |                                                                                                                                                               |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.     | A Simplified Topology of a three-phase transformer-less inverter2                                                                                             |  |

| 2.     | The conventional LF isolated inverters                                                                                                                        |  |

| 3.     | The comparison between a 150 W LF transformer and a 1250 W HF transformer3                                                                                    |  |

| 4.     | The general configuration of the HFL inverters4                                                                                                               |  |

| 5.     | A HF-ac/ac cycloconverter                                                                                                                                     |  |

| 6.     | Fixed-dc link HFL inverter                                                                                                                                    |  |

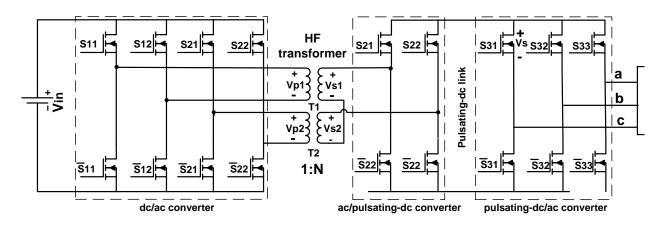

| 7.     | Schematic of a three-phase HFPDCL inverter7                                                                                                                   |  |

| 8.     | The modulation signals of the SPWM, THIPWM, and SVPWM schemes15                                                                                               |  |

| 9.     | Pulse placement and the generation of the dc-link waveform                                                                                                    |  |

| 10.    | Equivalent circuit of the pulsating-dc/ac converter and the HF pulsating-dc link16                                                                            |  |

| 11.    | The modified carrier signal for HFPDCL inverters                                                                                                              |  |

| 12.    | The modulation signal after injecting the zero sequence signal                                                                                                |  |

| 13.    | The sinusoidal encoded information on the PDCL waveform for the HM scheme20                                                                                   |  |

| 14.    | The modulation function of the dc/ac converter                                                                                                                |  |

| 15.    | The equivalent circuit of the PDCL and the pulsating-dc/ac converter22                                                                                        |  |

| 16.    | The modulation signal of the first leg of the pulsating-dc/ac converter24                                                                                     |  |

| 17.    | The switching signals of the pulsating-dc/ac converter using the HM scheme25                                                                                  |  |

| 18.    | Switching signal generation for the dc/ac converter (dc/ac modulator)                                                                                         |  |

| 19.    | Pulse placement on the PDCL using the dc/ac converter to provide zero states33                                                                                |  |

| 20.    | Switching signals generation for the pulsating-dc/ac converter                                                                                                |  |

| 21.    | A simplified operation overview of the inverter for the soft-switched HM34                                                                                    |  |

| 22.    | Switching functions and waveforms of the soft-switched HM35                                                                                                   |  |

| 23.    | Equivalent circuit of the ac/pulsating-dc converter, HF transformers, and the front-<br>end pulsating-dc/ac converter to study topological modes of operation |  |

# LIST OF FIGURES (Continued)

| 24. | Key waveforms of the equivalent circuit shown in Fig. 23 to study the soft-<br>switching operation of the pulsating-dc/ac converter                                                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25. | Topological modes of the equivalent circuit shown in Fig. 23 to study the soft-<br>switching operation of the pulsating-dc/ac converter                                                                  |

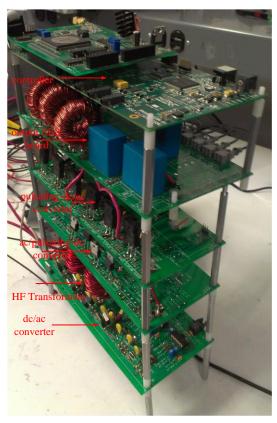

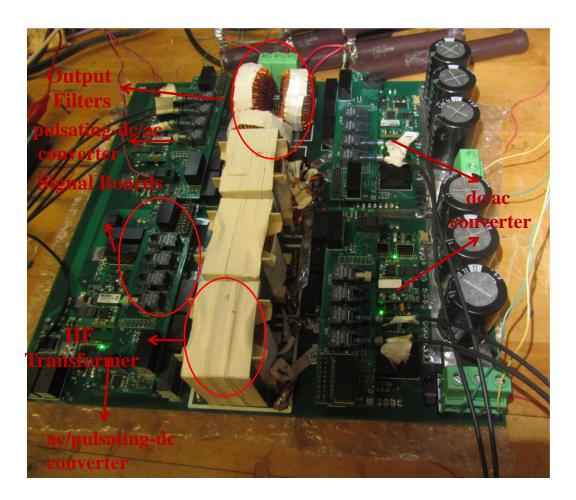

| 26. | The implemented prototype to validate the soft-switched hybrid modulation43                                                                                                                              |

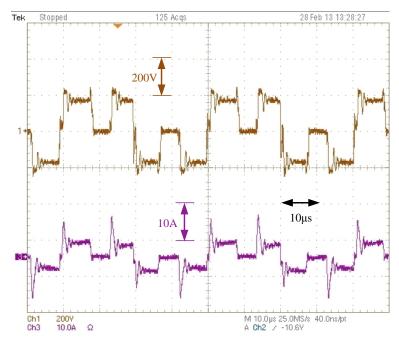

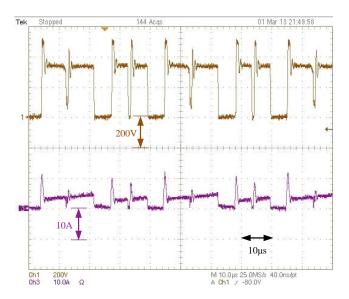

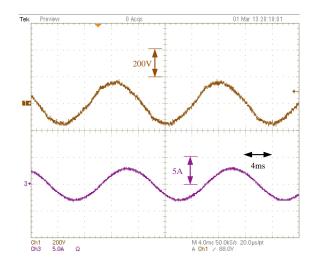

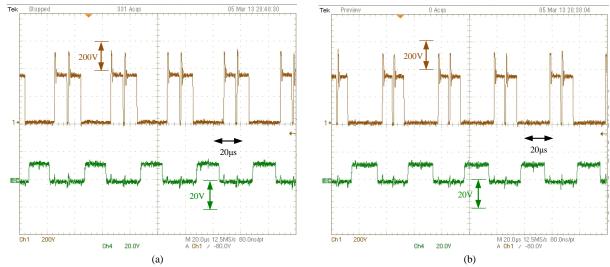

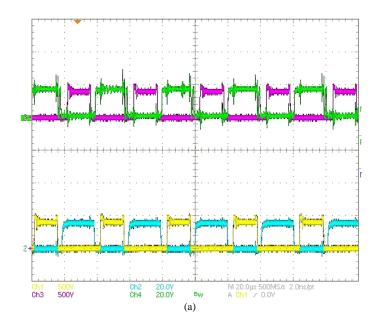

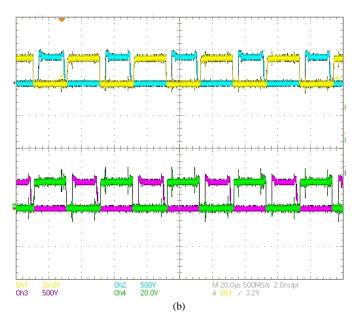

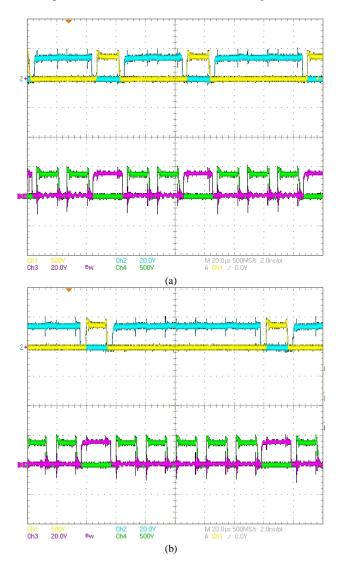

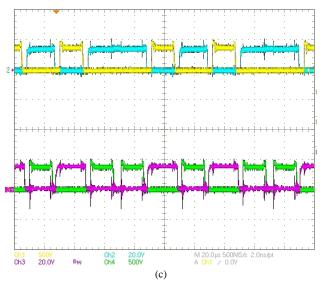

| 27. | The secondary-side voltage and current of a HF transformer of the inverter44                                                                                                                             |

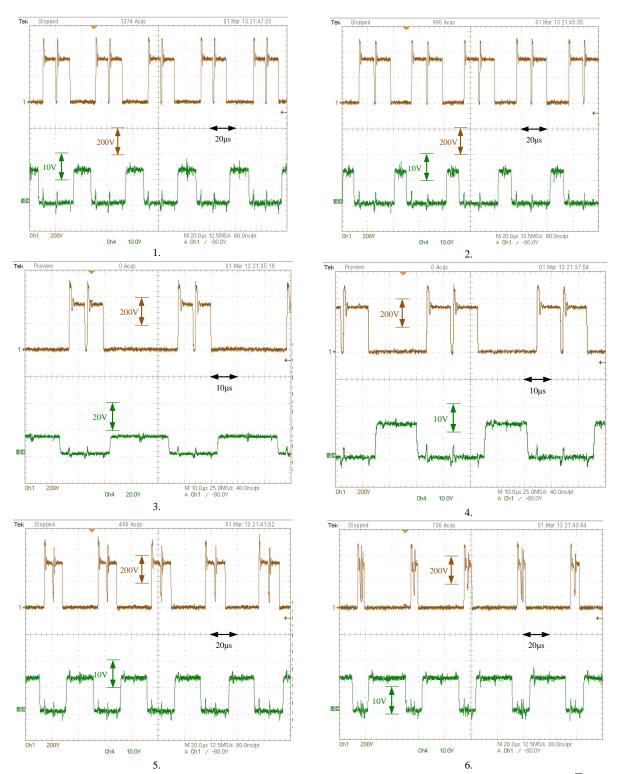

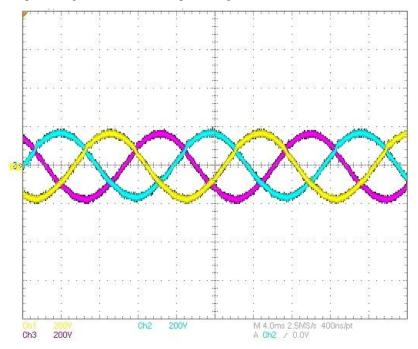

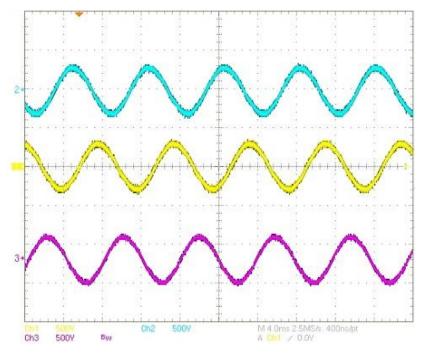

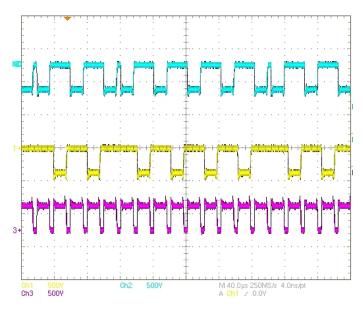

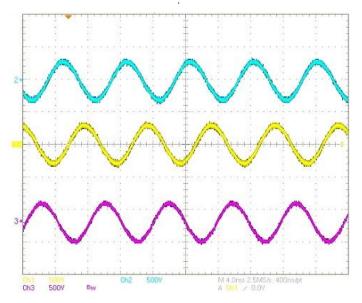

| 28. | PDCL voltage and current waveform of the HFPDCL inverter using the soft-<br>switched HM. Each switching cycle contains two pulses that represent different<br>output sine-wave reference voltage signals |

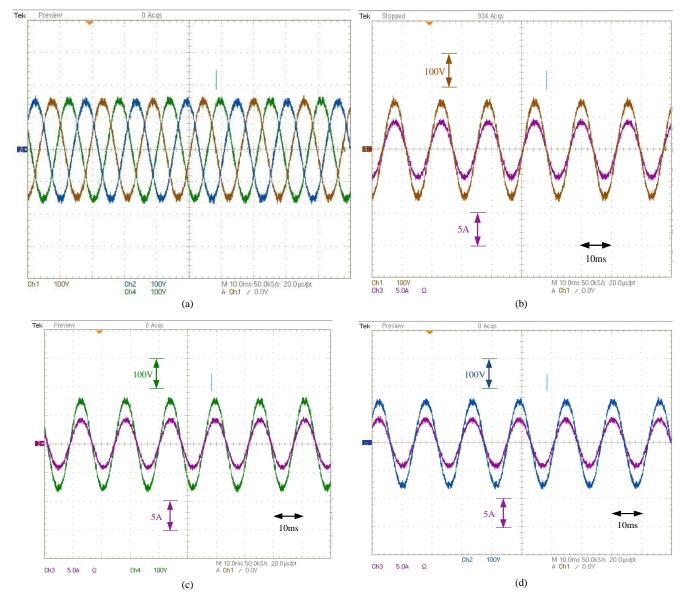

| 29. | Output phase voltages and currents for a 1-kW resistive load45                                                                                                                                           |

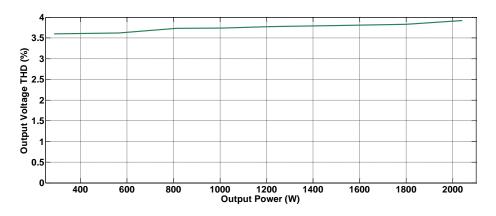

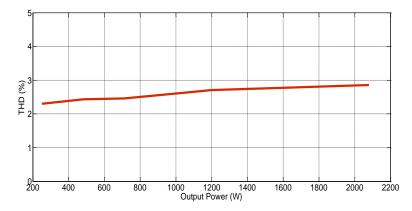

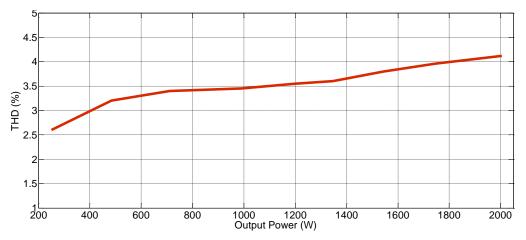

| 30. | Output current THD vs. output power of the inverter                                                                                                                                                      |

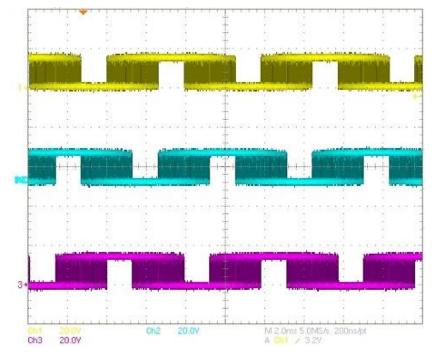

| 31. | Soft-switching operation of all switches of the pulsating-dc/ac converter47                                                                                                                              |

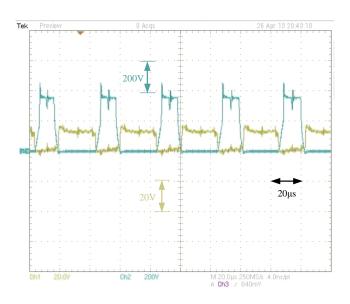

| 32. | The output phase voltage and current of a phase of the HFPDCL inverter when it supplies an induction motor                                                                                               |

| 33. | Soft-switching operation of the first leg of the pulsating-dc/ac converter when it supplies an induction load                                                                                            |

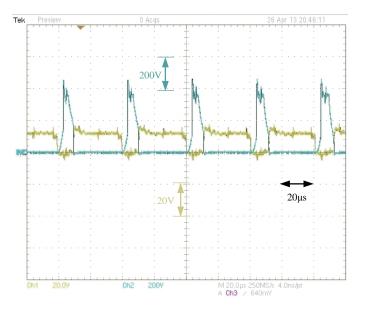

| 34. | The output voltage and current of a phase of the HFPDCL inverter when it supplies a nonlinear load                                                                                                       |

| 35. | Soft-switching operation of the first leg of the pulsating-dc/ac converter when it supplies a nonlinear load                                                                                             |

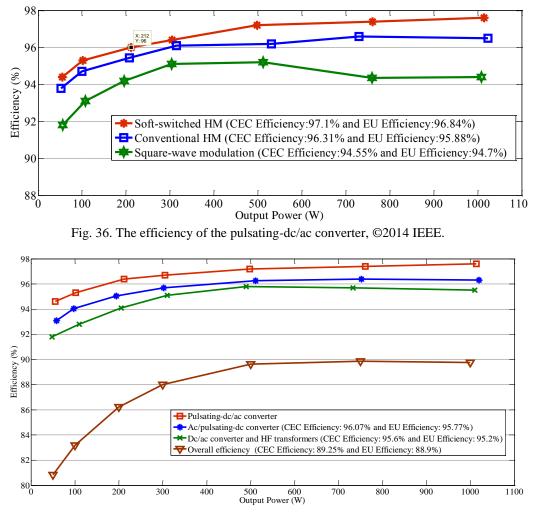

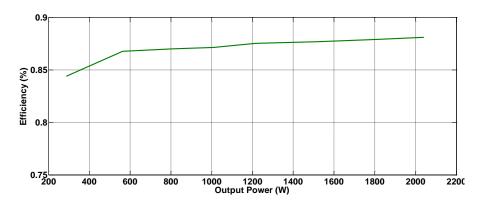

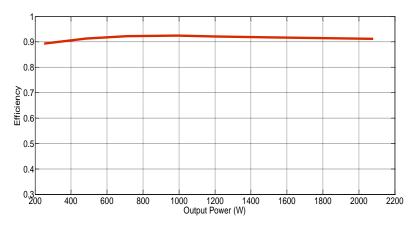

| 36. | The efficiency of the pulsating-dc/ac converter                                                                                                                                                          |

| 37. | The efficiency of the different stages of the HFPDCL inverter                                                                                                                                            |

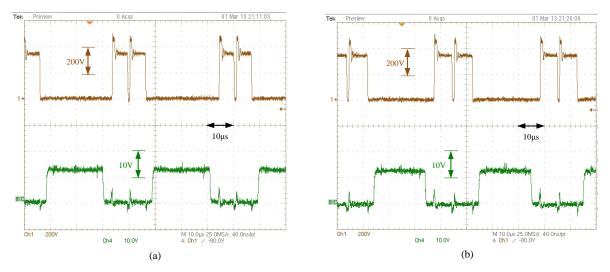

| 38. | The soft-switching operation of S <sub>31</sub> 51                                                                                                                                                       |

| 39. | The operation of the $S_{31}$ when the output power is 40W                                                                                                                                               |

| 40. | The implemented dc-link capacitor less HFL inverter                                                                                                                                                      |

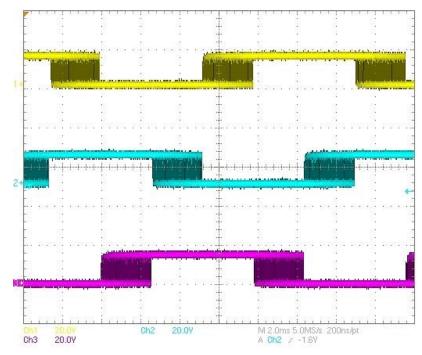

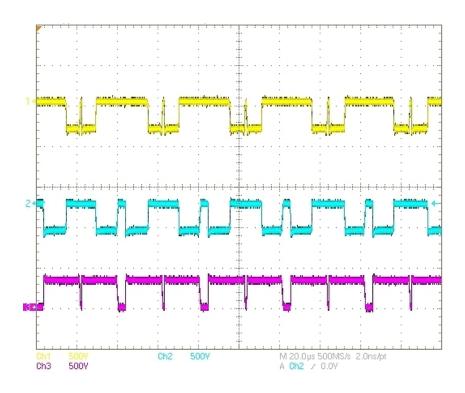

| 41. | The primary-side voltages of transformers and the PDCL waveform55                                                                                                                                        |

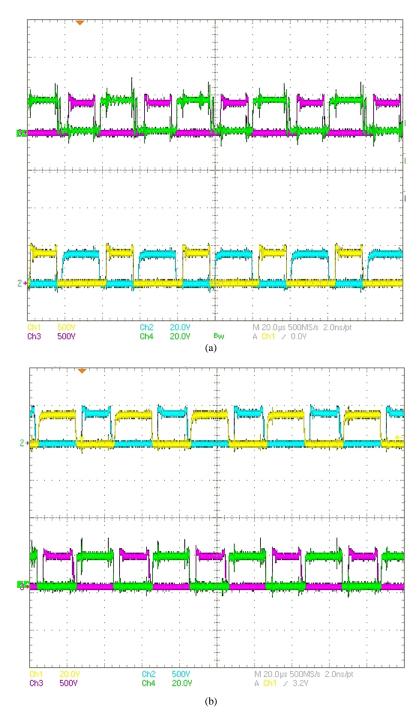

| 42. | The generated gate signals of the pulsating-dc/ac converter using the HM scheme 55                                                                                                                       |

# LIST OF FIGURES (Continued)

| 43. | The output voltage waveforms of the pulsating-dc/ac converter before the filter56                                         |

|-----|---------------------------------------------------------------------------------------------------------------------------|

| 44. | The three-phase sine-wave voltage waveforms using the HM scheme56                                                         |

| 45. | The THD of the output voltage waveforms for different output powers                                                       |

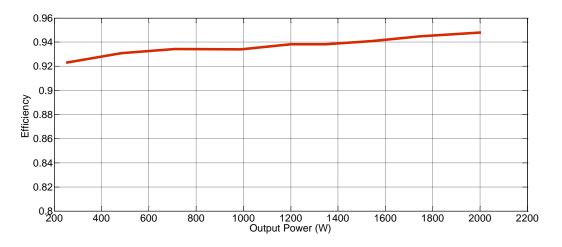

| 46. | The efficiency of the HFPDCL inverter for different output powers                                                         |

| 47. | The simplified schematic of a HFPDCL inverter using fully-controlled ac/pulsating-<br>dc converter                        |

| 48. | The output voltage waveform of the HFPDCL inverter using the presented discontinuous PWM scheme                           |

| 49. | The signals of the pulsating-dc/ac converter for the discontinuous PWM scheme61                                           |

| 50. | The overall efficiency of the HFPDCL inverter versus the output power62                                                   |

| 51  | The current THD of the HFPDCL inverter versus the output power                                                            |

| 52. | Soft-switching operation of all switches of the pulsating-dc/ac converter63                                               |

| 53. | The PDCL waveform when the dc/ac converter generates a stream of the pulses based on the maximum reference voltage signal |

| 54. | The dc-link waveform generation and ZVS of the pulsating-dc/ac converter67                                                |

| 55. | The switching signals of the pulsating-dc/ac converter using the HM scheme68                                              |

| 56. | The DPDPWM modulator of the pulsating-dc/ac converter during PI and PIV69                                                 |

| 57. | The DPDPWM modulator of the pulsating-dc/ac converter during PII and PV70                                                 |

| 58. | DPDPWM of the pulsating-dc/ac converter during PIII and PVI71                                                             |

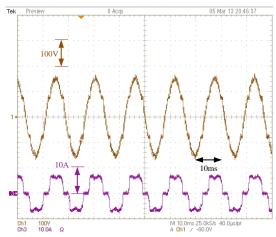

| 59. | The output voltage phase to phase waveforms before output filters72                                                       |

| 60. | The output sine waveforms of the HFPDCL inverter using DPDPWM scheme72                                                    |

| 61. | Soft-switching operation of the pulsating-dc/ac converter using DPDPWM73                                                  |

| 62. | The overall efficiency of the HFPDCL inverter using DPDPWM scheme74                                                       |

| 63. | The output THD of the HFPDCL inverter using DPDPWM scheme75                                                               |

| 64. | Soft-switching operation of the pulsating-dc/ac converter using DPDPWM76                                                  |

# LIST OF ABBREVIATIONS

| DPDPWM | Discontinuous Pulse Density Pulse Width Modulation |

|--------|----------------------------------------------------|

| HFPDCL | High Frequency Pulsating dc Link                   |

| HF     | High Frequency                                     |

| HM     | Hybrid Modulation                                  |

| LF     | Line Frequency                                     |

| PDCL   | Pulsating DC Link                                  |

| PDM    | Pulse Density Modulation                           |

| PV     | Photovoltaic                                       |

| PWM    | Pulse Width Modulation                             |

| THD    | Total Harmonic Distortion                          |

| ZCS    | Zero Current Switching                             |

| ZVS    | Zero Voltage Switchng                              |

#### SUMMARY

The main goal of this dissertation is to increase the performance of the capacitor-less highfrequency pulsating dc-link (HFPDCL) inverters suitable for renewable energy sources. The HFPDCL inverters are compact, small foot-printed, modular, and reliable since they do not employ large dc-link capacitors and line-frequency transformers. However, they require additional power conversion stages which increases the losses of the converter. The dc-link capacitor of the conventional fixed dc-link inverters provides a buffer stages for the inverter and it decouples the power conversion stages of the converter. Therefore, Power conversion stages of the HFPDCL inverters are not decoupled. As a result, they need a modulation scheme to synchronize the operation of the conversion stages and reduce the switching losses of the converter.

Auxiliary circuits conventionally are used to provide a soft-switching condition for power converters to reduce the switching losses. This increases the efficiency and performance of the converter. However, they require additional passive and active components. The modulation-based soft-switching schemes are a better solution since they do not require any additional components. Not only can they provide soft-switching for the converter, but they can also reduce the switching requirement of the converter. They use the pulsating dc-link feature of the HFPDCL inverters to provide soft-switching condition. The modulation scheme also needs to synchronize the operation of the different conversion stages of the HFPDCL inverters.

This dissertation presents modulation-based, soft-switching schemes to increase the performance of the HFPDCL inverters without using any auxiliary circuits. It reduces the switching requirement and provides a soft-switching condition to reduce the switching losses of the HFPDCL inverters to increase the overall efficiency. They also generate high-quality output waveforms with low total harmonic distortion (THD). The presented soft-switching modulation scheme operates

#### **SUMMARY** (Continued)

based on the pulsating nature of the dc-link of the HFPDCL inverters. The three presented modulation schemes are as follows: 1) a discontinuous modulation scheme that synthesizes the fixed-width pulses on the pulsating-dc link (PDCL) waveform, 2) soft-switched hybrid modulation that reduces the switching requirement of the output inverter of the HFPDCL inverter and provides a soft-switching condition for it, and 3) a pulse-density pulse-width hybrid modulation (discontinuous modulation) to reduce the switching requirement of the conversion stages of the HFPDCL inverter and provide a soft-switching condition for it.

Finally, two experimental setups are implemented to validate the performance of the presented soft-switched modulation schemes: 1) a discrete design that uses discrete silicon switching devices, and 2) a compact and modular design that uses power modules to increase the power density of the implemented HFPDCL inverter. The experimental results validate the performance of the presented soft-switched modulation schemes.

### I. Introduction

Renewable energy sources offer the promise of clean abundant energy gathered from resources such as sun, wind, earth, hydro power, geothermal, and biofuels. Renewable energy technologies show promising benefits compared to conventional energy sources [1]. Most renewable energy systems are modular and have the flexibility to match energy consumption growth [2]. Power electronic converters such as dc/ac converters (inverters) are the heart of renewable energy systems. They deliver power from a renewable energy source to a utility grid or a stand-alone load. The important aspects of the inverters are efficiency [3], cost [4], reliability [5], and power density [6]. Therefore, the inverters play a key role in harvesting power from renewable sources and delivering a proper AC power to consumers. The efficiency of the inverter is critical for the amount of power we can harvest from renewable energy sources and to maximize the power delivery to consumers [7]. The first step in the design procedure of the inverters is selecting a proper topology.

#### A. Topology

Transformer-less inverters show some advantages such as high efficiency, reliability, and a rather simple schematic [8], [9]. However, these topologies are not able to provide isolation for power electronic systems, which is a requirement in the USA and some parts of Europe. Additionally, ground current and noise issues make these topologies less attractive for distributed generation systems. Finally, transformer-less inverters cannot adapt the voltage level of the energy source to the voltage level of the load. Therefore, they are not suitable for energy sources with low output voltage such as photovoltaic and full-cell energy sources.

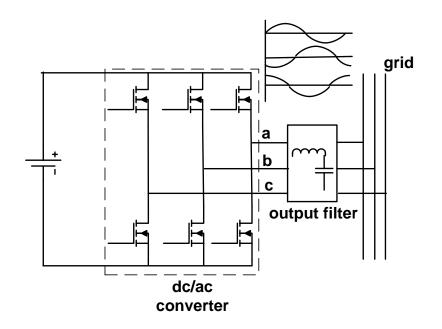

Fig. 1. A simplified Topology of a three-phase transformer-less inverter.

A simplified topology of a transformer-less grid-connected three-phase inverter is shown in Fig. 1. This topology only consists of one active stage. They usually are employed for low-power generation systems where galvanic isolation is not required. Consequently, it may lead to safety hazards in the case of any ground fault [10]. Park [11] presented a transformer-less topology for uninterruptible power supply (UPS) with relatively high efficiency and reliability. Lopez [12] and González [13] investigated a low-power, single-phase PV inverter to study the influence of the harmonics, injected by the inverter, on the ground current and investigate the leakage currents between the PV system and the ground. These issues show the troublesome performance of these inverters for high-power applications. As a result, this topology is suitable for low-power applications where galvanic isolation and ground currents can be neglected, such as small-distributed generation systems.

Line-frequency (LF) transformers are conventionally used to provide galvanic isolation and voltage scalability for power-electronic systems. They can be applied to applications such as UPS

[14], [15] and grid-connected inverters [16]. A simplified typical grid-connected three-phase inverter with a three-phase LF transformer is shown in Fig. 2. The LF transformer is connected after the output filters; therefore, it operates at LF. Krishnan [17] and Jain [18] investigated the performance of single-stage UPS inverters employing LF transformers. They reported reasonably good performance factors such as efficiency THD. However, LF transformers are bulky and heavy compared to high-frequency (HF) transformers. This not only decreases the power density of the system but also results in an increased cost of manufacturing and maintenance of the LF transformers.

Fig. 2. The conventional LF isolated inverters.

Fig. 3. The comparison between a 150 W LF transformer and a 1250 W HF transformer.

Fig. 3 shows a 150 W LF transformer and 1250 W HF (20 kHz) transformer. The shown HF transformer is much smaller than the LF transformer, even though its nominal power is almost 10 times higher than the LF transformer's. As a result, the LF transformers are the main obstacle to increasing the power density of the isolated power-electronic systems for distributed generation.

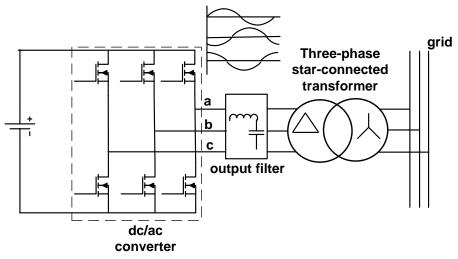

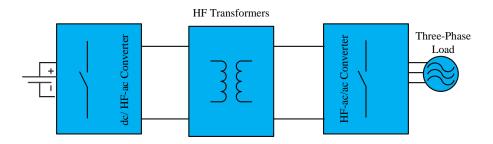

By developing high-frequency magnetic cores [19]-[21], high-frequency transformers can be used instead of the traditional LF transformers. Using HF transformers increases the power density of the high-frequency link (HFL) inverters. Therefore, HF transformers provide the required galvanic isolation and voltage scalability while dramatically decreasing the size of the transformers. The general configuration of the HFL inverters is shown in Fig. 4. The front-end dc/HF-ac converter generate bipolar pulses for HF operation of the HF transformers. A series of bipolar pulses are required to avoid saturation of the HF transformers. The output HF-ac/ac converter generates the desired output LF sinewave waveforms. The HF-ac/ac conversion stage can be a single stage or two stages.

Fig. 4. The general configuration of the HFL inverters.

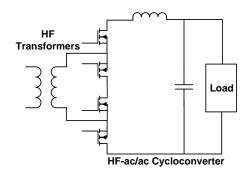

Fig. 5. A HF-ac/ac cycloconverter

The single stage HF-ac/ac converter consists of a three-phase cyclo-converter that requires bipolar voltage-block switching devices. Fig. 5 shows a single phase HFL inverter using a singlephase cycloconverter. Kan [22] presented a re-shaped single-phase HFL inverter using a HF-ac/ac cycloconverter to improve the performance of the cycloconverter-type HFL (CHFL) inverters. They developed a 500 W prototype to evaluate the performance of their proposed topology. They recorded an efficiency of 90% at a full output power condition. Rodrigues [23] proposed a softswitched three-phase inverter using HF-ac/ac cycloconverter at the secondary side of the HF transformers. The presented soft-switching scheme is modulation based. It also reduces the switching requirement of the HF-ac/ac converter by 33%. Researchers [24]-[26] also presented modulation and soft-switching schemes to reduce the losses of the CHFL inverters. This topology does not require dc-link capacitors, which reduces the size of the inverter. However, there is no freewheeling path for the current in the secondary-side cycloconverter. The cycloconverter used at the secondary-side of the inverter requires 12 switching devices, despite having only one conversion stage. As a result, this topology does decrease the number of the switching devices of the inverter. More importantly, this topology is not modular. Meaning that it cannot be implemented using standard bridge power modules.

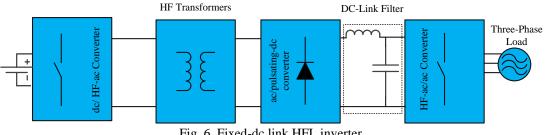

The two stage HF-ac/ac converters, as shown in Fig. 6, are conventionally comprised of a rectifier and a following dc/ac converter. The dc-link filter, comprised of an inductor and large dc-link capacitor, decouples the front-end conversion stages of the inverter from the output dc/ac converter. Therefore, the two front-end stages of the converter can independently operate as a dc/dc converter. The output dc/ac converter generates the desired LF output waveforms. The voltage of the dc-link capacitor is fixed. As a result, a large electrolytic capacitor is usually employed as the dc-link capacitor. This increases the size and decreases the reliability and power density of the

inverter. Electrolytic capacitors are the main cause of failure of power electronics systems because their lifetime is very sensitive to their operational temperature [27]-[29].

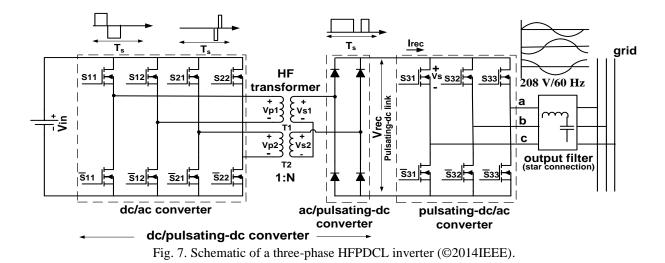

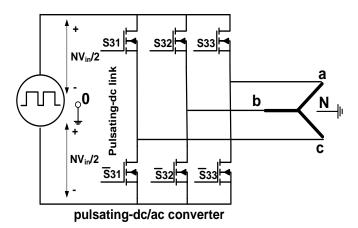

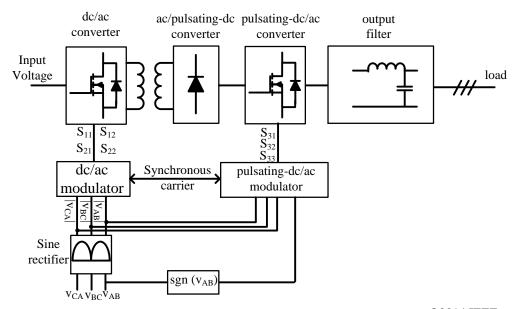

HFL inverters require more conversion stages than conventional inverters. This results in higher losses due to the higher number of switching devices. As a result, losses of the HFL inverters need to be decreased in order to increase the overall efficiency of the power electronic systems. HFPDCL inverters [30]-[37] have high-power density due to the elimination of the bulky dc-link capacitors and use of HF transformers. They do not need a faulty electrolytic capacitor, which results in a higher reliability than the fixed dc-link HFL inverters. Fig. 7 shows a simple schematic of a HFPDCL inverter that consists of two conversion stages: 1) a dc/pulsating-dc converter that comprises dc/ac converters, HF transformers, and an ac/pulsating-dc converter; and 2) a pulsatingdc/ac converter that generates the desired LF output waveforms.

Reference [30] used a small dc-link filter single-phase HFPDCL inverter to be able to synthesize the waveform of the dc-link. They generate a LF rectified sinewave voltage waveform at the dclink of the inverter to reduce the switching requirement of the output dc/ac converter. They reported a maximum efficiency of 87% for an implemented 1 kW HFPDCL inverter. Chen [31] proposed a single-phase HFPDCL inverter using a forward converter as the front-end dc/ac converter. The front-end forward converter provides the HF isolation of the inverter. They reported a low THD output waveform, and an efficiency between 80-85%.

Fig. 6. Fixed-dc link HFL inverter.

In [32], a multilevel HFPDCL inverter is proposed, which shows the proper performance of this topology for multilevel applications. Fujimoto [33] presented a novel single phase HFPDCL inverter using a fully-controlled synchronous ac/pulsating-dc converter. Their implemented 3 kW prototype showed an output THD below 5% and efficiency as high as 92%. Koutroulis [34] explained the design of a single-phase HFPDCL inverter. Their efficiency for 200 W prototype varies between 80% and 85%. Recent work by our group [35]-[37] has also shown the proper performance of the HFPDCL inverter for renewable energy sources.

#### B. Switching Scheme

HFL inverters have more conversion stages than the conventional LF isolated inverters. Therefore, the switching losses of the HFL inverters need to be addressed to increase the efficiency of the system. There are two soft-switching schemes available for HFL inverters: 1) soft-switching schemes using auxiliary circuits, and 2) modulation-based soft-switching schemes. Auxiliary circuits are conventionally used to provide soft-switching [38]-[41] conditions for isolated power converters. Yakushev and Han [38], [39] used an active clam, which consists of a switched-capacitor circuit, to provide a soft-switching condition for the switches of the full-bridge converter.

Tabias and Rivas [40], [41] used the concept of the resonant circuits to provide a soft-switching condition. All of these techniques require additional components. This results in a larger number of components and makes the topology of the HFL inverters more complicated. The passive and active components of the auxiliary circuits also result in some losses. More importantly, these approaches are load-dependent, and they are not usually effective for a wide range of operation conditions. Therefore, soft-switching schemes using no auxiliary circuits (modulation-based soft-switching schemes) are preferred over traditional soft-switching schemes using auxiliary circuits.

The PDCL feature of the HFPDCL can be used to decrease the switching requirement and switching losses of the HFPDCL inverters. It also eliminates the bulky filters of the fixed-dc link inverters. Therefore, the reliability and power density of the HFPDCL inverters are improved by elimination of the bulky electrolytic capacitors. However, multi-stage power conversion of the HFPDCL inverter requires a carefully designed switching scheme to reduce device losses and switching requirements of the inverter and to ensure the synthesis of the inverter output waveforms with acceptable harmonic distortion. As a result, a proper approach needs to be addressed to decrease the losses and increase the efficiency of the HFPDCL inverters.

Carrier based PWM modulation schemes [42], [43] have been developed based on the comparison of the modulation signals and a triangle carrier waveform. Discontinuous PWM schemes [44]-[48] reduce the switching requirement of the inverter compared to the conventional continuous PWM schemes. This decreases the switching losses and increases the efficiency of the inverter. This method of loss mitigation does not require any additional circuits in contrast to soft-switching methods using auxiliary circuits. In a cyclic manner, Discontinuous PWM clamps one predetermined leg of the pulsating-dc/ac converter to the dc-bus while the other legs of the converter operate at HF. Although different Discontinuous PWM schemes [49]-[53] are presented for the

fixed-dc link inverters, they are not optimized for HFPDCL inverters, where the nature of the dc link is pulsating instead of the conventional fixed dc. These presented discontinuous PWM schemes [49]-[53] decrease the switching requirement of the inverter. They can reduce the switching losses of the inverter by allowing no switching of one of the legs of the three-phase converter. Therefore, these schemes yield no commutation of a leg for a specific angular duration (e.g., 30° or 60°) of any line cycle. However, this still incurs HF switching of the remaining legs of the converter under hard-switching condition. They are developed based on the zero-sequence signal injection to the reference signals. They decrease the switching requirement of the inverters.

The modulation scheme described in [54] uses a square-wave modulation scheme. It uses the square-wave modulation for the dc/ac converter. Using such a modulation, the dc/ac converter generates a stream of pulses with fixed on-time width on the PDCL waveform. As such, a sine-wave modulation technique must be applied to the pulsating-dc/ac converter to generate the LF output voltage waveforms. Therefore, all the legs of the pulsating-dc/ac converter operate at HF under the hard-switching condition.

The originally proposed HM scheme (referred to as the conventional HM in this dissertation), described in [55]-[58], can be applied to the pulsating-dc/ac converter to decrease the switching requirements of the converter. Unlike the discontinuous-modulation schemes, the conventional HM scheme requires no HF commutation on two of the legs of the pulsating-dc/ac converter. Therefore, only one of the three legs operates under HF hard-switching condition. This additional reduction in switching is achieved by recognizing that if the dc/ac converter switches are sinusoidally modulated (emulating the inverter output), the PDCL waveform, representing the maximum (dc/ac-converter) phase-to-phase voltage, is also encoded with this sinusoidal information. This information is

exploited by the HM to reduce the switching need for the pulsating-dc/ac converter. Because the maximum phase-to-phase voltage of the dc/ac converter changes every 60° of the line cycle, the HM of the pulsating-dc/ac converter appropriately selects the two converter legs that are not switched in this 60° interval. Notwithstanding, switching loss incurred in the remaining converter leg (that is hard-switched) needs to be addressed.

As such, in this dissertation, a soft-switched HM scheme [59] is developed to provide a softswitching condition for the pulsating-dc/ac converter. A novel and fundamentally different modulation scheme must be applied to the dc/ac converter to enable soft-switched HM of the pulsating-dc/ac-converter switches. Using this scheme, the two predetermined legs of the pulsatingdc/ac converter are not switched in every 60° of the line cycle while the other leg works at HF but under soft-switching condition. Therefore, soft-switched HM scheme proposes a unique modulation mechanism for the dc/ac and the pulsating-dc/ac converters. However, this modulation increases the switching requirement of the front-end dc/ac converter and the rectifier. Therefore, a dual discontinuous pulse-density pulse-width modulation (DPDPWM-hybrid modulation) scheme to reduce the switching requirement of the dc/ac converter, the rectifier, and pulsating-dc/ac converter.

### C. Motivation and Objectives of Research

The switching losses of the HFPDCL inverters need to be decreased to increase the overall efficiency of the system. Although HFPDCL inverters consist of three active switching stages, they operate as a single stage power converter because the dc-link capacitors are eliminated from the power stage. The dc-link capacitor decouples the front-end and output converters of the HFL inverters. Therefore, the front-end dc/ac and the output dc/ac converters can be controlled

independently. As a result, the modulation scheme of the HFPDCL inverters needs to synchronize the operation of all the conversion stages due to the elimination of the dc-link capacitor.

HF transformers are used to provide galvanic isolation for the PDCL HF inverters. The power density of the HFL inverters is increased because of the high-frequency operation of the transformers in contrast to the inverters with line-frequency transformers. However, the leakage inductance of the HF transformers causes voltage spikes on the devices of the ac/pulsating-dc and pulsating-dc/ac converters. Therefore, a proper approach needs to be used to absorb the leaked energy of the HF transformers to limit the voltage spikes on the PDCL waveform. A carefully-designed and manufactured transformer can decrease the leakage inductance of the system. An RCD [60] clamp can also be used to absorb the leakage energy of the HF transformers and dissipate it to suppress the voltage spikes on the switching devices of the inverter. In addition, an active clamp [55] can also be used to recover the leakage energy and transfer it to the load or the input source.

Any random pulses can be synthesized on the PDCL waveform by the dc/ac converter because of the elimination of the dc-link capacitor. The synthesized pulses can be used by the pulsatingdc/ac converter to decrease the switching losses of the output stage of the HFPDCL inverter. There are two approaches to decrease the switching losses of the pulsating-dc/ac converter: 1) by decreasing the switching requirement and 2) by providing the soft-switching condition for the switching devices of the converter. The proposed approach in dissertation reduces the switching requirement of the HFPDCL inverter. Two predetermined legs of the pulsating-dc/ac converter clamp to the dc bus in 120° of the line cycle. Therefore, the switching requirements of the pulsatingdc/ac converter are practically decreased by 66%. The remaining leg of the pulsating-dc/ac converter can operate under ZVS condition to decrease the switching losses. As a result, the switching losses of the pulsating-dc/ac converter are practically mitigated. Therefore, the presented approach for mitigating the switching losses of the pulsating-dc/ac converter is provided without using any auxiliary circuit.

A unique switching scheme is required for the dc/ac converter to provide zero states on the PDCL waveform. The legs of the pulsating-dc/ac converter turn off/on during these provided zero states on the PDCL waveform. That provides zero-voltage switching condition for the remaining leg of the pulsating-dc/ac converter that operates at HF.

The ac/pulsating-dc converter consists of a single-phase diode-bridge module for unidirectional application. Additionally, it can be used for bidirectional applications by using a fully-controlled full-bridge module. Using a single-phase full-bridge module also provides zero-voltage switching condition for the ac/pulsating-dc converter. The switching requirement of the ac/pulsating-dc converter can be decreased by synthesizing a unique stream of pulses on the PDCL waveform and using pulse density modulation for the pulsating-dc/ac converter.

The soft-switched hybrid modulation [59] reduces the switching requirement of the pulsatingdc/ac converter by 66% and provides ZVS condition for the remaining leg of the converter operating at HF. However, it increases the switching requirement of the front-end dc/ac and the ac/pulsating dc converter. Therefore, a DPDPWM scheme is developed to not only decrease the switching requirement of the pulsating-dc/ac converter, but also decrease the switching requirement of the front-end dc/ac and the ac/pulsating-dc converters.

In Chapter II, a discontinuous PWM scheme, optimized for HFPDCL inverters, is developed to reduce the switching requirement of the pulsating-dc/ac converter without modulating the PDCL waveform. Therefore, the generated pulses on the PDCL waveform have a fixed duty cycle representing a dc value. Later in this chapter, the basic principal operation of the hard-switched HM

scheme is explained. Hard-switched HM scheme reduce the switching requirement of the pulsatingdc/ac converter by 66%.

In Chapter III, the soft-switched HM scheme is presented to reduce the switching requirement and switching losses of the pulsating-dc/ac converter. Therefore, two predetermined legs of the pulsating-dc/ac converter clamp to the dc rail while the other leg operates at HF under ZVS condition. The ZVS condition is provided for the pulsating-dc/ac converter by generating the zero states on the PDCL waveform. The zero states are generated on the PDCL waveform by a unique switching scheme for the dc/ac converter. Therefore, the switching losses of the pulsating-dc/ac converter are practically eliminated without using any auxiliary circuit.

In Chapter IV, the soft-switched HM scheme is validated by experimental results using a discrete 1 kW HFPDCL inverter. The results show that the soft switching condition is provided for the pulsating-dc/ac converter over a wide range of load conditions. The output current THD is well below 5% for a wide range of output powers and different load types. The efficiency of the pulsating-dc/ac converter is increased using soft-switched HM scheme in contrast to the existing modulation scheme for a PDCL HF inverter.

In Chapter V, a compact and modular design is developed for the HFPDCL inverter to decrease the leakage inductance of the board. It also increases the power density of the implemented HFPDCL inverter. The performance of the presented soft-switched modulation schemes are validated using the implemented 2 kW compact and modular HFPDCL inverter. In Chapter VI, a DPDPWM scheme is presented to reduce the switching requirement of the dc/ac converters. It also provides soft-switching condition for the pulsating-dc/ac and ac/pulsating-dc converters by generating the zero states on the PDCL waveform. The ZVS operation of the pulsating-dc/ac converter is validated using experimental results.

## **II.** A Discontinuous Modulation Schemes optimized for HFPDCL inverters

#### A. <u>DC-Modulated PDCL Waveform Discontinuous Modulation</u>

(Parts of this section, including figures and text, are based on my paper [67], ©2015 IEEE)

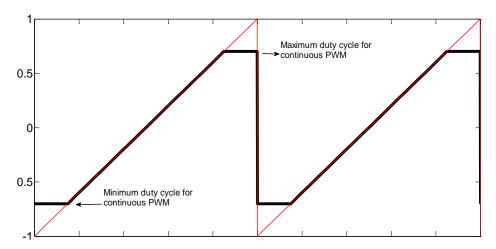

The modulation signals divide the modulation schemes of the inverters into two groups: continuous PWM and discontinuous PWM. In the continuous PWM schemes, the modulation signals are always in the boundary of the triangle carrier. However, in the discontinuous PWM schemes at least one phase leg of the inverter clamps to the negative or the positive rail of the dc bus. Therefore, one predetermined phase leg of the inverter does not modulate during any given period of the line cycle

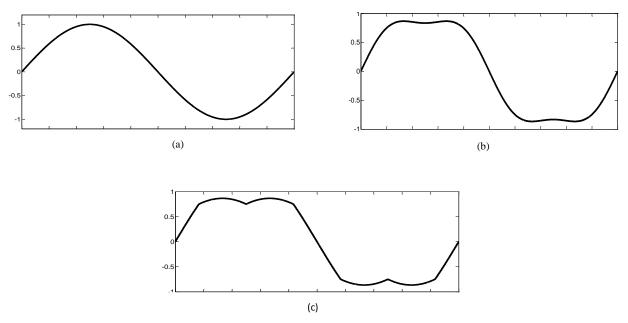

An isolated neutral star-connected load allows us to inject any zero sequence signals to the reference signals. It gives us freedom to vary the duty cycle of the switches of the output pulsating-dc/ac converter. This degree of freedom can be used to decrease the switching requirement of the converter and enhance the quality of the output waveforms. The conventional sine PWM (SPWM) is the simplest continuous modulation scheme and has gained wide application due to its simplicity. However, the dc-bus rail utilization of the SPWM scheme is low. PWM schemes such as third harmonic injection PWM (THIPWM) and space-vector PWM (SVPWM) inject a zero sequence signal to increase the dc-bus utilization of the inverter. Fig. 8 shows the modulation signals of the SPWM, THIPWM, and SVPWM. As we can see, although the THIPWM and SVPWM schemes increase the dc-bus utilization of the converter, they do not decrease the switching requirement of the inverter. As a result, the three leg phase of the output pulsating-dc/ac converter operate at HF using continuous modulation schemes.

Fig. 8. The modulation signals of the SPWM, THIPWM, and SVPWM schemes: a) SPWM, b) THIPWM, and c) SVPWM, ©2015 IEEE.

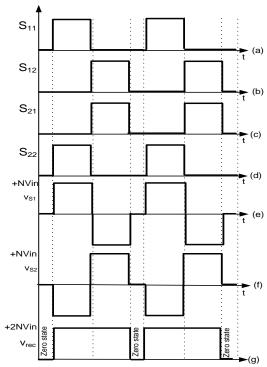

The front-end dc/ac converter of the HFPDCL inverter, shown in Fig. 7, determines the width of the pulses on the dc-link waveform. As a result, the operation of the front-end dc/ac and pulsating-dc/ac converters needs to be synchronized to synthesize the output LF waveforms. The front-end dc/ac converter determines the maximum achievable modulation index and the position of the generated zero states on the dc-link waveform. The pulsating-dc/ac converter synthesizes the output waveforms based on the generated pulses on the dc-link waveform by the front-end dc/ac converter. The zero states on the dc link waveform are generated by shorting the primary of the HF transformers. The ac/pulsating-dc converter (rectifier) rectifies the bipolar pulses generated by the front-end dc/ac converter. Fig. 9 shows the pulse placement and the generation of the dc-link waveform. The duty cycle of the pulses on the dc-link waveform are fixed; therefore, they represent a dc value. This dc value is set by the modulator of the HFPDCL inverters which synchronize the operation of the front-end dc/ac converter and the pulsating-dc/ac converter.

Fig. 9. Pulse placement and the generation of the dc-link waveform: (a)-(d) the synthesized gate signals of S11, S21, S21, and S22, (e)-(f) the secondary voltages of the HF transformer, and (g) the generated dc-link waveform, ©2015 IEEE.

Fig. 10. The equivalent circuit of the pulsating-dc/ac converter and the HF pulsating-dc link, ©2015 IEEE.

The equivalent circuit of the pulsating-dc/ac converter and the HF pulsating-dc link of the HFPDCL inverter is shown in Fig. 10. The frond-end dc/ac, HF transformers, and the rectifier are replaced by a pulsating-voltage power supply. The neutral point of the Y-connected load is isolated. The balanced three-phase reference signals can be defined as below:

$$u_{A}(t) = m * \sin(\omega t)$$

$$u_{B}(t) = m * \sin\left(\omega t + \frac{2\pi}{3}\right)$$

$$u_{C}(t) = m * \sin\left(\omega t + \frac{4\pi}{3}\right)$$

(1)

where m is the modulation index and  $\omega$  is the angular frequency of the output waveforms. It should be noted that the dc-link waveform is pulsating and is not fixed. Therefore, the value of the dc-link waveform is either N\*V<sub>in</sub> or zero. The dc-link voltage is zero when the HF transformers are shorted by the front-end dc/ac converter. Thus, when switches S<sub>31</sub>, S<sub>32</sub>, and  $\bar{S}_{33}$  are on and the dc-link value is N\*V<sub>in</sub>, the output phase voltage can be written as follows:

$$v_{aN} = v_{bN} = N \times \frac{v_{in}}{3}$$

$$v_{cN} = -N \times \frac{2V_{in}}{3}$$

(2)

A zero sequence signal can be injected to reference signals in (1) to generate the modulation signal of the inverter. The modulation signal can be represented as follows:

$$\begin{aligned} v_a(t) &= u_a(t) + z(t) \\ v_b(t) &= u_b(t) + z(t) \end{aligned} \tag{3}$$

$$\begin{aligned} v_c(t) &= u_c(t) + z(t) \end{aligned}$$

where z is the injected zero-sequence signal. The zero-sequence signal is equal to  $1/6m*sin(3\omega t)$  for the THIPWM. It is equal to  $1/2(1-max(u_i))+1/2(-1-min(u_i))$  for the SVPWM, where i is a, b, or c. These zero-sequence signals are injected to reference signals to increase the dc-link utilization of the inverter. The output phase voltages can be written as follows:

$$v_{aN}(t) = D_{PDCL} N \frac{V_{in}}{2} (m \times \sin(\omega t) + z(t))$$

$$v_{bN}(t) = D_{PDCL} N \frac{V_{in}}{2} (m \times \sin\left(\omega t + \frac{2\pi}{3}\right) + z(t))$$

$$v_{cN}(t) = D_{PDCL} N \frac{V_{in}}{2} (m \times \sin\left(\omega t + \frac{4\pi}{3}\right) + z(t))$$

(4)

where  $D_{PDCL}$  is the width of the pulses on the dc-link waveform set by the front-end dc/ac converter. The resulting output line-to-line voltages do not contain the zero-sequence signal z(t) and they can be written as follows:

$$v_{ab}(t) = D_{PDCL} N \frac{\sqrt{3}V_{in}}{2} \times m \times \sin\left(\omega t + \frac{5\pi}{6}\right)$$

$$v_{bc}(t) = D_{PDCL} N \frac{\sqrt{3}V_{in}}{2} \times m \times \sin\left(\omega t + \frac{5\pi}{6}\right)$$

(5)

$$v_{ca}(t) = D_{PDCL} N \frac{\sqrt{3}V_{in}}{2} \times m \times \sin\left(\omega t + \frac{3\pi}{2}\right)$$

The maximum output voltage is equal to the dc-link average voltage which is equal to  $D_{PDCL}NV_{in}$  when the modulation index is equal to  $\frac{\sqrt{3}}{2}$ . Therefore, the modulation signal is linear and in continuous mode when we have:

$$-1 + \frac{1 - D_{PDCL}}{2} - u_{min} < z(t) < 1 - \frac{1 - D_{PDCL}}{2} - u_{max}$$

(6)

Fig. 11. The modified carrier signal for HFPDCL inverters, ©2015 IEEE.

Fig. 12. The modulation signal after injecting the zero sequence signal, ©2015 IEEE.

where  $u_{min}$  and  $u_{max}$  are respectively the minimum and the maximum value of the defined reference signals in equation (1). For linear region, equation (6) means that the minimum duty cycle of the output pulsating-dc/ac converter is  $-1 + \frac{1-D_{PDCL}}{2}$  and the maximum duty cycle is  $1 - \frac{1-D_{PDCL}}{2}$ when the dc-link is HF pulsating. This is in contrast to the conventional fixed-dc link inverters where the maximum and the minimum duty cycles are respectively 1 and 0. The triangle carrier of the modulator of the HFPDCL inverters can be modified as shown in Fig. 11. This can be used to provide a high performance DPWM scheme for HFPDCL inverters. A zero sequence signal defined can be injected as follows:

$$Z(t) = \operatorname{sgn}[\sin(3 \times \omega t)] \times \left[\max|u_A, u_B, u_C| - m \times \frac{\sqrt{3}}{2}\right]$$

(7)

where sgn(x) is the sign function and  $sin(3\omega t)$  is the third harmonic function of the reference signals. The final modulation signal after injecting the zero-sequence signal and the sequence signal are shown in Fig. 6.

Therefore, the width of the pulses (DPDCL) on the dc-link waveform must be equal to  $\frac{\sqrt{3}}{2} * m$ . As a result; using the modified triangle carrier shown in Fig. 5 and the obtained modulation signal shown in Fig. 12, the desired output waveforms can be achieved. The resulting modulation scheme is discontinuous. Therefore, one phase leg of the pulsating-dc/ac converter clamps to the dc-link at any given time. Each phase leg of the inverter does not commutate at 1200 of the line cycle. This decreases the switching losses of the converter to increase the overall efficiency of the HFPDCL inverter.

#### B. Hybrid Modulation

(Parts of this section, including figures and text, are based on my paper [66], ©2014 IEEE)

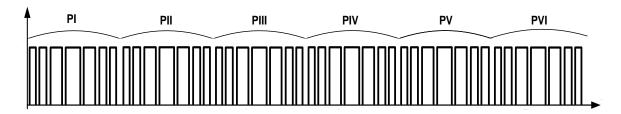

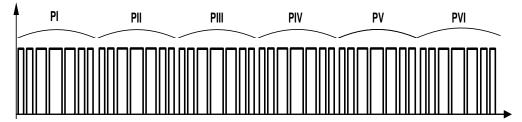

The HM scheme [55]-[57] unlike discontinues PWM schemes [49]-[53] decreases the switching requirement of the two predetermined legs of the pulsating-dc/ac converter in every 60° of the output line cycle. Therefore, every line cycle is divided in six different sectors; that is Pi-PVI. However, discontinues PWM schemes reduce the switching requirement of the pulsating-dc/ac converter by allowing no switching of one of the legs of the pulsating-dc/ac converter in every 30° or 60° of the line cycle.

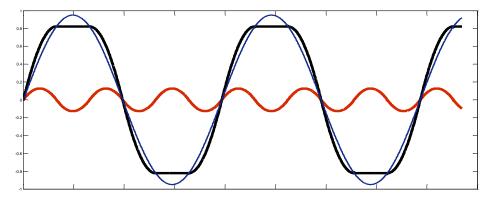

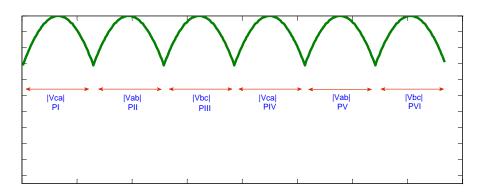

The additional decrease in switching requirement of the pulsating-dc/ac converter is achieved by generating a unique PDCL waveform that represents the maximum of the output reference signals. The maximum of the output reference signals changes in every 60° of the output line cycle. Fig. 13 shows the achieved PDCL waveform that consists of six distinct operating sectors, PI-PVI. Therefore, two predetermined legs of the pulsating-dc/ac converter do not need to commutate in Sectors, PI-PVI.

Fig. 13. The sinusoidal encoded information on the pulsating dc-link waveform for the HM scheme, ©2014 IEEE.

## 1. Front-End DC/AC Converter Modulation

As mentioned in the previous section, the HM scheme needs a PDCL waveform representing the maximum of the output reference signals. Therefore, the dc/ac converter generates a pattern that represents the maximum of the output reference signals. The generated bipolar pulses are, then, rectified to achieve the required PDCL waveform. The three-phase output reference signals are defined as (1). The PDCL waveform is generated to represent the maximum of the output reference signals  $u_{AB}$ ,  $u_{BC}$ , and  $u_{CA}$ . Therefore, the modulation signal for dc/ac converter is defined as:

$$1 - \max((|u_{AB}|, |u_{BC}|, |u_{CA}|)$$

(8)

where  $|u_{AB}|$ ,  $|u_{BC}|$ , and  $|u_{CA}|$  are respectively the absolute value of the output reference signals  $u_{AB}$ ,  $u_{BC}$ , and  $u_{CA}$ . The modulation signal for the dc/ac converter is shown in Fig. 14. As a result, the modulation function of the dc/ac converter is equal to  $|v_{CA}|$  in PI. The full-bridge modules of the dc/ac converter operate complementary. Therefore, the gate signal of the high-side switch  $S_{11}$  is identical to the gate signal of the high-side switch  $S_{22}$ . Accordingly, the gate signal of the high-side switch  $S_{12}$  is identical to the gate signal of the high-side switch  $S_{21}$ . The peak-to-peak value of the obtained PDCL waveform,  $v_{rec}$ , is calculated as follows:

$$v_{\rm rec(pk-pk)} = 2 \times N \times V_{\rm in} \tag{9}$$

Fig. 14. The modulation function of the dc/ac converter, ©2014 IEEE.

Fig. 15. The equivalent circuit of the PDCL and the pulsating-dc/ac converter, ©2014 IEEE.

#### 2. Pulsating-dc/ac Converter

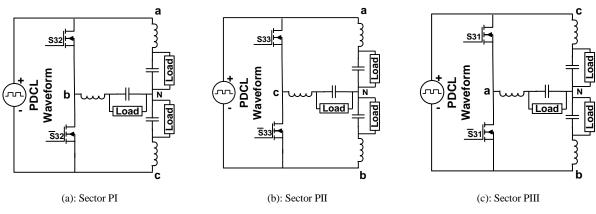

Fig. 15 shows the equivalent circuit of the PDCL and pulsating-dc/ac converter during different operating sectors. The pulsating supply represents the PDCL waveform that is generated by the dc/ac and ac/pulsating-dc converters. The generated PDCL waveform represents the maximum of the output reference signals. Therefore, two predetermined legs of the pulsating-dc/ac converter do not commutate in and Sectors, PI-PVI. Sectors PI, PII, and PIII are respectively are complementary with respect to Sectors PIV, PV, and PVI. Therefore, the gate signals of the switches of the pulsating-dc/ac converter are inverted in the complementary Sectors. In the following section, only Sectors PI, PII, and PIII are, as a result, explained.

#### Sector PI:

In this sector,  $u_{CA}$  is negative and its absolute value is the maximum of the output reference signals. Both of  $u_{AB}$  and  $u_{BC}$  are positive. Therefore, switches  $S_{31}$  and  $\overline{S}_{33}$  are always ON in Sector PI. The second leg of the pulsating-dc/ac converter operates at HF to generate other output reference signals. The equivalent circuit of the pulsating-dc/ac converter is shown in Fig. 15a. Nodes "a" and "c" are permanently connected to the PDCL, which represents the output reference signal  $u_{CA}$ . The output reference signal  $u_{BC}$  is the modulation signal of the high-side switch of the second leg of the pulsating-dc/ac converter,  $S_{32}$ . Therefore, three-phase output voltages are calculated as:

$$v_{ca} = v_{rec} = 2 \times N \times V_{in} \times m \times \sin\left(\omega t + \frac{4\pi}{3}\right)$$

$$v_{ab} = 2 \times N \times V_{in} \times (v_{rec} - u_{BC}) = 2 \times N \times V_{in} \times m \times \sin(\omega t)$$

$$v_{bc} = 2 \times N \times V_{in} \times m \times \sin\left(\omega t + \frac{2\pi}{3}\right)$$

(10)

Sector PII:

In Sector PII,  $u_{AB}$  is positive and it is the maximum of the output reference signals while  $u_{BC}$  and  $u_{CA}$  are negative. Therefore, node "a" and "b" need to be connected to the PDCL in Sector PII. The equivalent circuit of the pulsating-dc/ac converter is shown in Fig. 15b. The third legs of the pulsating-dc/ac converter operates at HF while  $S_{31}$  and  $\overline{S}_{32}$  are always ON. The high-side switch of the third leg of the pulsating-dc/ac converter,  $S_{33}$ , is modulated by the output reference signal  $u_{BC}$ . The three-phase output voltages are calculated as:

$$v_{ab} = v_{rec} = 2 \times N \times V_{in} \times m * \sin(\omega t)$$

$$v_{ca} = -2 \times N \times V_{in} \times (v_{rec} - |u_{BC}|) = 2 \times N \times V_{in} \times m \times \sin\left(\omega t + \frac{4\pi}{3}\right)$$

(11)

$$v_{bc} = 2 \times N \times V_{in} \times m \times \sin\left(\omega t + \frac{2\pi}{3}\right)$$

In equation (10), the absolute value of the  $u_{BC}$  is used because it is negative in Sector PII. Sector PIII:

The output reference signal  $u_{BC}$  becomes the maximum of the output reference signals in Sector PIII. The output reference signal  $u_{BC}$  is negative while  $u_{CA}$  and  $u_{AB}$  are positive. Therefore, the

second and third legs of the pulsating-dc/ac converter do not commutate as shown in Fig. 15c. The first leg of the pulsating-dc/ac converter operates at HF to generate phase-to-phase output voltages  $u_{ab}$  and  $u_{ca}$ . The high-side switch of the first leg of the pulsating-dc/ac converter is modulated by the output reference signal  $u_{AB}$ . As a result, the output reference signal  $u_{BC}$  is already modulated on the PDCL waveform by the dc/ac converter and two other output reference signals are generated by the first leg of the pulsating-dc/ac converter. The three-phase output voltage are calculated as follows:

$$v_{bc} = v_{rec} = 2 \times N \times V_{in} \times m \times \sin\left(\omega t + \frac{2\pi}{3}\right)$$

$$v_{ca} = 2 \times N \times V_{in} * m \times (v_{rec} - u_{AB}) = 2 \times N \times V_{in} \times m \times \sin(\omega t)$$

(12)

$$v_{ab} = 2 \times N \times V_{in} \times m \times \sin(\omega t)$$

Fig. 16. The modulation signal of the first leg of the pulsating-dc/ac converter, ©2014 IEEE.

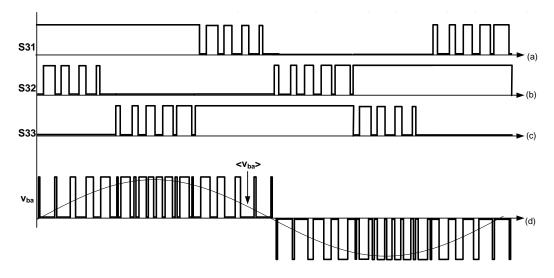

Therefore, all three-phase output voltages are generated by the pulsating-dc/ac converter while two predetermined legs of the converter do not commutate. This decreases the switching requirement of the pulsating-dc/ac converter by 66%. The overall modulation signal of the pulsating-dc/ac converter is shown in Fig. 16. As a result, each leg of the pulsating-dc/ac converter

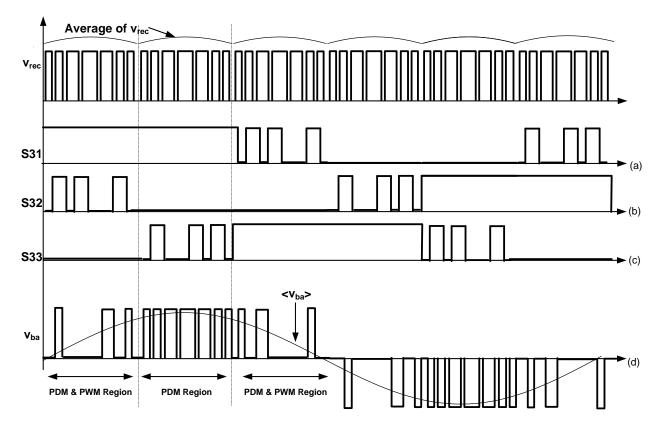

Fig. 17. The switching signals of the pulsating-dc/ac converter using the HM scheme. a) Gate signal of S<sub>31</sub>, b) Gate signal of S<sub>32</sub>, c) Gate signal of S<sub>33</sub>, and d) The achieved output voltage waveform v<sub>ba</sub>, ©2014 IEEE

do not commutate during 240° of the output LF. The next section explores the operation of the dc-

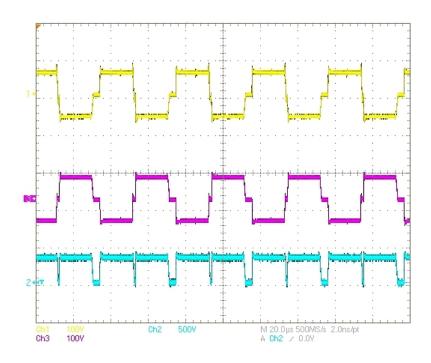

link-capacitor less HFL inverter using the HM scheme. The resulting gate signals for all three legs of the pulsating-dc/ac converter to generate the output voltage waveforms are shown in Fig. 17. Therefore, only one leg of the pulsating-dc/ac converter operates at HF in each Sector. TABLE I summarizes the HF operation of the three legs of the pulsating-dc/ac converter in any Sectors. In the next section, the operation of the dc-link-capacitor less HFL inverter using hybrid modulation is verified by the experimental results.

Gate signal PI PII PIII PIV PV PVI HF  $S_{31}$ HF 0 0 1 1 S<sub>32</sub> 0 HF 1 HF 0 1 S<sub>33</sub> 0 HF 0 0 HF 1

TABLE I: Switching signals for the pulsating-dc/ac converter.

#### C. Conclusion

A discontinuous PWM scheme optimized for HFPDCL inverters with HF pulsating dc-link waveform has been developed to decrease the switching requirement of the inverter and generate

high-quality output waveforms. The presented discontinuous PWM decreases the switching requirement of the output three-phase inverter (pulsating-dc/ac converter) by 33%. One phase leg of the output inverter is clamped to the dc-rail in 120° of the line cycle. It does not need to modulate the PDCL waveform. Therefore, the PDCL waveform presents a dc value. This modulation scheme clamps two legs of the pulsating-dc/ac converter to the dc rail at any given time. Therefore, it decreases the switching requirement of the pulsating-dc/ac converter by 66%. However, the remaining leg of the pulsating-dc/ac converter still operates under hard-switching condition.

# **III.** Soft-Switched Hybrid Modulation

(Parts of this chapter, including figures and text, are based on my journal paper [59], ©2014 IEEE)

HFPDCL inverters consist of three active stages, which are the front-end dc/ac, rectifier, and pulsating-dc/ac converters. The dc/ac converter generates width modulated bipolar pulses for HF transformers. The modulated voltage pulses across the secondary sides of the HF transformers are rectified by the ac/pulsating-dc converter to generate the PDCL waveform. An RCD snubber [60] can be used to limit the voltage spikes on the PDCL waveform due to the leakage inductances of the HF transformers and parasitic output capacitors of the ac/pulsating-dc converter. Finally, the pulsating-dc/ac converter generates the LF output sine waveforms using the pulses on the PDCL waveform.

Therefore, the PDCL waveform is synthesized by the dc/ac converter and the pulsating-dc/ac converter uses the synthesized pulses on the PDCL waveform to generate LF output sine waveforms. The soft-switched HM scheme decreases the switching losses of the pulsating-dc/ac converter by decreasing the switching requirement and ZVS operation of the pulsating-dc/ac converter. This section explains the modulation scheme to synthesize the PDCL waveform.

#### A. Synthesis of the PDCL waveform

The dc/ac converter generates two sets of bipolar pulses for the HF transformers to avoid core saturation. The HFPDCL inverter has two full-bridge modules operating as a dc/ac converter. The first full-bridge module includes  $S_{11}$ ,  $\overline{S}_{11}$ ,  $S_{12}$ , and  $\overline{S}_{12}$ . The second full-bridge module (using modulator II) includes  $S_{21}$ ,  $\overline{S}_{21}$ ,  $S_{22}$ , and  $\overline{S}_{22}$ . Each full-bridge module generates a set of bipolar pulses for a HF transformer. Two switches of each leg operate complementary and a proper dead-

$\langle \mathbf{a} \rangle$

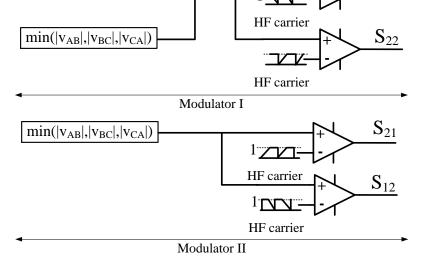

time is considered to avoid short-circuit of the input dc bus. Fig. 18 shows the modulation scheme for switching signal generation of the dc/ac converter. A set of normalized three-phase sine-wave references are defined as (1).

$$v_{AB} = m * \sin(\omega t)$$

$$v_{BC} = m * \sin\left(\omega t + \frac{2\pi}{3}\right)$$

$$v_{CA} = m * \sin\left(\omega t + \frac{4\pi}{3}\right)$$

(1)

where m is modulation index and  $\omega$  is output line angular frequency of the LF output sine-waves. We also obtain the following relationships for a balanced system:

1

$$v_{ij} + v_{jk} + v_{ki} = 0$$

$$v_{ij} = -(v_{jk} + v_{ki})$$

$$(2)$$

where i, j, k  $\underset{i \neq j \neq k}{\in}$  {A, B, C}. One can conclude:

$$v_{ij} = |v_{jk} + v_{ki}|$$

$$(3)$$

$$\underline{max(|v_{AB}|, |v_{BC}|, |v_{CA}|)} + \underbrace{S_{11}}_{1 \text{ NDV}}$$

Fig. 18. Switching signal generation for the dc/ac converter (dc/ac modulator), ©2014 IEEE.

Then, following equation are obtained for different 60° sectors of the output line cycle:

$$|v_{CA}| = |v_{AB}| + |v_{BC}|$$

$0 < \omega t < \frac{\pi}{3} \text{ or for } \pi < \omega t < \frac{4\pi}{3}.$  (4)

$$|v_{AB}| = |v_{BC}| + |v_{CA}|$$

$\frac{\pi}{3} < \omega t < \frac{2\pi}{3} \text{ or for } \frac{4\pi}{3} < \omega t < \frac{5\pi}{3}.$  (5)

$$|v_{BC}| = |v_{CA}| + |v_{AB}|$$

$\frac{2\pi}{3} < \omega t < \pi \text{ or for } \frac{5\pi}{3} < \omega t < 2\pi.$  (6)

Therefore, the PDCL waveform is required to be compartmentalized in six distinct sectors; that is PI: 0-60°, PII: 60°-120°, PIII: 120°-180°, PIV: 180°-240°, PV: 240°-300°, and PVI: 300°-360°. During each sector, the dc/ac converter generates two sets of pulses representing rectified signals  $v_{AB}$ ,  $v_{BC}$ , and  $v_{CA}$ . In each sector, the non-maximum voltage reference signal is synthesized by two pulses representing two other non-maximum reference signals as shown in equations (4)-(6). Therefore, the voltage reference signals of the dc/ac modulator change in every 60° of the line cycle. In sectors PI and PIV,  $|v_{CA}|$  is synthesized on the PDCL waveform using two sets of pulses synthesized by  $|v_{AB}|$  and  $|v_{BC}|$  as the voltage reference signals. These two sets of pulses are generated by the two-full-bridge modules of the dc/ac converter. In sectors PII and PV,  $|v_{AB}|$  is synthesized on the PDCL waveform using  $|v_{BC}|$  and  $|v_{CA}|$  as the voltage reference signals of the full-bridge modules of the dc/ac converter. Finally, in sectors PIII and PVI,  $|v_{BC}|$  is synthesized using two sets of pulses synthesized by  $|v_{AB}|$  and  $|v_{CA}|$  as the voltage reference signals of the full-bridge modules of the dc/ac converter. Finally, in sectors PIII and PVI,  $|v_{BC}|$  is synthesized using two sets of pulses synthesized by  $|v_{AB}|$  and  $|v_{CA}|$  as the voltage reference signals of the full-bridge modules of the dc/ac converter.

Equations (4)-(6) can be rewritten as:

$$|v_{BC}| = \max(|v_{AB}|, |v_{BC}|, |v_{CA}|) - \min(|v_{AB}|, |v_{BC}|, |v_{CA}|) \qquad 0 < \omega t < \frac{\pi}{6} \text{ or for } \frac{\pi}{2} < \omega t < \frac{2\pi}{3}$$

$$|v_{CA}| = \max(|v_{AB}|, |v_{BC}|, |v_{CA}|) - \min(|v_{AB}|, |v_{BC}|, |v_{CA}|) \qquad \frac{\pi}{3} < \omega t < \frac{\pi}{2} \text{ or for } \frac{5\pi}{6} < \omega t < \pi$$

(7)

(8)

$$|v_{AB}| = \max(|v_{AB}|, |v_{BC}|, |v_{CA}|) - \min(|v_{AB}|, |v_{BC}|, |v_{CA}|) \qquad \frac{\pi}{6} < \omega t < \frac{\pi}{3} \text{ or for } \frac{2\pi}{3} < \omega t < \frac{5\pi}{6}$$

(9)

Using equations (7)-(9), Modulator I of the dc/ac modulator can be implemented using the maximum and minimum signals of  $|v_{AB}|$ ,  $|v_{BC}|$ , and  $|v_{CA}|$ . This approach makes the implementation of the dc/ac modulator just based on the maximum and minimum function of the voltage reference signals.

For example, when  $\omega t$  is between 0 and  $\pi/6$ ,  $|v_{CA}|$  is the maximum of the rectified signals  $v_{AB}$ ,  $v_{BC}$ , and  $v_{CA}$  and  $|v_{AB}|$  is the minimum of the rectified signals  $v_{AB}$ ,  $v_{BC}$ , and  $v_{CA}$ . Therefore, the voltage reference signal of Modulator I is  $|v_{CA}|$  minus  $|v_{AB}|$ , which is equal to  $|v_{BC}|$ . Modulator II uses  $|v_{AB}|$  (the minimum reference signal) as its voltage reference signal. Therefore, a set of pulses are synthesized by  $|v_{AB}|$  and the other set of the pulses are synthesized by  $|v_{BC}|$  on the PDCL waveform. Then, the average of two resulting consecutive pulses on the PDCL waveform over the switching cycle is equal to  $|v_{CA}|$  (the maximum reference signal). The duration of the synthesized zero states between these two sets of pulses on the PDCL waveform are calculated as follows:

$$z(t) = 1 - \max(|v_{AB}|, |v_{BC}|, |v_{CA}|)$$

(10)

These zero states on the PDCL waveform are used to achieve ZVS operation for the switches of the pulsating-dc/ac converter. Therefore,  $|v_{AB}|$  and  $|v_{BC}|$  are directly synthesized on the PDCL waveform by two full-bridge modules of the dc/ac converter. Also,  $|v_{CA}|$  is indirectly synthesized on the PDCL waveform as two consecutive pulses. Therefore, all the required voltage reference signals are synthesized on the PDCL waveform. As a result, two legs of the pulsating-dc/ac converter do not switch while the other leg switches at middle of the provided zero states on the PDCL waveform to achieve ZVS condition. The soft-switched HM scheme for the pulsating-dc/ac converter is explained in the following section.

As shown in Fig. 18, the HF carrier of Modulator I has 180° phase shift with respect to the HF carrier of Modulator II of the dc/ac converter. Therefore, the dc/ac converter generates a set of bipolar pulses at the end and beginning of the switching cycle. But, it also generates a set of bipolar pulses at the middle of the switching cycle. Consequently, two sets of the generated pulses by the full-bridge modules of the dc/ac converter have 180° phase shift with respect to each other.

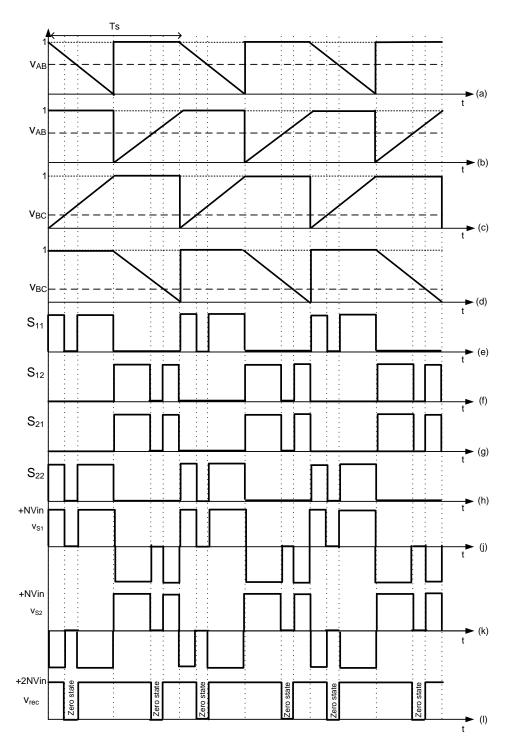

Fig. 19 shows the HF carriers, references, signal-waveforms of Modulator I and Modulator II of the dc/ac converter, bipolar pulses for the HF transformers, and the resulting PDCL voltage waveform. As shown in Fig. 19, two sets of pulses with  $180^{\circ}$  phase shift are generated on the PDCL waveform with enough zero states to enable ZVS condition for the pulsating-dc/ac converter. As a result, the average of two consecutive pulses on the PDCL waveform over the switching cycle is equal to the maximum of the rectified signals  $v_{AB}$ ,  $v_{BC}$ , and  $v_{CA}$ .

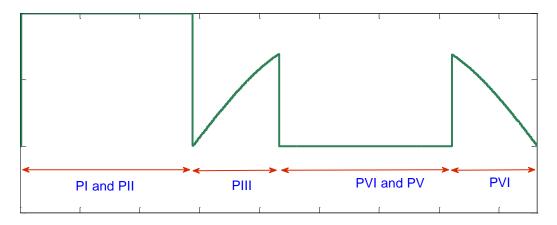

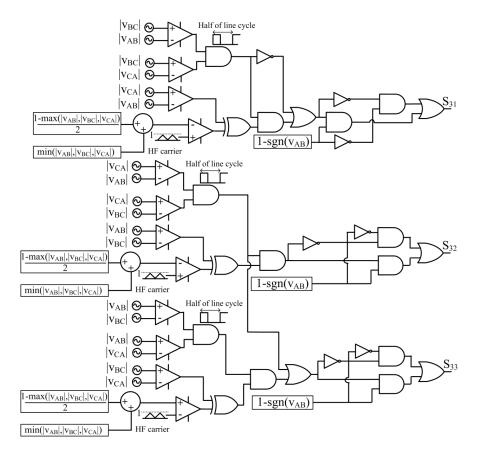

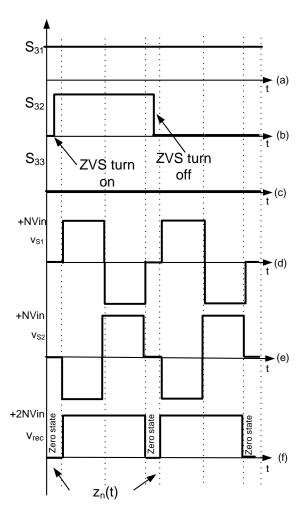

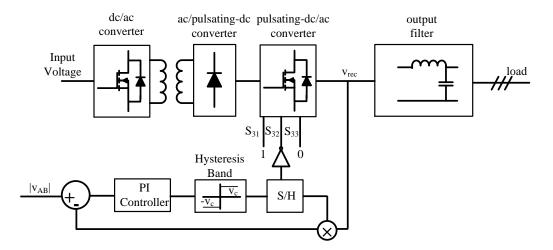

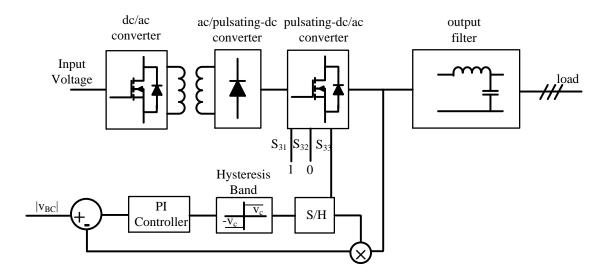

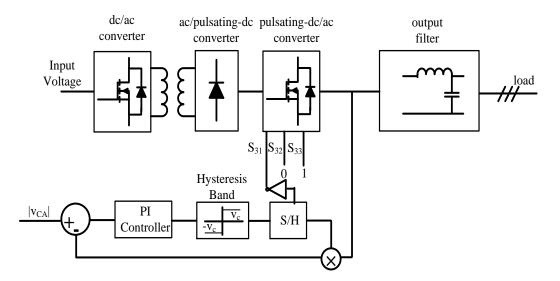

## B. Soft-switched hybrid modulation for the pulsating-dc/ac converter

The modulation scheme to generate the required PDCL waveform for pulsating-dc/ac converter is described in the previous section. The two sets of generated pulses by the full-bridge modules of the dc/ac converter are used to decrease the switching requirement of the pulsating-dc/ac converter. Also, the zero states on the PDCL waveform are used to provide ZVS condition for the pulsatingdc/ac converter. The modulation scheme to generate switching signals for three legs of the pulsating-dc/ac converter is shown in Fig. 20. The sign of  $v_{AB}$  (as represented by  $sgn(v_{AB})$ ) is used to generate the complementary pulses for the second half of the line cycle. Each leg of the pulsatingdc/ac converter does not switch for two-thirds of the line cycle. For instance, the first leg of the pulsating-dc/ac converter operates only at HF when  $|v_{BC}|$  is greater than  $|v_{AB}|$  and  $|v_{CA}|$ . The available zero states on the PDCL waveform are calculated using (10). Therefore, the term z(t)/2 is added to the reference signals of the comparators to operate at middle of the zeros states on the PDCL waveform. As a results, the switches of the pulsating-dc/ac converter turn off/on when the voltage across the PDCL waveform is zero. Fig. 21 shows a simplified operation overview of the soft-switched HM. The dc/ac and pulsating-dc/ac modulators are respectively described in Fig. 19 and Fig. 20. A sine-wave rectifier is used to provide rectified sine-wave voltage reference signals (v<sub>AB</sub>, v<sub>BC</sub>, and v<sub>CA</sub>) for the dc/ac and pulsating-dc/ac modulators. These modulators have synchronous carriers to achieve ZVS condition for the pulsating-dc/ac converter. The generated pulses for the pulsating-dc/ac converter are inverted when the sign of signal vAB changes. Therefore, the sign of v<sub>AB</sub> is provided for the pulsating-dc/ac modulator. The signals v<sub>AB</sub>, v<sub>BC</sub>, and v<sub>CA</sub> are the output of the controller for close loop of the HFPDCL inverter. Fig. 22 illustrates the switching scheme of the pulsating-dc/ac converter and the zero states on the PDCL over a line cycle. Figs. 6b-6d show the required gate signals to extract the desired phase-to-phase output voltages using the soft-switched HM. The resulting output voltage, v<sub>ba</sub>, is depicted in Fig. 6e before and after the output filter stage. Topological modes of operation are thoroughly presented in the next section. In order to study the topological modes of operation of the HFPDCL inverter using the soft-switch HM, an equivalent circuit is derived as shown in Fig. 23. It is obtained by eliminating the HF transformers and simplifying the dc/ac converter to analyze the soft-switching operation of the softswitched HM. The voltage supplies ( $v_{1s}$  and  $v_{2s}$ ) represent the secondary reflected voltages of transformers  $T_1$  and  $T_2$ , while the inductors are the secondary-side leakage inductances. The capacitors across the switches of the pulsating-dc/ac converter represent the parasitic capacitors of the switches.

Fig. 19. Pulse placement on the PDCL using the dc/ac converter to provide zero states: (a)-(d) the HF carriers and references of the full-bridge modules of the dc/ac converter to generate bipolar pulses for HF transformers, (e)-(h) the synthesized gate signals of  $S_{11}$ ,  $S_{21}$ ,  $S_{21}$ , and  $S_{22}$ , (j)-(k) the secondary voltages of the HF transformer, and (l) the generated PDCL waveform, ©2014 IEEE.

Fig. 20. Switching signals generation for the pulsating-dc/ac converter, ©2014 IEEE.

Fig. 21. A simplified operation overview of the HFPDCL inverter using the soft-switched HM, ©2014 IEEE.

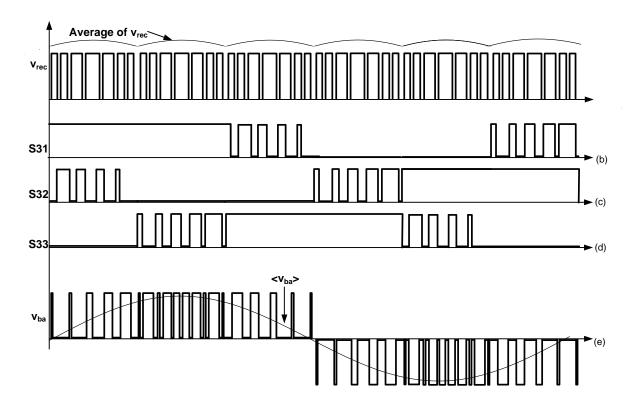

Fig. 22. Switching functions and waveforms of the soft-switched HM: (a) PDCL, (b)-(d) gate signals of pulsating-dc/ac converter switches, and (e) resulting phase-to-phase voltage before and after the output filters, ©2014 IEEE.

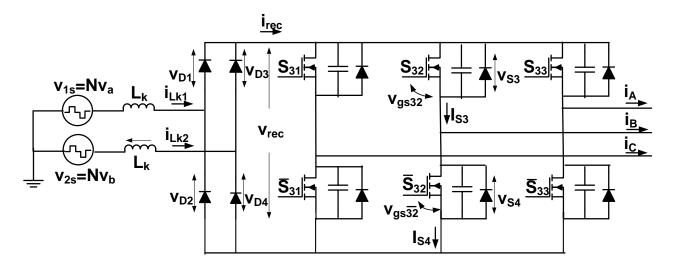

Fig. 23. Equivalent circuit of the ac/pulsating-dc converter, HF transformers, and the front-end pulsating-dc/ac converter to study topological modes of operation, ©2014 IEEE.

### C. Modes of Operation

To analyze the modes of operation, the following assumptions are made:

• The voltage drops of the diodes and conduction losses of the switches are neglected;

• The dead time considered for the complementary switches of the pulsating-dc/ac converter is disregarded (it should be noted that switches of the pulsating-dc/ac converter operate at zero states, therefore; no dead time is necessary for complementary switches of the converter);

• The currents are considered to be constant during switching cycle.

• The currents and voltages are assumed to be balanced three-phase sinusoidal waveforms; that is,

$$i_{A} = I_{m} sin(\omega t + \gamma)$$

$$i_{B} = I_{m} sin\left(\omega t + \gamma + \frac{2\pi}{3}\right)$$

$$i_{C} = I_{m} sin\left(\omega t + \gamma + \frac{4\pi}{3}\right)$$

(11)

where  $I_m$  is the peak value of the line output currents and  $\gamma$  represents the power factor of the output load, which is negative for inductive load. A HFPDCL inverter with diode rectifier supports a power factor up to 30° according to [55]-[57]. Due to symmetry, the soft-switching operation of a leg of the pulsating-dc/ac converter is analyzed, which operates at HF.

In this section,  $|v_{CA}|$  is greater than  $|v_{AB}|$  and  $|v_{BC}|$  and the sign of  $v_{AB}$  is negative. Therefore, switches  $S_{31}$ ,  $\overline{S}_{31}$ ,  $S_{33}$ , and  $\overline{S}_{33}$  do not switch. However, the second leg of the pulsating-dc/ac converter consisting of  $S_{32}$  and  $\overline{S}_{32}$  operates at HF. Currents  $i_A$  and  $i_C$  are positive, but  $i_B$  is negative.

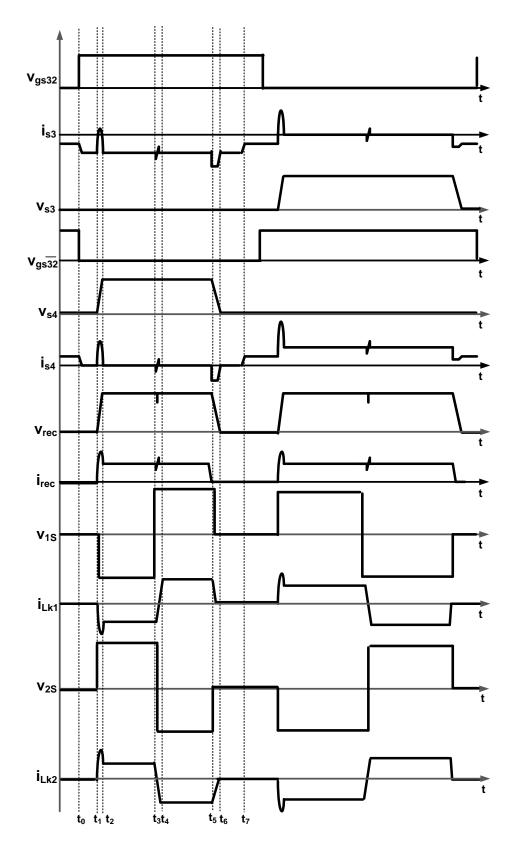

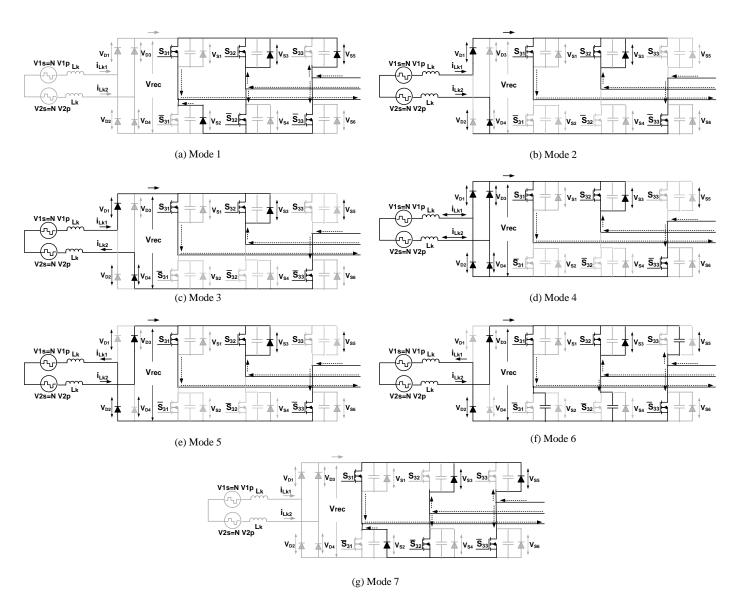

The topological modes of operation and the key waveforms are respectively shown in Figs. 24 and 25.