## Operation Scheduling Algorithms for Power, Energy and Resource Minimization in High-

Level Synthesis

BY

OUWEN SHI B.S., Xidian University, Xi'an, China, 2013

## THESIS

Submitted as partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2017

Chicago, Illinois

Defense Committee:

Shantanu Dutt, Chair and Advisor Amit Ranjan Trivedi Zhao Zhang

#### ACKNOWLEDGMENTS

I would like to express my greatest gratitude to my advisor, Professor Shantanu Dutt, who tirelessly guides me in algorithm study and development throughout the four years. His desire, passion and dedication in research always inspires me to strive for the highest possible standards and goals. The achievements in the thesis would not be possible without his continuous support and guidance.

I would also like to express my appreciation to my dissertation committee, Professor Amit Ranjan Trivedi and Professor Zhao Zhang, for their valuable suggestions on my thesis.

Besides, I would appreciate my colleague, Xiuyan Zhang, who worked with me in the same lab. He always positively influenced me by his diligence, optimism and courage. His cross-disciplinary knowledge in algorithms also expanded my vision.

In addition, thanks to the faculty and staff in the Electrical and Computer Engineering Department. In particular, I would like to thank Tina Alvarado, Ala Wroblewski and Evelyn Reyes, who helped me with various administration issues.

Finally, deep thanks given to my parents. They are always my source of support, encouragement and strength.

OS

#### PREFACE

The research cooperation with Professor Shantanu Dutt during the four years' study at the University of Illinois at Chicago provided me with knowledge on state-of-the-art high-level synthesis algorithms and opportunities to improve algorithmic development and problem-solving skills. This thesis is the outcome of the study, which includes two published papers, one paper accepted for publication and two DAC (Design Automation Conference) poster presentations as listed below. The operation scheduling algorithm proposed in each of the papers optimizes a different design objective in high-level synthesis.

- S. Dutt and O. Shi, "A Fast and Effective Lookahead and Fractional Search Based Scheduling Algorithm for High-Level Synthesis", accepted for publication in Proceedings of the Design Automation and Test in Europe (DATE), Dresden, Germany, Mar. 2018.

- S. Dutt and O. Shi, "A Fast and Effective Fractional Search and Lookahead Based List Scheduling Algorithm for High-Level Synthesis", poster presentation at 54th Design Automation Conference (DAC), Austin, TX, June 2017.

- 3. S. Dutt and O. Shi, "Power-delay product based resource library construction for effective power optimization in HLS," published at 2017 International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, Mar. 2017, pp. 229-236.

- O. Shi and S. Dutt, "Co-exploration of unit-time leakage power and latency spaces for leakage energy minimization in high-level synthesis," published in Journal of Low Power Electronics (JOLPE), Vol. 12, No. 4, Dec. 2016, pp. 295-308.

# **PREFACE** (Continued)

J. Xu, S. Dutt and O. Shi, "Power optimization in HLS Using Multi-Design Function Units", poster presentation at 51th Design Automation Conference (DAC), San Francisco, CA, June 2014.

### **Contribution of Authors**

Chapter 1 introduces the topic area of the thesis, categorizes problems in the area, reviews previous research works for each problem and highlighted the significance of our research contribution. Chapter 2 provides more technical background of our works and presents several classical scheduling algorithms, which our works are compared to. Chapter 3 represents the power-driven scheduling and module-selection algorithm PSA in [1] [2] and a series of unpublished experimental results in [2]. I played a major role in significantly modifying and debugging on initial version of the PSA program developed by Jian Xu. Xiuyan Zhang worked with me to collect the experimental results and worked with Prof. Shantanu Dutt for writing the report [2]. Chapter 4 represents a published manuscript [3] for which I am the second author, and it has contributions of PSA from [1] [2]. The main ideas and theoretical analysis are due to Prof. Shantanu Dutt, as is the major writing of the manuscript. I was responsible for the program as I did in Chapter 3 and worked with Prof. Shantanu Dutt to refine the manuscript. Jian Xu was involved in coding, experimentation and literature search in an earlier version of [3]. Chapter 5 represents a published manuscript [4] for which I am the first author. The major algorithmic ideas were proposed by Prof. Shantanu Dutt. I played a major role in debugging and implementation, suggested some improvements to the algorithms, as well as wrote an initial version of the manuscript that Prof. Shantanu Dutt then significantly re-wrote. Chapter 6 represents a poster presentation [5] and an accepted paper [6] for which I am the second author. Following the main algorithmic ideas and their theoretical results and analysis proposed by Prof. Shantanu Dutt, I implemented, experimented and provided some algorithmic improvements. I also wrote the initial manuscript that Prof. Shantanu Dutt refined.

# **TABLE OF CONTENTS**

## **CHAPTER**

## PAGE

| 1. | INTR | ODUCTION                                                 | 1  |

|----|------|----------------------------------------------------------|----|

|    | 1.1. | High-Level Synthesis                                     | 1  |

|    | 1.2. | Operation Scheduling                                     | 1  |

|    | 1.3. | Problem Category                                         | 2  |

|    | 1.4. | Previous Works                                           | 3  |

|    |      | 1.4.1. Power Minimization                                | 3  |

|    |      | 1.4.2. Energy Minimization                               | 4  |

|    |      | 1.4.3. FU Minimization                                   | 5  |

|    |      | 1.4.4. Resource Library Construction                     | 7  |

|    | 1.5. | Contributions                                            | 7  |

|    | 1.6. | Thesis Outline                                           | 8  |

| 2. | BACI | KGROUND                                                  | 10 |

|    | 2.1. | General Problem Formulation                              |    |

|    | 2.2. | As-Soon-As-Possible Scheduling                           |    |

|    |      | 2.2.1. ASAP Time Updating                                |    |

|    | 2.3. | As-Late-As-Possible Scheduling                           |    |

|    |      | 2.3.1. ALAP Time Updating                                | 14 |

|    | 2.4. | List Scheduling                                          |    |

|    |      | 2.4.1. Complexity                                        | 17 |

|    | 2.5. | Force-Directed Scheduling                                | 17 |

|    |      | 2.5.1. Scheduling Probabilities Determination            | 18 |

|    |      | 2.5.2. Distribution Graph Construction                   | 18 |

|    |      | 2.5.3. Self-Force Formulation                            |    |

|    |      | 2.5.4. Predecessor/Successor and Total Force Formulation | 20 |

|    |      | 2.5.5. Complexity and Optimality Analysis                | 21 |

|    | 2.6. | Simulated Annealing                                      | 22 |

|    |      | 2.6.1. Initial Solution                                  | 23 |

|    |      | 2.6.2. Temperature                                       |    |

|    |      | 2.6.3. Local Search and Move Set                         |    |

|    | 2.7. | Integer Linear Programming                               | 26 |

| 3. | PSA: | NEW POWER MINIMIZATION ALGORITHM                         | 28 |

|    | 3.1. | Power Model                                              | 29 |

|    | 3.2. | Simulated Annealing Framework                            | 30 |

|    |      | 3.2.1. Initial Solution                                  | 30 |

|    |      | 3.2.2. Move Set                                          | 31 |

|    |      | 3.2.3. Post-Move Processing                              | 32 |

|    | 3.3. | Internal Scheduler                                       | 32 |

|    | 3.4. | Experimental Results                                     | 35 |

| 4.   | NEW     | CRITERIA           | FOR         | <b>POWER-DRIVEN</b>      | RESOURCE | LIBRARY |

|------|---------|--------------------|-------------|--------------------------|----------|---------|

|      | CONS    | STRUCTION          | •••••       | ••••••                   |          |         |

|      | 4.1.    | Introduction of N  | /lodule Se  | election                 |          |         |

|      | 4.2.    | Motivation of Re   | esource Li  | ibrary Construction      |          |         |

|      | 4.3.    | Hypotheses for E   | Effective I | Library Construction     |          |         |

|      |         | 4.3.1. The First   | Hypothe     | sis                      |          |         |

|      |         | 4.3.2. The Seco    | ond Hypot   | thesis                   |          |         |

|      | 4.4.    | Resource Library   | / Constru   | ction Examples           |          |         |

|      | 4.5.    | Hypotheses Veri    | fication U  | Jsing PSA                |          | 61      |

| 5.   | LPR-    | GPS: NEW DIRE      | ECTION      | FOR ENERGY MININ         | AIZATION | 66      |

|      | 5.1.    |                    |             |                          |          |         |

|      | 5.2.    | Motivation of Le   | akage En    | ergy Minimization        |          |         |

|      | 5.3.    |                    |             | n for Leakage Energy Mi  |          |         |

|      |         |                    |             | heduling Probability Det |          |         |

|      |         |                    |             | r Estimation             |          |         |

|      |         |                    |             | g for Latency Estimation |          |         |

|      | 5.4.    | Experimental Re    | sults       | •                        |          | 87      |

| 6.   | FALI    | .S: FAST AND E     | FFICIEN     | <b>NT FU MINIMIZATIO</b> | N        |         |

|      | 6.1.    | Formulation of the | ne Optimi   | zation Objective         |          |         |

|      | 6.2.    | Our Scheduling     | Algorithm   | n for FU Minimization    |          |         |

|      |         | 6.2.1. Lookahe     | ad Schedu   | ıling                    |          |         |

|      |         | 6.2.2. Fractiona   | al Search.  | -                        |          | 104     |

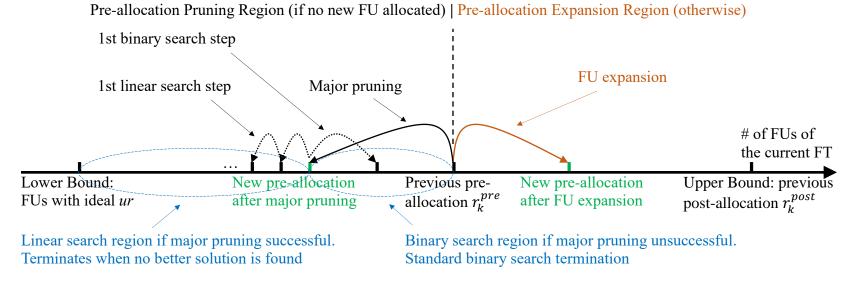

|      |         | 6.2.3. Pre-alloc   | ation Exp   | ansion Technique         |          | 108     |

|      |         | 6.2.4. Pre-alloc   | ation Pru   | ning Technique           |          | 108     |

|      |         | 6.2.5. Time Co     | mplexity.   |                          |          | 110     |

|      | 6.3.    | Experimental Re    | sults       |                          |          |         |

|      |         | 6.3.1. Results of  | of FALLS    |                          |          |         |

|      |         | 6.3.2. Our ACC     | ) Implem    | entation                 |          | 121     |

| 7.   | CON     | CLUSIONS           | •••••       |                          |          | 125     |

| APP  | ENDIX:  | Copyright Trans    | sfer Agre   | ements                   |          | 126     |

| CITI | ED LITI | ERATURE            | •••••       |                          |          | 129     |

| VIT  | 4       |                    | •••••       |                          |          |         |

# LIST OF TABLES

| <u>TABLE</u> | PAGE                                                                                                                                                 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι            | POWER-DELAY CHARACTERISTICS OF ARITHMETIC FTS OF THE 4-SPEED<br>FU LIBRARY                                                                           |

| II           | TOTAL POWER AND RUNTIME COMPARISON BETWEEN PSA-LS AND THE EXTENDED SA                                                                                |

| III          | LEAKAGE POWER AND RUNTIME COMPARISON AMONG THE COMPETING ALGORITHMS                                                                                  |

| IV           | TOTAL POWER AND RUNTIME COMPARISON AMONG ILP, SA AND VARIOUS VERSIONS OF PSA WITH 2/4-SPEED LIBRARIES                                                |

| V            | POWER-DELAY CHARACTERISTICS OF FUS WITH DUAL DESIGNS                                                                                                 |

| VI           | POWER-DELAY CHARACTERISTICS OF FUS WITH DUAL VDDS 60                                                                                                 |

| VII          | TOTAL ENERGY (EQUIVALENTLY, POWER) RESULTS FOR PSA USING DUAL-VDD FUS AND PSA USING DUAL-DESIGN FUS                                                  |

| VIII         | POWER RESULTS AND FU STATISTICS FOR PSA WITH 4-SPEED-ALL-GOOD LIBRARY, PSA WITH 3-SPEED-ALL-GOOD LIBRARY AND PSA WITH 4-SPEED-ONE-BAD LIBRARY        |

| IX           | CHARACTERISTICS OF FUS                                                                                                                               |

| Х            | TOTAL LE COMPARISON AMONG PFDS, PR-GPS AND LPR-GPS                                                                                                   |

| XI           | FU ALLOCATION AND AREA COMPARISON BETWEEN ACO AND FALLS USING THE TRIVIAL LIBRARY                                                                    |

| XII          | AVERAGE NUMBER OF FUS AND AREA (INCLUDING FU AREA AND<br>ARCHITECTURAL AREA) COMPARISONS AMONG COMPETING<br>ALGORITHMS USING THE NON-TRIVIAL LIBRARY |

| XIII         | AVERAGE ARCHITECTURE AREA, MAX CONGESTION AND<br>INTERCONNECTION COMPARISON AMONG COMPETING ALGORITHMS<br>USING THE NON-TRIVIAL LIBRARY              |

| XIV          | AVERAGE NUMBER OF FUS AND AREA (INCLUDING FU AREA AND ARCHITECTURAL AREA) COMPARISONS AMONG COMPETING ALGORITHMS USING THE TRIVIAL LIBRARY           |

# LIST OF TABLES (Continued)

## **TABLE**

## PAGE

| XV    | AVERAGE     |                  |          |          |          |         |         |      |

|-------|-------------|------------------|----------|----------|----------|---------|---------|------|

|       | INTERCONN   | ECTION CO        | MPARISC  | DN AMO   | NG COM   | PETING  | ALGORI  | ΓHMS |

|       | USING THE T | TRIVIAL LIB      | RARY     | •••••    |          | ••••••  |         | 119  |

| XVI   | AVERAGE     | RUNTIME          | COMPA    | RISON    | AMONG    | THE     | COMPE   | TING |

|       | ALGORITHM   | IS USING TH      | E NON-TI | RIVIAL L | JBRARY.  | •••••   | •••••   | 120  |

| XVII  | FU ALLOCA   | TION COMP.       | ARISON I | BETWEE   | N EXPLIC | ITLY PU | BLISHED | AND  |

|       | OUR ACO RE  | ESULTS USIN      | IG THE T | RIVIAL L | JBRARY.  |         |         | 123  |

| XVIII | AVERAGE N   | IFU AND RU       | UNTIME ( | IN SECO  | NDS) RES | SULTS O | F FALLS | AND  |

|       | OUR ACO IN  | <b>IPLEMENTA</b> | TION WI  | TH DIFF  | ERENT N  | UMBER   | OF ANTS | AND  |

|       | ITERATIONS  | USING THE        | TRIVIAL  | LIBRAR   | Υ        |         |         | 124  |

# LIST OF FIGURES

| <u>FIGURE</u> | PAGE                                                                                                                                                                    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | The pseudo code of ASAP scheduling                                                                                                                                      |

| 2             | The pseudo code of ASAP time updating algorithm                                                                                                                         |

| 3             | The pseudo code of ALAP scheduling                                                                                                                                      |

| 4             | The pseudo code of ALAP time updating algorithm                                                                                                                         |

| 5             | The pseudo code of list scheduling17                                                                                                                                    |

| 6             | The pseudo code of force-directed scheduling                                                                                                                            |

| 7             | The pseudo code of simulated annealing                                                                                                                                  |

| 8             | The pseudo code of PSA with the modified list scheduling                                                                                                                |

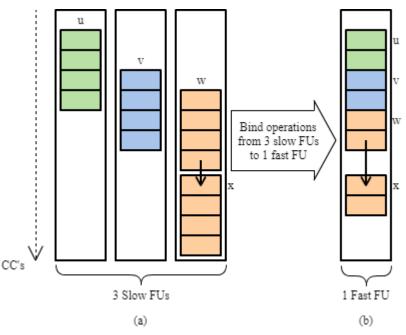

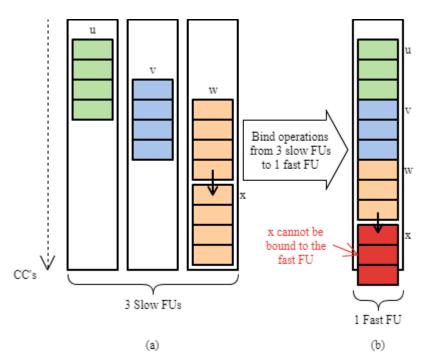

| 9             | An example for power reduction with module selection. The colors represent different operations and they are bound to FUs represented by large rectangles               |

| 10            | An example for unsuccessful power reduction with module selection. The colors represent different operations and they are bound to FUs represented by large rectangles  |

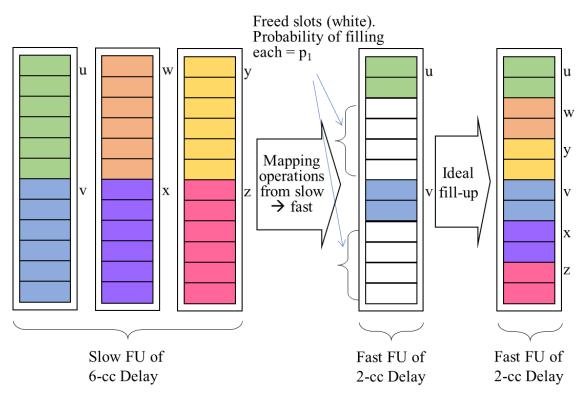

| 11            | Mapping operations from slow FUs to a fast FU 49                                                                                                                        |

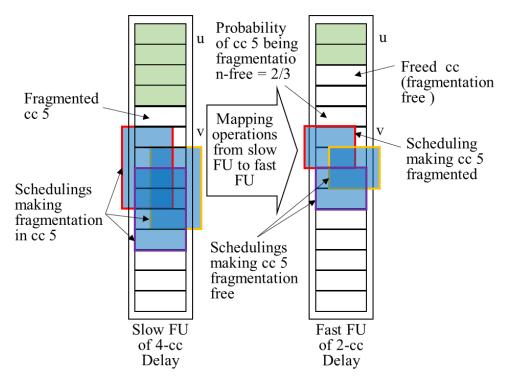

| 12            | Mapping operations from a slow FU to a fast FU does not always cause fragmentation in the latter, allowing more scheduling flexibility on the latter than the former 52 |

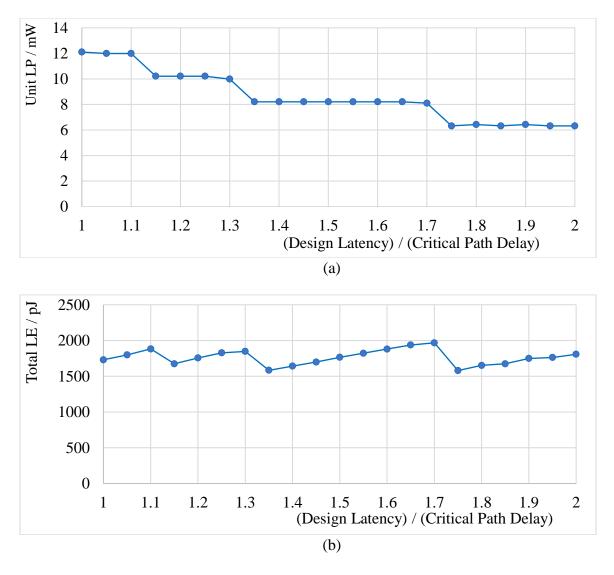

| 13            | (a) Unit LP results and (b) total LE results obtained by PR-GPS under different latency constraints for the DFG idctcol                                                 |

| 14            | The pseudo code of LPR-GPS algorithm76                                                                                                                                  |

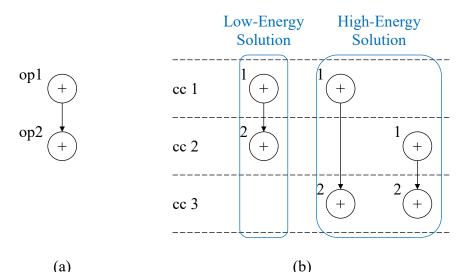

| 15            | (a) An unscheduled DFG with two operations op1 and op2. (b) All three solutions to schedule the DFG subject to a latency constraint of 3 cc's                           |

| 16            | An example to illustrate that the RMS-based metric estimate is an improvement over FDS force for a min-max goal                                                         |

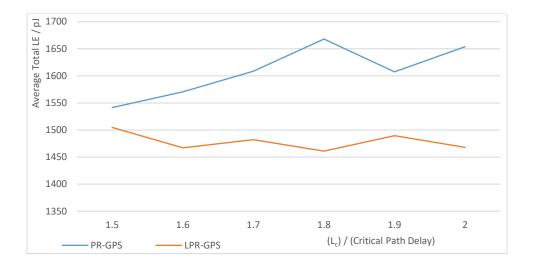

| 17            | Average total LE comparison between PR-GPS and LPR-GPS subject to different latency constraints                                                                         |

# LIST OF FIGURES (Continued)

| <u>FIGURE</u> | PAGE                                                                                                                                                                                                                                                                |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

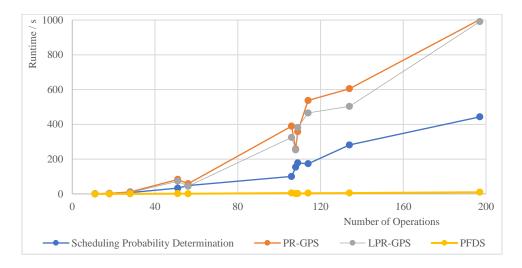

| 18            | Runtime comparisons among initial scheduling probability determination, PFDS, PR-GPS and LPR-GPS                                                                                                                                                                    |

| 19            | The pseudo code of our FALLS algorithm                                                                                                                                                                                                                              |

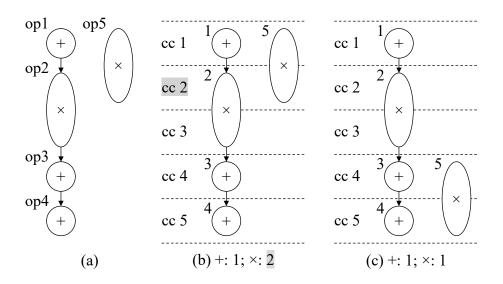

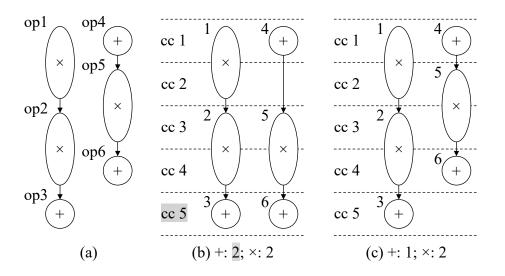

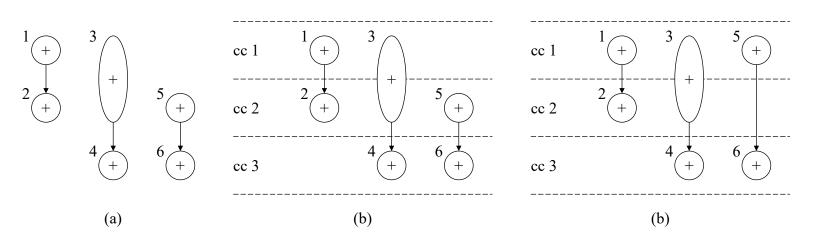

| 20            | Illustration of the advantage of reserving FUs for later use in the lookahead scheduling of FALLS. "opi" denotes operation i. FU allocation results shown below solutions. (a) An unscheduled DFG; (b) The solution of LS; (c) The solution of lookahead scheduling |

| 21            | Illustration of the benefit of early allocation of new FUs in the lookahead scheduling of FALLS. FU allocation results shown below solutions. (a) An unscheduled DFG; (b) The solution of LS; (c) The solution of lookahead scheduling                              |

| 22            | Graphical illustration of a single iteration of fractional search for a FT 107                                                                                                                                                                                      |

| 23            | Illustration of the benefit of FU pre-allocation estimate in fractional search of FALLS. (a) An unscheduled DFG; (b) The solution of the lookahead scheduling; (c) The solution of the lookahead scheduling with fractional search                                  |

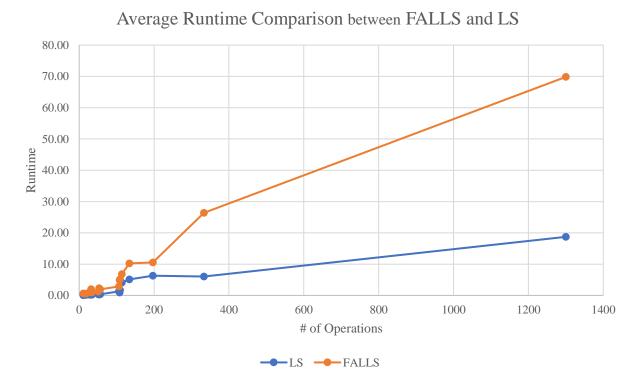

| 24            | Average runtime comparison in milliseconds between FALLS and LS 121                                                                                                                                                                                                 |

# LIST OF ABBREVIATIONS

| ACO   | Ant Colony Optimization                               |

|-------|-------------------------------------------------------|

| ALAP  | As Late As Possible                                   |

| ALU   | Arithmetic Logic Unit                                 |

| ASAP  | As Soon As Possible                                   |

| ASIC  | Application-Specific Integrated Circuit               |

| сс    | Clock Cycle                                           |

| CLA   | Carry-Lookahead Adder                                 |

| CSA   | Carry-Select Adder                                    |

| DFG   | Data Flow Graph                                       |

| DG    | Distribution Graph                                    |

| DP    | Dynamic Power                                         |

| DVFS  | Dynamic Voltage and Frequency Scaling                 |

| EDG   | Effective Distribution Graph                          |

| FA    | Full Adder                                            |

| FALLS | FrActional search and Lookahead based List Scheduling |

| FDS   | Force-Directed Scheduling                             |

| FT    | Function Type                                         |

| FU    | Functional Unit                                       |

| GPM   | Global Probability Map                                |

| HLS   | High-Level Synthesis                                  |

| IC    | Integrated Circuit                                    |

# LIST OF ABBREVIATIONS (Continued)

| ILP     | Integer Linear Programming                                  |

|---------|-------------------------------------------------------------|

| LE      | Leakage Energy                                              |

| LP      | Leakage Power                                               |

| LPR-GPS | Latency times unit Power minimization via RMS-driven Global |

|         | Probability map based Scheduling                            |

| LS      | List Scheduling                                             |

| ME-LCS  | Minimum-Energy Latency-Constrained Scheduling               |

| ML-RCS  | Minimum-Latency Resource-Constrained Scheduling             |

| MP-LCS  | Minimum-Power Latency-Constrained Scheduling                |

| MR      | Mobility Range                                              |

| MR-LCS  | Minimum-Resource Latency-Constrained Scheduling             |

| PDG     | Power Distribution Graph                                    |

| PDP     | Power-Delay-Product                                         |

| PS      | Predecessor/Successor                                       |

| PSA     | Power Simulated Annealing                                   |

| RCA     | Ripple-Carry Adder                                          |

| RMS     | Root-Mean-Square                                            |

| RTL     | Register-Transfer Level                                     |

| SA      | Simulated Annealing                                         |

| UIC     | University of Illinois at Chicago                           |

#### SUMMARY

Power, energy and resource minimization subject to a latency constraint are important optimization objectives in operation scheduling in high-level synthesis. The research work presented herein aims to address each of the objective as follows.

First, we proposed that the degree of optimization achievable in high-level synthesis (HLS) designs with functional unit (FU) or module selection is significantly dependent on how the FUs in the resource library are parameterized. For power minimization, our proposal is that appreciably more power optimization is possible when:

- the FUs for each function type (FT) have a wide range of both power and delay metrics;

- their pair-wise power-delay product ratios are close to 1, say, in the range [0.8, 1.25], than when these criteria are not satisfied.

We showed that it is possible to achieve these parameter ranges for arithmetic FTs due to design variety and flexibility to hierarchically combine different design approaches. We also provided a probabilistic rationale for our hypotheses and further bolster it empirically by constructing different FU libraries that either meet or do not meet the above FU parameter criteria. Using a new power-driven simulated annealing (SA) based algorithm PSA, we consistently found that the power consumption of designs using libraries that meet our criteria are significantly lower than those that do not.

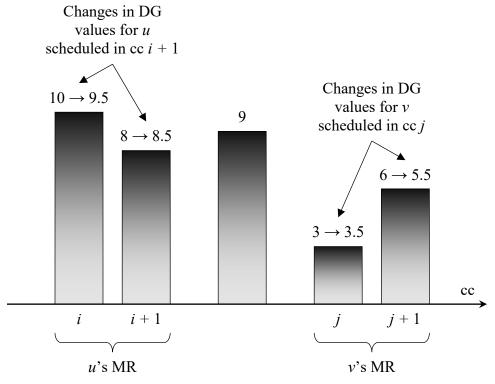

Then, we proposed a leakage energy (LE) minimization scheduling algorithm LPR-GPS. It co-explores unit-time leakage power (LP) and latency spaces in order to minimize their product. LPR-GPS extends the classical force-directed scheduling (FDS) by:

### **SUMMARY** (Continued)

- an initial probabilistic distribution graph (DG) based on a non-uniform probability-driven randomized scheduling that yields the final starting scheduling probabilities that are conducive to LE minimization;

- a root-mean-square (RMS) based estimation of the maximum FU usage distributed across cc's that contributes to LE minimization;

- a fast and greedy noncommittal scheduling algorithm for estimating the latency by scheduling output operations first.

Experimental results show LPR-GPS reduces total LE by an average of 44% compared to the power-driven FDS and 12% compared to a version of LPR-GPS that only minimizes unit-LP.

Finally, we proposed an iterative list scheduling (LS) type algorithm FALLS to minimize the total number of FUs allocated, and thus the total area, in HLS designs. FALLS incorporates a novel lookahead technique to selectively schedule available non-0-slack operations by allocating the needed FUs earlier or reserving available FUs for scheduling more timing-urgent operations later, such that no additional FU is needed and a higher FU utilization is obtained. Further, a fractional search framework is developed to iteratively estimate the number of FUs of each FT required in the final design based on the current scheduling and FU utilization, and reiterate the lookahead-based list scheduling with the new FU allocation estimate to further increase FU utilization. Experimental results comparing FALLS with several state-of-the-art algorithms using a non-trivial FU library show an average 18.9% to 71.4% FU reduction while only has 5.5% optimality gap compared to an optimal integer linear programming (ILP) formulation. FALLS also performs much better in architectural area (FU + mux/demux + register area), interconnect

# **SUMMARY** (Continued)

congestion and number of interconnects than state-of-the-art approximate algorithms, and is at most 4.0% worse in these metrics than the optimal ILP method.

### 1. INTRODUCTION

### 1.1. High-Level Synthesis

As the semiconductor technology node keeps moving towards the nanometer regime, and the transistor count on a chip significantly increases, it becomes more and more challenging to effectively and efficiently design modern integrated circuits (ICs). Thus, IC designers pay their attention to specifying the design in high-level languages like systemC, Verilog and VHDL, while relying on design tools to automatically transform the high-level design specification into the corresponding digital hardware implementation. The process executed by the tool is known as *high-level synthesis* (*HLS*) or *behavioral synthesis*.

HLS is crucial in the IC design flow, as the optimization applied at an earlier level is much more effective and efficient than a later one. For power optimization surveyed in [7], power saving opportunity at HLS is 8 to 12.5 times more than that at register-transfer level (RTL) and 20 times more than that at logic or physical level. Further, optimization effort at HLS is hundreds of times less than that at RTL and at least thousands of times less than that at logic and physical level.

#### 1.2. Operation Scheduling

HLS tools schedule operations in the design specification to control steps or clock cycles (cc's), perform module selection to determine which speed type (see Section 1.3 for definition) functional unit (FU) to be used for each operation, allocate FUs and bind the operations to allocated FUs, to maximize or minimize an objective function subject to various design constraints. The first functionality, known as *operation scheduling*, is an important optimization problem to be solved, since the scheduling solution determines FU allocation and an approximate

binding, and hence plays a key role in the IC design flow. The operation scheduling problem is known to be NP-hard, and thus requires effective and efficient heuristic or stochastic algorithms to be developed.

#### 1.3. <u>Problem Category</u>

Conventional operation scheduling problems in HLS are:

- Minimum-latency resource-constrained scheduling (ML-RCS): minimizing latency of the scheduling solution given resource constraints;

- Minimum-resource latency-constrained scheduling (MR-LCS): minimizing the total number of resources or a weighted sum of the number of resources of each type (functional type combined with one or more parameter values, like speed, power and area) used in the scheduling solution given a latency constraint.

In modern semiconductor industry, performance is no longer a main design objective. Instead, power and energy have become first-order design consideration for most computational devices. High power-consuming ICs deplete battery energy rapidly and cause reliability problems due to localized hot spots and phenomenon such as electromigration. Area is another consideration for some wearable and size-sensitive devices. All these make ML-RCS a less attractive problem.

Latency-constrained operation scheduling problems are therefore more interesting problems to be solved. MR-LCS is important since resource usage is strongly correlated to leakage energy (LE) and area. It also reduces interconnect complexity. However, although MR-LCS has been investigated for decades, current algorithms and methods cannot achieve good optimization quality and low runtime simultaneously. Besides, performance-constrained power and energy minimization have become new problems to be solved. Thus, in addition to the wellknown ML-RCS and MR-LCS problems, we define:

- Minimum-power latency-constrained scheduling (MP-LCS): minimizing the total power (sum of dynamic power and leakage power) of the scheduling solution given a latency constraint;

- Minimum-energy latency-constrained scheduling (ME-LCS): minimizing the total energy (sum of dynamic energy [DE] and leakage energy [LE]) of the scheduling solution given a latency constraint;

If a resource library has only one combination of delay, area, dynamic power (DP) and leakage power (LP) for each function type (FT) in the library, we call such library a *single-speed library*. Likewise, if there are more than one combination of delay, area, dynamic power and leakage for each FT in a resource library, we call such library a *multi-speed library*. If the input to ME-LCS is a single-speed library, the total dynamic power of the design will be a constant. Therefore, ME-LCS with a single-speed library is equivalent to minimize the total LE of the scheduling solution given a latency constraint. More details are presented in Section 5.1.

#### 1.4. <u>Previous Works</u>

There has been a considerable amount of work on operation scheduling. In this section, we will review the previous works in different problem categories.

### 1.4.1. <u>Power Minimization</u>

There is already a rich body of power minimization algorithms for HLS at different design levels. Some typical and recent works for each major approach are briefly discussed. Module selection in terms of multi- $V_{dd}$  and multi- $V_{th}$  assignment of FUs has been extensively studied. In [8], a near-optimal dynamic power optimization algorithm by achieving maximum number of low- $V_{dd}$  operations and minimum switching activity by solving a min-cost network

flow problem is proposed. Works in [9] [10] present heuristic approaches for incremental high- $V_{th}$  reassignment for minimizing LP. Other popular techniques like bus binding, clock/power gating and dynamic voltage and frequency scaling use extra control logic to slowdown or turn off inactive FUs or registers to save power. The work in [11] performs optimal bus binding optimization and rescheduling simultaneously to reduce total bus switching activity. An ILP formulation aiming at low-power area-efficient clock gating is proposed in [12]. All the algorithms and techniques discussed above have some similarities: they either adopt a scheduling solution from any known scheduling algorithm as one of the inputs to their algorithm, or iteratively modify an initial scheduling solution to explore new solution space for a different optimization objective. Apparently, a good scheduling solution can help these algorithms to achieve higher optimization quality on their objectives of interest.

There are a few works that are motivated by the well-known force-directed scheduling (FDS) [13] [14]. The technique in [15] enumerates all resource sharing combinations and evaluates the switching activity associated with them, to reduce the total dynamic power. In [16], multi- $V_{dd}$  assignment is used to reduce average and peak dynamic power across all cc's. The iterative scheduling process of FDS is maintained while a dynamic power force is used to evenly schedule operations to cc's and hence minimizes peak dynamic power. Besides, a post-rescheduling process to rebind operations from high- $V_{dd}$  to low- $V_{dd}$  FUs is proposed to minimize the average power.

#### 1.4.2. Energy Minimization

A few research works minimize energy from different directions. Early scheduling algorithms tried to indirectly minimize energy by minimizing a correlated optimization objective. In [17], a FDS-type algorithm was developed to iteratively schedule an operation to a cc, which is greedily guided by an energy function. The energy function is in fact balancing operations across cc's and thus is similar to FDS for minimizing FUs. Later, an ILP formulation with multi- $V_{dd}$  was proposed in [18] that yields optimal energy solutions. However, it is impractical for large designs due to its exponential runtime complexity. Recent heuristic works also utilized multi- $V_{dd}$  to minimize energy. A convex cost network flow model and a branch and bound method to assign frequency for each cc were proposed in [19].

To the best of our knowledge, and as indicated in a recent survey of low-power HLS [7], no previous scheduling algorithm with a single-speed library has addressed the issue of directly minimizing the total LE of a computation, or, equivalently, of the corresponding data-flow graph (DFG), which is the most important metric to minimize in systems that do not operate continuously.

#### 1.4.3. FU Minimization

The ILP formulation proposed in [20] [21] provides optimal scheduling solutions for FU minimization, but it is impractical for large designs due to its exponential runtime complexity. FDS presented in [13] [14] schedules operations iteratively by choosing the best scheduling option that best balances the operation execution distribution across all cc's using the concept of minimum "force", and thereby minimizes the number of FUs required. The sub-optimality of FDS stems from its greedy and sequential scheduling option selection and a lack of lookahead. In addition, the high runtime complexity of  $O(n^3)$  (*n* is the number of operations) motivates several refinements [22] [23]. The technique in [22] gradually reduces the time frame in which an operation can be scheduled by eliminating the current worst scheduling option. In addition, they modify the formulation of the spring constant in FDS forces which only consider the operation distribution in local cc's, to a global spring constant that considers the maximum operation

distribution in all cc's. In [23], an incremental force calculation was proposed by utilizing the fact that many operations have their time frame unchanged after an operation is scheduled. Some stochastic methods to solve the FU minimization problem have also been widely investigated. A simulated annealing (SA) approach was proposed in [24] and its move set guarantees that the complete solution space can be explored (i.e., the solution space graph is connected). In [25], the authors develop an ant-colony based algorithm to gradually approach a good solution by iteratively and probabilistically generating scheduling solutions based on which the scheduling probabilities are updated. In [26], the scheduling order of operations are determined by a genetic algorithm and then they can be scheduled by a constructive scheduling technique. All the above stochastic methods have high runtime for a good quality solution to be found, which prevents them to be effective for large problem sizes.

List scheduling (LS) is a classical algorithm for latency-constrained FU minimization. It schedules operations in as early cc's as possible if FUs are available, while greedily avoiding allocating new FUs unless it is mandatory for satisfying the latency constraint. Though the scheduling solution of LS is far from optimal due to many FUs allocated in intermediate and late cc's being sparsely utilized, its runtime complexity of  $O(n \log n)$  is very scalable. Therefore, several research works like [26] [27] [28] use LS or LS-type algorithms as an iterative internal sub-routine to achieve good optimization quality for their objectives of interests. Lookahead in LS has been studied in scheduling problems in non-HLS fields [29] [30]. Early lookahead in instruction scheduling like [29] helps LS with a bad "precedence function" (different from the one we will discuss) to avoid failed scheduling by tentatively scheduling some or all unscheduled operations. Recent works like [30] in heterogeneous computing use a lookahead approach to

exhaustively evaluate all candidate resources that can execute the scheduled operation, and chooses the resource that is most likely to lead to the smallest estimated latency.

#### 1.4.4. <u>Resource Library Construction</u>

To the best of our knowledge, there is no previous work aiming at multi-speed library construction. Further, we note here that previous module selection works used multi-speed libraries without paying attention to having appropriately parameterized FUs in them. For example, in [31] [32] [33] library characterizations are impractical or sub-optimal: the parameters of FUs in the library are not based on design realities and set artificially to meet the requirements of their designs. For example, the three adders considered in [31] have the same power-delay-products (PDPs), which is unrealistic in practice. The work in [32] also uses three adders but with PDP ratios of 1: 1.5: 1.33, which is somewhat sub-optimal as discussed later in the thesis (it is possible to design arithmetic FUs to have PDP ratios closer to but a little higher than 1). These simplifications neglect the importance of resource library construction that will be discussed later in the thesis.

### 1.5. <u>Contributions</u>

In this thesis, we propose the following three operation scheduling algorithms aim to three different optimization objectives. The algorithms and their advantages are as below:

• Our Power-driven Simulated Annealing (PSA) algorithm solves the MP-LCS problem given a multi-speed library:

- The simulated annealing (SA) framework of PSA can be combined with any good scheduling algorithm for enhancing different optimization objectives.

- Compared to the optimal integer linear programming (ILP) for MP-LCS, it has an average optimality gap of only 5.9% and is 193 times faster.

• Latency times unit Power minimization via our RMS-driven Global Probability map based Scheduling (LPR-GPS) algorithm that solves ME-LCS problem given a single-speed library:

- ME-LCS has never been investigated in previous works.

- Compared to two algorithms that only optimize the leakage power, LPR-GPS significantly reduces total LE by an average 37.05% and 12.41%, respectively, with reasonable runtime overhead.

- Our FrActional search and Lookahead based List Scheduling (FALLS) algorithm to solve MR-LCS problem given a single-speed library:

- Compared to several state-of-the-art algorithms, FALLS reduces the total number of FUs allocated by [18.9%, 71.4%].

- Compared to the optimal ILP for MR-LCS, it has an average optimality gap of only 5.5%.

- FALLS is extremely fast: it is 278k times faster than ILP and yields good solutions for a DFG of 1300 operations in less than a second.

Besides the algorithms above, we proposed power-delay criteria for multi-speed library construction for better power optimization, in a direction that no previous work has targeted. Using PSA as an experimental platform, designs using the libraries that meet our criteria has significantly lower power consumption than those that do not, including when the former have fewer combinations of power and delay per FT (i.e., fewer speeds and hence a smaller solution space) than the latter.

## 1.6. <u>Thesis Outline</u>

The rest of the thesis is organized as follows. In Chapter 1, we formally formulate the operation scheduling problem and review several conventional scheduling algorithms to which our algorithms will be compared to. Our power minimization scheduling algorithms PSA [1] [2]

and its experimental results are presented in Chapter 3. We then present our library construction hypotheses proposed in [1] [3] for power optimization and provide a theoretical justification for them in Chapter 4. In the same chapter, we present library construction examples and use PSA as a platform to empirically prove our hypotheses. Our energy minimization scheduling algorithm LPR-GPS [4] and its experimental results are presented in Chapter 5. Our scheduling algorithm FALLS [5] [6] for FU minimization and its experimental results are presented in Chapter 6. Finally, we conclude in Chapter 7.

## 2. BACKGROUND

In this chapter, we first give the formal and general formulation of operation scheduling problems with single-speed library and multi-speed library. Then several conventional scheduling algorithms that frequently appear in literatures are reviewed and discussed. Our algorithms introduced in later chapters are motivated and based on the algorithms in this chapter. Our experiments will compare our algorithms to some of these algorithms.

### 2.1. General Problem Formulation

We consider the following general operation scheduling problem with the optimization objective unspecified. Given:

- An unscheduled DFG G (V, E), where V is the set of operations, and E is the set of arcs representing data dependencies between the operations;

- A legal upper-bound latency constraint *L<sub>c</sub>* in number of cc's that is no smaller than the ASAP latency or the critical path delay;

- An FU library *K* that includes FU designs for each FT that appears in the operations in *V*. The library can be a single-speed library or a multi-speed library.

For any two operations  $u, v \in V$  and a data dependency arc  $(u, v) \in E$ , if u and v are scheduled in cc's  $t_u$  and  $t_v$ , respectively, the *dependency constraint* is:

$$t_u + d_u \le t_v \tag{2.1}$$

where  $d_u \ge 1$  is the operation delay of *u* in number of cc's, *u* is the *predecessor* of *v* and *v* is the *successor* of *u*.

Our objective is to schedule each operation in V to a certain cc and choose an appropriate FU design to execute the operation if a multi-speed library is used. Meanwhile, the optimization

objective, *cost*, is minimized, the achieved latency  $L \le L_c$  and all dependency constraints are satisfied. The costs that we are interested in this thesis are power, energy and total number of FUs, which we will further define in later chapters.

### 2.2. <u>As-Soon-As-Possible Scheduling</u>

As-Soon-As-Possible (ASAP) scheduling is one of the two simplest scheduling algorithms in HLS. As indicated by its name, the algorithm schedules each operation in the DFG to the earliest cc in which the operation can possibly be scheduled. Thus, the solution yielded by ASAP scheduling has the minimum latency, called the *ASAP latency* or the *critical path delay*, but is very likely to unnecessarily allocate extra FUs. ASAP scheduling can be performed if only the operation delays are known.

The ASAP scheduling is formulated as follows. For any operation u that has no predecessors, i.e.,  $pred(u) = \emptyset$ , its ASAP scheduled cc  $t_u^{ASAP}$  is simply:

$$t_u^{ASAP} = 1 \tag{2.2}$$

For *u* that has at least one predecessors, its ASAP scheduled cc  $t_u^{ASAP}$  is determined by:

$$t_u^{ASAP} = \max_{v \in pred(u)} (t_v^{ASAP} + d_v)$$

(2.3)

Let the number of operations in *V* be *n*. The algorithm analyzes all operations in O(n) time and in the worst case evaluates all predecessors of all operations in O(n) time. The time complexity is thus  $O(n^2)$ . However, each operation usually has limited predecessors that can be counted as a constant *c* that is far smaller than *n* in practice. Thus, ASAP scheduling is very fast. The pseudo code of ASAP scheduling is presented in Figure 1.

| Algorithm ASAP(DFG $G(V, E)$ , a single-speed library $K$ )        |

|--------------------------------------------------------------------|

| 1. While (there are unscheduled operations)                        |

| 2. If (the unscheduled operation <i>u</i> has no predecessor)      |

| 3. Schedule <i>u</i> per Equation (2.2)                            |

| 4. <b>Else if</b> (the predecessors of <i>u</i> are all scheduled) |

| 5. Schedule <i>u</i> per Equation (2.3)                            |

| 6. End If                                                          |

| 7. End While                                                       |

| 8. <b>Return</b> the scheduling solution                           |

Figure 1. The pseudo code of ASAP scheduling.

### 2.2.1. ASAP Time Updating

ASAP scheduling itself is not practically useful due to its excessive hardware usage. However, it provides important timing information for more advanced scheduling algorithms to make better scheduling decisions. For example, ASAP time provides the upper bound of the cc's in which an operation can possibly be scheduled in FDS and SA. In these algorithms, ASAP times often requires updating every time an operation is scheduled to provide the most up-to-date timing information. For example, let the ASAP time of operation *u* and *v* be 1 and 2, respectively, {*u*, *v*} = *V*, (*u*, *v*) = *E* and  $L_c = 4$ . If *u* is scheduled in cc 2 and *v* is still unscheduled, the updated ASAP time of *u* and *v* is 2 and 3, respectively, since the ASAP time of *u* is equal to its scheduled cc and *v* can no longer be scheduled in cc 2. The ASAP time updating can be done by reperforming the entire ASAP scheduling with the timing of scheduled operations updated in Figure 1, but also can be done by an updating strategy that only explores the operations that are affected.

The ASAP time updating algorithm recursively explores the predecessors of current operation, which is the newly scheduled operation initially. For each current predecessor being explored, all its successors are examined: if any of them results in an updating of the current predecessor's ASAP time, the predecessors of the current predecessor are examined in the next recursion. The recursion stops when no further predecessors' ASAP time need to be examined. In fact, the algorithm uses depth-first search to traverse the partial DFG that is only affected by the newly scheduled operation, and hence has a complexity of O(n) which is much faster than reperforming ASAP scheduling. The pseudo code of the ASAP time updating algorithm is presented in Figure 2.

```

Algorithm updateASAP(newly scheduled operation u)

1. If (this is not the initial function call)

For (each predecessor v of u)

2.

If (t_v^{ASAP} + d_v > t_u^{ASAP})

3.

\dot{t}_u^{ASAP} = \dot{t}_v^{ASAP} + d_v

4.

5.

End if

6.

End for

If (t_{u}^{ASAP} is not updated in the for-loop above)

7.

8.

Return

9.

End if

10. End if

11. For (each successor w of u)

If (w is not scheduled)

12.

updateASAP(w);

13.

14.

End if

15. End for

16. Return

```

Figure 2. The pseudo code of ASAP time updating algorithm.

## 2.3. <u>As-Late-As-Possible Scheduling</u>

As-Late-As-Possible (ALAP) scheduling is the other simplest scheduling algorithms in HLS and is symmetry to ASAP scheduling. As indicated by its name, the algorithm schedules each operation in the DFG to the latest cc in which the operation can possibly be scheduled. Thus, the solution yielded by ALAP scheduling has the maximum latency that is equal to the latency constraint, but is also very likely to unnecessarily allocate extra FUs. ALAP scheduling can be performed if only the operation delays are known. Given a legal latency constraint  $L_c$  that is no smaller than the ASAP latency, the ALAP scheduling is formulated as follows. For any operation u that has no successor, i.e.,  $succ(u) = \emptyset$ , its ALAP scheduled cc  $t_u^{ALAP}$  is simply:

$$t_u^{ASAP} = L_c - d_u + 1 \tag{2.4}$$

For *u* that has at least one successor, its ALAP scheduled cc  $t_u^{ALAP}$  is determined by:

$$t_u^{ALAP} = \min_{v \in succ(u)} (t_v^{ALAP}) - d_u$$

(2.5)

Similar to ASAP scheduling, the algorithm also has a time complexity  $O(n^2)$  and is very fast in practice. The pseudo code of ALAP scheduling is presented in Figure 3.

| <b>Algorithm ALAP</b> (DFG $G(V, E)$ , a single-speed library K, a legal latency constraint $L_c$ ) |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1. While (there are unscheduled operations)                                                         |  |  |  |  |  |

| 2. If (the unscheduled operation <i>u</i> has no successor)                                         |  |  |  |  |  |

| 3. Schedule <i>u</i> per Equation (2.4)                                                             |  |  |  |  |  |

| 4. <b>Else if</b> (the successor of <i>u</i> are all scheduled)                                     |  |  |  |  |  |

| 5. Schedule $u$ per Equation (2.5)                                                                  |  |  |  |  |  |

| 6. End If                                                                                           |  |  |  |  |  |

| 7. End While                                                                                        |  |  |  |  |  |

| 8. <b>Return</b> the scheduling solution                                                            |  |  |  |  |  |

6. Keturn the scheduling solution

Figure 3. The pseudo code of ALAP scheduling.

## 2.3.1. <u>ALAP Time Updating</u>

Similar to ASAP scheduling, ALAP scheduling itself is not practically useful but provides important timing information for more advanced scheduling algorithms to make better scheduling decisions. For example, ALAP time provides the lower bound of the cc's in which an operation can possibly be scheduled in FDS and SA; it also provides timing-urgency of available operations in LS. In some of these algorithms, ALAP times often requires updating every time an operation is scheduled to provide the most up-to-date timing information. For example, let the ALAP time of operation u and v be 3 and 4, respectively,  $\{u, v\} = V$ , (u, v) = E and  $L_c = 4$ . If v is scheduled in cc 3 and u is still unscheduled, the updated ALAP time of u and v is 2 and 3, respectively, since the ALAP time of v is equal to its scheduled cc and u can no longer be scheduled in cc 3. Symmetry to ASAP time, the ALAP time updating can be done by reperforming the entire ALAP scheduling with the timing of scheduled operations updated in Figure 3, but also can be done by an updating strategy that only explores the operations that are affected as presented in Figure 4.

| - 6 |                                                           |

|-----|-----------------------------------------------------------|

|     | Algorithm updateALAP(newly scheduled operation <i>u</i> ) |

|     | 1. If (this is not the initial function call)             |

|     | 2. For (each successor $v$ of $u$ )                       |

|     | 3. If $(t_v^{ALAP} - d_u < t_u^{ALAP})$                   |

|     | 4. $t_u^{ALAP} = t_v^{ALAP} - d_u$                        |

|     | 5. End if                                                 |

|     | 6. End for                                                |

|     | 7. If $(t_u^{ALAP}$ is not updated in the for-loop above) |

|     | 8. <b>Return</b>                                          |

|     | 9. End if                                                 |

|     | 10. <b>End if</b>                                         |

|     | 11. For (each predecessor $w$ of $u$ )                    |

|     | 12. If (w is not scheduled)                               |

|     | 13. $updateALAP(w);$                                      |

|     | 14. End if                                                |

|     | 15. End for                                               |

|     | 16. <b>Return</b>                                         |

| 1   |                                                           |

Figure 4. The pseudo code of ALAP time updating algorithm.

## 2.4. List Scheduling

Here we discuss the classical latency-constrained list scheduling (LS) algorithm for MR-LCS problem using a single-speed library. In each cc, LS always schedules the most timingurgent operations to available FUs. Starting with a minimum FU allocation, a new FU is only allocated when there is an available operation that needs to be scheduled immediately to satisfy the latency constraint, but there is no allocated FU of that FT currently available due to being busy executing other operations. By only allocating new FUs when it is mandatory, LS was expected to come close to minimizing the number of allocated FUs in the final scheduling solution. However, LS fails to achieve this goal due to the low FU utilization mentioned later in the section.

The pseudo code of LS is presented in Figure 5. Initially, only one FU per FT is allocated. The ALAP time  $t^{ALAP}$  is computed for each operation. Then in each cc t in chronological order, for each FT k, an available unscheduled operation set  $U_{t, k} \in V$ , which includes all unscheduled operations of FT k whose predecessors have all finished execution, is determined. The slack  $s_u$  of each operation u in  $U_{t, k}$  is then computed as:

$$s_u = t_u^L - t \ u \in U_{t,k} \tag{2.6}$$

If  $s_u = 0$ , *u* is *0-slack* and must be scheduled in cc *t*, i.e., one additional FU needs to be allocated if all FUs of FT *k* are busy executing other operations. The other operations in  $U_{t,k}$  are *non-0slack*. If there are still available FUs after all 0-slack operations are scheduled, the non-0-slack operations are scheduled in *t* and bound to the available FUs in slack-increasing order. This slack-based scheduling process iterates for each *t*, until all operations are scheduled.

We term the FU allocation vector r (one element per FT) before any operation is scheduled as pre-allocation; it is only one FU per FT in LS; Similarly, the FU allocation vector rafter all operations are scheduled is termed as post-allocation. In practice, the number of FUs in post-allocation is significantly more than that in pre-allocation in the solutions of LS, indicating many FUs are allocated in intermediate cc's. This results in the FUs allocated in later cc's being sparsely utilized. Due to the insufficient FU utilization, excessive FUs are likely to be allocated in the solutions of LS.

| Algorithm LS(DFG $G(V, E)$ , a single-speed library K, a legal latency constraint $L_c$ )      |

|------------------------------------------------------------------------------------------------|

| 1. $\mathbf{r} = (1, 1,, 1), t = 1$ //allocate one FU per FT before scheduling                 |

| 2. Compute the ALAP times $t^{ALAP}$ per $L_c$                                                 |

| 3. While (there are unscheduled operations)                                                    |

| 4. For (each FT $k$ )                                                                          |

| 5. Determine the available unscheduled operation set $U_{t,k}$                                 |

| 6. Compute slack $s_u$ for all $u \in U_{t,k}$ by Equation (2.6)                               |

| 7. Schedule 0-slack operations in $U_{t, k}$ to t, allocate new FUs if needed, update $r_k$ if |

| new FUs are allocated                                                                          |

| 8. Schedule non-0-slack operations in $U_{t, k}$ to t in slack-increasing order and bind       |

| them to remaining available FUs                                                                |

| 9. End For                                                                                     |

| 10. $t = t + 1$                                                                                |

| 11. End while                                                                                  |

| 12. <b>Return</b> the scheduling solution                                                      |

Figure 5. The pseudo code of list scheduling.

## 2.4.1. Complexity

The time complexity of LS is  $\Theta(n \log n)$ , since each sorting or searching operation in a balanced binary search tree based on ALAP times (equivalent to slack) takes  $\Theta(\log n)$  time, and the total number of searches = total number of available FUs across all clock cycles =  $\Theta(n)$ .

## 2.5. Force-Directed Scheduling

Force-directed scheduling (FDS) introduced in [13] [14] also target on MR-LCS problem with a single-speed library. As discussed earlier, FDS reduces the number of FUs in the design by evenly scheduling operations in all cc's to balance the FU distribution. In each scheduling iteration, FDS evaluates all *scheduling options*, the unscheduled operations and the candidate cc's where they can possibly be scheduled, and chooses the scheduling option to make scheduling that is probabilistically expected to minimize the sum of number of FUs allocated across all FTs. The fact, however, is that, conceptually and analytically speaking, FDS has some weakness in achieving this. The steps of FDS are summarized as follows and the pseudo code is presented in Figure 6.

### 2.5.1. <u>Scheduling Probabilities Determination</u>

First, the ASAP and ALAP times of all operations are determined by ASAP and ALAP scheduling, respectively. Then the *mobility*  $\mu_u$ , the number of cc's in which an operation *u* can be scheduled, is:

$$\mu_u = t_u^{ALAP} - t_u^{ASAP} + 1 \tag{2.7}$$

and the *mobility range* (MR) of  $u MR_u$  is  $[t_u^{ASAP}, t_u^{ALAP}]$ . The uniform scheduling probability  $p_u(i)$  of u in cc i is:

$$p_{u}(i) = \begin{cases} \frac{1}{\mu_{u}} & i \in MR_{u} \\ 0 & otherwise \end{cases}$$

(2.8)

Note that at any intermediate stage during the scheduling process, i.e., after some operations have been scheduled, the  $t_u^{ASAP}$  and  $t_u^{ASAP}$  of an unscheduled operation u are updated by substituting the scheduled cc  $t_v$  of each scheduled predecessor and successor v, if any, in place of  $t_v^{ASAP}$  and  $t_v^{ALAP}$  in Equations (2.2) to (2.5), respectively.

## 2.5.2. Distribution Graph Construction

For each FT, a distribution graph (DG) provides the expected FU usage in each cc. It is constructed by summing up all scheduling probabilities of operations of the same FT in each cc. The distribution value DG(k, i) of FT k in cc i is computed as:

$$DG(k,i) = \sum_{u \in V(k)} p_u(i)$$

(2.9)

where V(k) is the set of operations of FT *k*. Note that DG(k, i) is the expected number of operations and thus FUs of FT *k* executing in cc *i*. Also,  $DG(k) = \{DG(k, i): 1 \le i \le L_c\}$  is the DG of FT *k*, and  $DG = \{DG(k): k \text{ is a FT} \text{ in the DFG}\}$  is the overall DG for the given DFG. It should be noted that the largest distribution value  $DG_{max}(k)$  gives a probabilistic estimate of the number of FUs of FT *k* to be allocated in the design. The value is more accurate with more operations

scheduled and finally becomes deterministic after all operations are scheduled. The goal of FDS is to minimize

$$\sum_{k \in K} DG_{max}(k) \tag{2.10}$$

after all operations are scheduled. In every scheduling iteration, in which an operation u is scheduled, all affected DG(k, i)'s are updated to account for the zeroing of scheduling probabilities of u in cc's other than the one in which it has been scheduled or in general will be executing (in which this probability is 1), the shrinking of the MRs of some predecessors and successors of u and thus changes in their corresponding scheduling probabilities in the cc's of their original MR's. At any stage of the scheduling process, the DG provides a snapshot of scheduling probabilities across the operation and cc spaces, and thus the expected number of operations and FUs of each FT k in each cc. This also means that for each scheduling decision, we can estimate the global metric of interest, like Equation (2.10).

### 2.5.3. Self-Force Formulation

A self-force is calculated for each scheduling option. The self-force  $SF_u(i)$  for scheduling operation *u* of FT *k* in cc *i* is defined as:

$$SF_u(i) = \sum_{x \in MR_u} \sum_{y \in DR_u(x)} DG(k, y) \times \Delta p_u(x)$$

(2.11)

where  $DR_u(x)$  is the delay or execution range  $[x, x + d_u - 1]$  of u scheduled in cc x, and

$$\Delta p_u(x) = \begin{cases} 1 - p_u(x) & x = i \\ -p_u(x) & x \in MR_u - \{i\} \end{cases}$$

(2.12)

The self-force formulation assigns high weights to the probability changes  $\Delta p_u(x)$ 's in cc's that have high DG values, indicating scheduling in such cc's increases the risk to have an unbalanced FU distribution. On the other hand, if an operation is scheduled in a cc that has a low DG value, the weighted positive probability increment is comparably small, and the weighted negative probability decrement in other cc's in u's MR are comparably large, reflecting a good choice to flatten the DG and reduce the high DG values. Thus, a scheduling option with the smallest self-force is expected to minimize the maximum DG value, and hence the number of FUs of u's FT.

#### 2.5.4. <u>Predecessor/Successor and Total Force Formulation</u>

A predecessor/successor (PS) force is calculated for each scheduling option in a way similar to the self-force. Scheduling an operation is very likely to shrink the MR of its unscheduled predecessors and successors (by potentially decreasing their ALAP times or increasing their ASAP times, respectively), resulting in fewer opportunities to schedule them in cc's of low DG values at later scheduling iterations. Such an effect should also be considered by an overall force formulation. The PS-force  $PSF_u(i)$  for scheduling operation u in cc i is defined as:

$$PSF_{u}(i) = \sum_{v \in PS_{u}} \sum_{x \in MR_{v}} \sum_{y \in DR_{v}(x)} DG(type(v), y) \times \Delta p_{v}(x)$$

(2.13)

where  $PS_u = pred(u) \cup succ(u)$  and type(v) is the FT of a PS operation v, and

$$\Delta p_{\nu}(x) = p'_{\nu}(x) - p_{\nu}(x) \tag{2.14}$$

where  $p'_v(x)$  is the tentatively updated scheduling probability in cc x of the PS operation v for evaluating the scheduling option and  $p_v(x)$  is v's current scheduling probability in cc x. For example, suppose operation v, a predecessor of operation u, has a MR of 3 cc's,  $i_1$ ,  $i_2$  and  $i_3$ . According to Equation (2.8), the current scheduling probabilities  $p_v(i_1) = p_v(i_2) = p_v(i_3) = 1/3$ . If u is tentatively scheduled and hence v's MR temporarily shrinks to 2 cc's,  $i_1$  and  $i_2$ , due to a decrease in v's ALAP time. The tentatively updated MR of v leads to a tentatively updated scheduling probability  $p'_v(i_1) = p'_v(i_2) = 1/2$  and  $p'_v(i_3) = 0$ . Similar to the self-force, the PSforce of a scheduling option measures its probabilistic effect on the sum of DG values of all FTs among its predecessors and successors; the smaller the PS force, the smaller the sum of weighted probability changes of the local (within the MRs of u's predecessors and successors) DG values

among all related FTs.

Finally, the total force  $F_u(i)$  to evaluate the scheduling of operation u in cc i is given as:

$$F_u(i) = SF_u(i) + PSF_u(i) \tag{2.15}$$

| <b>Algorithm FDS</b> (DFG $G(V, E)$ , a single-speed library K, a legal latency constraint $L_c$ ) |

|----------------------------------------------------------------------------------------------------|

| 1. While (there are unscheduled operations)                                                        |

| 2. Update ASAP and ALAP times of unscheduled operations                                            |

| 3. Update the distribution graph per Equation (2.9) based on the updated ASAP and                  |

| ALAP times and the scheduled cc's of scheduled operations                                          |

| 4. <b>For</b> (each unscheduled operation <i>u</i> )                                               |

| 5. For (each cc $i$ in $MR_u$ )                                                                    |

| 6. Calculate self-force, PS-force and total force per Equations (2.11) to (2.15)                   |

| 7. End For                                                                                         |

| 8. End For                                                                                         |

| 9. Pick the scheduling option with the minimum total force to schedule                             |

| 10. End while                                                                                      |

| 11. <b>Return</b> the scheduling solution                                                          |

| Figure 6. The pseudo code of force directed scheduling                                             |

Figure 6. The pseudo code of force-directed scheduling.

# 2.5.5. <u>Complexity and Optimality Analysis</u>

The time complexity of FDS is analyzed as follows. FDS schedules one operation per iteration, therefore there are  $\Theta(n)$  scheduling iterations. In each scheduling iterations, there are O(n) unscheduled operations to be evaluated: the worst case happens in the first iteration when all operations are unscheduled. Finally, there are O(n) PS operations that need to consider in the PS-force. The nested triple *n*'s results in a total time complexity of  $O(n^3)$ .

As suggested by Equation (2.10), the objective of FDS is minimizing the sum of maximum distribution values of all FTs, a min-max goal. The problem with the FDS force formulation is that it essentially captures the difference between the DG value of the to-be-scheduled cc and the average DG value of all other cc's in the MR of each unscheduled

operation being evaluated, while any estimate of the increase or decrease in the maximum DG value(s) is not accounted for unless the maximum DG value lies in the MR of an operation. Further, across the forces of all scheduling options, the least force generally does not correspond to the largest decrease or smallest increase of the maximum DG value due to the aforementioned property of what the force measures. Thus, the scheduling decisions are actually not made based on this most important consideration, and hence FDS cannot guarantee a good approximation of the min–max goal.

To frame the above discussion more analytically, the self-force expression of Equation (2.11) for scheduling operation u in cc i, assuming uniform probabilities and a single cc delay, can be re-formulated as:

$$SF_{u}(i) = DG(k, i) - \sum_{x \in MR_{u}} DG(k, x) \times p_{u}(x)$$

=  $DG(k, i) - \frac{1}{|MR_{u}|} \sum_{x \in MR_{u}} DG(k, x)$  (2.16)

This shows that the force formulation of FDS yields the lowest force among all scheduling possibilities to be the one that corresponds to the largest difference between the average DG value in an operation's MR and the DG value in its scheduling cc. Clearly, this has a weak correlation to reducing the current maximum DG value. Therefore, the scheduling option evaluation in FDS is significantly flawed.

## 2.6. <u>Simulated Annealing</u>

Simulated annealing (SA) is a probabilistic method for approximating the global minimum of a cost function. It is often used when the solution space is discrete. Various SA formulations are thus proposed for operation scheduling problem. Many optimization objectives

in operation scheduling can be solved by SA with the corresponding cost functions. We will introduce the SA formulation for general latency-constrained scheduling with a single-speed library in this section. Based on [24] [25], our literature review and experiments, we believe this SA formulation provides the best scheduling solutions with a reasonable runtime.

The main idea of SA is that it considers some neighboring state P' of the current state P, and probabilistically determines whether to move the system to the new state P' or stay in state P. These moves ultimately lead the system to a state of near-optimal cost. The steps are summarized as follows:

1. Generate an initial state and configure the initial temperature  $T_0$  and the freezing temperature  $T_f$ .

2. Generate a new state in the neighborhood of the current state.

3. Change to the new state with a probability  $min\{1, e^{-\frac{c_{new}-c}{T}}\}$ , where  $c_{new}(c)$  is the cost of the new (current) solution and *T* is the current temperature.

4. Repeat steps 2 and 3 until the cost of new solutions does not change much, then decrease *T* base on a cooling scheme.

5. Repeat steps 2 to 4 until  $T \leq T_f$ .

There are several performance-related configurations that can be applied to SA. Each of the configurations that we choose is detailed in the following subsections. The pseudo code of our SA is presented in Figure 7.

# 2.6.1. Initial Solution

The initial solution of SA determines the optimization starting point. It is supposed to be generated fast and has a not-too-bad cost. As discussed in [25], ASAP and ALAP scheduling do not yield good initial solutions since they tend to cluster operations in earlier or later cc's, which

is bad for minimizing resource usage. Further, ALAP scheduling is even worse in energy minimization since the latency of the solution is not minimized and it also makes SA moves harder to change the initial solution towards a low-cost direction. LS also suffers from the same limitation of ASAP and ALAP scheduling. FDS is too slow for large DFGs due to its high time complexity. Therefore, we construct an initial solution by randomly picking an operation, scheduling it to a random cc to its MR, updating the MRs of unscheduled operations and iterating the random scheduling process until all operations are scheduled. The runtime complexity of the randomized scheduling process is  $O(n^2)$ , since there are *n* iterations and at most *n* options (in the first iteration) for the randomization algorithm to choose.

# 2.6.2. <u>Temperature</u>

Similar to the SA introduced in [25], we use the well-known geometric cooling scheme that is also used in [34]. The temperature decreasing factor is set to 0.9. When the current temperature reaches the freezing temperature, the best solution is reported.

However, it is not clear how the initial and freezing temperatures are determined in [25]. We adopt the idea in [35] that is also used in [24]: set the initial temperature so that the statistical probability to accept a cost-increasing move is high (e.g., 80%), and set the freezing temperature so that the statistical probability to accept such a move is very low (e.g., 1%). To be specific, before the annealing process, we generate a number of moves (e.g., 2*n*) to the initial solution and get the average cost of new solutions that have increased costs. We can then set the initial and freezing temperatures based on the average cost and the Boltzmann probability  $e^{-\frac{c_{new}-c}{T}}$  for accepting cost-increasing moves. This allows the SA to fully explore the global solution space at the beginning and the local minimum at the end.

### 2.6.3. Local Search and Move Set

The local search is to generate a number (e.g., 2n as in [25]) of successful moves in the current temperature.

Though the move sets in [24] [25] can guarantee that the entire solution space can be reached by the moves, every move makes only a little modification (e.g., reschedule an operation to the neighboring later cc in its MR and push the scheduled cc's of affected successors to their neighboring later cc's) the current solution. This is hard for SA to explore the solution space that is very different from the current solution and hence is less likely to fully explore the solution space for searching the global minimum. Further, the moves in [25] are very likely to fail since a move would be rejected if rescheduling an operation would violate the dependency constraint in its predecessor or successors. Checking dependency constraints for this situation is also time-consuming.

Our move set has 3 moves: up-move, down-move and random-move. The first two moves cover all four moves in [24], and the last move enables broader and more efficient solution space searching. Each of the moves are defined as follows:

- Up-move: Randomly choose an operation to reschedule it to a neighboring earlier cc in its MR and reschedule affected predecessors to their neighboring earlier cc's. The move fails if the randomly chosen operation was scheduled in the earliest cc in its MR.

- Down-move: Randomly choose an operation to reschedule it to a neighboring later cc in its MR and reschedule affected successors to their neighboring later cc's. The move fails if the randomly chosen operation was scheduled in the latest cc in its MR;

- Random-move: Randomly choose an operation and randomly reschedule it to another cc in its MR. The move fails if the randomly chosen operation has a MR = 1.

**Algorithm SA**(DFG G(V, E), a single-speed library K, a legal latency constraint  $L_c$ ) 1. ASAP and ALAP scheduling to determine initial MRs 2. Generate an initial scheduling solution *S* by randomization 3. Adaptively calculate the initial temperature  $t = t_0$  and the freezing temperature  $t_e$ 4. While  $(t > t_e)$ 5. **For** (*i* from 0 to 2*n*) Randomly generate a successful move and hence a new solution  $S_n$ 6.  $S = S_n$  according to the probability  $min \left\{ 1, e^{-\frac{S_n.cost-S.cost}{T}} \right\}$ 7. 8. i = i + 19 End for t = 0.9t10. 11. End While 12. Return the scheduling solution

Figure 7. The pseudo code of simulated annealing.

# 2.7. Integer Linear Programming