# Cryptographic Security: Countermeasures against Side-Channel Attacks

BY

KUN MA B.S. Jilin University, Changchun, China, 2006 M.S. Beijing University of Posts and Telecommunications, Beijing, China 2009

#### THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2014

Defense Committee:

Wenjing Rao, Chair and Advisor Zhichun Zhu Ashfaq Khokhar Venkatakrishnan Venkatesan Natarajan, Computer Science Kaijie Wu, Chongqing University

## ACKNOWLEDGMENTS

I would like to thank my advisors, Professor Wenjing Rao and Professor Kaijie Wu, for all their guidance, support and encouragement throughout my Ph.D study and research. Professor Wu introduced me to the interesting field of side channel attacks and countermeasures. Discussing with him has always been inspiring and helpful. My research work would not be made possible without the guidance of Professor Wu. We have been keeping research interations after he left University of Illinois at Chicago. I'm very grateful for his thoughtful support during the tough times. Professor Rao has been my advisor after Professor Wu left. Her insightful comments and suggestions on my research are important to me towards better work. I'm really grateful for her support in my last year of Ph.D study.

My sincere thanks also goes to my dissertation committee, Professor Zhichun Zhu, Professor Ashfaq Khokhar, Professor Venkat Venkatakrishnan, for valuable comments and suggestions. Special thanks to Professor Zhichun Zhu, who overcame every difficulties to join my dissertation defense even when she was on sabbatical and Professor Ashfaq Khokhar for his help in offering financial support when he was the Director of Graduate Studies in University of Illinois at Chicago.

Thanks to my family. My husband and my parents have been unconditionally supporting and encouraging me. They have always been the source of my strength.

# ACKNOWLEDGMENTS (Continued)

$\mathbf{K}\mathbf{M}$

# TABLE OF CONTENTS

# **CHAPTER**

# PAGE

|   | INTRO                    | DUCTION                                                       |  |  |  |

|---|--------------------------|---------------------------------------------------------------|--|--|--|

|   | 1.1                      | Cryptography                                                  |  |  |  |

|   | 1.2                      | Public Key Cryptography and Applications                      |  |  |  |

|   | 1.3                      | Security of Public Key Cryptography: A Mathematical Point     |  |  |  |

|   |                          | of View                                                       |  |  |  |

|   | 1.4                      | Side Channel Attacks                                          |  |  |  |

|   | 1.4.1                    | Timing Attacks                                                |  |  |  |

|   | 1.4.2                    | Power Analysis Attacks                                        |  |  |  |

|   | 1.4.3                    | Electromagnetic Analysis Attacks                              |  |  |  |

|   | 1.4.4                    | Fault Attacks                                                 |  |  |  |

|   | 1.5                      | Contributions                                                 |  |  |  |

| 2 | PRELIN                   | MINARIES                                                      |  |  |  |

|   | 2.1                      | Finite Fields                                                 |  |  |  |

|   | 2.1.1                    | Prime Field                                                   |  |  |  |

|   | 2.1.2                    | Binary Finite Field                                           |  |  |  |

|   | 2.2                      | Elliptic Curves                                               |  |  |  |

|   | 2.3                      | Elliptic Curve Scalar Multiplication                          |  |  |  |

|   | 2.3.1                    | Basic Algorithms                                              |  |  |  |

|   | 2.3.2                    | Montgomery Ladder Algorithm                                   |  |  |  |

|   | 2.3.3                    | Fast $\widetilde{\mathrm{ECSM}}$ over $\mathbb{F}_{2^m}$      |  |  |  |

|   | 2.4                      | Modular Exponentiation                                        |  |  |  |

|   | 2.4.1                    | Algorithms                                                    |  |  |  |

|   | 2.4.2                    | Computing RSA Fast with Chinese Remainder Theorem $\ . \ .$ . |  |  |  |

|   | SIDE CI                  | HANNEL ATTACKS AND COUNTERMEASURES FOR                        |  |  |  |

| • | PUBLIC KEY CRYPTOSYSTEMS |                                                               |  |  |  |

|   | 3.1                      | Fault Attacks and Countermeasures                             |  |  |  |

|   | 3.1.1                    | Fault Injection and Fault Models                              |  |  |  |

|   | 3.1.2                    | Fault Attacks on ECC and RSA                                  |  |  |  |

|   | 3.1.3                    | Countermeasures against Fault Attacks                         |  |  |  |

|   | 3.2                      | Power Analysis Attacks and Countermeasures                    |  |  |  |

|   | 3.2.1                    | Power Analysis Attacks on ECC and RSA                         |  |  |  |

|   | 3.2.2                    | Countermeasures against Power Analysis Attacks                |  |  |  |

# TABLE OF CONTENTS (Continued)

# <u>CHAPTER</u>

# PAGE

|                | The Proposed Low-cost Error Detection and Recovery Scheme | 48                                                            |     |  |  |  |

|----------------|-----------------------------------------------------------|---------------------------------------------------------------|-----|--|--|--|

| 4.1.1 The Idea |                                                           | The Idea                                                      | 49  |  |  |  |

|                | 4.1.2                                                     | The LOEDAR Scheme                                             | 52  |  |  |  |

|                | 4.2                                                       | Analysis of Error Detection Capability                        | 55  |  |  |  |

|                | 4.2.1                                                     | Single Error Occurrence in ECSM/EDR                           | 58  |  |  |  |

|                | 4.2.2                                                     | Multiple Error Occurrences in ECSM/EDR                        | 66  |  |  |  |

|                | 4.3                                                       | Resistance to Fault Attacks                                   |     |  |  |  |

|                | 4.4                                                       | Extendibility to Thwart Power Analysis Attacks                | 70  |  |  |  |

|                | 4.5                                                       | The Experiments                                               | 74  |  |  |  |

|                | 4.5.1                                                     | Overhead                                                      | 74  |  |  |  |

|                | 4.5.2                                                     | Comparison to Existing Schemes                                | 77  |  |  |  |

|                | 4.5.3                                                     | Error Detection and Recovery Test with Random Fault Injection | 79  |  |  |  |

| 5              | A NEW                                                     | COUNTERMEASURE AGAINST FAULT ATTACKS                          |     |  |  |  |

|                | FOR RSA                                                   | <b>A</b>                                                      | 81  |  |  |  |

|                | 5.1                                                       | Overview                                                      | 81  |  |  |  |

|                | 5.2                                                       | The Proposed Concurrent Error Detection Scheme                | 83  |  |  |  |

|                | 5.2.1                                                     | The Basic CED Scheme                                          | 84  |  |  |  |

|                | 5.2.2                                                     | The Modified CED Scheme                                       | 86  |  |  |  |

|                | 5.2.3                                                     | The Enhanced CED Scheme                                       | 88  |  |  |  |

|                | 5.2.4                                                     | One for All: Unifying the CED Schemes                         | 89  |  |  |  |

|                | 5.3                                                       | Error Detection Capability and Resistance to Fault Attacks .  | 90  |  |  |  |

|                | 5.3.1                                                     | Intentional Faults                                            | 91  |  |  |  |

|                | 5.3.2                                                     | Accidental Faults                                             | 93  |  |  |  |

|                | 5.4                                                       | Performance and Cost                                          | 93  |  |  |  |

|                | 5.4.1                                                     | Performance                                                   | 95  |  |  |  |

|                | 5.4.2                                                     | Cost                                                          | 98  |  |  |  |

| 6              | TOWARI                                                    | <b>DS A COMPREHENSIVE COUNTERMEASURE AGAINS'</b>              | г   |  |  |  |

|                | MULTIP                                                    | LE SIDE CHANNEL ATTACKS                                       | 101 |  |  |  |

|                | 6.1                                                       | Overview                                                      | 101 |  |  |  |

|                | 6.2                                                       | Basic Principles to Construct a Flexible Comprehensive Scheme | 103 |  |  |  |

|                | 6.3                                                       | A Comprehensive Protection Scheme for RSA                     | 104 |  |  |  |

|                | 6.4                                                       | Techniques to Improve Resistance and Performance              | 107 |  |  |  |

|                | 6.4.1                                                     | Register Transfer Level Techniques                            | 108 |  |  |  |

|                | 6.5                                                       | Mask Reusing                                                  | 117 |  |  |  |

|                | 6.6                                                       | Security Analysis                                             | 120 |  |  |  |

|                | 6.6.1                                                     | Resistance to Fault Attacks                                   | 120 |  |  |  |

|                | 6.6.2                                                     | Resistance to Power Analysis Attacks                          | 126 |  |  |  |

|                | 6.7                                                       | Experiment Results                                            | 129 |  |  |  |

|                | 6.7.1                                                     | Hardware Cost and Performance                                 | 130 |  |  |  |

|                | 6.7.2                                                     | Simulation of Power Analysis Attacks                          | 130 |  |  |  |

|                |                                                           |                                                               |     |  |  |  |

# TABLE OF CONTENTS (Continued)

# **CHAPTER**

# PAGE

| 7 | CONCLUSION       | 136 |

|---|------------------|-----|

|   | CITED LITERATURE | 139 |

|   | VITA             | 148 |

# LIST OF TABLES

| TABLE |                                                                                                    | PAGE      |

|-------|----------------------------------------------------------------------------------------------------|-----------|

| Ι     | KEY LENGTH VS. SECURITY LEVEL                                                                      | 4         |

| II    | SECURITY STRENGTH TIME FRAMES                                                                      | 5         |

| III   | THE $F_A(O)$ AND $F_B(O)$ OF THE POINT ADDITION OF SCALAR MULTIPLICATION                           | 61        |

| IV    | THE $Pr_{undetected\ error}$ OF THE POINT ADDITION OF SCALAR<br>MULTIPLICATION                     | 64        |

| V     | LOEDAR'S COMPATIBILITY WITH COUNTERMEASURES AGAI<br>POWER ANALYSIS                                 | NST<br>72 |

| VI    | COMPARISON OF COUNTERMEASURES WHEN APPLIED TO LOEDAR                                               | 74        |

| VII   | THE AREA AND DELAY OF THE ARITHMETIC UNITS                                                         | 75        |

| VIII  | HARDWARE OVERHEAD                                                                                  | 75        |

| IX    | TIME OVERHEAD AND SWITCHING ACTIVITY OVERHEAD                                                      | 76        |

| Х     | COMPARISON OF THE AREAS OF THE ARITHMETIC UNITS                                                    | 78        |

| XI    | COMPARISON OF THE AREAS OF THE COMPLETE SCHEMES                                                    | 78        |

| XII   | COMPARISON OF PERFORMANCE                                                                          | 79        |

| XIII  | MAJOR STEPS OF CRT-RSA, VILIGANT ALGORITHM AND GIGRAUD ALGORITHM                                   | 94        |

| XIV   | PERFORMANCE COMPARISON OF CRT-RSA, VIGILANT AL-<br>GORITHM AND GIRAUD ALGORITHM AND OUR CED SCHEME | 2 96      |

| XV    | COMPARISON OF THE HARDWARE OVERHEAD OF MODU-<br>LUS EXTENSION                                      | 98        |

# LIST OF TABLES (Continued)

#

TABLE

|       | DATING FREQUENCIES                                                 | 120 |

|-------|--------------------------------------------------------------------|-----|

| XVIII | RESISTANCE TO POWER ANALYSIS ATTACKS                               | 128 |

| XIX   | THE AREA AND PERFORMANCE OF THE PROPOSED COM-<br>PREHENSIVE SCHEME | 130 |

| XX    | COMPARISON OF THE WAVEFORM                                         | 135 |

PAGE

99

# LIST OF FIGURES

| <b>FIGURE</b> |                                                                                       | PAGE |

|---------------|---------------------------------------------------------------------------------------|------|

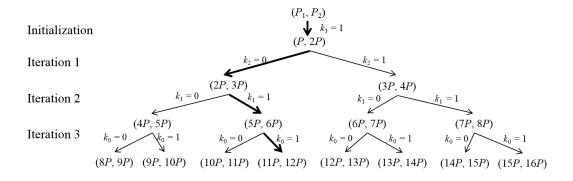

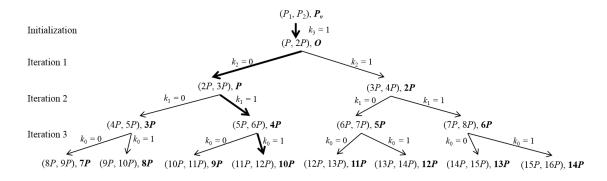

| 1             | Point updating graph of the Montgomery ladder algorithm                               | 49   |

| 2             | Point updating graph of the LOEDAR scheme                                             | 51   |

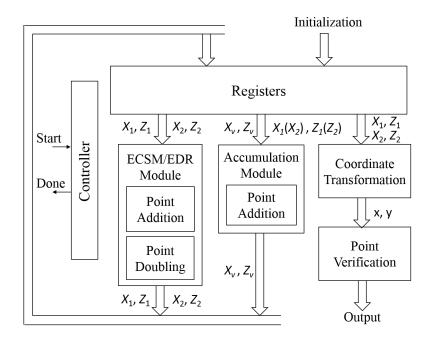

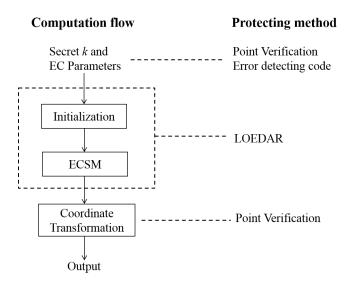

| 3             | The architecture of the LOEDAR scheme                                                 | 55   |

| 4             | LOEDAR's protection in the computation flow                                           | 56   |

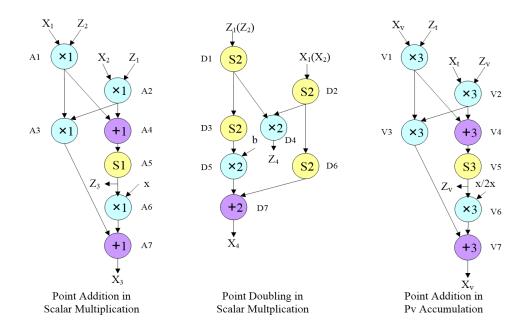

| 5             | DFG of point addition and point doubling in ECSM and $P_v$ accumulation               | n 59 |

| 6             | The unified CED scheme                                                                | 90   |

| 7             | The nested structure of single-purpose countermeasures in a comprehen-<br>sive scheme | 104  |

| 8             | The nested structure of the comprehensive scheme                                      | 106  |

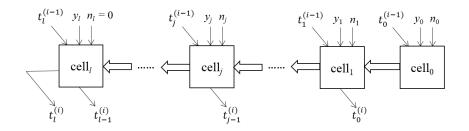

| 9             | The systolic architecture of modular multiplier                                       | 111  |

| 10            | An example: the working state of cells in systolic array                              | 112  |

| 11            | The schedule of cells for interleaving modular multiplications $\ldots \ldots$        | 114  |

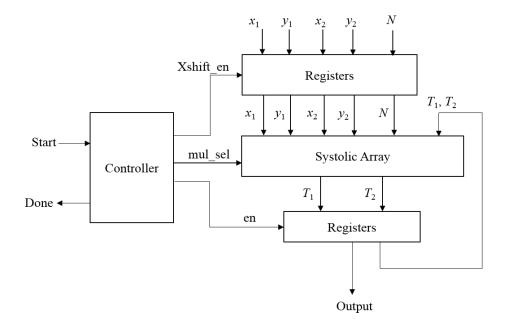

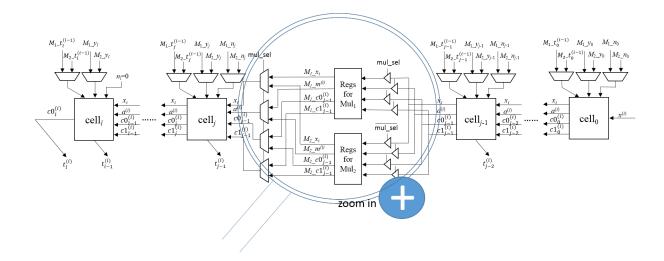

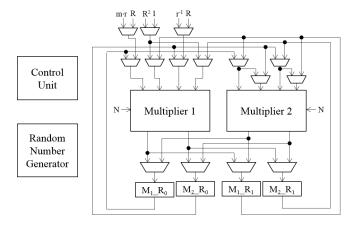

| 12            | The architecture of the modular multiplier                                            | 115  |

| 13            | Implementation of the interleaving modular multiplier                                 | 116  |

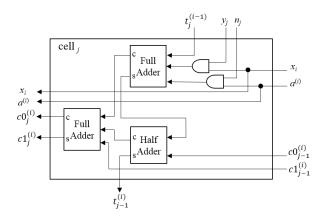

| 14            | The circuit of a cell the modular multiplier                                          | 116  |

| 15            | The hardware architecture of the comprehensive scheme $\ldots \ldots \ldots$          | 117  |

| 16            | Mask reusing for consecutive messages                                                 | 118  |

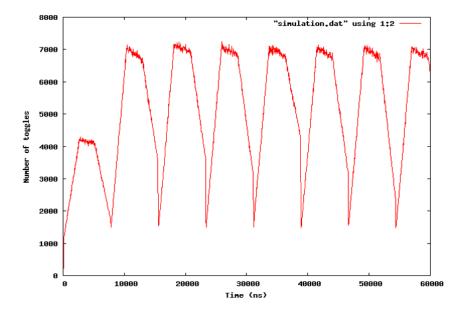

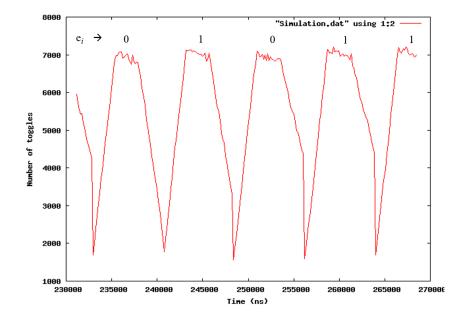

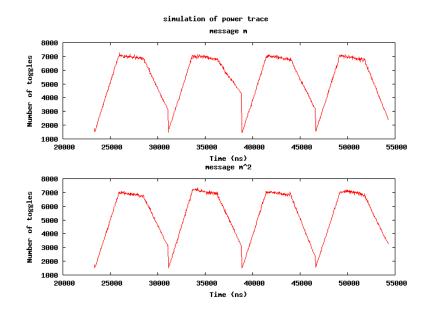

| 17            | Similation of the power trace using toggle counts                                     | 132  |

| 18            | Power trace of middle iterations for computing modular exponentiation                 | 133  |

# LIST OF FIGURES (Continued)

####

## SUMMARY

Side channel attacks have become a serious threat to a cryptosystem. Even if a cryptographic algorithm is mathematically secure, its software or hardware implementation may leak information through side channels. Side channel attacks exploit the side channel leakage to break a cryptosystem. A small amount of side channel information may be sufficient to compromise a cryptosystem which cannot be broken by pure cryptanalysis with current computing capability in limited time. As side channel attacks are not only powerful but also practical, protecting cryptosystem against side channel attacks is critical to ensure security in cryptographic applications.

This work aims at protecting public key cryptosystems against side channel attacks. Fault attack is one of the most powerful side channel attacks. In fault attacks, an attacker needs to induce faults to disturb the cryptosystem and reveal the secret information by analyzing the erroneous output or the reaction of the cryptosystem under faults. We present countermeasures against fault attacks for two widely used public key cryptosystems, Elliptic Curve Cryptography (ECC) and RSA. The countermeasures prevent the attacker from obtaining erroneous result through error detection. Although parallel computation with two identical datapaths or recomputation can verify the correctness of result, the high overhead in terms of hardware or time may not be acceptable. In this dissertation, we propose low-cost error detection methods for ECC and RSA as countermeasures against fault attacks.

### SUMMARY (Continued)

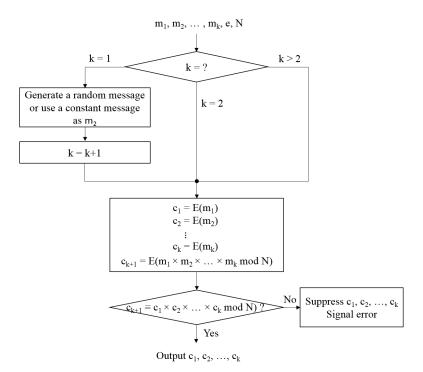

The error detection method for ECC shares the same design principle as the error detection method for RSA. We discover or construct an invariant in the ECC or RSA algorithm based on mathematical properties. The invariant is verified to detect errors. In the proposed error detection scheme for ECC, an invariant is constructed by introducing a new point in the Montgomery ladder algorithm. Meanwhile, it retains the property to compute ECC fast. The proposed scheme also supports fast recovery upon detecting errors. It saves the intermediate results as a checked state after their correctness is verified. Upon detecting errors, it can easily roll back to the previous checked state and restart computation from there rather than from the very beginning. The process reduces the loss in time to recover from error and hence improves the overall efficiency. This is desirable in mission-critical systems which are required to deliver service on time even in the events of natural or attacker-induced faults. The proposed error detection scheme for RSA exploits the multiplicative homomorphic property of RSA to construct an invariant. The invariant is verified for every k messages to detect errors. k can be adjusted to trade-off time overhead with storage overhead and output latency according to requirement of applications.

When designing the error detection schemes against fault attacks for ECC and RSA, we also take into account their extendibility to thwart other types of side channel attacks, e.g., power analysis attacks. In practice, public key cryptosystems are threatened by all types of side channel attacks since an attacker is able to choose any attacking approach. Protecting a cryptosystem against fault attacks is not sufficient to ensure security. Hence, extendibility or compatibility is important for a countermeasure to be useful in the face of various side channel

## SUMMARY (Continued)

attacks. The proposed scheme for ECC is compatible with most of the existing countermeasures against power analysis attacks. It is easy to extend it to thwart power analysis attacks. The proposed error detection scheme for RSA does not impose any requirement on how to compute modular exponentiation. Hence, it can work with any RSA architecture which could be a fine-tuned architecture resistant to other types of side channel attacks.

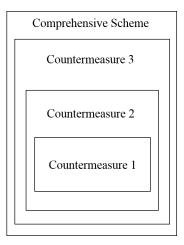

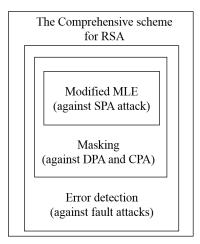

Although various countermeasures have been proposed to thwart side channel attacks, most of them target only one type of side channel attacks. With a rich variety of such singlepurpose countermeasures, we discuss how to construct a comprehensive countermeasure using the single-purpose countermeasures to thwart multiple types of side channel attacks. Combining the single-purpose countermeasures carelessly may create new leakage. We propose the basic principles to choose single-purpose countermeasures and construct a comprehensive one without compromising the security of any single-purpose countermeasure. Following the principles, we present a comprehensive scheme for RSA to thwart two of the most powerful side channel attacks, fault attacks and power analysis attacks. Techniques at hardware level are used to enhance the resistance to power analysis attacks and improve the overall performance of the scheme. Resistance to other types of side channel attacks can be integrated flexibly under the proposed principles. The constructing method can be used to create a comprehensive scheme for ECC cryptosystem.

## CHAPTER 1

## INTRODUCTION

Cryptography has been applied to secure communication for thousands of years. It enables communicating parties to exchange sensitive information securely over an insecure communication channel by encrypting messages. With the development of Internet and electronic techniques, cryptography is not limited to just a set of encryption mechanism. Modern cryptography is developed to provide new security properties for various applications and services. Examples include digital signature to demonstrate the authenticity of a digital document, user authentication to control access to some restricted services, data protection to prevent unauthorized use or reproduction of copyrighted files, etc.

### 1.1 Cryptography

Modern cryptography can provide confidentiality, data integrity, authentication and nonrepudiation. The purpose of confidentiality is to guarantee that the information cannot be disclosed by unauthorized users. Confidentiality is enforced by encryption. When two or more parties have to exchange sensitive information over an insecure communication channel, the communication parties encode sensitive information to a serial of unreadable codes using encryption algorithm, send them over the communication channel. Only the authorized parties can decode it. The received message, after decoded, should be exactly the same one sent by the sending party. This is referred to as data integrity. Accuracy and consistency of data should be maintained, and unauthorized modification violates data integrity. Besides verification of data integrity, the receiver should be able to verify the origin of data. It is achieved by authentication. Communication parties are able to validate identification each other through authentication. Non-repudiation prevents the sender of information from denying having sent it.

Different security goals can be achieved by different cryptographic schemes such as hash functions, secret key cryptography, public key cryptography, etc. Hash functions can be applied to verify data integrity. Hash function maps an arbitrary finite size of block data to a string of fixed length. Any modification of data will generally lead to different hash values. The Secure Hash Algorithm (SHA) is a family of hash functions published by National Institute of Standards and Technology (NIST) as Federal Information Processing Standards (FIPS). Secret key cryptography is also called symmetric key cryptography in which a single, shared, secret piece of information, called key, is used to encrypt and decrypt data. Data Encryption Standard (DES) and Advanced Encryption Standard (AES) are two well-known secret key cryptographic algorithms. AES has been announced as FIPS to supersede DES. Secret key encryption is fast and hence is suited to encryption of high volume of data. It can be used to encrypt messages in secure communication. When the communicating parties are located far away from each other, they have to agree on a secret key before encrypting messages. The exchange of secret key is addressed by public key cryptography. Public key cryptography, or asymmetric key cryptography, involves a pair of different keys, a public key and a private key. The public key is published openly and the private key is kept secret. Besides key establishment for secret key encryption, public key cryptography also plays an important role in digital signature. Digital signature addresses data authentication and non-repudiation. Analogous to ink signature in the real world, digital signature is used to authenticate signer in electronic world. A signer generates a signature for an electronic document using the private key, and anyone can verify the signature with the corresponding public key. Ronald Rivest, Adi Shamir and Leonard Adleman presented the first public key cryptographic scheme, RSA, in 1978 (1). RSA has been used as public key cryptographic scheme for decades. Elliptic Curve Cryptography, an alternative public key cryptographic approach, was introduced independently by Neal Koblitz (2) and Victor Miller (3) in 1985. NIST has included the schemes based on ECC in its recommended cryptographic algorithms (4).

In modern cryptography, key is an essential element to provide security properties. It is used in cryptographic algorithms to encrypt the plaintext or to decrypt the ciphertext. In cryptographic terminology, plaintext is the message to be encrypted and ciphertext is the encryption of plaintext. According to the basic principle of modern cryptography, Kerckhoffss principle, the security of a cryptosystem should depend on the secrecy of the key and not on the secrecy of cryptographic algorithm. Most modern cryptographic algorithms are designed under the assumption that the adversaries will gain full knowledge of the cryptosystem. In other words, the design of cryptosystem is not required to be secret. As a result, modern cryptography provides secrecy by just keeping relatively small keys secret. Key length is an important security parameter which is measured in bits of the key. It is always used to indicate the security strength of a cryptosystem, such as 256-bit AES, 2048-bit RSA. Generally speaking, increasing key length will gain the security strength, for example, 2048-bit RSA provides higher

### TABLE I

| Security strength (Bits) | ECC key length (Bits) | RSA key length (Bits) | AES key length (Bits) |

|--------------------------|-----------------------|-----------------------|-----------------------|

| 80                       | 163-223               | 1024                  | -                     |

| 112                      | 224-255               | 2048                  | -                     |

| 128                      | 256-383               | 3072                  | 128                   |

| 192                      | 384-511               | 7680                  | 192                   |

| 256                      | 512+                  | 15360                 | 256                   |

#### KEY LENGTH VS. SECURITY LEVEL

security than 1024-bit RSA. However, secret key cryptography and public key cryptography cannot be compared directly by key length for security level as they may have different levels of cryptographic complexity. The security levels are only estimated based on specific public key cryptographic algorithms. NIST guidelines give key length verses security level (5), as shown in Table I. 2048-bit RSA provides equivalent strength to 112-bit symmetric key algorithms. RSA requires much longer keys than ECC for the same security level. For example, 224-bit ECC would have the same strength as 2048-bit RSA.

As the length of key determines security level, it should be chosen according to the requirement of cryptographic applications. For security purpose, NIST also recommends the length of keys to ensure security in next two decades (5). Table II shows the recommendations when cryptographic protection is applied to data, where "Acceptable" means that the algorithm or key length is now known to be secure and "Disallowed" indicates that the algorithm or key length shall not be used.

## TABLE II

| Security Strength (Bits) | 2014 through 2030 | 2031 and beyond |

|--------------------------|-------------------|-----------------|

| 80                       | Disallowed        | Disallowed      |

| 112                      | Acceptable        | Disallowed      |

| 128                      | Acceptable        | Acceptable      |

| 192                      | Acceptable        | Acceptable      |

| 256                      | Acceptable        | Acceptable      |

### SECURITY STRENGTH TIME FRAMES

Even though the cryptographic schemes are designed for high theoretical strength, their implementations in hardware or software may leak information. Side channel attacks exploit the information leaked by physical implementation such as timing, power consumption, electromagnetic radiation and erroneous result to break a cryptosystem. In this dissertation, we focus on protecting public key cryptographic schemes against side channel attacks.

#### **1.2** Public Key Cryptography and Applications

Public key cryptography involves a pair of different keys, a public key and a private key. The public key is used for encrypting a message. The private key must be known to decrypt a ciphertext. The roles of keys are reversed in digital signature. The private key is used to sign a message, and the signature can be verified with the public key. Without knowing the private key, others should not be able to generate a valid signature.

In 1976, Whitfield Diffie and Martin Hellman presented the public key cryptosystem and discussed one-way functions to develop public key cryptosystem (6). A one-way function is a function such that it is easy to compute in one direction but very difficult to compute in the other. More precisely, a function f is a one-way function if it is easy to compute the y = f(x) for any argument x, yet, it is computationally infeasible to solve the equation for x given y, i.e.,  $x = f^{-1}(y)$ . If the inverse direction is easy to compute given a certain piece of information (the trapdoor), the one-way function is a trapdoor one-way function. Public key cryptosystems are based on trapdoor one-way functions. The private key gives information about the trapdoor. Lacking the trapdoor, one can only compute the function in the forward direction. The forward direction corresponds to encryption or signature verification. Knowing the trapdoor, one can compute the function in inverse direction which corresponds to decryption or signature generation.

RSA, presented by Rivest, Shamir and Adleman in 1978 (1), is still one of the most popular public key cryptosystems. The encryption function is based on modular exponentiation. A message m is encrypted by exponentiating m with a public key e, i.e.,  $c = m^e \mod N$ , where N is the product of two large primes p and q. The ciphertext c can be decrypted by computing  $m = c^d \mod N$  with the private key d. In digital signature, the signer performs modular exponentiation  $s = m^d \mod N$  with the private key d to generate the signature s, and the signature receiver uses the signer's public key e to verify the signature by computing  $m' = s^e \mod N$ . The signature is correct if and only if  $m' \equiv m \mod N$ . The message m may be pre-processed with a padding scheme agreed on by two communicating parties.

To generate the keys for RSA, two distinct prime numbers p and q are randomly selected. The length of p and q should be similar. Modulus N is computed as  $N = p \cdot q$ , and its Eulers totient function is  $\varphi(N) = (p-1)(q-1)$ . Then an integer *e* is chosen as the public key such that  $1 < e < \varphi(N)$ , *e* and  $\varphi(N)$  are coprime, i.e.,  $gcd(e, \varphi(N)) = 1$ . The private key *d* is computed as  $d = e^{-1} \mod \varphi(N)$ . Since *p*, *q* and  $\varphi(N)$  are used to compute the private key, they must also be kept secret besides the private key itself. For security reasons, *p* and *q* should be chosen with additional requirements described in Public Key Cryptography Standards (PKCS) #1 (7).

The correctness of RSA can be proved with Fermats little theorem. The theorem states that if p is a prime number and a is not divisible by p, then  $a^{p-1} \equiv 1 \mod p$ . According to the key generation procedure of RSA, the public key and the private key satisfy  $ed \equiv$  $1 \mod \varphi(N)$  where  $\varphi(N) = (p-1)(q-1)$ . By the definition of modular operation, ed - 1 =i(p-1)(q-1) for some nonnegative integer i. In RSA signature scheme, the signature is verified by computing  $s^e \mod N = (m^d)^e \mod N = m^{ed} \mod N$ . In RSA encryption scheme, the ciphertext is decrypted by computing  $c^d \mod N = (m^e)^d \mod N = m^{ed} \mod N$ . Using Fermats little theorem, we have

$$m^{ed} = m \cdot m^{(ed-1)} = m \cdot m^{i(p-1)(q-1)} = m \cdot (m^{(p-1)})^{i(q-1)} \equiv m \mod p \tag{1.1}$$

Similarly, we have

$$m^{e}d = m \cdot m^{(ed-1)} = m \cdot m^{i(p-1)(q-1)} = m \cdot (m^{(q-1)})^{i(p-1)} \equiv m \mod q$$

(1.2)

Therefore,  $m^e d \equiv m \mod p \cdot q$ .

As an alternative to RSA, ECC can achieve strong security level with relatively small keys. According to Table I, one should use 3072-bit RSA for 128-bit AES, while the equivalent key length for ECC is only 256 bits. ECC offers more security per bit increase in key length than RSA. Although elliptic curve arithmetic for ECC is slightly more complex than RSA, ECC is more computational efficient than RSA due to the increased security strength per bit of ECC.

ECC performs operations on elliptic curve. An elliptic curve is a set of points satisfying a curve equation along with a point at infinity. For cryptographic purpose, the elliptic curve is defined over a finite field. Elliptic curve arithmetic will be discussed in §2.2. Given a set of parameters which defines an elliptic curve and a base point P on the elliptic curve, the key pair (d, Q) is generated by a randomly selected non-zero integer d and a multiplication Q = dP. d is the private key and required to be kept secret, and Q is the public key which can be made public. The key generation procedure involves Elliptic Curve Scalar Multiplication (ECSM) which multiplies a point P on the elliptic curve with a scalar k, i.e., kP. The result is also a point on the curve. ECSM is the core operation in ECC-based cryptographic implementations.

In the Elliptic Curve Digital Signature Algorithm (ECDSA), which was standardized in FIPS 186-4 (8), the signer generates a key pair (d, Q) where d is the private signing key and Q = dP is the public key for signature verification. The signer chooses a per-message random integer k such that  $1 \le k \le n - 1$  where n is the order of base point P, i.e., n = ord(P). Then  $kP = (x_1, y_1)$  is computed, and the result  $x_1$  is converted to integer  $\overline{x_1}$  to compute  $r = \overline{x_1} \mod n$ . The message m is hashed to a bit string of length no more than n and is then converted to an integer e. Then s is computed as  $s = k^{-1}(e + dr) \mod n$ . The signature for message m is (r, s). Neither r nor s can be zero, otherwise the signature should be recomputed by choosing a new random integer k. To verify the received signature (r, s), the received message m is hashed and converted to an integer e. Then point X is computed as  $X = (x_1, y_1) = u_1P + u_2Q$ , where  $u_1 = ew \mod n$ ,  $u_2 = rw \mod n$  and  $w = s^{-1} \mod n$ . The signature is valid if and only if  $r = \overline{x_1} \mod n$  where  $\overline{x_1}$  is the integer computed from  $x_1$ .

The signature verification procedure can authenticate the signer. Suppose signature (r, s)is generated for message m. According to the signature generation procedure,  $s = k^{-1}(e + dr) \mod n$ . Hence  $k = s^{-1}(e + dr) \mod n$ . In the verification procedure,

$$u_1 P + u_2 Q = (u_1 + u_2 d) P = s^{-1} (e + dr) P = kP$$

(1.3)

Hence, only the signature generated by the message owner who has the private key can pass the verification procedure. It is crucial that the per-message random number k is kept secret, otherwise the private key d can be revealed by computing  $d = r^{-1}(ks - e) \mod n$ . The random number k should be used to sign only one message. If it is used to sign two different messages  $m_1$  and  $m_2$  with the same private key d and generate two signatures  $(r, s_1)$  and  $(r, s_2)$ , then k can be computed by  $k = (s_1 - s_2)^{-1}(e_1 - e_2) \mod n$ . Hence, d can be recovered by  $d = r^{-1}(ks - e) \mod n$ .

The Diffie-Hellman key exchange based on ECC, Elliptic Curve Diffie-Hellman (ECDH), is a variant of Diffie-Hellman key exchange protocol which enables communicating parties to establish a shared secret key for secret key encryption over an insecure communication channel. Suppose Alice and Bob are two communicating parties who want to exchange secret. They have to agree on a set of elliptic curve and domain parameters and each generates a pair of keys, i.e., a public key and a private key, for operation. Alice may randomly select an integer as her private key  $d_A$  and compute  $Q_A = d_A P$  as her public key, where P is the base point on the elliptic curve agreed upon. Similarly, Bob generates his key pair  $(d_B, Q_B)$ . Then Alice and Bob exchange their public keys over the insecure channel. Alice receives Bobs public key  $Q_B$  and she computes  $(x, y) = d_A Q_B$ . Bob receives Alices public key  $Q_A$  and he computes  $(x, y) = d_B Q_A$ . The value (x, y) computed by both parties are equal because  $d_A Q_B = d_A d_B P = d_B d_A P = d_B Q_A$ . Hence, it is a shared secret between Alice and Bob. The shared secret can be directly used as the secret key, but care should be taken to remove weak bits. Most standardized ECDH-based protocols derive the secret key from the shared secret.

ECDH immediately leads to the classic Elliptic Curve El-Gamal (EC-ElGamal) encryption. To encrypt a message m, a random number r is chosen, 1 < r < n where n = ord(P). Then we compute R = rP and c = rQ + m with the public key Q. The ciphertext is (R, c). To decrypt the ciphertext, we compute m = c - dR with the private key d (Q = dP). The classic EC-ElGamal encryption scheme is insecure against active attackers (9). Moreover, it requires that a mesage should be transformed to a point on the elliptic curve. This problem can be addressed by hashed ElGamal or the Elliptic Curve Integrated Encryption Scheme (ECIES). The hashed ElGamal appears in the ANSI X9.63 standard (10). In contrast to the classic EC-ElGamal, it applies a key derivation function H to rQ, i.e., k = H(rQ) where r is a random number and Q is the public key (Q = dP). And c is computed with a secret key encryption scheme,  $c = \mathcal{E}_k(m)$ . The ciphertext is (R, c) where R = rP. To decrypt the ciphertext, we compute  $k = H(d \cdot R)$  and  $m = \mathcal{D}_k(c)$ .

ECIES is the same as hashed ElGamal except that it includes Message Authentication Code (MAC) to prevent active attacks. It also appears in ANSI X9.63 standard (10).

#### 1.3 Security of Public Key Cryptography: A Mathematical Point of View

Public key cryptosystems are based on one-way functions which are believed to be computational infeasible to invert. RSA computes exponentiation modulo a composite number N. The composite number N is the product of two large primes p and q. Given p and q, it is easy to compute  $N = p \cdot q$ . However, inverting this function is difficult. Inverting the function is to find the factors p and q given N. The factorization problem is a hard mathematical problem when the numbers are very large and p, q are of similar size. No efficient factorization algorithm is known. The difficulty of solving the prime factorization problem is the basis of RSA security. The security of ECC is based on the difficulty of solving the Elliptic Curve Discrete Logarithm Problem (ECDLP). More specifically, given points P and Q on elliptic curve, it finds a number k that kP = Q and k is thus called the discrete logarithm of Q to the base P. As of now, RSA-768 has been successfully factored. The factorization work took almost 2000 2.2GHz-Opteron-CPU years (11). The record of solving ECDLP over 112-bit prime field was announced in 2010. The calculation took around 3.5 months on a cluster of more than 200 PlayStation 3 game consoles (12). The previous record solving the problem over 109-bit prime field was set in 2002 requiring 549 days of computing by more than 10,000 members in almost 250 teams, that is around 4000 to 5000 PC years. However, the key lengths used in practice are usually at least 1024 bits for RSA and at least 163 bits for ECC. NIST recommends the length of keys for public key cryptosystems to ensure security in next two decades (5). According to Table I and Table II, RSA 2048-bit and ECC at least 224-bit are considered to be secure before year 2030. With the length of key properly chosen based on the NIST recommendation, public key cryptosystem are now considered mathematically secure.

#### 1.4 Side Channel Attacks

In practice, however, public key cryptosystems are not secure enough as they are designed to be. Attackers can exploit the weakness in the software or hardware implementations of public key cryptosystems. The implementations leak additional information via side channels. Typical side channels include timing, power consumption, electromagnetic radiation, erroneous output, etc. A small amount of side channel information may be sufficient to break the cryptosystems. Side channel attacks exploiting side channel information require much less computing resources than mathematical cryptanalysis. They are powerful to break public key cryptosystems which are believed mathematically secure and hence become a serious threat. Side channel attacks can be classified in the following ways.

• Active vs. passive: Active attacks attempt to tamper the functionality of cryptographic device. For example, in fault attacks faults are induced to cryptographic device to generate erroneous output. Passive attacks collect side channel information by measuring the physical parameters, observing the behavior of cryptographic device. The functionality of cryptographic device is not disturbed.

• Invasive vs. non-invasive: Invasive attacks obtain side channel information in an invasive way such as depackaging the device. Different components of the device can then be accessed directly. In non-invasive attacks, the cryptographic device is intact and external information such as timing, power consumption are exploited.

Based on the types of side channel information exploited by attacks, side channel attacks can also be divided into timing attack, power analysis attack, fault attack, etc.

### 1.4.1 Timing Attacks

Timing attacks exploit the non-constant execution time of cryptographic algorithm to recover the secret information. The time variation can be caused by conditional branches in the algorithm, performance optimizations, etc. The execution time may be slightly different depending on the input data and secret key. Hence, the secret information can be derived by analyzing the time for each execution.

The timing characteristics in public key cryptosystems are more dependent on key than secret key cryptosystems. Hence, public key cryptosystems are more vulnerable to timing attacks.

The most obvious way to prevent timing attacks is to implement cryptographic algorithms such that the execution time is constant. This is often difficult. Another approach is to make timing measurements inaccurate by randomization techniques such as adding random delays. Attackers have to collect more measurements to compensate the noise caused by random delays. The fast increase of measurements required can make timing attacks infeasible.

#### 1.4.2 Power Analysis Attacks

Nowadays, CMOS technology is the predominant technology for digital integrated circuits. The dynamic power consumption of CMOS circuits depends on the change of data. Switching from logic 0 to logic 1 (i.e.,  $0 \rightarrow 1$ ) or from logic 1 to logic 0 (i.e.,  $1 \rightarrow 0$ ) consumes dynamic power, while staying at the same logic level (i.e.,  $0 \rightarrow 0$  and  $1 \rightarrow 1$ ) does not. Power analysis attacks exploit the dependence of the dynamic power consumption of a cryptographic device on the data it is processing to recover secret information.

Simple Power Analysis (SPA) attacks require only one power consumption trace over time. In SPA, an attacker identifies the key-dependent operations by observing the power consumption trace. Differential Power Analysis (DPA) attacks involve statistical analysis of correlation between the power consumption and the processed data. In DPA, an attacker makes a hypothesis on the partial key and computes the intermediate values from the key. The intermediate values are then transformed to leakage through a leakage model, e.g., Hamming weight model or Hamming distance model. The attacker performs statistical tests, e.g., distance-of-means, correlation analysis, on the leakage and the power consumption with a large number of power traces. A large correlation should appear for the correct hypothesis.

To prevent SPA attacks, key-dependent operations should be avoided or made indistinguishable in power consumption. DPA attacks can be prevented by hiding the power consumption or masking the data. Hiding reduces the correlation between intermediate data and power consumption by adding noise, reducing signal leakage or using a variable clock frequency. Masking makes intermediate data unpredictable, thereby breaking the correlation between intermediate data and power consumption.

More details on power analysis attacks on public key cryptosystems and countermeasures will be discussed in Chapter 3.

#### 1.4.3 Electromagnetic Analysis Attacks

Electromagnetic analysis (EMA) attacks exploit the leakage of electromagnetic fields due to current flows. Quisquater and Samyde presented the first EMA attack (13). They measured the electromagnetic radiation of a smart card with an oscilloscope, a flat coil and a Faraday cage. The measurement can be analyzed in a similar way to power analysis attacks. And similar to power analysis attacks, there are simple electromagnetic analysis (SEMA) attacks and differential electromagnetic analysis (DEMA) attacks.

EM radiation can be measured from a distance. Hence, the measurement may be more noisy compared to the power measurement in power analysis attacks.

Countermeasures against EMA attacks include confining the radiation by metal layers, blurring the radiation with an active emitting grid, canceling the radiation using dual logic, etc.

#### 1.4.4 Fault Attacks

In contrast to timing attacks, power analysis attacks and electromagnetic analysis attacks, fault attacks are active attacks which require an attacker to induce faults into cryptographic device when it is performing computation. The erroneous output is analyzed to reveal the secret information. To thwart fault attacks, error detection can be performed when the cryptographic device is computing. The result will not be outputted once errors are detected. This prevents an attacker from obtaining erroneous result for analysis. More details on fault attacks on public key cryptosystems and countermeasures will be discussed in Chapter 3.

In this dissertation, we consider two of the most powerful side channel attacks, fault attacks and power analysis attacks, and present countermeasures for public key cryptosystems against them.

#### 1.5 Contributions

In this dissertation, we present new countermeasures for two widely used public key cryptosystems, ECC and RSA, to thwart fault attacks. The countermeasures are based on error detection methods. If an error is detected, the cryptosystem will not output the erroneous result and hence prevent an attacker from obtaining it to perform fault analysis. The proposed low-cost error detection and recovery scheme for ECC introduces a new point  $P_v$  into the Montgomery ladder algorithm and updates it in a way such that  $P_v + P_2 \equiv 2P_1$ , where  $P_1$  and  $P_2$ are two point variables used in the Montgomery ladder algorithm.  $P_v + P_2 \equiv 2P_1$  is verified to detect errors. The error detection scheme for RSA exploits the homomorphic property of RSA encryption, i.e.,  $E(m_1 \cdot m_2) \equiv E(m_1) \cdot E(m_2)$ , and checks it to detect errors. Both error detection schemes are design from the same idea: constructing an invariant from the mathematical properties of the public key cryptosystems and checking the correctness of the invariant to detect errors. The proposed error detection methods can achieve good error detection capability while significantly reduce the overhead in terms of time and hardware compared to error detection methods based on parallel computing and recomputing. The idea of discovering or constructing an invariant for error detection should work for other mathematically structured cryptographic cryptosystems besides ECC and RSA. We hope it can provide some guidance for designing the error detection methods for other cryptosystems.

We also discuss the basic principles to construct a comprehensive scheme to thwart multiple side channel attacks. A comprehensive scheme is critical in the security of public key cryptosystems since an attacker can choose any side channel attack in practice and he/she needs to succeed in only one attack to break the public key cryptosystems. Most existing countermeasures target at preventing a single type of side channel attacks. The countermeasures proposed to thwart more than one type of side channel attacks customize the computations, which makes them inflexible to be extended when new side channel attacks appear. Careless modification can cause new leakage compromising the expected security, as shown by Kim and Quisquater (14). Designing a new scheme from scratch whenever resistance to new side channel attacks has to be included is unrealistic. We present an approach to construct a comprehensive scheme from a rich variety of single-purpose countermeasures against different side channel attacks at any time. We show a scheme for RSA constructed with the proposed approach and propose techniques at the Register Transfer Level to improve the performance and the resistant to power analysis attacks.

The rest of the dissertation is organized as follows. In Chapter 2, we introduce the mathematical background, basic definitions and algorithms for the public key cryptosystems, ECC and RSA. In Chapter 3, we focus on two of the most powerful side channel attacks, fault attacks and power analysis attacks on ECC and RSA. The related work on countermeasures against them is introduced. We present a low-cost error detection and recovery scheme (LOEDAR) for ECC to thwart fault attacks in Chapter 4. It can be easily extended to thwart power analysis attacks. In Chapter 5, we propose a concurrent error detection scheme for RSA to thwart fault attacks, which can work with any fine-tuned RSA architecture resistant to other side channel attacks. To protect the public key cryptosystems against multiple types of side channel attacks, we discuss the basic principles to construct a comprehensive scheme using single-purpose countermeasures and present one such scheme for RSA in Chapter 6. Chapter 7 concludes the dissertation.

## CHAPTER 2

#### PRELIMINARIES

Public key cryptographic algorithms operate over finite fields. These algebraic structures are the mathematical basis to understand public key cryptographic algorithms. They define the arithmetic operations in public key cryptographic algorithms. This chapter gives a brief overview of the finite fields, and introduces elliptic curves and operations on the elliptic curves. Then the algorithms to compute ECSM for ECC and modular exponentiation for RSA are introduced.

### 2.1 Finite Fields

A field is a set  $\mathbb{F}$  with two operations, usually called addition (+) and multiplication (·), respectively, for which the following conditions are satisfied:

- Closure: If  $a, b \in \mathbb{F}$ , then  $a + b \in \mathbb{F}$  and  $a \cdot b \in \mathbb{F}$ .

- Associativity: a + (b + c) = (a + b) + c and  $a \cdot (b \cdot c) = (a \cdot b) \cdot c$  for all  $a, b, c \in \mathbb{F}$ .

- Commutativity: a + b = b + a and  $a \cdot b = b \cdot a$  for all  $a, b \in \mathbb{F}$ .

- Additive identity and multiplicative identity: There exists an element, denoted by 0, 0 ∈ F such that for all a ∈ F, 0 + a = a + 0 = a. There also exists an element, denoted by 1, 1 ∈ F such that for all a ∈ F, 1 ⋅ a = a ⋅ 1 = a.

- Additive inverse and multiplicative inverse: For any  $a \in \mathbb{F}$ , there exists  $-a \in F$  such that a + (-a) = 0. For any  $a \in \mathbb{F}$  and  $a \neq 0$ , there exist  $b \in \mathbb{F}$  such that  $a \cdot b = b \cdot a = 1$ .

• Distributivity:  $a \cdot (b+c) = a \cdot b + a \cdot c$  and  $(b+c) \cdot a = b \cdot a + c \cdot a$  for all  $a, b, c \in \mathbb{F}$ .

According to the above definition of field, the set of all real numbers is a field, denoted by  $\mathbb{R}$ , and the set of all rational numbers is also a field, denoted by  $\mathbb{Q}$ . There are infinite elements in  $\mathbb{R}$  and  $\mathbb{Q}$ . A field containing a finite number of elements is called finite field or Galois field. The order of finite field, i.e., the number of elements in the field, is equal to  $p^m$  for some prime p and positive integer m. p is called the characteristic of the field. Hence, the finite field can be denoted by  $\mathbb{F}_{p^m}$ . When m = 1, the finite field is called prime field and denoted by  $\mathbb{F}_p$ . When p = 2, the field is known as binary extension finite field or simply binary finite field, denoted by  $\mathbb{F}_{2^m}$ . Prime field and binary finite field play an important role in public key cryptography.

### 2.1.1 Prime Field

Given a positive integer n, an integer i can be expressed as i = qn + r for some integer r,  $0 \le r \le n - 1$ , and some integer q. r, namely the remainder, is i modulo n, i.e.,  $r = i \mod n$ . For prime p, the set of mod-p remainders contains p integers,  $R_p = \{0, 1, \dots, p - 1\}$ . The remainder set  $R_p$  forms a prime field  $\mathbb{F}_p$  under mod-p addition and mod-p multiplication. The mod-p addition and mod-p multiplication are addition and multiplication performed modulo p. The prime field  $\mathbb{F}_p$  has a prime p number of elements.

#### 2.1.2 Binary Finite Field

Binary finite field  $\mathbb{F}_{2^m}$  can be constructed with polynomials. A polynomial in X over the field  $\mathbb{F}$  is an expression of the form

$$a(X) = a_n X^n + a_{n-1} X^{n-1} + \dots + a_1 X + a_0$$

where  $a_n, a_{n-1}, \dots, a_1, a_0 \in \mathbb{F}$  and n is a positive integer.  $a_n, a_{n-1}, \dots, a_1, a_0$  are the coefficients of the polynomial. The largest i for which  $a_i$  is nonzero is called the degree of the polynomial. A polynomial a(X) is said to be irreducible if  $degree(a(X)) \ge 1$  and a(X) is divisible only by polynomials of degree 0 or  $c \cdot a(X)$  for some  $c \in \mathbb{F}$ .

The set of all polynomials over the field  $\mathbb{F}$  in X is denoted by  $\mathbb{F}[X]$ . The field  $\mathbb{F}_{p^m}$ , when  $m \neq 1$ , can be obtained by taking  $\mathbb{F}_p[X]$ , the set of all polynomials with coefficients over the prime field  $\mathbb{F}_p$ , modulo an irreducible polynomial of degree m. Hence, the binary finite field  $\mathbb{F}_{2^m}$  can be constructed by taking  $\mathbb{F}_2[X]$  modulo an irreducible polynomial of degree m. Hence, the binary finite field  $\mathbb{F}_{2^m}$  can be constructed by taking  $\mathbb{F}_2[X]$  modulo an irreducible polynomial of degree m. Hence, the elements in  $\mathbb{F}_{2^m}$  are the polynomials of degree at most m-1 and coefficients of the polynomials are in the field  $\mathbb{F}_2 = \{0, 1\}$ . For example, the binary finite field  $\mathbb{F}_{2^4}$  contains 16 polynomials: 0, 1,  $X, X + 1, X^2, X^2 + 1, X^2 + X, X^2 + X + 1, X^3, X^3 + 1, X^3 + X, X^3 + X + 1, X^3 + X^2, X^3 + X^2 + 1, X^3 + X^2 + X + 1, X^3, X^3 + 1, X^3 + X, X^3 + X + 1, X^3 + X^2, X^3 + X^2 + 1, X^3 + X^2 + X + 1$ . Arithmetic operations over  $\mathbb{F}_{2^4}$  are performed using an irreducible polynomial as the reduction polynomial, e.g.,  $f(X) = X^4 + X + 1$ . The following are examples of addition and multiplication. Suppose  $g(X) = X^3 + X + 1$  and  $h(X) = X^2 + 1$ .

Addition :

$$g(X) + h(X) = (X^3 + X + 1) + (X^2 + 1)$$

=  $X^3 + X^2 + X$

Multiplication :

$$g(X) \cdot h(X) = (X^3 + X + 1) \cdot (X^2 + 1)$$

=  $X^5 + X^2 + X + 1 \mod (X^4 + X + 1)$

= 1

A binary finite field  $\mathbb{F}_{2^m}$  can also be viewed as a vector space of dimension m over  $\mathbb{F}_2$ . And the elements in the field can be represented in bases such as polynomial bases and normal bases.

Let  $\alpha$  be an element of  $\mathbb{F}_{2^m}$  such that  $\alpha$  is a root of an irreducible polynomial f(X) of degree m over  $\mathbb{F}_2$ , the element  $\alpha \in \mathbb{F}_{2^m}$  generates

$$\{1, \alpha, \alpha^2, \cdots, \alpha^{m-1}\}$$

which is called a polynomial basis of  $\mathbb{F}_{2^m}$  over  $\mathbb{F}_2$ . Any element in the field can be represented in terms of the basis as  $a(X) = a_{m-1}\alpha^{m-1} + \cdots + a_1\alpha + a_0$ . In computer systems, the element can be represented by the vector formed by the coefficients. For example,  $X^3 + X^2 + 1$  in the field  $\mathbb{F}_{2^4}$  is represented as (1101)<sub>2</sub>.

A normal basis of  $\mathbb{F}_{2^m}$  over  $\mathbb{F}_2$  is a basis of the form

$$\{\alpha, \alpha^2, \alpha^{2^2}, \cdots, \alpha^{2^{m-1}}\}$$

for an element  $\alpha \in \mathbb{F}_{2^m}$ . One advantage of normal bases is that raising an element to the power of 2 is simply a cyclic shift of the element vector.

## 2.2 Elliptic Curves

An elliptic curve E over a field  $\mathbb{F}$  is defined by a Weierstrass equation:

$$E: y^{2} + a_{1}xy + a_{3}y = x^{3} + a_{2}x^{2} + a_{4}x + a_{6}$$

(2.1)

where  $a_1, a_2, a_3, a_4, a_6 \in \mathbb{F}$  and the discriminant of E is nonzero. The discriminant of E is defined as follows:

$$\Delta = -d_2^2 d_8 - 8d_4^3 - 27d_6^2 + 9d_2 d_4 d_6$$

$$d_2 = a_1^2 + 4a_2$$

$$d_4 = 2a_4 + a_1 a_3$$

$$d_6 = a_3^2 + 4a_6$$

$$d_8 = a_1^2 a_6 + 4a_2 a_6 - a_1 a_3 a_4 + a_2 a_3^2 - a_4^2.$$

(2.2)

For cryptographic applications, elliptic curves are defined over finite fields. In the binary finite field  $\mathbb{F}_{2^m}$ , i.e., the characteristic is 2, Equation 2.1 can be transformed to

$$E: y^2 + xy = x^3 + ax^2 + b \tag{2.3}$$

where  $a, b \in \mathbb{F}$  and  $b \neq 0$ . The set of points  $(x, y) \in \mathbb{F}_{2^m} \times \mathbb{F}_{2^m}$  satisfying Equation 2.3 along with the point at infinity  $\mathcal{O}$  forms a group under addition. The point at infinity  $\mathcal{O}$  serves as the identity of the group, i.e.,  $P + \mathcal{O} = \mathcal{O} + P = P$  for all P on E. For any two points  $P_1$  and  $P_2$  on E,  $P_1 \neq \mathcal{O}$ ,  $P_2 \neq \mathcal{O}$ , they can be written as  $P_1 = (x_1, y_1)$  and  $P_2 = (x_2, y_2)$ .

If  $P_2 \neq \pm P_1$ , then  $P_1 + P_2 = (x_3, y_3)$ , where

$$\begin{cases} x_3 = \left(\frac{y_1 + y_2}{x_1 + x_2}\right)^2 + \frac{y_1 + y_2}{x_1 + x_2} + x_1 + x_2 + a, \\ y_3 = \left(\frac{y_1 + y_2}{x_1 + x_2}\right)(x_1 + x_3) + x_3 + y_1 \end{cases}$$

(2.4)

The operation is known as point addition.

- If  $P_2 = -P_1$ , then  $P_1 + P_2 = O$ .

- If  $P_2 = P_1$ , then  $P_1 + P_2 = 2P_1 = (x_3, y_3)$ , where

$$\begin{cases} x_3 = x_1^2 + \frac{b}{x_1^2}, \\ y_3 = x_1^2 + \left(x_1 + \frac{y_1}{x_1}\right)x_3 + x_3 \end{cases}$$

(2.5)

The operation is referred to as point doubling.

If the characteristic of the finite field  $\mathbb{F}$  is not equal to 2 or 3, the Weierstrass equation can be transformed to

$$E: y^2 = x^3 + ax + b. (2.6)$$

Let  $P_1 = (x_1, y_1)$  and  $P_2 = (x_2, y_2)$ ,  $P_1 \neq \mathcal{O}$ ,  $P_2 \neq \mathcal{O}$ ,  $P_1 \neq \pm P_2$ , point addition  $P_1 + P_2 = (x_3, y_3)$  is computed as

$$\begin{cases} x_3 = \lambda^2 - x_1 - x_2, \\ y_3 = \lambda(x_1 - x_3) - y_1 \end{cases}$$

(2.7)

where  $\lambda = (y_2 - y_1)/(x_2 - x_1)$ .

Point doubling  $2P_1 = (x_3, y_3)$  is computed as

$$\begin{cases} x_3 = \lambda^2 - 2x_1, \\ y_3 = \lambda(x_1 - x_3) - y_1 \end{cases}$$

(2.8)

where  $\lambda = (3x_1^2 + a)/(2y_1)$ .

Point addition and point doubling consist of arithmetic operations over a finite field such as addition, multiplication, squaring operation and inversion. Inversion over binary finite field or prime field is more expensive than other arithmetic operations. To avoid expensive inversions, affine coordinates can be transformed into projective coordinates. The projective form of the Weierstrass equation of an elliptic curve E can be obtained by replacing x by  $X/Z^c$  and y by  $Y/Z^d$  where  $c, d \in \mathbb{N}$ .

In homogeneous projective coordinates, coordinates are transformed by setting x = X/Zand y = Y/Z. The equation of elliptic curve over binary finite fields, i.e., Equation 2.3, is transformed to

$$Y^{2}Z + XYZ = X^{3} + aX^{2}Z + bZ^{3}.$$

(2.9)

An affine point (x, y) is represented by a projective point  $(X, Y, Z) = (\theta x, \theta y, \theta)$  for some  $\theta \in \mathbb{F}$ . The X, Y-coordinate and Z-coordinate can be computed separately for point addition and point doubling. Affine coordinates can be mapped to projective coordinates in other ways. In the Jacobian projective coordinate, an affine point (x, y) is mapped to a projective point (X, Y, Z) = $(\theta^2 x, \theta^3 y, \theta)$  for some  $\theta \in \mathbb{F}$  by setting  $x = X/Z^2$  and  $y = Y/Z^3$ . In the Lopez Dahab projective coordinate (15), an affine point (x, y) is mapped to a projective point  $(X, Y, Z) = (\theta x, \theta^2 y, \theta)$ for some  $\theta \in \mathbb{F}$  by setting x = X/Z and  $y = Y/Z^2$ .

## 2.3 Elliptic Curve Scalar Multiplication

In this section, we introduce the methods to compute ECSM, i.e., kP where k is an integer and P is a point on the elliptic curve E. The ECSM operation dominates the computation in ECC schemes.

## 2.3.1 Basic Algorithms

The basic algorithms to compute ECSM are binary method and add-and-double-always method. Algorithm 1 shows the left-to-right binary method. The algorithm computes from the second Most Significant Bit (MSB) towards the Least Significant Bit (LSB) of k. It doubles point R for each bit of k and adds P to R only when the bit of k is 1. Therefore, the sequence of operations is dependent on the value of k.

The add-and-double-always method inserts a dummy point addition to make the sequence of operations independent on the value of k, as shown in Algorithm 2.

## 2.3.2 Montgomery Ladder Algorithm

Montgomery introduced a different method to compute kP (16). He observed that the xcoordinate of the addition of two points can be computed from the x-coordinates of the two points and the x-coordinate of the difference between them. The algorithm computes with two

Algorithm 1 Left-to-right binary method

Input:  $P \in E$ ,  $k = (k_{l-1}k_{l-2}\cdots k_0)_2$  where  $k_{l-1} = 1$ Output: Q = kP $R \leftarrow P$ for i = l - 2 downto 0 do  $R \leftarrow 2R$ if  $k_i = 1$  then  $R \leftarrow R + P$ end if end for Return (R)

Algorithm 2 Add-and-double-always method

Input:  $P \in E$ ,  $k = (k_{l-1}k_{l-2}\cdots k_0)_2$  where  $k_{l-1} = 1$ Output: Q = kP  $R[0] \leftarrow P$ for i = l - 2 downto 0 do  $R[0] \leftarrow 2R[0]$   $R[1] \leftarrow R[0] + P$   $R[0] \leftarrow R[k_i]$ end for Return (R[0])

points,  $P_1$  and  $P_2$ , whose difference is always P after each iteration. In each iteration, one point addition and one point doubling are performed independent on the value of k. Algorithm 3 shows the method.

|  | Algorithm | 3 | Montgomery | y ladder | algorithm |

|--|-----------|---|------------|----------|-----------|

|--|-----------|---|------------|----------|-----------|

Input:  $P \in E$ ,  $k = (k_{l-1}k_{l-2}\cdots k_0)_2$  where  $k_{l-1} = 1$ Output: Q = kPSet  $P_1 \leftarrow P$ ,  $P_2 \leftarrow 2P$ for i = l - 2 downto 0 do if  $k_i = 1$  then  $P_1 \leftarrow P_1 + P_2$   $P_2 \leftarrow 2P_2$ else  $P_2 \leftarrow P_2 + P_1$   $P_1 \leftarrow 2P_1$ end if end for Return  $(Q = P_1)$

#### 2.3.3 Fast ECSM over $\mathbb{F}_{2^m}$

Lopez and Dahab presented an efficient implementation of the Montgomery ladder algorithm for computing kP on elliptic curves over  $\mathbb{F}_{2^m}$  (17). They showed that given  $P_1 = (x_1, y_1)$ ,  $P_2 = (x_2, y_2)$  and  $P = P_2 - P_1 = (x, y)$ , the x-coordinate of  $P_1 + P_2$  can be computed as follows.

$$x(P_1 + P_2) = x + \left(\frac{x_1}{x_1 + x_2}\right)^2 + \frac{x_1}{x_1 + x_2}$$

(2.10)

The x-coordinate of the doubling of a point  $P_1$  can also be computed from the x-coordinate of  $P_1$ , as shown in Equation 2.5. Therefore, only the x-coordinates of  $P_1$ ,  $P_2$  and P can be used to perform arithmetic operations needed in the (l-1) iterations in Algorithm 3. At the end of the (l-1)th iteration, the x-coordinates of kP and (k+1)P are obtained. The y-coordinate of kP can be recovered as follows.

$$y_1 = (x_1 + x)\{(x_1 + x)(x_2 + x) + x^2 + y\}/x + y$$

(2.11)

where  $x_1, x_2$  are the x-coordinates of  $P_1$  and  $P_2$  after the (l-1)th iteration.

To avoid expensive inversions over  $\mathbb{F}_{2^m}$ , the affine coordinates of  $P_1$  and  $P_2$  can be transformed to projective coordinates by setting x = X/Z and y = Y/Z. Hence, the x-coordinates of  $P_1$  and  $P_2$ , i.e.,  $x_1$  and  $x_2$ , are represented by  $X_1/Z_1$  and  $X_2/Z_2$ .

The x-coordinate of  $P_1 + P_2$  can be computed as  $X(P_1 + P_2)/Z(P_1 + P_2)$  where

$$\begin{cases} Z(P_1 + P_2) = Z_3 = (X_1 \cdot Z_2 + X_2 \cdot Z_1)^2 \\ X(P_1 + P_2) = X_3 = x \cdot Z_3 + (X_1 \cdot Z_2) \cdot (X_2 \cdot Z_1) \end{cases}$$

(2.12)

where x is the affine x-coordinate of  $P = P_2 - P_1$ .

The x-coordinate of  $2P_1$  can be computed as  $X(2P_1)/Z(2P_1)$  where

$$\begin{cases} X(2P_1) = X_4 = X_1^4 + b \cdot Z_1^4 \\ Z(2P_1) = Z_4 = X_1^2 \cdot Z_1^2 \end{cases}$$

(2.13)

## 2.4 Modular Exponentiation

RSA is based on modular exponentiation. Given a message m and an exponent d, modular exponentiation computes  $m^d \mod N$  where N is the modulus.

# 2.4.1 Algorithms

A basic method for computing modular exponentiation is the binary exponentiation algorithm, also known as the square-and-multiply algorithm. Algorithm 4 shows the left-to-right version which starts at the second MSB of the exponent and works downward. Each bit of exponent is processed with a modular square operation and a conditional modular multiplication. The right-to-left binary exponentiation algorithm is similar to the left-to-right one except that it starts at the LSB and works upward.

# Algorithm 4 Binary exponentiation algorithm

Input:  $m, d = (d_{l-1} \cdots d_1 d_0)_2$  where  $d_{l-1} = 1, N$ Output:  $m^d \mod N$   $R \leftarrow m$ for i = l - 2 downto 0 do  $R \leftarrow R^2 \mod N$ if  $d_i = 1$  then  $R \leftarrow R \cdot m \mod N$ end if end for Return (R) In the binary exponentiation algorithm, the sequence of operations is dependent on the value of d since the modular multiplication is performed only when the bit of d is 1. The squareand-multiply-always algorithm inserts a dummy operation to make the sequence of operations independent on d, as shown in Algorithm 5.

| Algorithm 5 Square-and-multiply-always algorithm                          |

|---------------------------------------------------------------------------|

| <b>Input</b> : $m, d = (d_{l-1} \cdots d_1 d_0)_2$ where $d_{l-1} = 1, N$ |

| $\mathbf{Output}: \ m^d \bmod N$                                          |

| $R[0] \leftarrow m$                                                       |

| for $i = l - 2$ downto 0 do                                               |

| $R[0] \leftarrow R[0]^2 \mod N$                                           |

| $R[1] \leftarrow R[0] \cdot m$                                            |

| $R[0] \leftarrow R[d_i]$                                                  |

| end for                                                                   |

| Return $(R[0])$                                                           |

The Montgomery ladder exponentiation algorithm also ensures the sequence of operations independent on the value of d. As shown in Algorithm 6, it starts at the second MSB of the exponent and processes bit by bit down to the LSB. A modular multiplication and a modular squaring operation are performed in each iteration. R[1] and R[0] satisfy the relation  $R[1] = R[0] \cdot m \mod N$  after each iteration. At the end of the *l*th iteration,  $R[0] = m^d \mod N$ and  $R[1] = m^{d+1} \mod N$  are obtained. There is no dummy operations in the algorithm.

Algorithm 6 Montgomery ladder exponentiation algorithm

Input:  $m, d = (d_{l-1} \cdots d_1 d_0)_2, N$ Output:  $m^d \mod N$   $R[0] \leftarrow 1, R[1] \leftarrow m$ for i = l - 1 to 0 do  $R[\overline{d_i}] \leftarrow R[\overline{d_i}] \cdot R[d_i] \mod N$   $R[d_i] \leftarrow R[d_i] \cdot R[d_i] \mod N$ end for Return (R[0])

# 2.4.2 Computing RSA Fast with Chinese Remainder Theorem

Modular exponentiation in RSA is time-consuming due to the lengths of exponent and modulus. Chinese Remainder Theorem can be used to accelerate computation of the modular exponentiation with the private key in RSA, known as CRT-RSA. Algorithm 7 shows CRT-RSA where  $I_q = q^{-1} \mod p$ ,  $I_p = p^{-1} \mod q$ .

# Algorithm 7 CRT-RSA

**Input**: m, d, p and q where  $p \cdot q = N$  **Output**:  $m^d \mod N$   $d_p \leftarrow d \mod (p-1), d_q \leftarrow d \mod (q-1)$   $s_p \leftarrow m_{d_p} \mod p$   $s_q \leftarrow m_{d_q} \mod q$   $s \leftarrow \operatorname{CRT}(s_p, s_q) = ((s_p \cdot q \cdot I_q) + (s_q \cdot p \cdot I_p)) \mod N$ **Return (s)**  Compared to the straightforward implementation of RSA, CRT-RSA computes two modular exponentiations  $m^{d \mod (p-1)} \mod p$  and  $m^{d \mod (q-1)} \mod q$ . Since p and q are chosen to have about half the bit length of N, i.e.,  $|p| \approx |q| \approx |N|/2$ , the exponents in the two modular exponentiations are of half bit length of d. Hence, CRT-RSA is about 4 times faster than the straightforward implementation of RSA. Note that CRT-RSA can be used only in digital signature or decryption since it requires to know the secret information p and q.

# CHAPTER 3

# SIDE CHANNEL ATTACKS AND COUNTERMEASURES FOR PUBLIC KEY CRYPTOSYSTEMS

As introduced in §1.4, side channel attacks exploit the weakness in the implementations of cryptographic algorithms. An attacker can gain information about the internal state of the cryptosystem by monitoring timing, power consumption, electromagnetic emission or erroneous output, and derive the secret key by analyzing the information. Based on the source of leakage, side channel attacks can be divided into timing attacks, power analysis attacks, fault attacks, etc. Fault attacks and power analysis attacks are two of the most powerful ones of all side channel attacks. In this section, we survey fault attacks and power analysis attacks on ECC and RSA and the countermeasures against them.

#### **3.1** Fault Attacks and Countermeasures

Fault attacks are active attacks in which attackers need to disturb the cryptosystem by inducing faults. With erroneous output or the reaction of the cryptosystem under faults, attackers can reveal the secret information. The first fault attack targeted RSA (18) in which a fault was introduced to the computation of one modular exponentiation in CRT-RSA and the secret prime number was derived from the erronous output. Since then, fault attacks have been reported to break other cryptosystems.

#### 3.1.1 Fault Injection and Fault Models

There are many techniques to induce faults. Variations in supply voltage or variations in the external clock may cause data misread, instruction miss or erroneous data. Temperature can lead to misfunctioning of cryptographic device. Circuit manufacturers give the temperature bound for a circuit to function correctly. If the temperature exceeds the bound, operations may not work. And the data stored in memory cells could be modified due to heating. White light can also induce faults due to photoelectric effects. The photons can induce current when a circuit exposed to intense light for a short time period. Laser improves the precision of fault injection. Its directionality allows it to target a small circuit area. X-rays and ion beams can inject faults without depackaging the chip.

The difficulty in inducing a fault depends on the precision in terms of timing and location. Different fault attacks are based on different fault models which require certain control on timing and location. Without any control, a fault is induced randomly. With better control of location, a block of operations can be targeted. Powerful attackers may be able to inject a fault to selected bits with precise control. Attackers may also be able to control the timing of fault injection, however, it is hard to induce a fault at some exact time. Based on the control level of timing, location and the number of bits affected, the most popular fault models used in the literature of fault attacks are single bit fault model, byte fault model, random fault model and arbitrary fault model. The single bit fault model assumes that a fault affects only a single bit of a targeted variable. It is considered unrealistic to target a specific bit of the variable at a specific point of time. Boneh, Demillo and Lipton introduced the single bit fault model which relaxed the control over location and timing in the first fault attack (18). In the model, a variable used in the cryptographic algorithm rather than a specific bit is targeted, and one bit of the affected variable is flipped. The byte fault model represents the attacks where only a bounded number of bits are affected by an induced fault. When cryptographic devices store and load variables in blocks, the block of bits, typically one byte, can be affected by induced faults. In the byte fault model, a specific variable is targeted, and a fault can affect one byte at an unknown position in the variable. The number of affected bits is usually bounded by a small number, which allows an attacker to try all possible error patterns to identify the correct error pattern for secret information recovery. The random fault model assumes that a variable affected by an induced fault is changed to some random value. It models the case that an attacker lacks the knowledge of how an induced fault affects the value of the variable. The resulting random values are usually assumed to be distributed uniformly to simplify analysis. The weakest fault model is the arbitrary fault model. In the model, an attacker has even less control over location. Only a specific line of the code of cryptographic algorithm can be targeted. And the attacker may not know the effect of the faults, e.g., the distribution of error. An attack based on the arbitrary fault model is more dangerous compared to attacks based on other fault models since it requires less about the capability of an attacker.

#### 3.1.2 Fault Attacks on ECC and RSA

Fault attacks on ECC can be divided into three categories: weak curve based fault attacks, differential fault attacks and safe error attacks. Weak curve based attacks try to move the computation of ECSM from a strong elliptic curve to a weak elliptic curve. Biehl, Meyer and Muller presented a weak curve based fault attack (19). They observed that parameter  $a_6$  in the Weierstrass equation (Equation 2.1) was not used in computation of ECSM. An attacker can cheat the cryptosystem with a point  $P' \in E'$ where E' is a cryptographically weak elliptic curve.

$$E': y^2 + a_1 xy + a_3 y = x^3 + a_2 x^2 + a_4 x + a_6'$$

(3.1)