# A study of using STT-MRAM as Memory PUF: Design, Modeling and Quality Evaluation

BY

# PAOLO VINELLA

B.S., Politecnico di Torino, Turin, Italy, 2012

## THESIS

Submitted as partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2015

Chicago, Illinois

Defense Committee:

Wenjing Rao, Chair and Advisor Zhichun Zhu Fabrizio Bonani, Politecnico di Torino

Dedicated to my Parents,

who have always provided me with the best and unconditional moral and economical support, enabling me to achieve results I am proud of and accomplish my goals at School as well as in life. I will hardly be thankful enough for what you have done.

## ACKNOWLEDGMENTS

My most truthful gratitude goes to the Academic Committee, including Staff and Faculty, at both University of Illinois at Chicago and Politecnico di Torino, for providing me with the great opportunity of being part of the joint program TOP-UIC for my Master Degree. An ambitious and challenging path that has enriched me on both cultural and academic levels.

I am grateful to Prof. Rao, my Thesis Advisor at UIC, for accepting me into her Research Group and assisting me through the entire thesis work, and for deeply believing in my potential, offering me both a Teaching Assistantship and a Research Assistantship at UIC. An additional experience that I have more than welcomed and has surely had a huge impact on further enriching and amplifying my skills.

A special thanks to Prof. Bonani, not only Thesis Advisor representing Politecnico di Torino, but also twice my Professor of two among my past Academic courses, held both in Italy and in China.

A particular mention goes also to Soroush Khaleghi, who offered me his precious consulting in part of this thesis work, especially in Section 3.7, while working on his PhD at UIC in the research group of Prof. Rao.

Last, but absolutely not least, my sincere gratitude needs to reach Miss Lynn Thomas as well, Project Coordinator of TOP-UIC for the Chicago side of the Program, and the whole Staff of the ECE Dept. at UIC for supporting me with their care and impeccable professionalism.

$\mathbf{PV}$

# TABLE OF CONTENTS

# **CHAPTER**

# PAGE

| 1        | INTROE  | OUCTION                                                          | 1  |

|----------|---------|------------------------------------------------------------------|----|

| <b>2</b> | BACKG   | ROUND                                                            | 3  |

|          | 2.1     | Computer memories: trend towards non-volatile technology .       | 5  |

|          | 2.1.1   | Digital memories hierarchy general considerations                | 6  |

|          | 2.1.2   | Future memory trends: the "dream memory"                         | 7  |

|          | 2.1.3   | MRAM as non-volatile universal memory candidate                  | 9  |

|          | 2.2     | MTJ as Magnetic Memory using Magnetoresistance: MRAM             | 12 |

|          | 2.2.1   | Using electromagnetism to store digital information: main idea   | 12 |

|          | 2.2.2   | Magnetoresistance effect and Spin-Torque transfer                | 12 |

|          | 2.2.3   | STT-MRAM: spintronic meets "second generation" magnetic          |    |

|          |         | memory                                                           | 14 |

|          | 2.2.4   | STT-MRAM digital memory cell                                     | 16 |

|          | 2.2.5   | Main applications: consolidated work and novel trends $\ldots$ . | 18 |

|          | 2.3     | STT-MRAM electrical models and characterizations                 | 24 |

|          | 2.4     | Hardware Security and the role of PUF                            | 30 |

|          | 2.4.1   | The need of identifying chips                                    | 32 |

|          | 2.4.2   | PUF: Physically Unclonable Functions                             | 33 |

|          | 2.4.3   | An analog example of PUF                                         | 36 |

|          | 2.4.4   | Typical digital PUFs: Ring Oscillator and SRAM                   | 37 |

|          | 2.4.5   | Introduction on evaluating the quality of a PUF $\ldots$ .       | 38 |

|          | 2.5     | STT-MRAM as PUF: introduction and current work $\ldots$ .        | 40 |

|          | 2.5.1   | MRAM resistance dispersion as PUF                                | 40 |

|          | 2.5.2   | Current work proposed schemes: comparison and tradeoffs          | 43 |

|          | 2.5.2.1 | STT-MRAM as PUF from the nano electronic standpoint              | 49 |

| 3        | MY WO   | <b>RK</b>                                                        | 50 |

|          | 3.1     | Main motivations                                                 | 50 |

|          | 3.2     | Initial analysis on the static electrical model of STT-MRAM .    | 52 |

|          | 3.2.1   | Statistical study of a population of STT-MRAM MTJ memory         |    |

|          |         | cells                                                            | 52 |

|          | 3.2.2   | MTJ population performance evaluation                            | 54 |

|          | 3.2.3   | Effect of the variation of the MTJ oxide thickness over the      |    |

|          |         | population                                                       | 60 |

|          | 3.3     | Improving the usage of STT-MRAM as PUF                           | 66 |

|          | 3.4     | Design schemes variations                                        | 69 |

|          | 3.5     | Simulations details and metrics: evaluating the quality of a PUF | 73 |

# TABLE OF CONTENTS (Continued)

# **CHAPTER**

$\mathbf{4}$

# PAGE

| 3.5.1   | Uniqueness evaluation metrics                                                                                                     | 75  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.5.2   | Reliability – BER evaluation metrics                                                                                              | 77  |

| 3.6     | PUF Quality simulations results and critical analysis                                                                             | 79  |

| 3.6.1   | PUF Uniqueness study for all design schemes                                                                                       | 80  |

| 3.6.1.1 | Case 1 study                                                                                                                      | 80  |

| 3.6.1.2 | $Case 2 study \ldots \ldots$    | 81  |

| 3.6.1.3 | $Case 3 study \ldots \ldots$                                                                                                      | 83  |

| 3.6.1.4 | $Case 4 study \ldots \ldots$    | 85  |

| 3.6.1.5 | Comparative study among Cases                                                                                                     | 86  |

| 3.6.2   | PUF Reliability (BER) study for all design schemes (Cases 1,                                                                      |     |

|         | $2, 3, 4) \ldots \ldots$ | 87  |

| 3.6.2.1 | Case 1 study                                                                                                                      | 88  |

| 3.6.2.2 | $Case 2 study \ldots \ldots$    | 89  |

| 3.6.2.3 | Case 3 study                                                                                                                      | 90  |

| 3.6.2.4 | $Case 4 study \ldots \ldots$    | 91  |

| 3.6.2.5 | Comparative study among Cases                                                                                                     | 92  |

| 3.6.2.6 | Influence of variation of the reading voltage over BER                                                                            | 93  |

| 3.6.2.7 | Influence of reading voltage over the MTJs' resistance                                                                            | 95  |

| 3.7     | Improving PUF Signature unclonability against software sim-                                                                       |     |

|         | ulations                                                                                                                          | 97  |

| 3.7.1   | Strong vs Weak PUF: from Chip Signature to challenge-response                                                                     |     |

|         | pairs                                                                                                                             | 100 |

| 3.7.2   | Augmenting STT-MRAM PUF as Strong PUF                                                                                             | 102 |

| 3.7.3   | Memory layout assumptions                                                                                                         | 103 |

| 3.7.4   | Mathematical formulation of the challenges space                                                                                  | 104 |

| 3.7.5   | Mathematical formulation of the response space                                                                                    | 112 |

| 3.7.6   | Complexity for the attacker to defeat the Strong PUF                                                                              | 114 |

| 3.7.7   | A basic high-level digital approach to implement the switches                                                                     | 116 |

| CONCI   | LUSIONS                                                                                                                           | 119 |

| 4.1     | Final conclusions and remarks                                                                                                     | 119 |

| 4.2     | Future Work                                                                                                                       | 121 |

| APPEN   | NDICES                                                                                                                            | 123 |

|         | pendix A                                                                                                                          | 124 |

|         | pendix B                                                                                                                          | 125 |

| 1106    |                                                                                                                                   | 120 |

| CITED   | LITERATURE                                                                                                                        | 136 |

| VITA .  |                                                                                                                                   | 140 |

|         |                                                                                                                                   |     |

# LIST OF TABLES

| TABLE |                                                                                                                        | PAGE |

|-------|------------------------------------------------------------------------------------------------------------------------|------|

| Ι     | MTJ AS STT-MRAM: PARAMETERS AND VARIABLES                                                                              | 28   |

| Π     | STT-MRAM: MTJ STACK MAIN PARAMETERS OF RESIS-<br>TANCE STATISTICAL DISTRIBUTION IN PARALLEL AND<br>ANTIPARALLEL STATES | 42   |

| III   | PUF GENERATION: COMPARISON OF CASE 1 AND CASE 2.                                                                       | 47   |

| IV    | A COMPARISON OF THE EFFECTIVE MEMORY SIZE NEEDED<br>TO REALIZE A PUF SIGNATURE OF A GIVEN SIZE, CASE<br>BY CASE        | 72   |

| V     | PUF UNIQUENESS EVALUATION: A COMPARATIVE STUDY<br>AMONG CASE 1, 2, 3 AND 4                                             | 86   |

| VI    | BER COMPARISON WHEN THE APPLIED READING VOLT-AGE VARIES                                                                | 94   |

| VII   | REASONING ON POSSIBLE GROUPINGS OF THE AVAIL-<br>ABLE MEMORY CELLS                                                     | 106  |

| VIII  | REASONING ON POSSIBLE GROUPINGS OF THE AVAIL-<br>ABLE MEMORY CELLS WITH MORE RESTRICTIONS ON<br>THE GROUPING RULES     | 108  |

| IX    | CONSIDERING MORE SENSE AMPLIFIERS FOR EACH WORD                                                                        | 110  |

# LIST OF FIGURES

| <b>FIGURE</b> | Ī                                                                                                                                                                                                                                                                                                   | PAGE |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1             | Main digital memories: Capacity vs Access Time. In red, magnetic memories                                                                                                                                                                                                                           | 10   |

| 2             | Magnetic tunneling junction: basic structure, P and AP states from<br>the analog (resistor) and digital (bit value) perspective                                                                                                                                                                     | 14   |

| 3             | STT-MRAM basic digital memory cell, constituted of an MTJ stack<br>on top of an access MOS transistor. In (a) the electrical scheme, in<br>(b) the simplified physical layout and in (c) the dependance of the<br>parallel and antiparallel resistance on the voltage drop insisting on<br>the MTJ. | 17   |

| 4             | STT-MRAM memory array: WL is the word line employed to activate a given row, then read and write operations happen exploiting the BL (bit line) and SL (source line), which provide access to the MTJ. In this particular example a '0 1 1' binary string has to be written.                        | 18   |

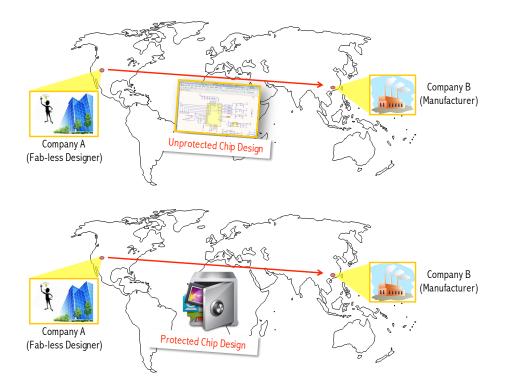

| 5             | During chip manufacturing, unprotected (top) chip design may lead<br>to design thefts. Design protection is then becoming a must (bottom).                                                                                                                                                          | 31   |

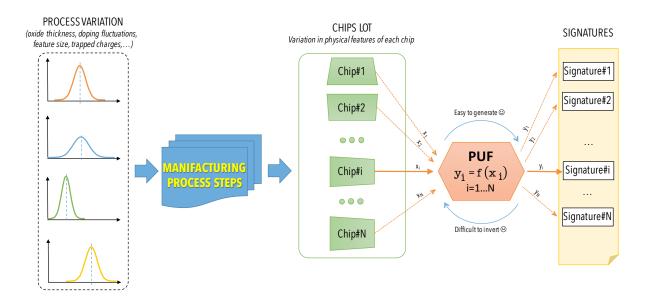

| 6             | From chips manufacturing to unique signature: PUF generation $\ .$ .                                                                                                                                                                                                                                | 35   |

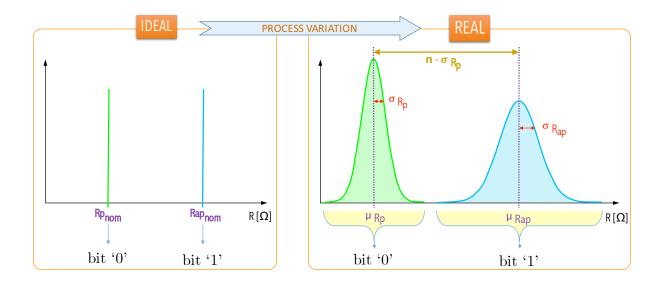

| 7             | P and AP states have a low- and high-state resistance. In reality process variation leads to a spread of them both.                                                                                                                                                                                 | 41   |

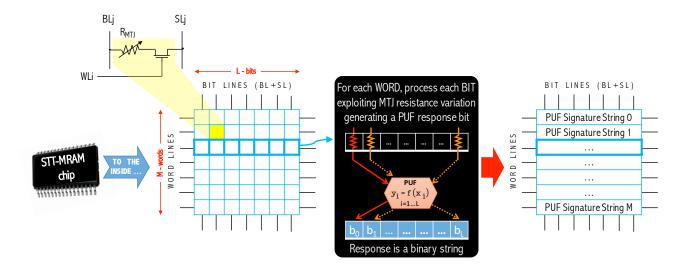

| 8             | Generating a PUF signature from a STT-MRAM memory chip $\ . \ .$                                                                                                                                                                                                                                    | 44   |

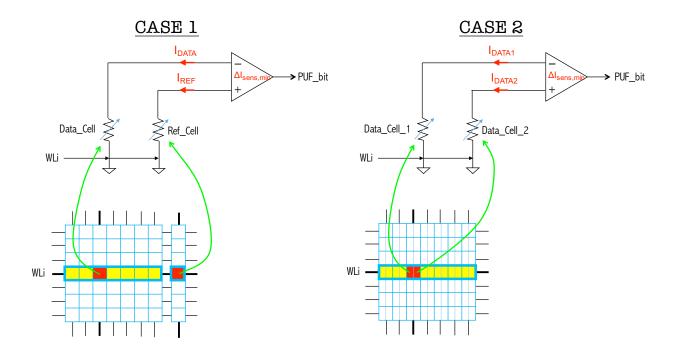

| 9             | A representation of the methodology used in the two papers consti-<br>tuting the current work in order to generate a signature using the<br>PUF method on a chip of STT-MRAM                                                                                                                        | 45   |

| 10            | STT-MRAM generated population: first statistical parameters over<br>the MTJ stacks' resistance dispersion                                                                                                                                                                                           | 55   |

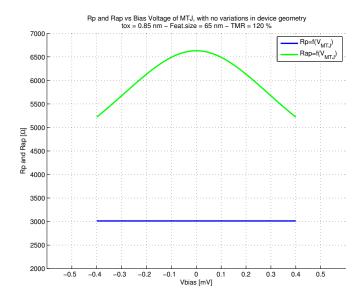

| 11            | Dependence of $R_p$ and $R_{ap}$ on $V_{MTJ}$ applied to a memory cell $\ldots$                                                                                                                                                                                                                     | 56   |

# LIST OF FIGURES (Continued)

# **FIGURE**

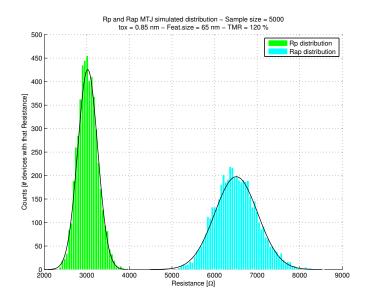

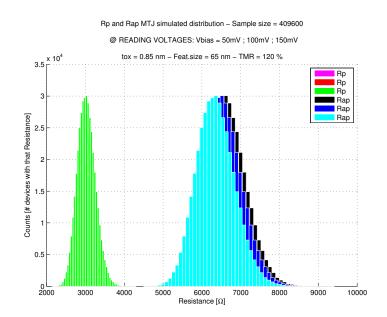

| 12 | Distribution of the simulated sample set of MTJ elements: $R_p$ and $R_{ap}$ distribute normally given normally distributed physical parameters and applied voltage                                                                                          | 57 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

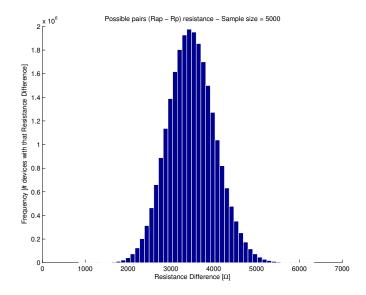

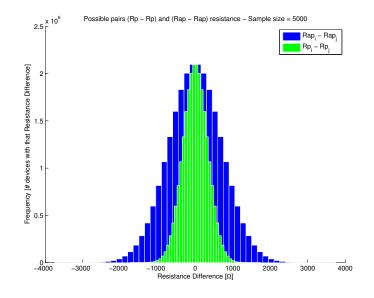

| 13 | Possible pairs of $(R_{ap} - R_p)$ taken as resistance differences                                                                                                                                                                                           | 58 |

| 14 | Possible pairs of $(R_{ap_i} - R_{ap_j})$ and $(R_{p_i} - R_{p_j}) \dots \dots \dots$                                                                                                                                                                        | 59 |

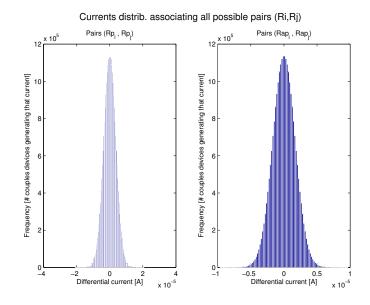

| 15 | Differential currents when $V_{MTJ} = 100mV$ , normally distributed,<br>is applied to the memory cells. The parallel configuration ensures<br>a population of differential currents with an intensity slightly more<br>than doubled with respect to $R_{ap}$ | 60 |

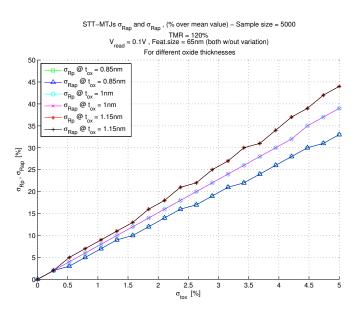

| 16 | $\sigma_{Rp}$ and $\sigma_{Rap}$ variation as function of oxide thickness $t_{ox}$ and its amount of standard deviation. $V_{MTJ}$ and feature size assumed to be constant and not varying at all                                                            | 62 |

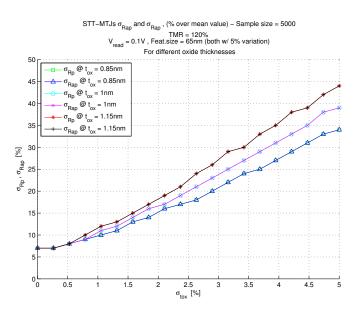

| 17 | $\sigma_{Rp}$ and $\sigma_{Rap}$ variation as function of oxide thickness $t_{ox}$ and its<br>amount of standard deviation. $V_{MTJ}$ and feature size are now nor-<br>mally distributed as well, thus both affected by a standard deviation<br>(kept to 5%) | 63 |

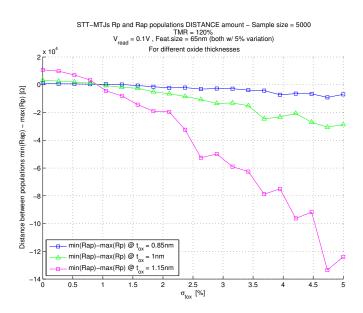

| 18 | Distance between populations of parallel and antiparallel states func-<br>tion of the standard deviation of oxide thickness, for three different<br>values of $t_{ox}$ ; $\sigma_{V_{MTJ}}$ and $\sigma_{A,B} = 5\%$ .                                       | 64 |

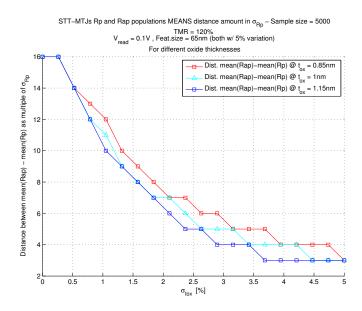

| 19 | Distance between the mean values of the populations of parallel and antiparallel states expressed as multiple of $\sigma_{Rp}$ , as function of the oxide thickness.                                                                                         | 65 |

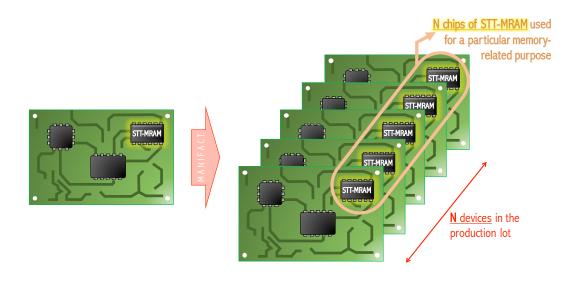

| 20 | A set of $N$ devices produced at a manufacturing facility each of which containing a STT-MRAM memory chip                                                                                                                                                    | 67 |

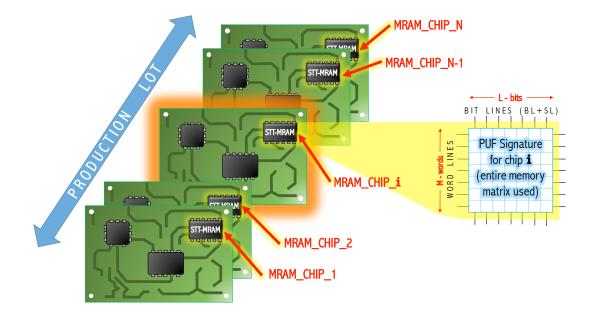

| 21 | The PUF signature is produced using, for each chip, the entire STT-MRAM memory matrix for a single signature. Each PCB can then be identified exploiting the resistance variation of the MTJs constituting the cells of the magnetic memory.                 | 68 |

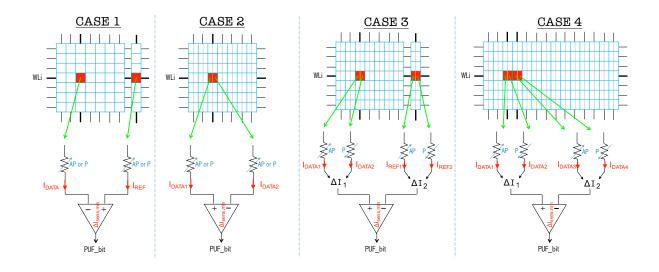

| 22 | A comparison among CASE 1, CASE 2, CASE 3 and CASE 4 - the sensing schemes used in the simulation framework to evaluate the quality of the PUF coming from a set of memory matrices                                                                          | 71 |

# LIST OF FIGURES (Continued)

# **FIGURE**

# PAGE

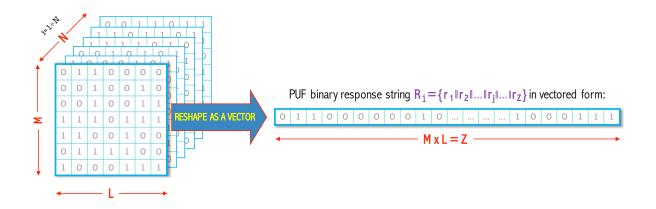

| 23 | Transforming the binary response string of the PUF from matrix to vectored form.                                                                                                                                                                                      | 74 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

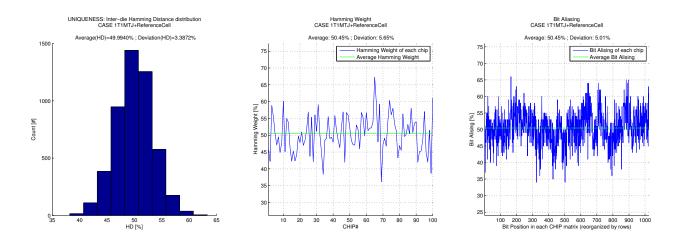

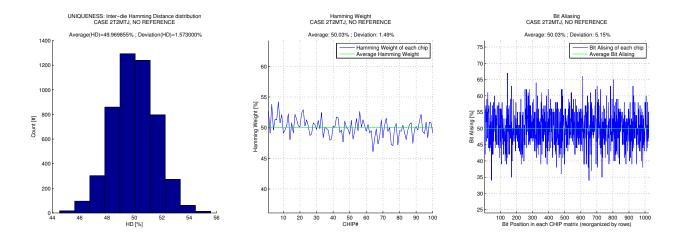

| 24 | PUF Uniqueness evaluation for CASE 1, MTJs all pre-programmed in parallel (P) configuration.                                                                                                                                                                          | 80 |

| 25 | PUF Uniqueness evaluation for CASE 1, MTJs all pre-programmed<br>in antiparallel (AP) configuration.                                                                                                                                                                  | 81 |

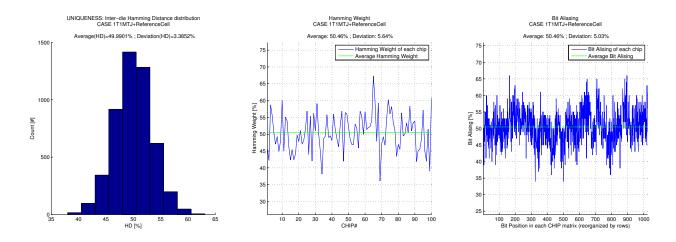

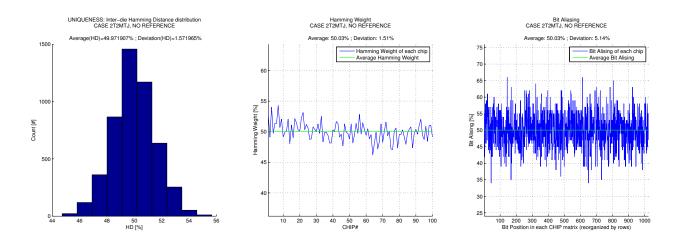

| 26 | PUF Uniqueness evaluation for CASE 2, MTJs all pre-programmed in parallel (P) configuration.                                                                                                                                                                          | 82 |

| 27 | PUF Uniqueness evaluation for CASE 2, MTJs all pre-programmed<br>in antiparallel (AP) configuration.                                                                                                                                                                  | 83 |

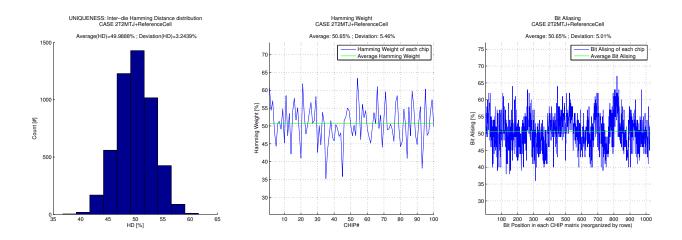

| 28 | PUF Uniqueness evaluation for CASE 3, MTJs pre-programmed in reversed-combo (P+AP) configuration.                                                                                                                                                                     | 84 |

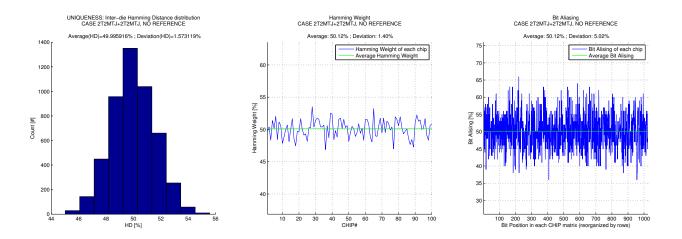

| 29 | PUF Uniqueness evaluation for CASE 4, MTJs pre-programmed in reversed-combo (P+AP) configuration.                                                                                                                                                                     | 85 |

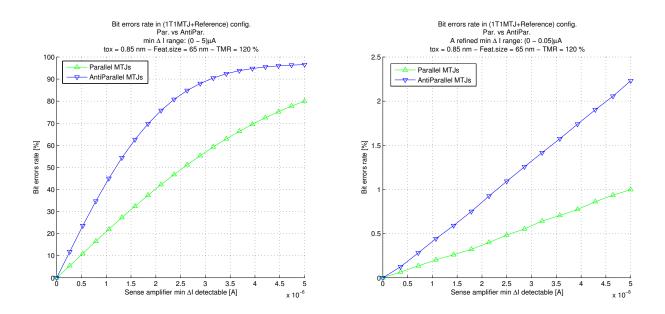

| 30 | Bit-Error Rate for Case 1, comparing parallel (P) vs antiparallel (AP) case. The former is the winner here.                                                                                                                                                           | 89 |

| 31 | Bit-Error Rate for Case 2, comparing parallel (P) vs antiparallel (AP) case. The former is the winner here.                                                                                                                                                           | 90 |

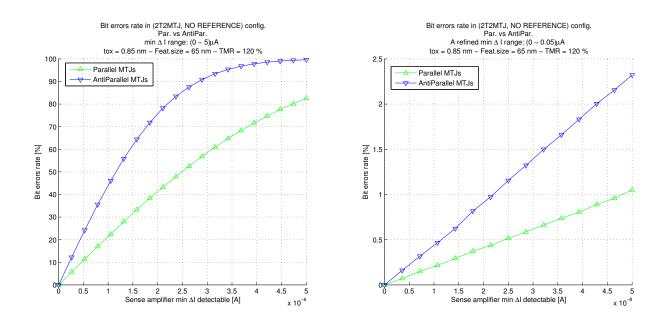

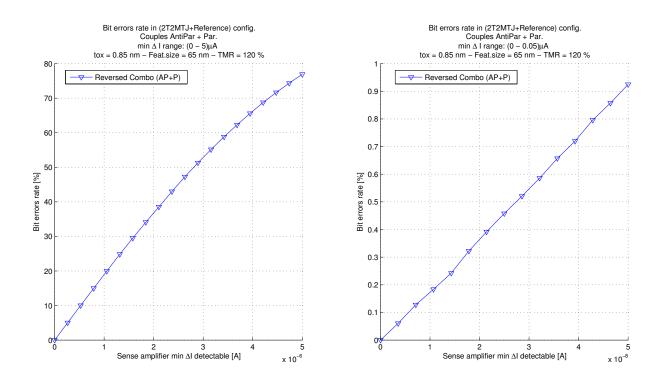

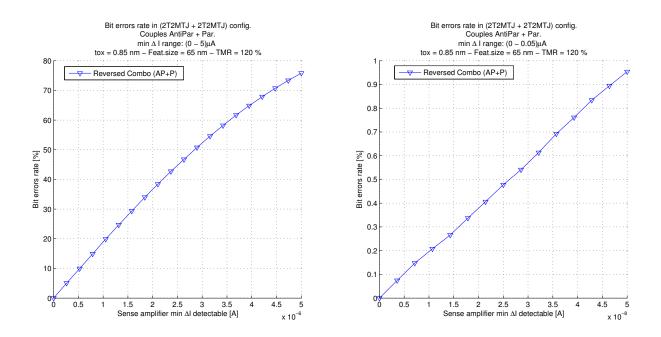

| 32 | Bit-Error Rate for Case 3, which includes a reversed-combo (P+AP) programming and the use of reference cells.                                                                                                                                                         | 91 |

| 33 | Bit-Error Rate for Case 4, which includes a reversed-combo (P+AP) programming and no reference cells.                                                                                                                                                                 | 92 |

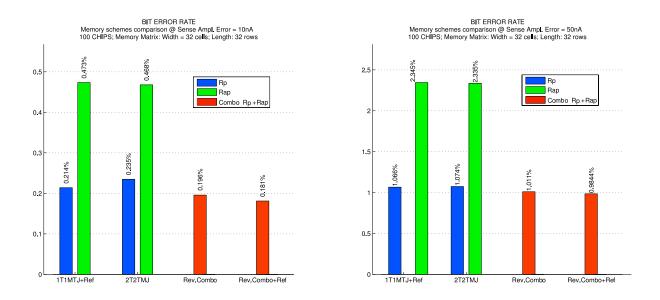

| 34 | BER comparison at sense amplifier error of $10nA$ and $50nA$ . Smaller detectable differential currents lead to more expensive and more precise sense amplifiers which reduce the BER. Also, at smaller currents, the BER differences among Cases is more appreciable | 93 |

| 35 | Influence of the nominal reading voltage over the shifting of the pop-<br>ulation of resistances of the MTJs.                                                                                                                                                         | 95 |

# LIST OF FIGURES (Continued)

# **FIGURE**

# PAGE

| 36 | Beyond Cases 14: Increasing the space of Signatures of the PUF generated by means of STT-MRAM                            | 98  |

|----|--------------------------------------------------------------------------------------------------------------------------|-----|

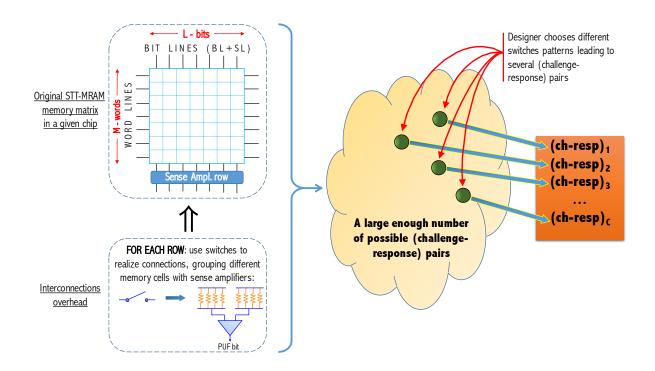

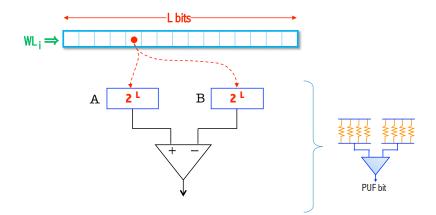

| 37 | STT-MRAM as Strong PUF: obtaining a set of different (challenge-response) pairs for a given STT-MRAM chip                | 103 |

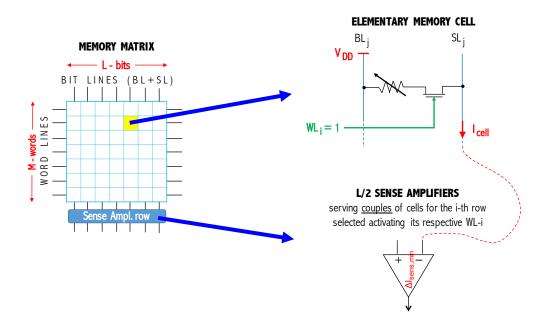

| 38 | Memory layout assumptions                                                                                                | 104 |

| 39 | Preliminary thoughts on possible combinations of grouping memory cells (seen as MTJs' associated resistance) in parallel | 105 |

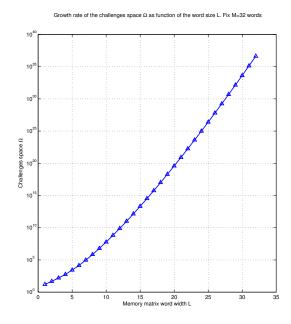

| 40 | PUF challenges space $\Omega$ dependance on memory width $L$ (semilog plot)                                              | 112 |

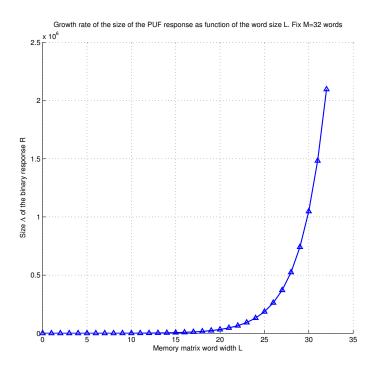

| 41 | PUF response string size $\Lambda$ dependance on memory width $L$                                                        | 113 |

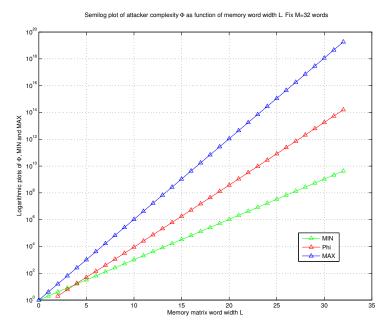

| 42 | Attacker complexity $\Phi$ dependance on memory width $L$ (semilog plot).                                                | 115 |

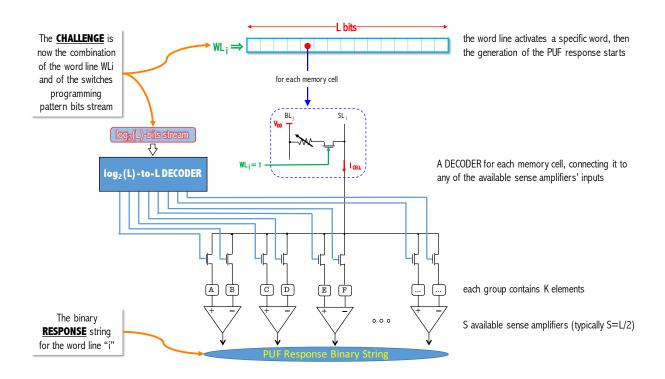

| 43 | A possible high-level digital implementation of STT-MRAM as Strong<br>PUF. A Decoder is needed for each memory cell.     | 117 |

## SUMMARY

The contribution of the present thesis work is to offer an extensive analysis and new methodologies and guidelines on the use of **Magnetic Memory (MRAM)**, in its most advanced, recent and performing flavor (STT-MRAM) as a tool to realize a unique and unclonable binary signature out of a magnetic memory chip, eventually implanted as a part of a more complex digital system device, providing then a low-cost and robust tool to generate a signature out of each of the devices of a given manufactured production lot.

The need of generating a signature comes from the new dictations of **Hardware Security** field, a set of practices and rules devised to fight intellectual property theft and electronic chips piracy. The technique used to apply these principles to magnetic memory is called **Physically Unclonable Function**, or **PUF** for short.

**Chapter 1** briefly provides a qualitative overview on MRAM and PUF, describing their respective potentials and advantages.

In Chapter 2, a deep background on the topics of Magnetic Memory and Hardware Security is offered. Especially when it comes to MRAM, this technology is very new and experimental: there is then no unified literature on the topic and the current research outcomes, even though very challenging and original, do not follow any common standard. Chapter 2 has then been written, after collecting information from several tenth between books and papers on the topic, to guide the reader on magnetic memories, from their main working principles towards the current applications, providing a hopefully clear and ordered path of the current experimental

## SUMMARY (Continued)

trends, classifying them according to the different fields of use in the digital electronics domain. Also, some background on Hardware Security and PUF is offered.

Chapter 3 reflects the main thesis goals, achievements and contributions to the fields of MRAM and Hardware Security, containing the following results:

- Analytical study of a proposed DC electrical model of the equivalent resistance of a magnetic memory (MRAM) cell, to verify and test its boundaries, statistical analysis and application to physical unclonable functions. Focus on the associated equivalent resistances distribution of the two parallel/antiparallel states of a magnetic memory and dependence on physical parameters (MRAM oxide thickness and process variations);

- 2. Extension of the previously proposed work [17] [18] on MRAM as Physical Unclonable Function, consisting of two circuit layouts, based on a string of MRAM, to an entire memory matrix – in order to use the very same main memory of a digital system to implement a PUF, assuming MRAM to become the next generation on-chip main memory;

- 3. Further extension with respect to point 2) using two new electrical sensing models;

- 4. Analysis of the results for all the four cases, evaluating the PUF quality (in terms of uniqueness and stability), and influence of the variability of some parameters of an MRAM on the PUF quality itself, using the concept of Hamming distance, including bit-error rate;

- 5. Augmenting the proposed PUF model for Hardware Security: STT-MRAM not only becomes a tool to generate a unique Signature ID for a given memory chip but also a way to support chip Authentication (a so called Strong PUF).

## CHAPTER 1

## INTRODUCTION

Magnetic memories, for short MRAM, represent a novel class of digital memory technology able to store data playing with magnetic field effects on ferromagnetic nanomaterials, devised to overcome current limitations driven by the scale down of current CMOS-based memory devices. Its most recent flavor, p-STT-MRAM, promises to become a unique, universal, fast memory technology applicable through all the memory hierarchy stack of a digital computer system, combining all the advantages of current memories at little cost and design effort. MRAM technology enables super fast speeds in both read and write operations, non-volatility, unlimited endurance, low cost and high density.

Hardware Security is a new field, applied to electronic systems, representing a set of design practices and rules that contribute in the intellectual property protection, fighting electronic chips piracy and design thefts. Its most refined implementation, called Physically Unclonable Function (PUF), enables to exploit some random physical properties of a given electronic device, subject to process variation due to fabrication tolerances, to generate a strong and unique signature out of a particular integrated circuit, for (but not limited to) security and authentication purposes.

Both MRAM and PUF are very new concepts of digital electronic design: MRAM is a new promising memory device, while PUF is a new application needed for Hardware Security reasons. They are originally not necessarily correlated, and the contribution of this thesis work is to study them both and tie them together, improving the first ideas over the study of MRAM as PUF conducted by [17] and [18] with a more extensive and rigorous analysis over MRAM process variation to validate its suitability as PUF and proposing new electrical models to generate a Physically Unclonable Function out of an MRAM chip.

The way a magnetic memory cell stores a binary information (a logic 0 or 1) is associated to its behavior as binary variable resistor (respectively low resistive state and high resistive state). It has been seen, realizing early prototypes of magnetic memory, that both states do not exhibit a nominal value only but are accompanied by a rather wide standard deviation. This peculiarity, fought for digital applications, can be used to realize a Physically Unclonable Function to generate a binary signature out of a MRAM chip.

The work done so far on STT-MRAM as PUF is very little and extremely preliminary, and finding a suitable model to describe the resistive states of MRAM both for digital and PUF applications, taking into account process variation, is something never deeply investigated before – current models have either been proposed theoretically or they come from specific fitting analysis of very narrowed types of magnetic memories only.

## CHAPTER 2

# BACKGROUND

The focus of the present thesis work is on employing **magnetic memory**, a non-volatile digital memory technology, in the field of **Hardware Security**, in order to verify its capabilities into securely identifying a chip design of a particular produced chip lot, by generating a unique signature for each of them, aimed at preventing devices cloning and design theft.

Different methods exist to implement hardware security features within a chip, most of which are digital (given the intrinsic digital nature of nowadays' chips). In the present thesis work, the **Physical Unclonable Function (PUF)** method is analyzed.

The physical device employed to achieve this goal is the magnetic-tunneling junction, or MTJ, in its most advanced flavor at the moment: the spin-torque transfer magnetic memory (STT-MRAM).

The goal of this background chapter is to provide an extensive introduction on MRAM with a stronger accent on Hardware Security and PUF fields. The related notions are presented and organized as follows:

- A brief analysis on the future trends of digital memories is presented, highlighting the main reasons and current limitations loading to the transition to the next-generation memories, where 'magnetic' and 'non-volatile' are both becoming two adjective of a viable solution.

- The main working principles behind magnetic memories is introduced, focusing then on the particular memory technology used in the present thesis work: the STT-MRAM.

- Further remark is posed on STT-MRAM from an higher-level standpoint. A DC electrical model, together with the main characterization features of this technology especially for PUF applications, are introduced.

- The present chapter moves then into investigating the field of Hardware Security, typical possible solutions to achieve chip authentication and the role of PUF, presenting some among the most popular current PUF ideas and implementations.

- Finally, the current work and ideas, still preliminary, on specifically employing STT-MRAM as PUF are presented. This last part represents an introduction as well as the main connection with next Chapter and the motivations of this thesis work.

#### 2.1 Computer memories: trend towards non-volatile technology

Digital computer memories have experienced a quite fast evolutions in the last few decades. CPU caches are reaching incredible speeds and higher densities of integration, and the same promises are carried out by volatile main memory (RAM). Above all, the most abrupt and remarkable evolution during the last ten years has interested secondary storage: great developments on Flash memories are leading to a gradual transitioning from the slower noisier hard disk drives (HDD) to solid-state drives (SDD), effectively overcoming one of the most frustrating bottlenecks in computer systems.

Solid state memories, based on advanced evolutions of MOS semiconducting technology revisited to introduce non-volatile features, have driven the development of more efficient embedded systems, after some preliminary attempts on using miniaturized hard-disk drives did not lead to any feasible result.

Nowadays **embedded system** does not mean any longer low performance super-specialized chip: recent evolutions on semiconductor technology are seriously changing this scenario. Low power devices, combined with very remarkable performance and more careful chip design, enable to realize microprocessors which can feature high-speed multicore capabilities without need of any active power dissipation and very low power requirements. Traditional personal computers are being used less and less by people in everyday's life, and transition towards handheld devices as tablet, smartphones and intermediate categories (the so called *phablets*) is something that we experience more and more. This is what an embedded systems is starting to sound like in the last few years. The future, in my opinion, will be a combination of super portable and wearable computing systems linked, through an high speed and reliable internet connection, to cloud services and remote computation. Personal computers, in their traditional definition, will gradually disappear or at least be confined into a very reduced set of specific applications.

This is the reason why, nowadays, there is less and less room into choosing between **speed** and energy saving: even in embedded systems, we need them both. Although this may sound in total opposition with respect to the traditional trade off between high performances and power consumption, researchers are pushing towards new memory classes which are able to achieve both.

One of the most promising trends is **non-volatile memory**: a particular class of digital memory devices, proposed in different flavors, that tries to combine the best aspects of any current memory technology. Magnetic memory, MRAM, is a type of non-volatile memory, and the present thesis work focuses on implementing Hardware Security techniques on top of its most advanced version: the Spin-Torque Transfer Magnetic Memory: STT-MRAM.

### 2.1.1 Digital memories hierarchy general considerations

Thinking computer architecture means thinking about memory organization and sub-systems. Almost every digital chip requires a certain amount of memory to save, either temporarily or permanently (with respect to time or power on/off), some data. In nowadays computer systems, the memory hierarchy is structured as: CPU registers, cache memory (typically more than one level), main memory (or RAM) and secondary storage (HDDs or, more recently, SSDs).

Although this hierarchy allows to get, at each level, a reasonable trade-off between performance, area, cost and power, the need of enabling an intercommunication among these levels implies using controllers and real-time translation between hardware and software protocols used at each stage. In the traditional approach, it is impossible to get a computer system working only with one kind of memory. For example, using RAM for everything would imply at the same time extremely slow CPU registers, as well as poor density as secondary storage and lack of non-volatility.

Performance limitations are equivalent to bottlenecks. Most of the time the processor waits (issuing NOPs) for new data to be fetched into its high-speed registers. The outer data, requested by the CPU, is present in slower memory systems with respect to CPU SRAM cache, like DRAM, which may in turn need to load data from other slower memory devices like hard drives. An evident limitation to the overall system performances.

### 2.1.2 Future memory trends: the "dream memory"

None of the current memory technology can be classified as the best. Cache memories are small and fast, but rather expensive and volatile. The main memory is denser and less expensive, but slower (requires refresh) and volatile. Finally, secondary storage is denser, non-volatile and even less expensive, but is far slower and not long-term reliable (for example, floating gate degradation issues in Flash technology). Researcher are constantly working on improving memory technologies, and the desire of a "**dream memory**" could soon become completely true: a universal technology overcoming the limitations of all the current memory types and combining all of them together. A unique, universal, fast memory technology applicable to all memory hierarchy levels, combining only the advantages of current memories at a small extra cost and reduced additional design efforts:

- High speed of operations: time of access a given memory location reduced to a few nanoseconds, in both reading and writing modes. We are basically requesting cache-level performances;

- Low power: the memory does not consume a lot of dynamic power during its operations (read, write) and especially the static (standby) power is reduced ideally to zero. This is a feature typically presents in the lower tiers of current memory hierarchy;

- High density of integration: being able to pack a rather large memory capacity into as little area as possible. A mandatory requirement for current cache and RAM;

- Reliability, high endurance: a prerequisite for any memory, employing memory error detection and/or correction with minimum hardware overhead;

- Non-volatility: ability to store information even when the power is completely shut down and in reduced power states. Nowadays, a typical feature of secondary storage only;

- Absence of refresh: memory cells are able to retain their content through the entire cycle of operation at power on without leakage current causing the need of refreshing the information, the principal cause of current RAM main memory slow-down.

- Low cost: both in design and in manufacturing phases. A requirement strictly related to the design complexity and the materials used.

- Integration on top of silicon technology: avoid to use a completely different/new technology to physically implement a new memory but rather exploit current silicon technologies, which are quite inexpensive.

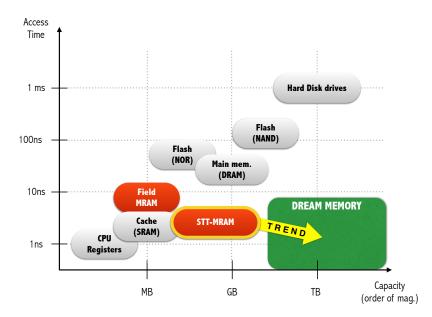

*ITRS* is a committee defining standards for an **International Technology Roadmap** for Semiconductors. Inside its most recent report, Edition 2013 [1], the main predictions and trends reflect the considerations highlighted so far. For the near term, 2013-2020, it is expected that designers and researchers work on CMOS efficient scaling, endurance, noise margin reduction and solve memory latency gap into systems. Moreover, for the long-term trend, 2021-2028, ITRS forecasted that new memory structures will need to be identified and implemented, replacing both DRAM and SRAM with more efficient solutions, indicating **non-volatile memories** as possible candidates. At the same time, the typical desired combination of requirements of "low-cost, high-density, low-power and fast-latency memory" [1] are required especially for large systems. A comparison of speed versus capacity (density) of memory technologies is qualitatively shown in Figure 1. Non-volatile memories look like a promising solution to address ITRS concerns and roadmap guidances as well as a valid candidate to become a universal memory. Possibly, the dream memory we are looking for. Figure 1, in particular, shows the two generations of MRAM: the first generation, slower and less dense (Field MRAM) and the second and last generation, STT-MRAM, overcoming most of the limitations of the Field approach especially in writing speed and power consumption, as well as density.

#### 2.1.3 MRAM as non-volatile universal memory candidate

Among the possible types of non-volatile memories, magnetic memory (MRAM) looks like a very viable solution. Based on a particular stack of materials called magnetic tunneling junction (MTJ), it brings a unique combination of advantages establishing a new class of digital

Figure 1. Main digital memories: Capacity vs Access Time. In red, magnetic memories

memory. A summary of these advantages is well documented in the book *Emerging Memories Technologies and Trends* [2]. In a few words, MRAM allows to achieve:

- An unlimited number of read and write operations;

- Both read and write access times orders of magnitude faster than conventional Flash and EEPROM, reaching, in the most advanced implementations, even SRAM speeds of the order of few nanoseconds;

- **High memory cells density**: area of occupation is reduced to a minimum thanks to a vertical stacking technique with respect to the access transistor of the memory cell itself.

MTJ fits on top of a single transistor, thus the memory cell size is comparable (and even better) to DRAM or Flash technologies;

- Low power, low operation voltages; absence of refresh operation, plus write operations do not require an erase to be done in advance;

- Non-volatile storage, enabling implementations as *instant-on* main memory;

- Immunity to radiation, a strict requirement for military and space applications;

Moreover, the book [2] lists the main players on the MRAM market: IBM, Sanyo, Infineon and Motorola are worth being mentioned. In particular, IBM can be considered the pioneer of the field with its first viable solution realized in 1997 [3].

Currently, researchers are working on overcoming the **main limitations of MRAM**: during write operations, both power consumptions and latency are still higher than SRAM. This factor, combined with nanoelectronics-level considerations, also limits the density of integration and the GigaByte barrier still needs to be broken.

#### 2.2 MTJ as Magnetic Memory using Magnetoresistance: MRAM

## 2.2.1 Using electromagnetism to store digital information: main idea

Every digital memory technology relies on a specific microscopic working principle. For example, DRAM is based on capacitive effects, Flash memories on charges trapped on a floating gate within a thin oxide. Magnetic memory (MRAM) is based on **electromagnetism**, and in particular playing with the magnetic field effects on ferromagnetic materials, to store data in a binary form. MRAM is physically realized as a stacks of ferromagnetic materials. Each of these ferromagnet is characterized by a well defined magnetization M, a macroscopic vectorial quantity characterized by a direction and an intensity. The key point for MRAM is about controlling and changing in a stable manner the magnetization direction of a ferromagnetic layer ("switching").

## 2.2.2 Magnetoresistance effect and Spin-Torque transfer

Magnetization needs to be translated to an higher-level concept in order to be exploited in digital applications. The **magnetoresistance effect** is the link between nanoscale and digital level, and expresses the observed resistance across a particular stack of materials including ferromagnetic ones, while playing with their magnetization direction.

MRAM are based on the discovery, in 1975, of the Tunneling Magnetoresistance, or TMR [4]. Let us consider a stack made, from the top through the bottom, of:

- A first ferromagnetic (FM) layer, called **free layer** or storage layer, whose magnetization vector M<sub>1</sub> is free to switch under the influence of an external quantity (a magnetic field);

- A thin insulating layer, **oxide**, through which electrons tunneling happens;

• A second ferromagnetic (FM) layer, named **pinned layer** or fixed layer, whose magnetization vector M<sub>2</sub> is always kept fixed in any operating condition.

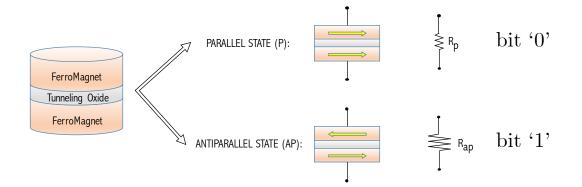

This structure is called Magnetic Tunneling Junction, or MTJ. Both FM layers are characterized by a proper magnetization vector M aligned along a precise direction called easy axis. An external applied magnetic field causes the free layer to switch its direction by 180 degrees, letting it be either parallel or antiparallel to the magnetization vector of the pinned layer. Two possible states are then defined:

- Parallel configuration (P): M<sub>1</sub> and M<sub>2</sub> are in phase, resulting in a parallel state associated resistance R<sub>p</sub> rather low;

- Antiparallel configuration (AP): M<sub>1</sub> and M<sub>2</sub> are out of phase by 180 degrees, resulting in an antiparallel state associated resistance R<sub>ap</sub> rather high.

These states of high and low resistance can be used to store a digital binary value, 0 or 1. For convention,  $R_p$  corresponds to the low state (0) and  $R_{ap}$  to the high state (1). Figure 2 sums up the MTJ structure and its interesting property to behave as a **variable (binary) resistor**.

The **TMR ratio** is the expression of the distance between the two resistive states, defined in Equation 2.1. Nowadays the TMR can go up to more than 100% at room temperature. Using thin films causes an abrupt P/AP difference, thus an high TMR. To make a magnetic memory reliable, the TMR must be as high as possible in order to be able to discriminate correctly the two digital levels leaving very little room to sensing errors.

$$TMR_{\%} = \frac{\Delta R}{R_p} \cdot 100 = \frac{R_{ap} - R_p}{R_p} \cdot 100$$

(2.1)

Figure 2. Magnetic tunneling junction: basic structure, P and AP states from the analog (resistor) and digital (bit value) perspective.

## 2.2.3 STT-MRAM: spintronic meets "second generation" magnetic memory

The TMR effect has been used for years in the head of hard disk drives to read and write data in the spinning plates. First applications to MRAM began with the so called **Field MRAM**, which used a magnetic field to toggle the magnetization of the free layer. Unfortunately, this approach had several tradeoffs:

- The need of additional lines in a memory array to discriminate read operations from writes <sup>1</sup>;

- High write power, since a large current in a wire placed nearby the free layer of the MTJ needed to be used to trigger a magnetic field whose intensity is able to realize the switching;

$<sup>^{1}</sup>$ Switching is actually the write operation in a magnetic memory

• Disturbance problems: the magnetic field used to write a cell caused potential switching of nearby cells.

In the last few years, the idea of implementing TMR effect into MRAM has thus shifted towards a novel approach: **spintronics**. **Spin-torque transfer MRAM**, **STT-MRAM**, is based on letting a current flow through the MTJ device itself to realize the switching of the magnetization of the free layer. This means that a current flowing through the device can both sense the resistance (for reading operation) and program (write operation) the memory.

Spin-torque transfer was discovered only in 1996. The current is seen as a set of spin-up and spin-down electrons. While flowing through a non-magnetic material, nothing happens to both populations of electrons. On the contrary, when the current crosses a ferromagnet, they are both subject to interesting alterations: the electrons whose spin is aligned with the magnetization direction grows in terms of population size, and the growth is compensated by an equal loss of electrons from the opposite spin population. While the magnetization vector of a ferromagnet can change the populations of spin-up and spin-down electrons, it has been observed that also the opposite principle can arise: a polarized current can switch the magnetization itself. This behavior is exactly the one used to drive the switching in a STT-MRAM.

With respect to Field MRAM, STT-MRAM does not use any magnetic field: the write selectivity is very precise (since the spin-torque effect happens within a cell without influencing surrounding ones), thus magnetic interferences are not present anymore. Write current is also much lower than the one required by Field MRAM as well as the architecture is simpler (no longer multiple wires to discriminate between read and write operations). Moreover, when device scaling occurs, transistors length decreases as well, leading to a reduced maximum drainto-source current: fortunately, the required current to perform MRAM cell switching scales down very nicely with MTJ size shrinking.

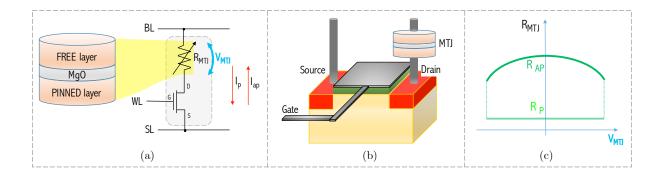

#### 2.2.4 STT-MRAM digital memory cell

The typical structure of a memory cell constituted of STT-MRAM is depicted in Figure 3. Each cell, in its basic configuration, is called 1T1MTJ being constituted by a single access transistor and and a single MTJ stack. Figure 3 also shows qualitatively the dependance of the binary MTJ resistance on the applied bias to the cell, and the hysteresis realized by the switching behavior. When the applied voltage rises above a well known quantity (typically a few hundreds mV) the switching between the two states (P to AP or viceversa) happens, and it is driven by the polarity of the voltage. In order to program the cell, either a voltage or a current source can be used. The red arrows in Figure 3 indicate the required direction of the current flowing across the device to trigger the spin-torque transfer effect.

Basic memory operations are realized as follows:

- Memory cell selection happens through the access transistor. Its gate is driven by the WL (word line) signal;

- To write in the memory, a current is applied. The direction of the current determines how the cell is programmed.

- Reading operation happens sensing either the current or the voltage across the MTJ, which is simply treated as a variable binary resistor.

Figure 3. STT-MRAM basic digital memory cell, constituted of an MTJ stack on top of an access MOS transistor. In (a) the electrical scheme, in (b) the simplified physical layout and in (c) the dependance of the parallel and antiparallel resistance on the voltage drop insisting on the MTJ.

It is extremely important to keep the current flowing across the MTJ stack during reading phase much smaller compared to the one required for writing operation, in order to avoid the MRAM cell changing its value while a read operation takes place.

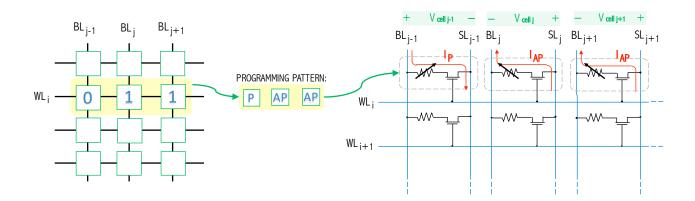

A qualitative idea on how a MRAM memory array looks like is illustrated in Figure 4.

A further advantage of MRAM is the density of integration: with respect to current memory technology competitors, in fact, the MTJ stack is grown immediately above the drain contact of its access transistor, translating into a 3D stacked structure that starts from the bit line all the way through the MTJ and the MOSFET. Building MRAMs simply means adding a few thin extra layers of materials over a MOS-based integrated circuit, leading to a density of integration extremely high.

Figure 4. STT-MRAM memory array: WL is the word line employed to activate a given row, then read and write operations happen exploiting the BL (bit line) and SL (source line), which provide access to the MTJ. In this particular example a '0 1 1' binary string has to be written.

### 2.2.5 Main applications: consolidated work and novel trends

In the last few years, different research groups and memory Companies spent remarkable efforts to design, build and test a multitude of MRAM ideas and applications. In this subsection, the most populars ones are briefly listed, together with some additional information on MRAM. The first implementations regarded the first generation, Field MRAM, then researchers started to transition towards the adoption of STT-MRAM, given that more recently this second generation magnetic memory has become more mature and stable.

#### Nanoscale ideas

A magnetic tunnel transistor has been proposed [5] based on a double tunneling junction. A sort of BJT based on hot-electrons transport to generate the collector current, making use of two MTJs within the emitter/base/collector junction and exploiting the principles behind spintronic. More recently, a new pseudo-spin-MOSFET has been fabricated and characterized [6]: a circuit using an ordinary MOSFET plus an MTJ to reproduce functions of spin transistor, offering a transconductance which is function of the status of the MTJ stack (parallel or antiparallel). To enhance spintronic applications improving the TMR ratio, MTJ tunneling oxide based on aluminium has been replaced with magnesium, in a stack including Fe/MgO/Fe: Yuasa et al reported earlier in 2004 [7] a giant TMR ratio up to 180% at room temperature, using MTJs based on single-crystal stacks using MgO as oxide. Nowadays, every MTJ structure is based on complex sets of layers, but the oxide is still MgO.

#### A universal memory

The obvious application of STT-MRAM is memory. In 2006, IBM was able to realize a 16Mb Field MRAM prototype chip [8], after experimenting the performance and playing with the characteristics of magnetic tunnel junctions development. The latest advancement in using STT-MRAM as the new universal memory has been achieved by Toshiba with the p-STT-MRAM (perpendicular) [9]. This technology is currently the closest to the idea of universal memory, and it is based on having the magnetization vector in the two ferromagnetic layers perpendicular to their surface rather then parallel, becoming finally a promising solution for high density, high speed, non-volatile random access memory: density similar to DRAM, non-volatility and speeds comparable with SRAM, as well as a theoretically infinite write endurance and low power, yet high speed switching.

### Unbalanced MTJ flip-flop and FPGA

A new class of circuits, built by adding an MTJ the the source side of the nMOS of each of the two cross-coupled inverters constituting an SRAM memory element. MTJs are always programmed in a complementary state and until metastability is triggered the flip-flop keeps latching a defined binary value. Triggering the metastability causes the configuration stored in the MTJ couple to be loaded in the flip-flop replacing its previous content. The device can be seen as an hybrid of volatile and non-volatile memory element, where the volatile part is exactly the same of an SRAM while the two MTJs add the capability to store a configuration that can resist to long power-off periods and can be loaded at any time to replace the current SRAM cell (flip-flop) stable state. Furthermore, while the SRAM is holding its current configuration to perform a given memory operation, the MTJs can be simultaneously programmed to a different state (shadow programming) and the new configuration is immediately ready to be loaded after triggering the next metastability. This huge advantage found immediate applications into experimental FPGA, when the reconfiguration of memory blocks defining interconnections and logic blocks behaviors needs to happen as fast as possible. Remarkable results are illustrated in [10] using traditional Field MRAM, while [11] also adopts a more recent version of Thermally Assisted Switching which ensure faster operations over traditional Field MRAM.

### MTJ-based nonvolatile Logic in Memory

Logic-in-memory architecture is a rather old concept: including storage elements embedded and distributed over a CMOS plane getting rid of large delays and power required every time logic needs to access memory modules (typically over an external bus). MTJ is a good memory fit for this goal. More or less complex digital devices (from basic NOR or NAND to more complex LUT implementations) can be built and, together with the normal inputs and outputs, they come with some configurations inputs which instruct the logical block to its function. First, configuration inputs program some data stored into MTJ devices, which allows to execute an arbitrary logic operation taking the data inputs and providing the related output. Typical applications include not only Nonvolatile FPGA but also CAM (content-addressable memories). A remarkable example of Logicin-Memory architecture is offered by the work of Matsunaga et al [12], describing how a non-volatile full adder can be implemented using this approach.

## Associative Computing

Logic-in-Memory enabled new CAM to be built. The work of Guo et al in [13] describes how CMOS and MTJ can work together to realize a TCAM (ternary content-address memory) key-data, using STT-MRAM and integrable with DDR3 protocol (the device can be plugged into a normal DDR3 socket). The goal of TCAM is processing in memory, reducing access times to an external slower memory, and offering not only CAM functionality (rapid search of data) but also processing, within the same memory chip, the output (a reduced instruction set is offered to the user) before being transferred eventually to the CPU, which is now simply in charge of handling the result rather then processing computation on raw data.

#### Normally-Off Processor with p-STT-MRAM

The use of the advanced version p-STT-MRAM proposed by Toshiba in a more recent sub-30nm flavor enabled an effective reduction in power of cache memory within a CPU. Previous generation of conventional STT-MRAM, when used as cache memory, caused an extremely high active energy in the CPU (due to rather high write energy) although ensuring an almost-zero standby power. The breakthrough by Toshiba's advanced p-STT-MRAM in 2012 [14] and 2014 [15] enabled a decrease in power for short CPU standby state while a combination with power gating techniques ensures the same advantage also for longer CPU standby states, testing the results on HP-mobile processors. Overall, standby power is reduced by roughly 50%, processor performance are comparable to that of SRAM and using nonvolatile p-STT-MRAM L2 cache also active power is drastically reduced (about 30% while CPU active state is dominant, 65% in moderate usage of CPU resources and 90% in almost totally-idling state). Future ideas include avoiding a net difference between volatile (SRAM) and non-volatile (MRAM) parts in a CPU cache devising a solution which is an hybrid of the two: non-volatility feature will run all the way down from L2, L3 caches down to CPU core, L1 cache and registers files. In this optic, Big.LITTLE architectures sound according to Toshiba a viable next implementation.

#### Resistive computation: a non-volatile CPU microarchitecture

Similar to the achievements by Toshiba, Guo et al introduced in a remarkable paper [16] a proposed set of guidelines to implement the concept of resistive computation. The main idea is based on solving the power wall problem while scaling down beyond 45nm migrating most of the architecture of a modern CPU from traditional CMOS to STT-MRAM. Every main CPU inner block is analyzed in details carefully re-engineering its peculiarity embedding a non-volatile approach, then an 8 core Sun Niagara-like CMT processor is modeled at 32nm technology node, showing huge reduction in terms of power dissipation and leakage power yet offering performance comparable to standard CMOS.

### Hardware Security and PUF

Last but not least, preliminary work has been conducted in [17] and [18] to show how STT-MRAM can be employed to generate a unique Signature (or ID) for a digital MRAM memory chip, exploiting the process variation of the parallel and antiparallel configurations as Physical Unclonable Function. No more words will be spent in this paragraph since this is the main topic of the thesis work and will be widely treated in the next chapters.

#### 2.3 STT-MRAM electrical models and characterizations

A wide variety of models and equations has been proposed both on literature and papers to represent the behavior of an STT-MRAM memory cell under different conditions (associated equivalent resistance, writing current pulse, switching behavior,...). At the moment there are no accepted standards on which model is better to be used for a specific purpose. In order to use STT-MRAM as PUF, a goal of this thesis work, the memory needs to be modeled in the simulations that have been conducted. After researching among different proposed equations, only one model seems representative enough for our purposes, since it takes into account a precious link: the effect of microscopic quantities (such as, but not limited to, the oxide thickness of the MTJ) over the digital STT-MRAM itself.

In order to characterize a PUF based on STT-MRAM, we obviously first need to characterize the STT-MRAM memory chip itself. What we need is a model that expresses the resistance of the parallel and antiparallel states ( $R_p$  and  $R_{ap}$ ) of each memory cell based on the MTJ stack properties. First of all, then, focus has been put into researching among the equations regarding a DC static modeling of the equivalent resistance of the MTJs rather then dynamic models which focus more on the switching behavior of the device (writing).

The present thesis work is an extension of the work by Zhang et al, illustrated in two subsequent papers [17] and [18]. Both papers used a particular way to model  $R_p$  and  $R_{ap}$ . Particularly in [18], more focused on STT-MRAM rather than non-volatile memories in general, the model which has been used is somehow based on the fact that the MTJ resistance is related to the area of the MTJ stack and to the oxide thickness, and although no direct equation is showed, the paper actually only links these two physical parameters to an intermediate quantity (rather than the resistance of P/AP states): the **product RA**, an intrinsic quantity defined for each MTJ stack. RA is the resistance-area product. The mathematical formulation of this peculiar dependence is illustrated in Equation 2.2.

$$RA \propto \left( e^{a_0 \cdot t_{ox} + b_0} + \sum_{m=1}^{c} (-1)^{m-1} \cdot V_{MTJ}^{2m} \cdot e^{a_m \cdot t_{ox} + b_m} \right)^{-d}$$

(2.2)

Equation 2.2, proposed by [19] and used in [18], links oxide thickness and feature size of the MTJ (dimension of each layer composing its stack) to the physical value RA. Keeping constant the voltage applied to the MTJ structure,  $V_{MTJ}$ , different oxide thicknesses  $t_{ox}$  lead to a different RA value. For example, for  $t_{ox}=0.85nm$ , it is usually assumed  $RA=10\Omega\mu m^2$ . Except for  $t_{ox}$  and  $V_{MTJ}$ , the remaining terms of the right end side of Equation 2.2 are simply fitting parameters, technology dependent.

This equation does not really provide a complete model to the effective resistances  $R_p$  and  $R_{ap}$ . A well recognized model in this sense is the one provided in [20] and more extensively improved in [21], and is here mentioned and explained in the following equations.

Equation 2.3 expresses the **conductance physical model of the MTJ**, showing how the conductance at zero bias is a decreasing function of the oxide thickness  $t_{ox}$ , and depends on the potential barrier height  $\varphi$ (for MgO MTJs  $\varphi$ =0.4).

$$G(0) = 3.16 \cdot 10^{10} \cdot \varphi^{1/2} \cdot \frac{e^{-1.025 \cdot t_{ox} \cdot \varphi^{1/2}}}{t_{ox}}$$

(2.3)

However, in the electrical macro-models of MTJs, the resistance performance of the device can be expresses through the **simplified resistance equation** shown in Equation 2.4. It seems important to highlight that we refer here to  $R_p$ .

$$R(0) = \frac{t_{ox}}{F \cdot \varphi^{1/2} \cdot Area} \cdot e^{1.025 \cdot t_{ox} \cdot \varphi^{1/2}}$$

(2.4)

The **parameter F** is a factor computed starting from the resistance-area product according to Equation 2.5. For example,  $RA=10\Omega\mu m^2$  gives then F=332.253.

$$F = \frac{3322.53}{RA}$$

(2.5)

The variable **Area** is instead the cross-section area of the MTJ, and it is computed in different ways according to the physical shape of the device. Equation 2.6 lists down the typical possibilities.

$$Area = \begin{cases} \pi \cdot A^2, & \text{if circular shape} \\ \frac{\pi}{4} \cdot A \cdot B, & \text{if elliptical shape} \\ A \cdot B, & \text{if rectangular shape} \end{cases}$$

(2.6)

The resistance of the MTJ is not really constant.  $R_p$ , modeled in Equation 2.4, gives the value of this resistance at zero-voltage bias. In order to determine how its value changes according to the bias applied to the MTJ,  $V_{MTJ}$ , Equation 2.7 is used. In particular, it is worth remarking that  $R_p$  exhibits a very weak dependance on the applied bias and it can practically be considered constant over the entire range of variability of  $V_{MTJ}$ .

$$R(V) = \frac{R(0)}{1 + \frac{t_{ox}^2 \cdot e^2 \cdot m}{4 \cdot \hbar^2 \cdot \varphi} \cdot V_{MTJ}^2}$$

(2.7)

The important contribution of  $V_{MTJ}$  appears instead in the **TMR** (used to evaluate  $R_{ap}$  starting from  $R_p$ , as previously mentioned into Equation 2.1). For simplicity, now we refer to TMR<sub>0</sub> assuming it is no longer a percentage value but rather a number (then,  $TMR_{\%}=120\%$  becomes now  $TMR_0=1.2$ ). The real TMR is actually very dependent on the applied voltage to the MTJ, as described in Equation 2.8 - here  $V_h$  is the voltage at which TMR becomes half of  $TMR_0$ .

$$TMR_{real} = \frac{TMR_0}{1 + \frac{V_{MTJ}^2}{V_b^2}}$$

(2.8)

Finally, given then  $R_p$  and  $TMR_{real}$ , it is possible to evaluate the antiparallel resistance using Equation 2.9, which is a simple rephrasing of Equation 2.1.

$$R_{AP} = R_P \cdot (1 + TMR_{real}) \tag{2.9}$$

Table I recalls the principal parameters defining any MTJ structure, particularly when it comes about STT-MRAM memory applications, including the variables and constants encountered so far.

# TABLE I

# MTJ AS STT-MRAM: PARAMETERS AND VARIABLES

| Parameter               | Description                                                                                                         | Typ.Value/Example                         |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| Microscopic quantities  |                                                                                                                     |                                           |  |  |  |

| $t_{ox}$                | Oxide thickness typ. around 1                                                                                       |                                           |  |  |  |

| φ                       | potential barrier across tunneling oxide                                                                            | MgO: $0.4 \text{eV}$ ; AlO: $2 \text{eV}$ |  |  |  |

| RA                      | Resistance-Area product, intrinsic parameter of $\propto 10 \div 10^2 \Omega \mu$<br>a MTJ stack of given materials |                                           |  |  |  |

| Feature size            | Manufacturing size of the MTJ and CMOS, not typ. $45 \div 65n$ necessarily coincident                               |                                           |  |  |  |

| A, B                    | Physical dimension of the cross-section of the MTJ, related to feature size                                         | typ. 65nm                                 |  |  |  |

| Area                    | MTJ cross-section area (from A, B, MTJ shape)                                                                       | $\propto nm^2$                            |  |  |  |

| e                       | Electron elementary charge                                                                                          | $1.60 \cdot 10^{-19}C$                    |  |  |  |

| m                       | Electron mass                                                                                                       | $9.1\cdot 10^{-31}kg$                     |  |  |  |

| ħ                       | Reduced Planck's constant                                                                                           | $1.0545 \cdot 10^{-34} J \cdot s$         |  |  |  |

| Macroscopic             | quantities                                                                                                          |                                           |  |  |  |

| $R \ (R_p, R_{ap})$     | Effective resistance across the MTJ stack. "R" typically refers to the parallel state                               | ex. $(2k\Omega, 4k\Omega)$                |  |  |  |

| $TMR_0$                 | Tunneling magnetoresistance ratio at 0V bias $ex. 100\%$                                                            |                                           |  |  |  |

| $TMR_{real}$            | Tunneling magnetoresistance ratio at given bias $ex. 95\%$                                                          |                                           |  |  |  |

| $V_{MTJ}$ or $V_{bias}$ | Voltage across the MTJ structure; in this work assumed to be used to read a cell                                    | typ. $100 \mathrm{mV}$                    |  |  |  |

| $V_h$                   | Voltage at which $TMR_{real}$ becomes half $TMR_0$                                                                  | typ. 0.5V                                 |  |  |  |

Other kind of models have been developed to shape different behaviors of MTJ STT-MRAM structures. However, the one illustrated in this section is the only one which appears the most complete as well the closest to size the behavior of a wide range of MTJ structures in terms of physical size and voltages, granting its use in different papers related to the STT-MRAM topic.

Other models use typically too simplified equation to describe the behavior of the MTJ resistance, for example based on a few fitting parameters related to a specific set of physical feature sizes [22], appearing as a mere modeling as function of the applied bias only. Another lack in the field is a model which simultaneously takes into account the equations shown so far and the dependance over temperature. Currently, temperature-dependent models regarding STT-MRAM are not available at the macroscopical level, and they typically relate the temperature dependance to microscopic quantities like the tunneling electron spin polarizations of the two ferromagnets [23].

### 2.4 Hardware Security and the role of PUF

Every idea should be protected against theft and plagiarism. Electronics, and in general every product of engineering in general, is the result of clever insights, improvements and breakthrough achievements on which a team responsible for its design invests manpower, thus brains and costs.

Although market competition is a good source of continuous positive challenge and improvement, design theft, on the other side, is something that needs to be fought, and a source of substantial income losses. Hardware Security is a set of design practices that contribute in the intellectual property protection, fighting electronic chips piracy and design thefts.

Any electronic component can only hit the target market after several steps. Engineering design and manufacturing are two among them. In other words, **hardware design** and **manufacturing** are two key (and obviously unavoidable) steps. They require many steps to be accomplished, as well as the involvement of several Companies typically spread worldwide.

The globalization of the market has involved both aspects, and while chip design is usually kept in-house, in a given Company A, responsible for the design and the selling of a given chip, this Company will typically outsource the manufacturing phase to (at least) another Company B dislocated worldwide (China and Brazil are a few examples). We call Company A fab-less, while Company B is the responsible of the physical implementation of the device.

This scenario involves **Company A to share chips designs and specifications with Company B**, and during this phase, one or more third parties may access, steal and re-use them to produce illegally other lots of that particular technology. The worst case scenario includes the manufacturer itself, Company B, since it is the one in possess of both the intellectual property (the design) and the physical resources (its silicon foundry) to produce, out of control of company A, some chips and selling them to a black market - or even to the consumer market.

A basic illustration in Figure 5 shows the design path from Company A to B and the desire of protecting somehow the design during this phase, until the chips hits the market.

Figure 5. During chip manufacturing, unprotected (top) chip design may lead to design thefts. Design protection is then becoming a must (bottom).

Hardware designers have then started, especially during the last years, to implement Hardware Security features in a given chip that needs to hit the production. By **Hardware Security** we mean a set of rules, protocols and implementation techniques, usually embedded at design stage of the original chip, to fight and hopefully avoid design thefts, adding some sort of layer of security.

This layer can be implemented in different ways. For example, hardware is re-engineered in such a way to hide parts of the schematics, or similar techniques that require huge computational power to reverse-engineer the protection scheme and access back the original design subject of the possible theft. More recently, Hardware Security is relying more and more on another idea: identifying chips through a Physical Unclonable Function or PUF.

# 2.4.1 The need of identifying chips

A viable solution to fight design (and thus physical chips) thefts is the possibility of forging a **unique identification number (ID) on each chip** of a given produced lot. When the chip, after production, hits the market, eventually implanted on a wider system, each device that has been sold needs to be activated to work. The activation process requires the device to send its ID to the Company which, after checking in its database of recognized chips, will grant the OK and unlock its functionalities.

The classical approach would be embed a small non-volatile memory in each produced chip, a ROM, to permanently hold the ID. The main problem to this classical approach is that the chip producer, in charge of physically realizing the chip, together with its ID, would be capable of knowing in advance each ID itself. At the same time, if the ID is written from the chip design Company, Company A, after the lot is produced and handed back with an empty programmable read-only memory (PROM), once the chip hits the market anybody can access anyway the ID and realize similar chips with the same ID. Or, even worse, be able to detect the general algorithm behind the ID generation and replicate it to produce IDs that would still give a PASS when queried for the activation. Plus, embedding a different kind of memory (like a ROM) for the only purpose of identification implies the use of additional masks on silicon and an increased cost of the produced chips.

This idea needs then to rely on a completely different approach: a key needs to be present and associated to each chip, but simultaneously it should not be embedded permanently at all inside a given produced chip. This is the main idea behind a Physical Unclonable Function, subject of next subchapters.

# 2.4.2 PUF: Physically Unclonable Functions

**PUF** stands for **Physical(ly) Unclonable Function**, and identifies a well known physical characteristic which is associated univocally to a specific structure like an integrated circuit at the physical level. The word *physical* is very important, since the idea behind PUF is to *rely* on specific parameters at the materials level constituting a given device to generate some useful information for identification purposes.

In particular, what is exploited are some features that are, on the contrary, rather fought at the digital level: we refer to **manufacturing process inaccuracies**, that in the worst possible scenario would lead to a low yield of a chip lot.