Switching Transition Control of Insulated-Gate Power Semiconductor Devices

$\mathbf{B}\mathbf{Y}$

HOSSEIN RIAZMONTAZER B.S., Iran University of Science & Technology (IUST), 2008 M.S., Amirkabir University of Technology (Tehran Polytechnic), 2011

## THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2015

Chicago, Illinois

Defense Committee:

Sudip Mazumder, Chair and Advisor Milos Zefran Danilo Erricolo Sabri Cetinkunt, Mechanical & Industrial Engineering Ian Brown, Illinois Institute of Technology This thesis is dedicated to my mother "Mandana" who was my true support from the first day in school, my father "Nader", my brother "Farid", my grandfather "Baba Bahram", my grandmother "Maman Feri" who always provide me continuous love and support. Finally, and most importantly, I would like to dedicate my thesis to my wife "Sayeh" for her support, encouragement, quiet patience and unwavering love. She is truly the best gift I have received in my life. Thank you for being my best friend. I owe you everything!

# Acknowledgement

I would like to thank my dissertation advisor and committee members—namely Sudip Mazumder, Milos Zefran, Danilo Erricolo, Ian Brown and, Sabri Cetinkunt,—for their invaluable support and guidance throughout my research and study at University of Illinois at Chicago.

HR

## TABLE OF CONTENTS

<u>CHAPTER</u>

| I.    | INTRODUCTION                                                                             |     |  |  |

|-------|------------------------------------------------------------------------------------------|-----|--|--|

|       | A. Switching Transition Control of Insulated Gate PSDs                                   |     |  |  |

|       | 1. Inductive Load Switching of Insulated Gate PSDs                                       |     |  |  |

|       | 2. Passive Gate Drives                                                                   |     |  |  |

|       | 3. Switching Transition Control by Controlling the Gate Resistance                       |     |  |  |

|       | 4. Switching Transition Control by Controlling the Gate Current                          |     |  |  |

|       | 5. Switching Transition Conrol by Controlling the Gate Voltage                           |     |  |  |

|       | B. Motivation and Objective of Doctoral Research                                         |     |  |  |

| II.   | OPTICALLY-SWITCHED-DRIVE BASED UNIFIED INDEPENDENT <i>DV/DT</i> AND <i>DI/DT</i> CONTROL |     |  |  |

|       | For Turn-off Switching Transition of Power MOSFETs                                       |     |  |  |

|       | A. Turn-off Transition Behavior and General Control Scheme                               |     |  |  |

|       | 1. Threshold Condition for Transition Between $dv_{Ds}/dt$ and $di_D/dt$ Control         |     |  |  |

|       | Regions                                                                                  | 28  |  |  |

|       | 2. Availability of Independent $dv_{DS}/dt$ and $di_D/dt$ Control                        |     |  |  |

|       | <ul><li>B. Experimental Results</li></ul>                                                |     |  |  |

|       | C. Conclusion                                                                            |     |  |  |

| III.  | CLOSED-LOOP CONTROL OF TURN-OFF TRANSITION OF HIGH-VOLTAGE SIC MOSFETS                   |     |  |  |

| 111.  | A. Introduction                                                                          |     |  |  |

|       | <ul><li>B. Proposed Closed-Loop Gate Driver.</li></ul>                                   |     |  |  |

|       | C. Experimental Results                                                                  |     |  |  |

|       | D. Conclusion                                                                            |     |  |  |

|       | D. Conclusion                                                                            | 00  |  |  |

| IV.   | SELF CONTAINED CONTROL OF TURN-ON TRANSITION OF IGBTS                                    | 61  |  |  |

|       | A. Problem Identification                                                                | 61  |  |  |

|       | B. Control Mechanism for the Turn-on Transition                                          | 63  |  |  |

|       | C. Experimental Results                                                                  | 82  |  |  |

|       | D. Conclusion                                                                            | 93  |  |  |

| V.    | CONCLUSION AND FUTURE WORK                                                               | 94  |  |  |

|       | A. Conclusion                                                                            | 94  |  |  |

|       | B. Future Work                                                                           | 96  |  |  |

| CITED | LITERATURE                                                                               | 98  |  |  |

| APPEN | IDIX                                                                                     | 104 |  |  |

| νίτα  |                                                                                          | 106 |  |  |

|       |                                                                                          |     |  |  |

|    | LIST OF TABLES                      |      |

|----|-------------------------------------|------|

| TA | BLE                                 | PAGE |

| I. | TRUTH TABLE OF THE CONTROL CIRCUIT. |      |

## LIST OF FIGURES

| FIGU | JRE PAGE                                                                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

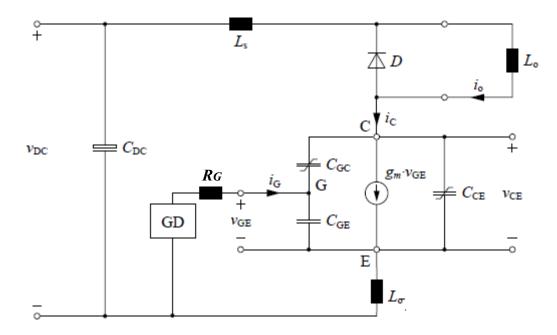

| 1.   | Equivalent circuit for the inductive load switching, including a simple IGBT model4                                                                                                                |

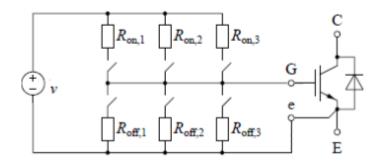

| 2.   | Simplified concept of switching transition control by controlling the gate resistance                                                                                                              |

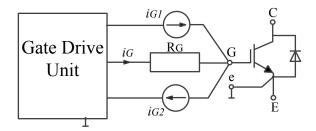

| 3.   | Simplified concept of switching transition control by controlling the gate current                                                                                                                 |

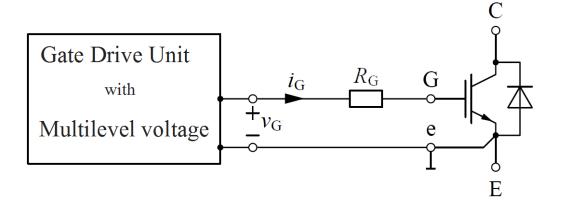

| 4.   | Simplified concept of switching transition control by controlling the voltage using event feedbacks                                                                                                |

| 5.   | Test circuit and control block diagram24                                                                                                                                                           |

| 6.   | Turn-off behavior of the MOSFET and control circuit key waveforms                                                                                                                                  |

| 7.   | Turn-on delay of OTPT vs. the optical power, using the resistive-load circuit                                                                                                                      |

| 8.   | Gate-to-Drain capacitance of M1 ( also known as Miller capacitance) as a function of drain-to-source voltage                                                                                       |

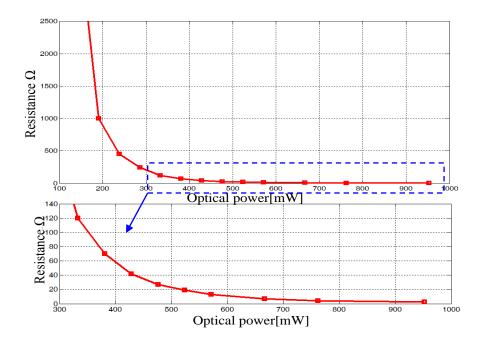

| 9.   | Resistance of OTPT vs. the optical power, using the resistive-load circuit of Fig 7 26                                                                                                             |

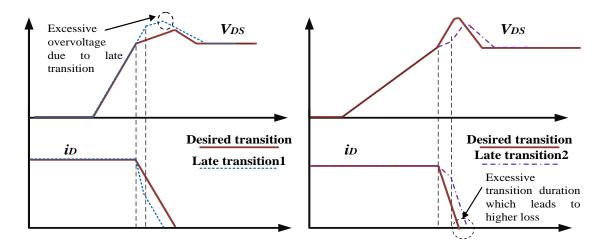

| 10.  | Effect of late transition between the $dv_{DS}/dt$ and $di_D/dt$ control regions on device stress<br>and switching loss                                                                            |

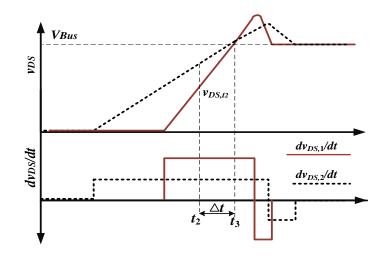

| 11.  | Signals $v_{DS}$ and $dv_{DS}/dt$ , at the desired time (t <sub>2</sub> ) of transition for two different $dv_{DS}/dt$ , considering the constant delay of $\Delta t$ seconds in the feedback loop |

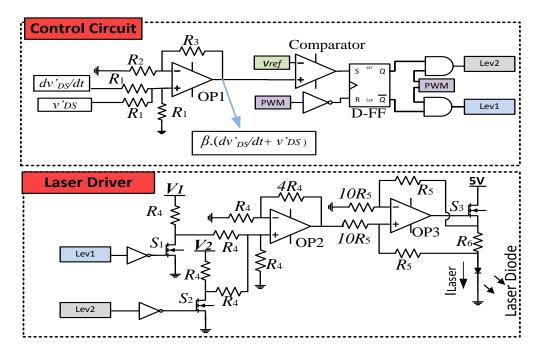

| 12.  | Schematics of the control circuit and the laser driver                                                                                                                                             |

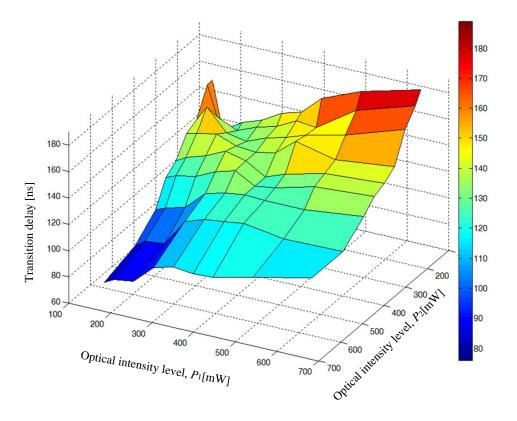

| 13.  | Measured transition delay of resistance of the OTPT when the optical intensity changes from $P_1$ to $P_2$                                                                                         |

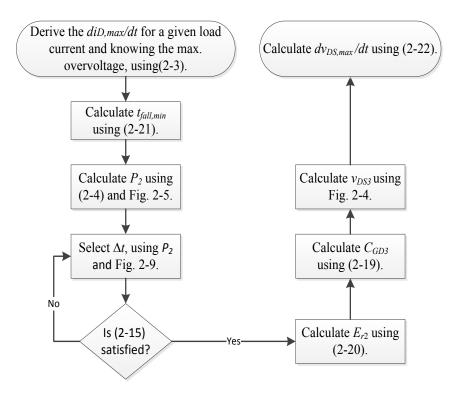

| 14.  | The flowchart of the procedure of calculating the quantitative boundaries of $dv_{DS}/dt$ and $di_D/dt$ for independent control of turn-off $dv_{DS}/dt$ and $di_D/dt$                             |

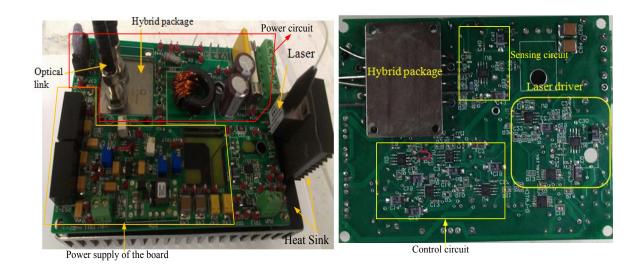

| 15.  | Fabricated test set up                                                                                                                                                                             |

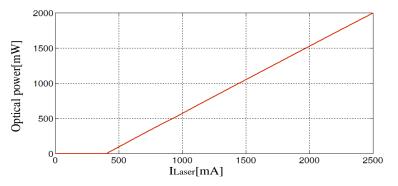

| 16.  | Output optical power of the laser at the end of the fiber-optic cable as a function of laser current(ILaser)                                                                                       |

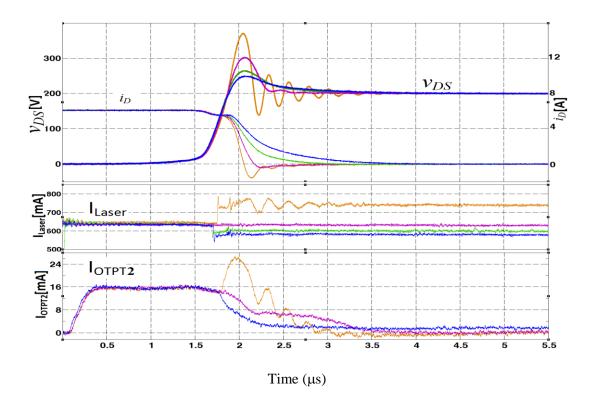

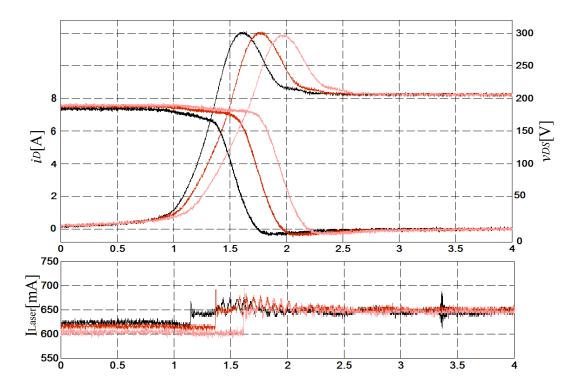

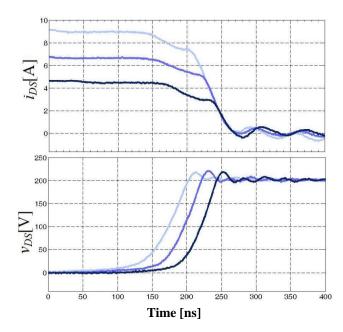

| 17.  | Measured turn-off waveform of $v_{DS}$ , $iD$ , $I_{Laser}$ , and $I_{OTPT2}$ with varied $di_D/dt$ and a fixed $dv_{DS}/dt$                                                                       |

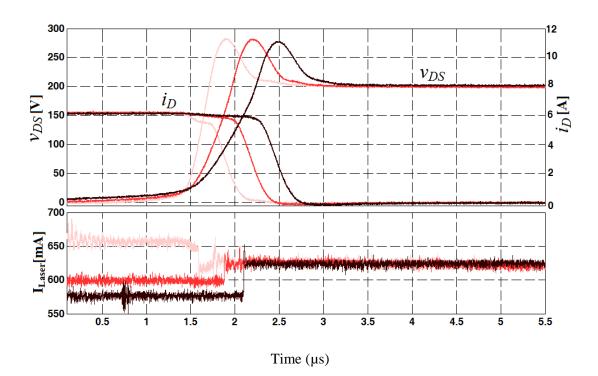

| 18.  | Measured turn-off waveforms of $v_{DS}$ , $i_D$ , and ILaser with varied $dv_{DS}/dt$ and a fixed $di_D/dt$                                                                                        |

## LIST OF FIGURES (Continued)

| 19. | Test circuit and control block diagram for the high-side drive case,                                                                                                        | 45 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 20. | Measured turn-off waveform of $v_{DS}$ , $i_D$ and $I_{Laser}$ with varied $di_D/dt$ and a fixed $dv_{DS}/dt$ for the high-side drive case.                                 | 45 |

| 21. | Measured turn-off waveforms of $v_{DS}$ , $i_D$ , and $I_{\text{Laser}}$ with varied $dv_{DS}/dt$ and a fixed $di_D/dt$ for the high-side drive case.                       |    |

| 22. | Measured turn-off waveform of $v_{DS}$ , $i_D$ , and $I_{Laser}$ for different bus voltages                                                                                 | 46 |

| 23. | Measured turn-off waveforms of $v_{DS}$ , $i_D$ , and $I_{Laser}$ for different load currents                                                                               | 47 |

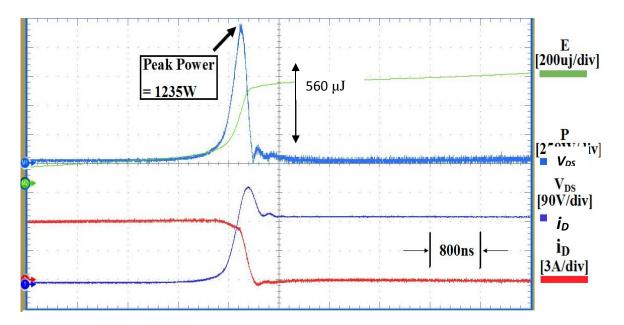

| 24. | Measured switching loss and energy for conventional approach [16] to driving the gate                                                                                       | 48 |

| 25. | Measured switching loss and energy for the proposed optical-transition controller                                                                                           | 48 |

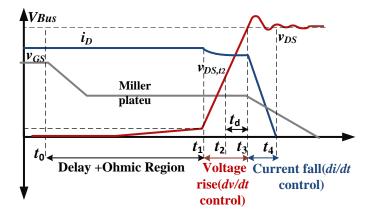

| 26. | Key waveforms of the MOSFET (M1) during turn-off                                                                                                                            | 53 |

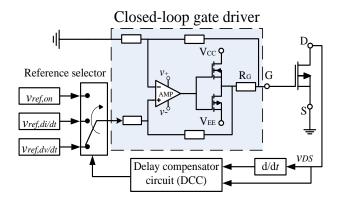

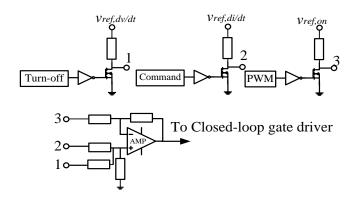

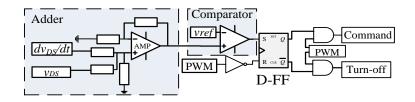

| 27. | Block diagram of the proposed control scheme                                                                                                                                | 53 |

| 28. | Schematic of the Reference selector circuit,                                                                                                                                | 53 |

| 29. | Schematic of the Delay compensator circuit (DCC)                                                                                                                            | 54 |

| 30. | Fabricated prototype of the proposed closed-loop active gate driver along with the clamped-inductive test circuit of Fig.26.                                                | 56 |

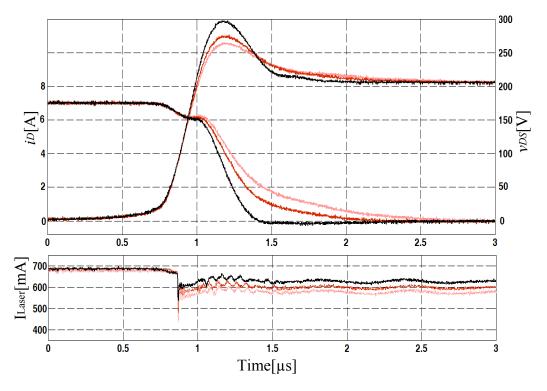

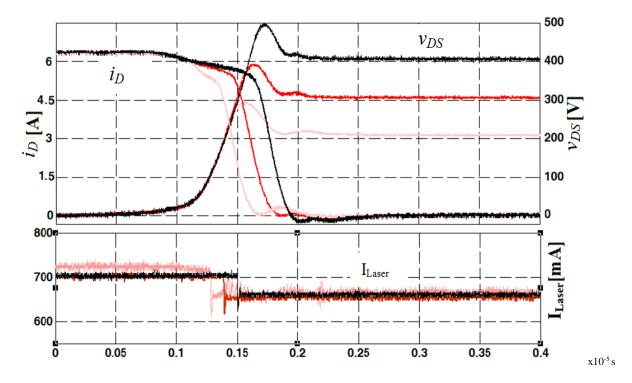

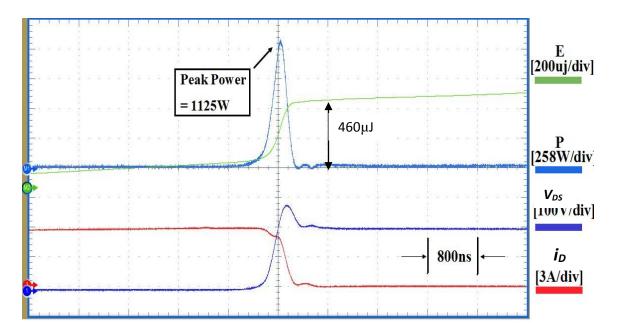

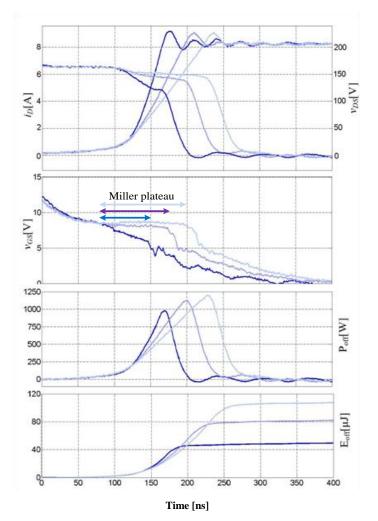

| 31. | Measured turn-on waveforms of $v_{DS}$ , $i_D$ and $v_{GS}$ along with the calculated values for Poff<br>and Eoff while the voltage slope varies and current slope is fixed | 57 |

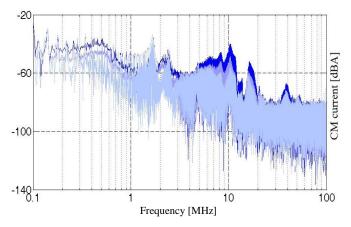

| 32. | Spectrum of the input CM current                                                                                                                                            | 57 |

| 33. | Measured turn-on waveforms of $v_{DS}$ , $i_D$ and $v_{GS}$ along with the calculated values for Poff<br>and Eoff while the current slope varies and voltage slope is fixed | 58 |

| 34. | Measured turn-off waveforms of $v_{DS}$ and $i_D$ for different load currents at $di_D/dt=100$ A/µs and $dv_{DS}/dt=3.75$ kV/µs,                                            | 59 |

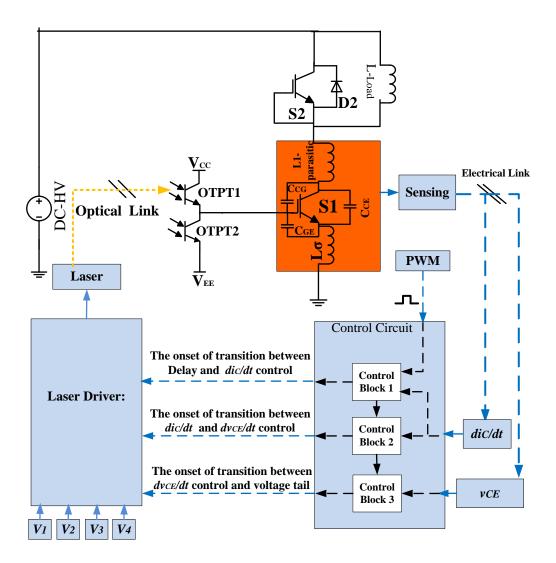

| 35. | Test circuit and control block diagram                                                                                                                                      | 64 |

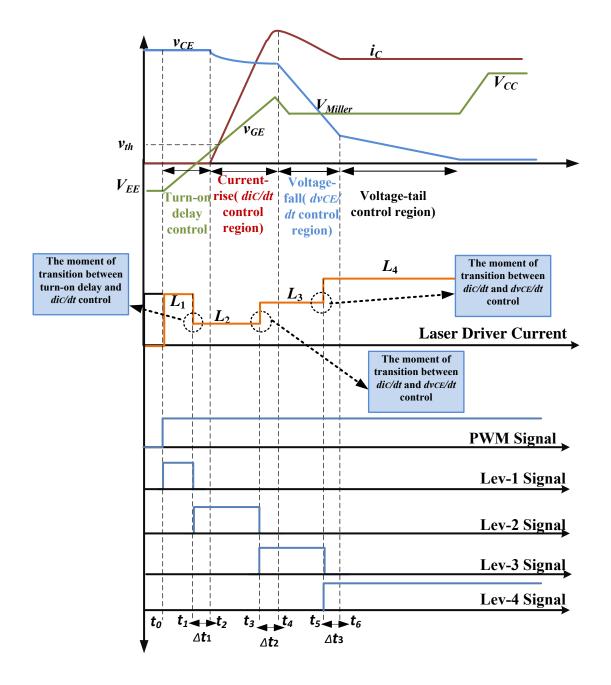

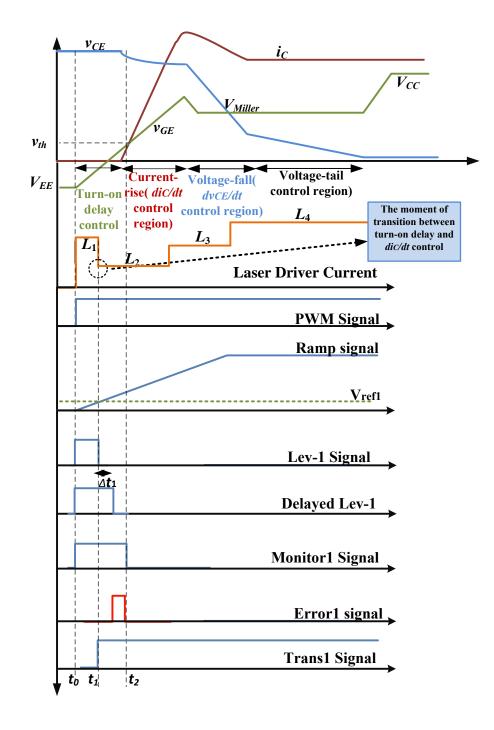

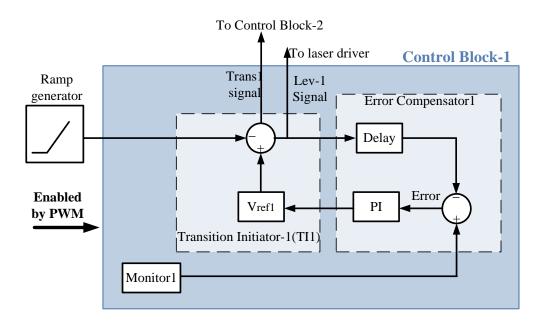

| 36. | Turn-on behavior of the IGBT and control circuit key waveforms                                                                                                              | 65 |

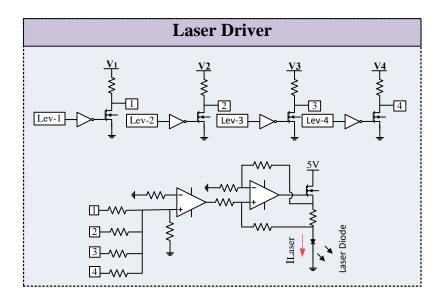

| 37. | Schematic of the Laser Driver circuit                                                                                                                                       | 69 |

| 38. | Turn-on behavior of the IGBT and Control Block-1 key waveforms.                                                                                                             | 70 |

## LIST OF FIGURES (Continued)

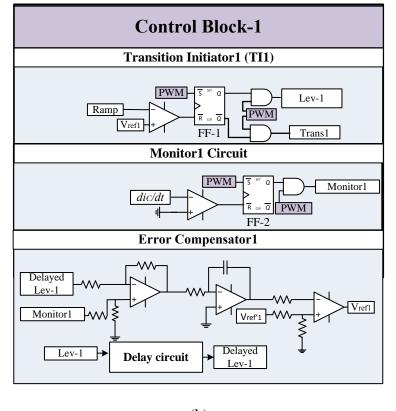

| 39. | Control Block1: (a) Block diagram, (b) schematic                                                                                                                                                                                                                                                                                             |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

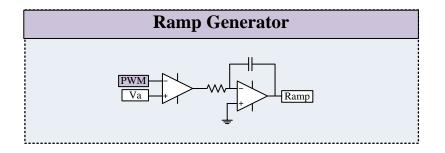

| 40. | Schematic of the Ramp Generator circuit. Ramp Generator circuit is a major component of each three control blocks                                                                                                                                                                                                                            |

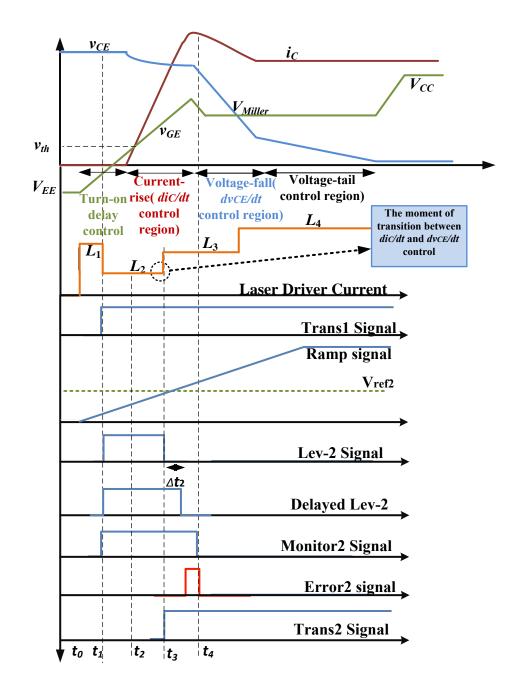

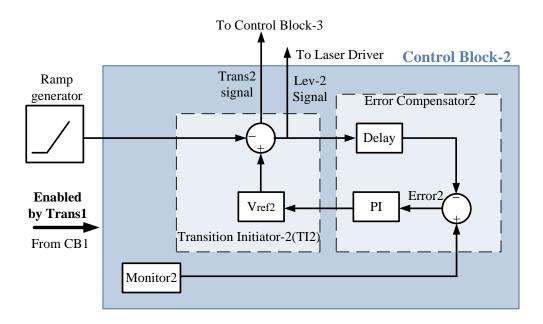

| 41. | Turn-on behavior of the IGBT and Control Block-2 key waveforms                                                                                                                                                                                                                                                                               |

| 42. | Control Block-2: (a) Block diagram, (b) Schematic                                                                                                                                                                                                                                                                                            |

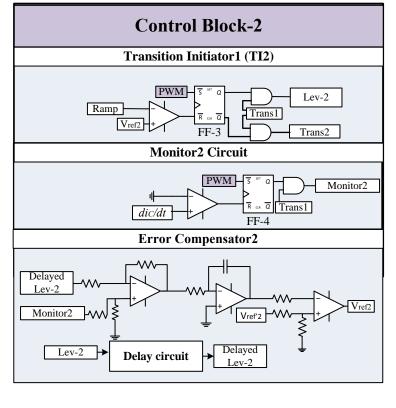

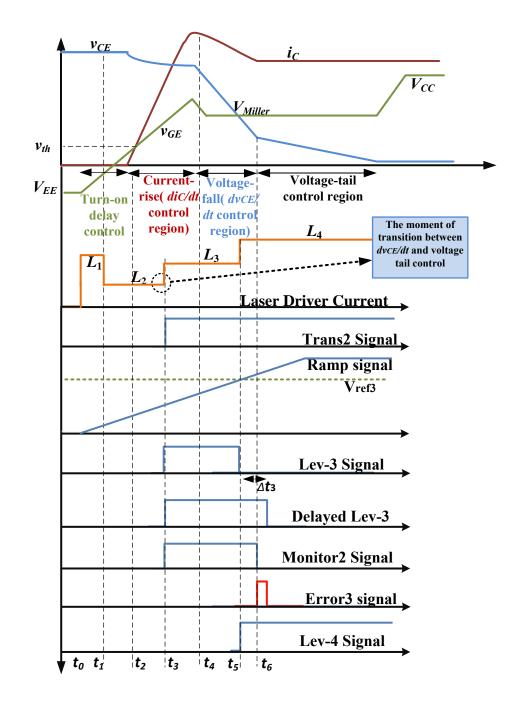

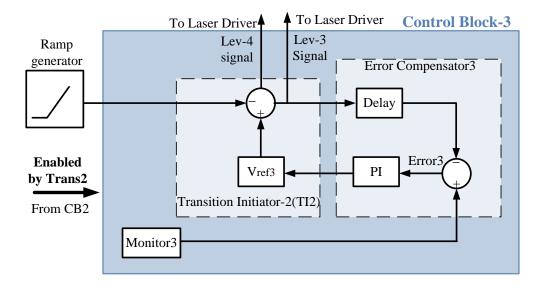

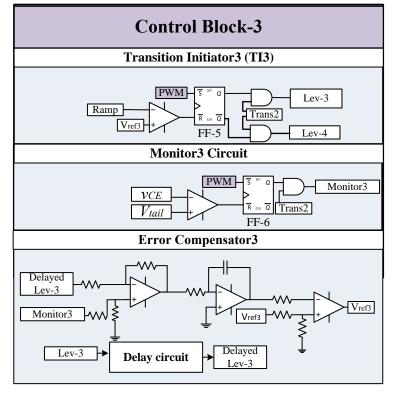

| 43. | Turn-on behavior of the IGBT and Control Block-3 key waveforms                                                                                                                                                                                                                                                                               |

| 44. | Control Block-3: (a) Block diagram, (b) Schematic                                                                                                                                                                                                                                                                                            |

| 45. | Fabricated prototype of the proposed control scheme with the clamped-inductive test circuit of Fig.4-1                                                                                                                                                                                                                                       |

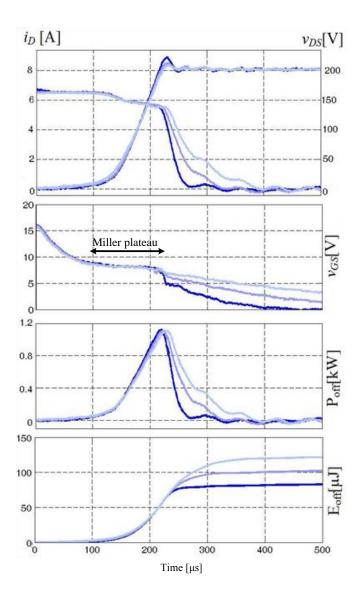

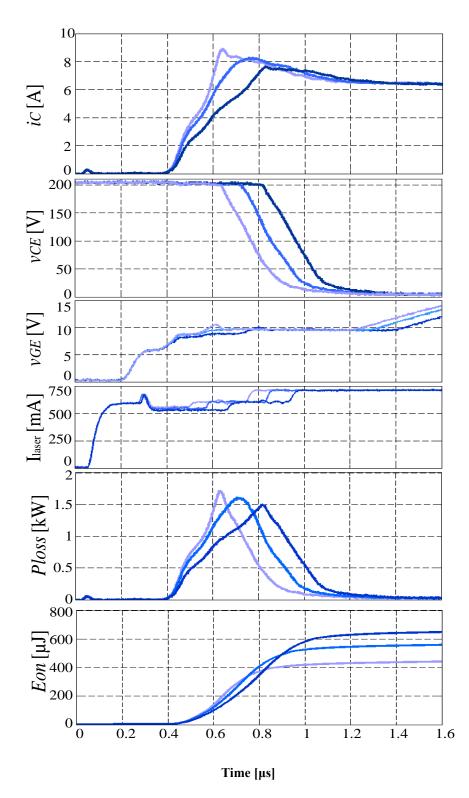

| 46. | Measured turn-on waveforms of $v_{CE}$ , $i_C$ , $v_{GE}$ and ILaser and calculated waveforms of instantaneous power loss(Ploss) and turn-on switching energy(Eon) with varied current slop ( $di_C/dt$ ) of 40A/µs, 26Aµs and 18A/µs while voltage slope ( $dv_{CE}/dt$ ) is fixed at 700v/µs and turn-on delay is fixed at 350ns           |

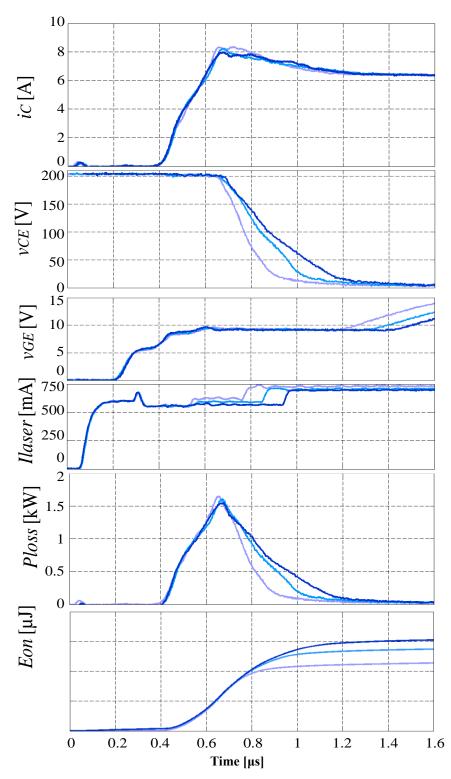

| 47. | Measured turn-on waveforms of $v_{CE}$ , $i_C$ , $v_{GE}$ and $I_{Laser}$ , and calculated waveforms of instantaneous power loss(Ploss) and turn-on switching energy(Eon) with varied voltage slope ( $dv_{CE}/dt$ ) of 850V/µs, 530V/µs and 320V/µs while current slop ( $di_C/dt$ ) is fixed at 32A/µs and turn-on delay is fixed at 350ns |

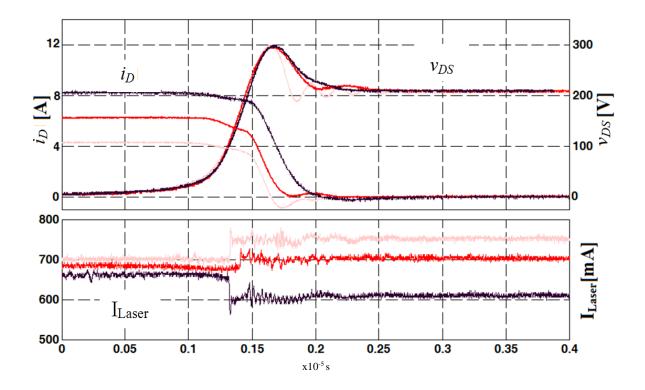

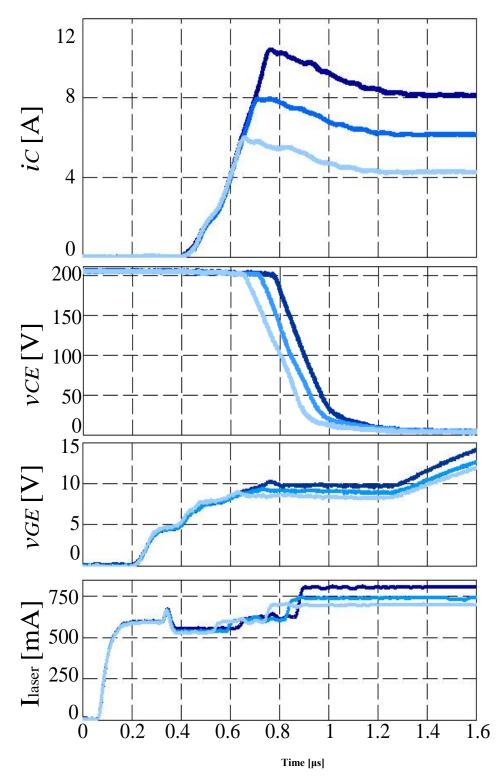

| 48. | Measured turn-on waveforms of $v_{CE}$ , $i_C$ , $v_{GE}$ and $I_{Laser}$ in the load current conditions of 4A, 6A, and 8A                                                                                                                                                                                                                   |

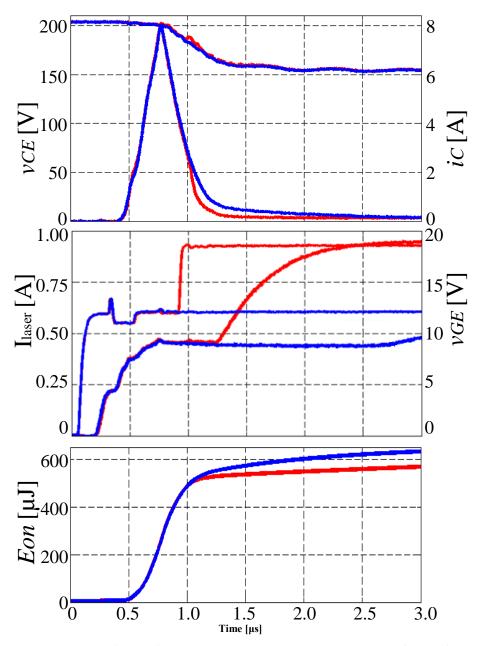

| 49. | Measured turn-on waveforms of $v_{CE}$ , $i_C$ , $v_{GE}$ and $I_{Laser}$ , and calculated waveforms of turn-<br>on switching energy(Eon) for the two cases of three-level and four -level control                                                                                                                                           |

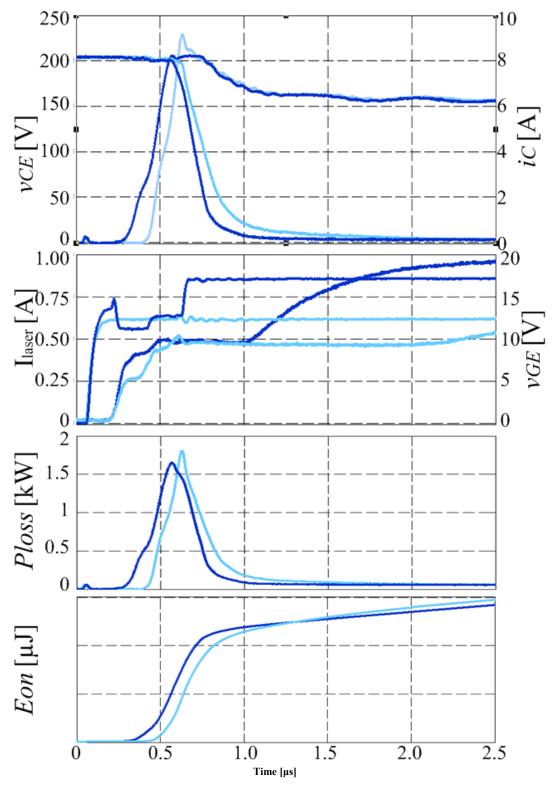

| 50. | Measured turn-on waveforms of $v_{CE}$ , $i_C$ , $v_{GE}$ and $I_{Laser}$ , and calculated waveforms of instantaneous power loss(Ploss) and turn-on switching energy(Eon) for proposed control method (light blue) and conventional fixed resistance method (dark blue)                                                                      |

# LIST OF ABBREVIATIONS

| PSD  | Power Semiconductor Device          |

|------|-------------------------------------|

| OTPT | Optically Switched Power Transistor |

| HF   | High Frequency                      |

| HV   | High Voltage                        |

| EMI  | Electro-magnetic Interference       |

| EMC  | Electro Magnetic Compatibility      |

| SMPS | Switched-mode Power Supply          |

| СМ   | Common Mode                         |

| DM   | Differential Mode                   |

| PWM  | Pulse Width Modulation              |

| ZCS  | Zero Current Switching              |

| ZVS  | Zero Voltage Switching              |

| ET   | Electrically Triggered              |

| ОТ   | Optically Triggered                 |

| PLL  | Phase-locked Loop                   |

#### SUMMARY

As the industry demands move toward more compact and high-power-density applications, it is desirable to increase the switching frequency of the power semiconductor devices (PSDs) to reduce the size and cost of the passive elements. On the other hand, increasing the switching frequency results in higher switching loss in PSDs. Therefore, voltage and current slopes during the switching transitions need to be increased to decrease the duration of the switching transition and switching loss. However, adverse current and voltage slopes during the switching transitions are the main sources of the noise, EMI issues and switching stress such as over current and overvoltage. Consequently, a solution to empower one to gain an optimal performance in terms of switching loss, device stress and EMI is desirable.

Several EMI and stress reduction techniques have been introduced in the literature to mitigate the undesirable affect of high *di/dt* and *dv/dt*. Those approaches include but not limited to: Active and passive clamps, snubber circuits, Active and passive EMI filters and soft switching techniques. The main drawbacks of the above-mentioned approaches are adding additional bulky and expensive passive and/or active devices to the power circuit, modification of the original topology and complexity of the control.

Active and passive gate drive (or switching transition control) techniques are used to control EMI, device stress and switching losses by shaping the current and voltage slopes of the switching transitions of a PSD. In contrast to previously mentioned EMI and stress reduction techniques, switching transition controllers are placed in the control and gate drive stages and do not need any change in the original topology of the power circuit. Active gate drive circuits are controlling the *di/dt* and/or *dv/dt* of turn-off and/or turn on switching transitions of PSDs to gain the optimal performance regarding EMI, device stress and switching losses. The main limitations of the state

#### **SUMMARY** (Continued)

of the art switching transition controllers are lack or limited adjustability of di/dt and dv/dt, and lack or limited ability to independently control di/dt, dv/dt and delay to gain an optimal performance in terms of loss, device stress and EMI.

This dissertation outlines novel optical-based and electrical-based switching transition controllers for insulated gate power semiconductor devices such Si and SiC MOSFETs and IGBTs. The main advantage of the proposed controllers is unified independent control of di/dt and dv/dt of turn-on and turn-off switching transition. This feature gives more degree freedom to designer in different applications to gain an optimal performance regarding the switching loss, device stress and EMI noise. The other unique feature of the optical-based controllers is using optical beam to trigger and control the switching transition of PSDs that reduces the susceptibility to the external noise.

Initially an optical-based two level switching transition controller is outlined. This controller is able to independently control the turn-off di/dt and dv/dt of the power MOSFETs by adjusting the optical intensity in each region of control. Independent controllability of turn-off dv/dt and di/dt is guaranteed by predicting the onset of transition between the regions of control considering the optical-to-electrical and circuit propagation delays. Subsequently, an electrical switching transition controller is presented for high speed SiC MOSFETs. This controller adjusts the di/dt and dv/dt of the turn-off switching transition by closed-loop control of the gate current. It independently control the very fast di/dt and dv/dt of the SiC MOSFET by predicting the onset of transition between dv/dt and di/dt control regions. Finally, an optical-based four-level switching transition controller is outlined that is able to independently control the delay, di/dt, dv/dt and voltage tail of the turn-on transition of the IGBTs. This controller comprises of three control

# SUMMARY (Continued)

blocks that predict the onset of transition between the four control regions. Each control parameter can be controlled individually by adjusting the optical intensity in that region.

### I. Introduction

Insulated gate power semiconductor devices (PSDs), such as IGBT and MOSFET, are widely used in hard-switched power electronics applications with a broad range of power rating and applied voltage. These hard-switched applications include switched mode power supplies (SMPS), motor drives, solar inverters, and battery chargers [1]-[4]. As the industry moves toward to higher frequencies to increase the power density, the switching loss increases. Therefore, it is desirable to increase the voltage and current slopes (dv/dt and di/dt) of the switching transition to decrease the switching loss. However, adverse voltage and current slopes cause excessive device stress and electro-magnetic interference (EMI) because of the parasitic elements of the PSD and power circuit.

International standards for electromagnetic compatibility (EMC) require power electronics converters to meet certain noise levels [5]-[8]. Furthermore, EMI noises may cause a malfunction in the control circuit of the power converter or other sensitive electronic devices. High dv/dt and di/dt during switching transition are the main sources of EMI in power electronics circuits. EMI noises generated by the power electronics converters are categorized as conducted and radiated noises [9]. Conducted noise is propagated through circuit wires and interconnections while radiated noise is spatially propagated. High dv/dt is the primary source of the common mode (CM) noise which causes a displacement current in the parasitic capacitances of the circuit. This displacement current causes imbalance and fluctuation of the reference ground as well as shortening the life of machine bearing and stator insulation[10]. On the other hand, high di/dt generates differential mode (DM) noise. High di/dt current loops in the circuit are also responsible for the radiated EMI [5]. Furthermore, high di/dt causes voltage overshoot at turn-off transition of

the PSD, because of parasitic and/or leakage inductances in the commutation path. Moreover, it generates current overshoot at turn-on transition due to reverse recovery action of the freewheeling diode.

Several EMI reduction techniques have been introduced in the literature. Active and passive snubber circuits are employed to reduce the voltage and current slopes and diminish the EMI noise and device stress. However, additional active and/or passive components are needed in the power stage. Additional components in the power stage usually increase the size, cost, complexity and loss of the circuit. [11],[12]. Active Clamp circuits are implemented to decrease the device overvoltage and consequent high-frequency ringing in the turn-off transition [13]. However, these approaches are ineffective when the CM-EMI-noise reduction is needed. Also, they require additional passive devices as well as additional active PSDs in the power stage. Needless to say that, additional gate drive stages and control circuits are needed to drive the additional PSDs. Another approach to decrease conducted EMI noise is using active and passive EMI filters [14], [15]. Similar to previous methods in [11]-[13], EMI filters usually decrease the power density and increase the volume and weight of the circuit. This drawback is because of using additional components in the power circuit, especially bulky and costly inductors. Moreover, EMI filters are incapable of decreasing the device stress. Soft switching techniques are interesting ways to decrease EMI noise as well as the device stress and switching loss [16],[17]. They are categorized as zero voltage switching (ZVS) and zero current switching (ZCS). However, the ZVS technique is usually not realizable in light loads in power electronic converters rather than resonant converters. Also, these techniques usually require modification in the power stage as well as the control techniques, which increases the size and cost of the circuit and make the control more difficult. Soft switching techniques are usually successful to mitigate the EMI

noise. However, employing soft switching techniques in some topologies does not lead to a significant reduction of EMI noise to meet the EMC standards [18], [19]. Other approaches like parasitic cancellation [20], interleaving [21], balance approach [22], grounding and shielding [5], [9]are also proposed in the literature. However, the main downsides of these EMI and stress reduction techniques that modify the power stage are: added passive and active power-rated components that increase the cost and weight and control complexity of the original hard-switched converter.

Active and passive gate drive (or switching transition control) techniques are used to control EMI, device stress and switching losses by shaping the current and voltage slopes of the switching transitions of a PSD. In contrast to previously mentioned EMI and stress reduction techniques that require modifications and/or additional devices in the power stage, switching transition controllers are placed in the control and gate drive stages and do not need any change in the original topology of the power circuit. Active gate drive circuits are controlling the di/dt and/or dv/dt of turn-off and/or turn on switching transitions of PSDs to gain the optimal performance regarding EMI, device stress and switching losses.

### A. Switching Transition Control of Insulated Gate PSDs

### 1. Inductive Load Switching of Insulated Gate PSDs

Most of the PSDs in the power electronics circuits are used under the inductive load. Fig. 1. shows the equivalent circuit of the clamped-inductive circuit using a simple IGBT model. Parasitic inductances of DC-link, Busbar and collector of the IGBT are summed and shown as  $L_s$ .  $L_{\sigma}$  corresponds the inductance seen from emitter terminal of the IGBT. Following we will derive the equations for the *di/dt* and *dv/dt* of the IGBTs in turn-on and turn-off transitions. It is noted

Fig. 1. Equivalent circuit of the clamped-inductive circuit using a simple IGBT model.

that, in the remaining paper, the terms dv/dt and di/dt are used to represent the rate of change of voltage across and the rate of change of current through a general PSD. While,  $dv_{DS}/dt$  and  $di_D/dt$  are used to represent the rate of change of voltage across and the rate of change of current through a power MOSFET, and  $dv_{ce}/dt$  and  $di_c/dt$  are used to represent the rate of change of voltage across and the rate of change of current through an IGBT.

Collector current and gate voltage of an IGBT are related by the following equation:

$$i_c = g_m \cdot v_{GE} \tag{1}$$

In (1),  $i_c$  is the collector current of the IGBT, while  $g_m$  is the forward transconductance of the IGBT and  $v_{GE}$  is the gate-to-emitter voltage of the IGBT. Therefore,  $di_c/dt$  is derived by the following relation:

$$\frac{di_c}{dt} = \frac{dv_{GE}}{dt} \cdot \left( g_m + v_{GE} \frac{dg_m}{dv_{GE}} \right)$$

(2)

Neglecting the term  $(v_{GE}. dv_{GE}/dg_m)$ ,  $di_c/dt$  can be approximated as:

$$\frac{di_c}{dt} = \frac{dv_{GE}}{dt}. g_m = \frac{i_G}{c_{GE}}. g_m \tag{3}$$

In (3),  $C_{GE}$  is the gate to emitter capacitance of the IGBT, and  $i_G$  is the gate current of the IGBT. Based on (1-3),  $di_c/dt$  can be controlled by adjusting the gate current. In the turn-off transition, gate current is derived by writing the KVL in the gate loop:

$$i_G = -\frac{\nu_{GE} + L_{\sigma}.(di_C/dt)}{R_G} \tag{4}$$

In (4),  $R_G$  is the gate resistance. The gate-to-emitter voltage of the IGBT is approximated using the following equation:

$$v_{GE} = v_{th} + i_c / g_m \tag{5}$$

In (5),  $v_{th}$  is the gate threshold voltage. Using (1-5) and (1-4) in (1-3), In (1-3),  $di_c/dt$  can be approximated using the following equation during the turn-off transition of IGBT:

$$\frac{di_c}{dt} \approx -\frac{(v_{th} + i_C/2.g_m)}{R_G.C_{GE}/g_m + L_\sigma}$$

(6)

In a similar manner the turn-off  $di_D/dt$  of power MOSFETs is expressed using the following equations:

$$\frac{di_D}{dt} = \frac{i_G}{C_{GS}} \cdot g_{fs} \tag{7}$$

$$\frac{di_D}{dt} \approx -\frac{(v_{th} + i_D/2.g_{fs})}{R_G.C_{GS}/g_{fs} + L_{\sigma}}$$

(8)

In (7),  $C_{GS}$  is the gate-to-source capacitance of the MOSFET, and  $g_{fs}$  is the forward transconductance of MOSFET. Similarly, the turn-on di/dt of IGBT and MOSFET are respectively derived in (9) and (10):

$$\frac{di_c}{dt} \approx \frac{v_G - (v_{th} + i_C/2.g_m)}{R_G.C_{GE}/g_m + L_\sigma}$$

(9)

$$\frac{di_D}{dt} \approx \frac{v_G - (v_{th} + i_D/2.g_{fs})}{R_G.C_{GS}/g_{fs} + L_\sigma}$$

(10)

The dv/dt of IGBT can be expressed by the following equation:

$$\frac{dv_{ce}}{dt} = -\frac{i_G}{c_{GC}} \tag{11}$$

In (11),  $C_{GC}$  is the gate-to-collector capacitance of the IGBT. In the inductive load switching of the IGBT, the current passing through IGBT is almost fixed during the voltage rise and voltage fall intervals. Therefore, one can neglect the term  $L_{\sigma}$ .  $(di_C/dt)$  in (4). Hence, the voltage slopes of the IGBT in turn-on and turn-off transitions are, respectively, shown by the following equations:

$$\frac{dv_{ce}}{dt} = -\frac{v_G - (v_{th} + i_c/g_m)}{c_{GC} R_G} = -\frac{v_G - V_{Miller}}{c_{GC} R_G}$$

(12)

$$\frac{dv_{ce}}{dt} = \frac{(v_{th} + i_c/g_m)}{c_{GC}R_G} = \frac{V_{Miller}}{c_{GC}R_G}$$

(13)

In (12) and (13),  $V_{Miller}$  is the Miller voltage. In the same manner, the voltage slopes of the MOSFET are, respectively, derived for turn-on and turn-off transitions as follows:

$$\frac{dv_{DS}}{dt} = -\frac{v_G - (v_{th} + i_D/g_{mfs})}{c_{GD}.R_G} = -\frac{v_G - V_{Miller}}{c_{GD}.R_G}$$

(14)

$$\frac{dv_{DS}}{dt} = \frac{(v_{th} + i_c/g_m)}{C_{GD}.R_G} = \frac{V_{Miller}}{C_{GD}.R_G} = \frac{i_G}{C_{GD}}$$

(15)

High di/dt at turn-off causes an overvoltage across the PSD. This overvoltage is because of the parasitic and/or leakage inductances in the commutation path. The amount of overvoltage is derived by the following relation:

$$\Delta v_{ov} = (L_{\sigma} + L_s) \cdot di/dt \tag{16}$$

The peak reverse-recovery current (IRR<sub>peak</sub>) of the free-wheeling diode (FWD) is also a function of the current slope, temperature (T) and load current( $I_{L0}$ ):

$$IRR_{Peak} = \left(\frac{di}{dt}\right)^{1/2} f(I_{L0}, T)$$

(17)

### 2. <u>Passive Gate Drives</u>

Passive gate drive techniques are using additional passive components in the gate drive circuit of a PSD. Commonly, they use an additional gate resistance or add an external capacitor in parallel to the gate-to-collector and/or gate-to-emitter parasitic capacitances of an IGBT (gate-to-drain and/or gate-to-source parasitic capacitances of a MOSFET). Increasing the gate resistance, decreases the voltage and current slopes and diminishes the EMI noise as well as device stress. However, it results in higher switching loss. Putting an additional capacitor in parallel with the Miller capacitance of a PSD, increases the total Miller capacitance. Therefore, the dv/dt of the switching transition and CM EMI noise decreases while there is no change in the di/dt. Although the method of increasing the gate resistance, but it imposes more device stress in turn-off transition. The higher device stress is because of the higher di/dt of this method that results in more voltage overshoot and/or high frequency oscillation due to parasitic inductances in the commutation path.

The *di/dt* can be limited by adding a capacitance in parallel to the gate-to-emitter capacitance of an IGBT [23]. However, the turn-on delay and gate driver losses are increased because of the larger amount of the gate-to-emitter capacitance.

Passive transition control techniques do not have any adjustability in the control of the dv/dt and di/dt. Therefore, dynamic optimization of the switching performance in terms of EMI, device stress and switching losses is not possible in the operating range of a PSD. Hence, Active gate drive techniques have been introduced in the literature to dynamically control the switching transition of a PSD. Active gate drive techniques are generally classified in three categories: controlling the gate resistance, controlling the gate voltage and controlling the gate current.

### 3. <u>Switching Transition Control by Controlling the Gate Resistance</u>

Simplified concept of switching transition control by controlling the resistance of the gate is shown in Fig. 2. Takizawa *et al.*[24], have employed switchable gate resistors to control the turnon and turn-off transition of an IGBT. As the turn-on command is received by the gate drive circuit, the gate is charged by maximum current through a low impedance path provided by two parallel resistors. Therefore, the turn-on delay is decreased. As soon as the collector current begins to rise, one of the resistors is taken out of the charging path. Hence, the gate resistance increases and *di/dt* and peak reverse recovery current decreases. At the end of the current rise interval and start of the voltage fall interval, the deactivated resistive path is activated again. Hence, the gate of the IGBT is charged by maximum current, dv/dt is increased and switching loss is decreased. The positive *di/dt* value is sensed by the gate driver and one of the resistive paths is deactivated just in the current rise interval. The same concept is implemented for the turn-off transition. The gate is charged by the maximum current through two parallel resistors in the turn-off off delay and voltage rise intervals. Afterwards, one of the resistive paths is deactivated during the current fall interval. As a result, the turn-on delay and di/dt are decreased while the dv/dt is increased. Consequently, the switching losses, EMI noise generated by high di/dt and peak overvoltage are all diminished. However, this method is not able to adjust the dv/dt and di/dt. Therefore, the optimal switching performance in terms of loss, EMI and device stress is not granted using the proposed methods in [24].

Fig. 2. Simplified concept of switching transition control by controlling the gate resistance

A similar concept has been used for the turn-off transition of the power MOSFETs in [25]. In this scheme, a low impedance path is provided for the discharging path of the gate of a power MOSFET during the turn-off delay and voltage rise intervals. This low impedance path decreases the turn-off delay and increases the turn-off dv/dt to decrease the turn-off switching losses. The drain current of the MOSFET falls when the voltage reaches the bus voltage. The low impedance path is deactivated using a delay circuit by the beginning of the current fall interval. Therefore, a higher resistance is placed in the discharging path of the gate of the MOSFET. Consequently, the turn-off di/dt and subsequent high frequency oscillation is decreased. As a result, the over voltage stress across the MOSFET and EMI noise generated by high di/dt are decreased. However, the presented approach in [25] also suffers from the lack of adjustability over the di/dt and dv/dt.

switching performance is suboptimal in entire operating range, except the designed operating point. This suboptimal performance is due to the fact that a change in the operating condition would result in an early or late change in the gate resistance. This may result in undesired overvoltage or excessive loss that will be thoroughly explained in chapter II.

A three stage gate driver for IGBTs is presented in [26]. In this gate driver, a resistor with a low resistance is placed in the charging path of the gate of the IGBT to reduce the turn-on delay. After the threshold voltage has been detected by the detection circuit, a resistor with a higher resistance is placed in the gate circuit to reduce the di/dt and peak reverse-recovery current. Afterwards, the resistance of the charging path of the gate is decreased again to reduce the Miller plateau and increase the dv/dt. The same three stage approach is used to decrease the di/dt and increase the dv/dt in the turn-off transition. However, one would face a significant error in detection of the different stages in case of changing in the operating conditions. The reason is that, the gate voltage is compared to a constant reference value to detect the gate threshold and Miller voltages which are respectively correspond to the start of the current rise and voltage fall regions. However, the threshold voltage of the gate and Miller voltage are respectively dependent on the temperature and load current and may change significantly.

The main drawback of the active gate drive techniques which control the resistance of the gate is the lack of adjustability of the switching di/dt and dv/dt. Another drawback of these methods is imprecise detection of the di/dt and dv/dt control regions. The lack of adjustability and imprecise detection, results in the suboptimal switching performance of the PSD over the operating range.

#### 4. <u>Switching Transition Control by Controlling the Gate Current</u>

Simplified concept of switching transition control by controlling the gate current is shown in Fig. 3. In these control methods that are based on controlling the gate current, additional current is injected or taken out from the gate of the PSDs in selected transition intervals. Controlling the gate current have employed in [27] and [28] to control the turn-off transition of IGBTs. In this method, a high value gate resistance is chosen and placed in the gate charging path of the IGBT. The value of the gate resistance is selected such that the turn-on di/dt and reverse recovery current are decreased. Therefore, the device stress and EMI are also diminished in the current rise interval. When the collector current reaches it maximum value, the gate drive circuit injects an additional current to the gate of the IGBT in the voltage fall interval. The voltage fall interval is followed in series with the current rise interval and begins when the collector current reaches it maximum value. The injected current to the gate of the IGBT, results in a higher dv/dt which shrinks the voltage fall duration and decreases the switching loss. The moment at which an additional current is injected to the gate of the IGBT is initiated using a delay circuit. However, this delay is not self adjusted and needs to be tuned in case of changing in the operating condition. Furthermore, the di/dt and dv/dt during the turn-on transition are not adjustable. Therefore, the optimal performance is not attainable over the operating range of the device, since the driver can only be tuned for one operating point which is usually the nominal operating condition. This method is further improved in [29], [30], to solve the delay problem, using a phase-locked-loop (PLL) circuit to detect the Miller plateau.

Fig. 3. Simplified concept of switching transition control by controlling the gate current.

A three stage drive concept similar to [26] has been proposed in [31], [32]. The only difference is the adjustability of the di/dt in the current rise and current fall intervals which is not possible in [26]. Similar to [26], the gate is charged by maximum current to reduce the turn-on delay. Unlike [26], the charging current of the gate of the IGBT is adjusted during the current rise interval of the IGBT using a controllable current source. Adjustability of the di/dt enables one to control the EMI noise and peak reverse recovery current over the operating range of the device. After the current rise interval has ended, the instant of the voltage fall is detected using parasitic inductance of the Kelvin emitter of the IGBT. Afterwards, the gate is charged by maximum current to increase the dv/dt and decrease the switching loss. In the turn-off transition, initially the gate is discharged by maximum current to reduce the turn-off delay. Gate current is then controlled during the voltage rise and current fall stages. Although, this approach offers controllability over di/dt at turn-on and turn-off transitions, the dv/dt is not adjustable. Moreover, the value of the dv/dt is dependent on the value of the di/dt in the turn-off transition.

References [33] and [34] have implemented two active gate drive circuits to control the switching transition of an IGBT during turn-on and turn-off transitions. At turn-on transition, the gate is charged by the conventional gate current, and additional current is injected to the gate of the IGBT during the turn-on delay and voltage fall intervals. This additional current is provided by an additional path. High gate current at these intervals decreases the turn-on delay as well as

the turn-on switching loss. The additional current path is deactivated during the current fall interval by sensing the generated voltage over the parasitic inductance of the Kelvin emitter of the IGBT. Therefore, the di/dt, peak reverse recovery current and EMI are decreased while switching loss and turn-on delay are mitigated. A similar concept has been implemented to control the turn-off switching transition. Similarly, the gate is discharged by maximum current through the conventional path and an additional current path, during the turn-off delay and voltage rise intervals. Discharging the gate by the maximum current, decreases the turn on delay and switching loss. The additional discharging path is then deactivated during the current fall interval to decrease the turn-off overvoltage and EMI noise. The falling instant of the collector current is detected by sensing the overvoltage across the parasitic inductance of the Kelvin emitter of the IGBT. However, di/dt and dv/dt cannot be adjusted using the presented approaches in [33], [34]. Therefore, the optimal performance in terms of the EMI noise, switching loss and device stress is not granted.

Similar approaches as [33] are proposed in [35]-[37] to control the turn-off switching transition of power MOSFETs. Similar to [33], the gate is discharged by the maximum current during the turn-off delay and voltage rise intervals. The high rate of the discharging of the gate, results in a lower turn-on delay and lower switching loss due to the higher rate of the dv/dt. During the current fall interval, an additional current is injected to the gate of the MOSFET that results in a lower di/dt and overvoltage during this interval. Although the di/dt is not adjustable using [35] and [36], it is adjustable using the proposed approach in [37]. The reason is that the injected current to the gate of the MOSFET is controllable using the proposed approach in [37]. However, all of the methods in [35]-[37] do not have any controllability over the dv/dt.

Closed-loop active-gate-drive circuits are proposed in [38], [39] to control the switching transition of an IGBT. In these references, four current-source circuits are implemented to adjust the dv/dt and di/dt in turn-on and turn-off transitions of an IGBT. The dv/dt is adjusted by a current-mirror circuit which controls the gate current using a feedback current. This feedback current is proportional to the dv/dt of IGBT. The feedback current is provided by an external capacitor in parallel with the Miller capacitance of the IGBT. These dv/dt control circuits are only activated when the voltage gradient is present over the collector and emitter terminals of an IGBT. Similarly, the voltage drop over the parasitic inductance of the Kelvin emitter of the IGBT is used as a feedback signal for the di/dt control circuits. The current source circuits use the feedback signal to accordingly adjust the gate current and thus control the di/dt in the turn-on and turn-off transitions. Although the full adjustability of di/dt and dv/dt is possible using the proposed circuits in [38], [39], four individual circuits are needed to control the di/dt and dv/dt in turn-on and turnoff transitions. A similar approach is used to adjust the dv/dt of the switching transition of an IGBT, [40]. However, using the presented approach in [40], only one circuit is needed for dv/dtcontrol of both turn-on and turn-off transitions.

### 5. <u>Switching Transition Control by Controlling the Gate Voltage</u>

Most of the active-gate-drive methods based on controlling the gate voltage either use an event feedback to change the gate voltage or dynamically control the transition performance using the closed loop feedback of di/dt and/or dv/dt. However, Grbovic [41] proposed an IGBT gate driver based on the open-loop control of the gate voltage to control the turn-on switching performance. The di/dt is adjusted by controlling the slope of the gate-emitter voltage using a voltage shape generator. Afterwards, maximum voltage is applied to the gate circuit to shrink the Miller plateau and increase the dv/dt. Therefore, not only the peak reverse recovery current is

controlled using the voltage shape generator, but also the switching loss is decreased by decreasing the voltage fall duration. However, the controllability of the voltage slope is limited using this approach.

Simplified concept of the active gate drive by means of controlling the gate voltage is shown in Fig. 4. In this concept the gate of an insulated gate PSD is subject to a multi level voltage. Each level is adjusted such that the desired switching performance is achieved. The duration of each level is also adjusted by event feedbacks. An active gate drive circuit to control the turn-on di/dt and turn-off dv/dt of IGBTs is proposed in [42]. In this approach, an intermediate voltage level, which is less than the maximum applied voltage and greater than the threshold voltage of the IGBT, is applied to the gate of the IGBT during the current rise interval in the turnon transition. Therefore, the slope of the collector-to-emitter current of the IGBT is adjusted using the intermediate voltage level. As a result, the peak reverse recovery current is controlled. By the end of the reverse recovery period, the control circuit applies the maximum voltage to the gate of the IGBT to charge the gate-to-emitter capacitance with the maximum current. Hence, the voltage fall duration as well as the turn-on losses is decreased. However, the controllability over the turnon dv/dt is limited. During the voltage rise and current fall intervals of the turn-off transition, an intermediate voltage is applied to the gate of the IGBT during. This intermediate voltage is less than the gate threshold voltage. As a result, the di/dt is reduced. Although, the turn-off delay and voltage overshoot are decreased using this approach, the switching loss is increased. The reason is lack of independent controllability of di/dt and dv/dt which results in a reduced rate of fall of the collector-to-emitter voltage.

Fig. 4. Simplified concept of switching transition control by controlling the voltage using event feedbacks.

Closed loop gate drive circuits are proposed in [43]-[45] which control the di/dt of turn-on and turn-off transitions. The di/dt generates voltage across the parasitic inductance of the Kelvin emitter of the IGBT. This voltage is sensed and compared to a reference value and error is fed to an amplifier and buffer stage to regulate the desired di/dt. It has been shown that the proposed approaches can control the peak reverse recovery in turn-on and voltage overshoot in turn-off transitions by adjusting the di/dt. However, the dv/dt is not controllable by the proposed approach in [43]-[45].

In reference [46], an open-loop gate driver similar to [42] is presented to control the turnoff di/dt of the IGBTs. The idea of [46] is to apply a pulse voltage with duration of  $t_p$  to the gate of the IGBT in the current fall region to decrease the di/dt and consequent voltage overshoot and high-frequency oscillations. However, the fundamental parameter of the pulse such as  $t_p$  and the time at which the pulse begins has to be adjusted manually. Therefore, the optimal performance of the IGBT is limited. Moreover, there is no controllability over dv/dt.

A closed loop gate driver which controls the turn-off transition of IGBTs has been proposed in [47]. This gate driver controls the voltage gradient across the collector-to-emitter terminals of IGBTs using the feedback of the collector-to-emitter voltage. The collector-toemitter voltage is sensed and compared to a reference ramp signal. The error is then fed to an opamp and buffer stages to drive the gate of the IGBT. However, because of the shape of the reference ramp, the actual dv/dt has some deviation from the reference ramp, especially in low amount of voltages. The reason is that, when the reference ramp begins to rise, the controller should initially discharge the gate of the IGBT and the voltage gradient does not occur across the collector-to-emitter terminals of the IGBT until the gate voltage reaches the Miller plateau. To compensate this drawback, authors have changed the ramp signal and added a primary step prior to the ramp in the reference voltage [48], [49]. This step allows the gate of the IGBT to discharge to the Miller plateau level. Therefore, the IGBT is ready to follow the reference ramp as soon as it begins. However, generating the reference signal is quite difficult using the analog circuits. Although, the dv/dt follows the reference voltage using the above mentioned approaches and voltage overshoot is decreased, the dv/dt cannot be adjusted to a different value without changing the circuit components. Furthermore, the controllability over the turn-off di/dt and voltage overshoot is limited. Moreover, additional switching losses are incurred because of the initial step of the reference voltage. This method is then improved in [50], in which a field programmable gate array (FPGA) is used to dynamically adjust the duration of the initial step of the reference voltage and its voltage slope based on the feedback signals. Therefore, adjustable dv/dt is achieved, and an excessive loss due to the initial step in the reference voltage is decreased. The presented work in [48] is also evolved in [51]-[52] by adding analog feedback loops of the voltage gradient and gate voltage. These additional feedback loops decrease the undesired effect of the initial step of the reference voltage and increases the stability of the control loop. Also, authors have employed two different step levels of the reference voltage in [53]-[54] instead of a single step level in [48], to minimize the undesired effect of the initial step of the reference voltage.

Lobsiger and Kolar [55], have presented a closed-loop gate driver to dynamically control the di/dt and dv/dt of the switching transitions of the IGBTs. Two feedback loops and a proportional-integral (PI) stage are used to control the switching transition in this method. Feedback loops consist of a di/dt feedback loop and a dv/dt feedback loop. The di/dt feedback loop is deactivated using a clipping circuit in the dv/dt control region and vice versa. The di/dtand dv/dt are individually controlled by a reference voltage and circuit-dependent feedback gains. However, using the same reference voltage for both di/dt and dv/dt along with the constant feedback gains in each switching-transition period makes it difficult to adjust dv/dtwithout bounding adjustability of di/dt and vice-versa.

Closed-loop digital control of the slope of the collector-to-emitter voltage and collector current of the IGBTs is developed in [56],[57]. In this approach, the collector current, collector-to-emitter voltage and gate voltage of the IGBT are sampled using the Analog to digital (A/D) converters. The sampled data is then fed to an FPGA in which the data is processed, and the desired output is generated based on the different states of the switching transition. The generated output is then fed to a digital to analog (D/A) converter followed by a buffer stage to provide the desired current level with the specified duration for the gate of the IGBT. Therefore, the complete control of the switching transition is attained. Because of the large transition delays of the A/D and D/A conversion of the feedback signals, the output command, and required time for processing the data using the FPGA, the real-time control of the switching transition is only attainable for transitions slower than few microseconds. Therefore, iterative and adaptive approaches are implemented to control the switching transition in the next cycles based on the

provided data from the previous cycles. However, the accurate control is not granted for a significant change in the operating condition which affects the subsequent switching transitions. The other drawbacks are the limitation in the bandwidth of the sensing of the feedback signals and generating the output signal which bounds the accuracy of the control.

#### **B.** Motivation and Objective of Doctoral Research

As outlined in the previous sections, the high frequency requirement of modern power electronics applications requires reducing the switching loss and increasing the power density. This is achieved through increasing the voltage and current slopes of PSDs in the switching transition. On the other hand, the high dv/dt and di/dt in the switching transitions generate voltage and current overshoot as well as conducted and radiated noise. Therefore, several power stage solutions are presented in the literature to decrease the device stress and EMI noise. Power stage solutions require modification in the original topology and/or adding active and/or passive components. Therefore, the total cost and size of the system increases. Furthermore, control of the power electronics converter may become more complicated. Hence, active gate drive solutions are introduced to optimally control the switching transition in terms of losses, device stress and EMI by shaping the switching transition using the gate drive circuits. Active gate drive solutions are divided into three categories: controlling the gate resistance, controlling the gate voltage and controlling the gate current. Because of intertwined nature of the switching *di/dt* and dv/dt, the independent controllability over the dv/dt and di/dt is not realized in most of the active gate drive methods.

Although controlling the switching transitions of electrically-triggered (ET) PSDs has been explored, limited work has been conducted on the switching-transition control of optically-

triggered (OT) PSDs. Recent work on monolithic and hybrid OT PSDs [58]-[63] have demonstrated the feasibility of using a single optical link for both pulse-width-modulation (PWM) and switching-transition control of a PSD using a controller, which is spatially separated from the PSD power stage. The direct optical link precludes the possibility of signal corruption by external EMI. However, the optical-to-electrical conversion delay is appreciable as compared to the total duration of the switching transition which adversely affects the performance of the transition controller with feedback [61],[62].

This doctoral dissertation outlines the turn-off switching-transition control of an OT hybrid PSD in chapter 2. The OT hybrid PSD comprises two GaAs-based OTPTs and a SiC MOSFET. The outlined mechanism for optical control can be extended to Si power MOSFETs as well because of similarities in device behavioral dynamics [64],[65].. The OTPTs are placed in the charging (turn-on) and discharging (turn-off) paths of the gate of the SiC MOSFET. Unified turn-off dv/dt and di/dt control are achieved using a single circuit by modulating the intensity of the optical beam that triggers the OTPT, which controls the turn-off of the SiC MOSFET. A laser driver is designed to dynamically adjust the optical intensities for dv/dt and di/dt control. The independent control of turn-off dv/dt and di/dt is achieved by means of a control circuit which compensates for the total delay in the control loop. It also predicts the moment of transition between dv/dt and di/dt regions of control. The experimental results are also provided in chapter II. It is shown that the controller can independently control the turn-off dv/dt and di/dt in different load currents and applied voltages. Chapter 3 presents a novel closedloop active-gate-control (AGC) circuit for high-voltage SiC MOSFETs, used in the high-voltage, high-frequency and high-power-density applications. The proposed controller independently adjusts the switching di/dt and dv/dt by closed-loop control of the gate current and enables one to

reach optimal performance in terms of loss, device stress, and EMI. The di/dt is adjusted to control the overvoltage stress and peak reverse recovery current while the dv/dt is adjusted to control the common mode (CM) noise and switching loss. The dv/dt is the primary source of the common mode noise in power electronics converters. Dynamic control of switching dv/dt has been somewhat overlooked in the state-of-the art works based on Si based power semiconductor devices (PSDs), and maximum achievable dv/dt is used to decrease the switching loss. However, the magnitude of generated dv/dt in the high-voltage SiC-based applications is appreciable because of the exceptionally higher switching speed of the SiC MOSFETs as compared to Si IGBTs. In contrast to other works, the proposed controller dynamically and independently controls the turn-off di/dt and dv/dt of a SiC MOSFET using closed-loop control of the gate current. Independent control of turn-off di/dt and dv/dt is achieved using a delay compensation circuit. This circuit compensates the total delay in the feedback loop and predicts the onset of transition between dv/dt and di/dt control regions. The proposed control circuit operation and advantages are presented and verified by experimental results in chapter 3.

Chapter 4 presents the turn-on switching-transition control of an OT IGBT. The IGBT is triggered by two GaAs-based OTPTs. Switching dynamics of IGBT is controlled by modulating the optical intensity to the base of OTPT using a laser driver. Turn-on transition control adjusts the turn-on delay such that the switching transition control has minimum effect on the PWM modulation of the converter. It also decreases the overshoot of the turn-on current that is generated by reverse-recovery current (IRR) of the free-wheeling diode (FWD) due to high di/dtduring turn-on. Moreover, it adjusts the turn-on dv/dt to control the switching loss and electromagnetic interference (EMI) while keeps the PSD in the safe-operating area. Additionally it reduces the voltage tail and associated switching loss by detecting the voltage tail and increasing the optical intensity in that region. In contrast to other works, the proposed control method independently adjusts the turn-on delay, *di/dt* and *dv/dt* and reduces the voltage tail in different operating conditions. The onset of transition between delay, *di/dt*, *dv/dt* and voltage-tail control regions is determined using a self-contained control circuit [75]. The control circuit generates a command that initiates the transition between the two control regions. This command is then delayed to account for the total delay in the OTPT and feedback loop. Subsequently, the actual onset of transition is sensed, and the error between the delayed command and actual onset of transition is compensated using a PI compensator. The proposed control circuit operation and advantages are presented and verified by experimental results.

# II. Optically-switched-drive Based Unified Independent dv/dt and di/dt Control for Turn-off Switching Transition of Power MOSFETs

(Parts of this section, including figures and text, are based on my paper [73], ©2015 IEEE)

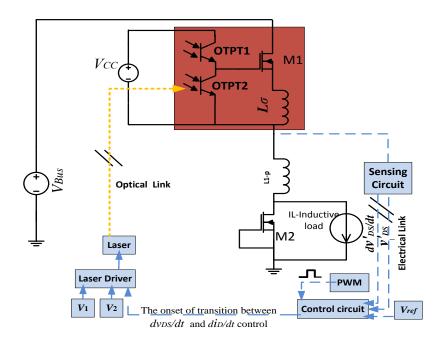

### A. Turn-off Transition Behavior and General Control Scheme

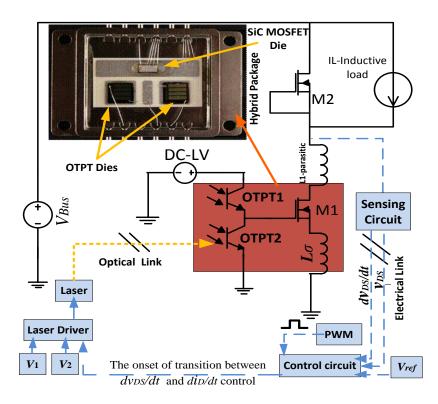

The standard clamped-inductive test circuit and control block diagram for optical transition control are shown in Fig. 5. The test circuit comprises a bridge leg with the hybrid device package (comprising M1 and the two OTPTs) placed in the low side and a self-gated SiC MOSFET (M2) in the high side. MOSFET M2 has characteristics similar to the characteristics of the SiC MOSFET in the hybrid package. OTPT1 and OTPT2 work complementarily and turn the SiC MOSFET (M1) on and off, respectively.

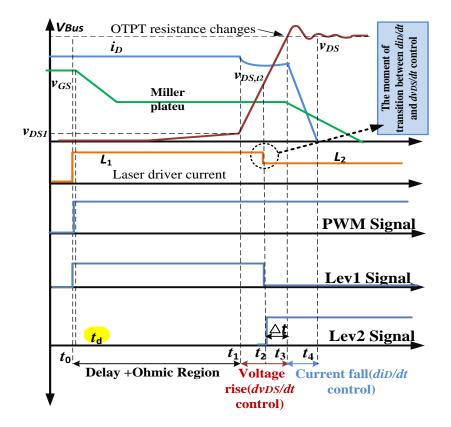

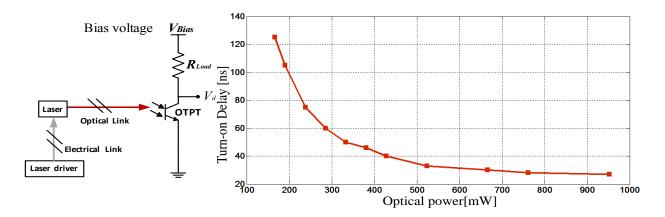

As indicated in Fig. 6, when the turn-off command is initiated by the PWM signal at  $t_0$ , the laser driver provides the current level  $L_1$  (proportional to the external voltage control command  $V_1$  shown in Fig. 5) for the laser with its wavelength centered at 808 nm. The laser delivers an optical power corresponding to the current level  $L_1$  to the base region of the OTPT2 via an optical link. OTPT2 then turns-on, after some delay, at  $t_d$ , allowing the gate charge of M1 to be discharged through it. The turn-on delay of OTPT as a function of optical power has been measured using the resistive circuit of Fig. 2-7 employing the point to point method. The results are then plotted in Fig. 7. The higher optical intensity results in smaller turn-on delay due to the higher rate of photo-generated carrier density inside the OTPT as shown in Fig. 7. More information about the characteristics and behavior of OTPT is provided in [67],[68].. After the OTPT is turned on, the gate-to-source voltage ( $v_{GS}$ ) of M1 starts to fall until it reaches the Miller

24

plateau voltage ( $V_{Miller}$ ); subsequently, the drain-to-source voltage ( $v_{DS}$ ) of M1 begins to rise. The slope of  $v_{DS}$  is approximated using the following relation:

Fig. 5: Test circuit and control block diagram. V1 and V2, respectively, control  $dv_{DS}/dt$  and  $di_D/dt$  of M1 in the  $dv_{DS}/dt$  - and  $di_D/dt$  -control regions of operation as illustrated in Fig. 2. The threshold condition, for the onset of transition between the  $dv_{DS}/dt$  and the  $di_D/dt$  -control regions, is provided in Section II-A-1, ©2015 IEEE.

$$dv_{DS}/dt \approx \frac{v_{GS,TH} + i_D/g_{fS}}{R_G C_{GD}} = \frac{V_{Miller}}{R_G C_{GD}}.$$

(1)

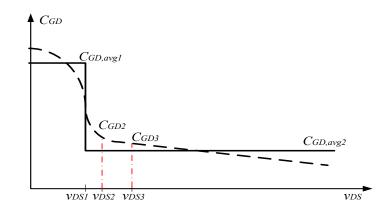

In (1),  $g_{fs}$  is the forward transconductance of M1,  $i_D$  is the drain current,  $C_{GD}$  is the gate-to-drain capacitance of M1 also known as Miller capacitance,  $R_G$  is the gate resistance, and  $v_{GS,TH}$  is the threshold voltage of M1. However, the gate-to-drain capacitance of MOSFETs is a nonlinear function of  $v_{DS}$ .  $C_{GD}$  of M1 is approximated as a two-step function of drain-to-source voltage of M1 as shown in Fig. 8:

$$C_{GD} = \begin{cases} C_{GD,avg1} & ; v_{DS} < v_{DS1} \\ C_{GD,avg2} & ; v_{DS} \ge v_{DS1} \end{cases}$$

(2)

Fig. 6: Turn-off behavior of the MOSFET and control circuit key waveforms. The output currents  $L_1$  and  $L_2$  of the laser driver are proportional to the voltage commands  $V_1$  and  $V_2$ , which dictate the  $dv_{DS}/dt$  and  $di_D/dt$  dynamics of M1 in the  $dv_{DS}/dt$  and  $di_D/dt$  control regions, ©2015 IEEE.

Fig. 7: Turn-on delay of OTPT vs. the optical power, using the resistive-load circuit.  $V_{Bias}$ = 10V,  $R_{Load}$ =200 $\Omega$ , frequency=50kHz and duty cycle=50%, ©2015 IEEE.

Fig. 8: Gate-to-Drain capacitance of M1 (also known as Miller capacitance) as a function of drain-to-source voltage, ©2015 IEEE.

Fig. 9: Resistance of OTPT vs. the optical power, using the resistive-load circuit of Fig 7, ©2015 IEEE.

Equation (2) is mostly true for other types of power MOSFETs and even IGBTs, as well[ [41]. Typically,  $C_{GD,avg1}$  is dramatically higher than  $C_{GD,avg2}$ . Therefore, slope of the drain-tosource voltage of M1 before  $v_{DS}$  reaches the turning point  $v_{DS1}$  (corresponding to the time t<sub>1</sub> in Fig. 6), is significantly lower as compared to the duration in which  $v_{DS} \ge v_{DS1}$ . The interval in which  $v_{DS}$  is lower than  $v_{DS1}$  is referred as ohmic region, as shown in Fig. 6. Furthermore, the interval in which  $v_{DS}$  is higher than  $v_{DS1}$  and lower than the bus voltage ( $V_{Bus}$ ) is referred as  $dv_{DS}/dt$  control region (corresponding to the interval between  $t_1$  and  $t_3$  in Fig. 6).

According to (1), the  $dv_{DS}/dt$  can be controlled by varying the resistance in the discharging path of the gate. The latter in turn is adjusted by changing the optical intensity of OTPT2. Current level  $L_1$  of the laser driver sets the optical intensity in the  $dv_{DS}/dt$  control region. Resistance of OTPT as a function of optical power is measured using the resistive circuit of Fig. 7 and data is plotted in Fig. 9.

When  $v_{DS}$  matches the bus voltage ( $V_{Bus}$ ) at  $t_3$ , current  $i_D$  falls which causes an overvoltage across M1 due to the parasitic inductances in the commutation path. This region is referred to as the  $di_D/dt$  control region. The overvoltage ( $\Delta v_{ov}$ ) across the drain-to-source terminals of M1 is given by the following expression:

$$\Delta v_{ov} = L_c \cdot \frac{dt_D}{dt} \tag{3}$$

Where  $L_c$  is the sum of the parasitic inductances in the commutation path, which includes the parasitic inductances of M1 and M2, bus-parasitic inductance, and trace inductances. In the  $di_D/dt$  control region,  $di_D/dt$  is given by the following expression:

$$\frac{di_D}{dt} \approx -\frac{V_{GS,TH} + i_D/2g_{fs}}{R_G C_{iss}/g_{fs} + L_\sigma}.$$

(4)

In (3),  $C_{iss}$  is the input capacitance of M1 and  $L_{\sigma}$  is the sum of parasitic inductances seen from the source of M1. Following (3), the  $di_D/dt$  is controlled by varying the resistance of the discharging path of the gate of M1. This resistance is adjusted by changing the optical intensity of OTPT2, as shown in Fig. 3. Current level ( $L_2$ ) of the laser driver sets the optical intensity in the  $di_D/dt$  control region and  $L_2$  is proportional to the external voltage control command  $V_2$ , as shown in Fig. 5.

Of course, while the control of  $dv_{DS}/dt$  and  $di_D/dt$  in their respective regions of operation is important, a seamless transition between the  $dv_{DS}/dt$  and  $di_D/dt$  control regions is equally important. In the following subsection, we derive this threshold condition for transition between the two control regions and outline its implementation.

# 1. Threshold Condition for Transition Between dv<sub>DS</sub>/dt and dip/dt Control Regions

The transition between  $L_1$  and  $L_2$ , thereby transitioning from the  $dv_{DS}/dt$  to the  $di_D/dt$ control region, is initiated by the control circuit illustrated in Fig. 5. This transition guarantees the independent control of  $di_D/dt$  and  $dv_{DS}/dt$ . Following, [34] and [39], an easy way to detect the onset of the  $di_D/dt$  control region is to detect the change in the  $di_D/dt$  from near zero to a significantly larger value. If this approach is adopted, the onset of transition is initiated later than the desired instant due to control-loop and OTPT-related delays. So, one may lose the control over  $di_D/dt$  in all or a part of this  $di_D/dt$  control region, which may lead to excessive device stress or switching loss as illustrated in Fig. 10. Another approach [25] for predicting the onset of the  $di_D/dt$  control region is based on detecting the saturation region of the voltage corresponding to  $dv_{DS}/dt$  control regions after a fixed delay. However, the error in the prediction of onset of transition is significant in applications where the  $dv_{DS}/dt$  varies over a wide range.

Therefore, in the proposed scheme, to ensure the independent control of  $dv_{DS}/dt$ and  $di_D/dt$ , a simple control circuit is designed which predicts the onset of transition between the  $dv_{DS}/dt$  and  $di_D/dt$  control regions based on the actual  $dv_{DS}/dt$  and the scaled bus-voltage

Fig. 10: Effect of late transition between the  $dv_{DS}/dt$  and  $di_D/dt$  control regions on device stress and switching loss, ©2015 IEEE.

Fig. 11: Signals  $v_{DS}$  and  $dv_{DS}/dt$ , at the desired time ( $t_2$ ) of transition for two different  $dv_{DS}/dt$ , considering the constant delay of  $\Delta t$  seconds in the feedback loop, ©2015 IEEE.

reference  $(v_{ref})$ . The  $di_D/dt$  control region onsets at  $t_3$ , when  $v_{DS}$  reaches the bus voltage  $(V_{Bus})$ as shown in Fig. 6. and Fig.11. However, considering a combined constant delay of  $\Delta t$  seconds due to the feedback and due to the delay in the actuation of OTPT2, the control circuit initiates the transition between  $dv_{DS}/dt$  and  $di_D/dt$  control regions at time  $t_2$  (=  $t_3 - \Delta t$ ). An accurate onset of transition ensures the independent controllability of the  $dv_{DS}/dt$  and  $di_D/dt$  control regions.

Now, using Fig. 11, one can show that for any given  $dv_{DS}/dt$  the following equality holds:

$$v_{DS,t2} + (dv_{DS,t2}/dt) \Delta t = V_{Bus}.$$

(5)

In (5),  $v_{DS,t2}$  and  $dv_{DS,t2}/dt$  represent, respectively, the values of  $v_{DS}$  and  $dv_{DS}/dt$  at time  $t_2$ . Assuming the scaling factors of  $\alpha_1$ ,  $\alpha_2$  and  $\alpha_3$  associated with sensing  $V_{Bus}$ ,  $v_{DS}$  and  $dv_{DS}/dt$ , respectively, the following equations hold:

$$v_{ref} = \alpha_1 \cdot V_{Bus} \tag{6}$$

$$\dot{\nu}_{DS,t2} = \alpha_2. \, \nu_{DS,t2} \tag{7}$$

$$d\dot{v}_{DS,t2}/dt = \alpha_3. \, (dv_{DS,t2}/dt). \tag{8}$$

In (7),  $\dot{v}_{DS,t2}$  represents the value of sensed  $v_{DS}$  at time  $t_2$  with a scaling factor of  $\alpha_2$ . In (8),  $d\dot{v}_{DS,t2}/dt$  represents the value of sensed  $dv_{DS}/dt$  at  $t_2$  with a scaling factor of  $\alpha_3$ . Substituting (6)-(8) into (5) yields the following relation:

$$\frac{\dot{\nu}_{DS,t2}}{\alpha_2} + \frac{d\dot{\nu}_{DS,t2}/dt}{\alpha_3} \cdot \Delta t = \frac{\nu_{ref}}{\alpha_1}.$$

(9)

Because  $\Delta t$  is considered to be a constant, (8) can be rewritten as follows:

$$\beta_1 \cdot \dot{v}_{DS,t2} + \beta_2 \cdot (d\dot{v}_{DS,t2}/dt) = v_{ref}.$$

(10)

In (9),  $\beta_1$  equals to  $(\alpha_1/\alpha_2)$  and  $\beta_2$  equals to  $(\alpha_1 \Delta t/\alpha_3)$ . Using (9), the threshold condition for transition from the  $dv_{DS}/dt$  to di/dt control region is found to be:

$$(\beta_1 \cdot \dot{v}_{DS} + \beta_2 \cdot (d\dot{v}_{DS}/dt)) - v_{ref} \ge \varepsilon.$$

(11)

In (11),  $\dot{v}_{DS}$  and  $d\dot{v}_{DS}/dt$  represent, respectively, the sensed values of  $v_{DS}$  and  $dv_{DS}/dt$  at any time with scaling factors of  $\alpha_2$  and  $\alpha_3$  while  $\varepsilon$  represents a very small positive value. Essentially, (11) indicates that there is a time t (ideally  $t = t_2 = t_3 - \Delta t$ ) at which the difference between  $\beta_1 \cdot \dot{v}_{DS} + \beta_2 \cdot (d\dot{v}_{DS}/dt)$  and  $v_{ref}$  is either zero or very close to zero. This concept is used to design a controller which compensates for the delay in the feedback loop and ensures a seamless transition between  $dv_{DS}/dt$  and  $di_D/dt$  control regions.

The control circuit and laser driver schematics are shown in Fig. 12. The coefficients  $\beta_1$  and  $\beta_2$  are considered to be equal to make the design of the control circuit easier. Therefore, the coefficients  $\alpha_1$  and  $\alpha_2$  have the following relation:

$$\beta_1 = \beta_2 = \beta \Longrightarrow \frac{\alpha_1}{\alpha_2} = \frac{\alpha_1}{\alpha_3} \Delta t \Longrightarrow \alpha_2 = \frac{\alpha_3}{\Delta t}$$

(12)

The sensed  $v_{DS}$  and  $dv_{DS}/dt$  are scaled with proper coefficient  $\beta$  and added using the OP1, as shown in Fig. 12, Where  $\beta = R_1/3$ .  $(1 + R_3/R_2)$ . The output of OP1 is then compared with  $v_{ref}$ using a comparator to monitor if the threshold condition in (2-11) is met. If (2-11) is satisfied, the control circuit initiates the transition from  $dv_{DS}/dt$  to  $di_D/dt$  control region by setting Lev1 to logic state 0 and Lev2 to logic state 1 using the D-FF and AND operators of Fig. 12.

Because of the negative  $dv_{DS}/dt$  in the  $di_D/dt$  control region, the threshold condition might not be satisfied in the  $di_D/dt$  control region. Therefore, a D flip-flop is used to prevent undesirable fluctuations of the logic states of signals Lev1 and Lev2 in the  $di_D/dt$  control region. The truth table for the control circuit can be found in the Table. 1. In Table. 1, X means no change in the state of the signal. Any negligible error in initiating the onset of transition (i.e.,

Fig. 12. Schematics of the control circuit and the laser driver, ©2015 IEEE.

$\varepsilon \neq 0$  and instead  $\varepsilon \approx 0$ ) is due to the non-idealities in the circuit elements, nonlinearities, and error in the estimation of the total delay of the feedback loop.

Subsequent to the change in the logic states of Lev1 and Lev2, the laser driver changes its output current ( $I_{Laser}$ ) from  $L_1$  to  $L_2$  (which is proportional to  $V_1$  and  $V_2$ ) and is given by the following relation:

$$I_{\text{Laser}} = \begin{cases} \gamma. V_1 = L_1 & \text{, when Lev1 signal is high} \\ \gamma. V_2 = L_2 & \text{, when Lev2 signal is high} \\ 0 & \text{, when PWM signal is low} \end{cases}$$

(13)

In (13),  $\gamma$  is a circuit-dependent constant and it is equal to  $\gamma = 0.1/R_6$ . The outputs of the flipflop Q and  $\overline{Q}$ , in the Fig. 2-5, work complementarily. Furthermore, the Lev1 and Lev2 signals are derived using the AND operation of the PWM signal with  $\overline{Q}$  and Q, respectively. Therefore, Lev1 and Lev2 signals in (13) are complement to each other in the duration when the PWM signal is high and they are both low when PWM signal is low, as illustrated in Fig. 6. and Table. 1. Following (1), (3), and (13), one can adjust  $dv_{DS}/dt$  and  $di_D/dt$  by respectively controlling  $V_1$  and  $V_2$ , which in turn control the output current of the laser driver to magnitudes of  $L_1$  and  $L_2$ . Modulating the optical intensity by the proposed laser driver, along with the implementation of the threshold condition (11), enables one to attain the unified  $dv_{DS}/dt$  and  $di_D/dt$  control.

TABLE I: Truth table of the control circuit.

| Comparator | PWM | Q | $\overline{\mathbf{Q}}$ | Lev1 | Lev2 |

|------------|-----|---|-------------------------|------|------|

| 1          | 0   | 1 | 0                       | 0    | 1    |

| 0          | 1   | 0 | 1                       | 0    | 0    |

| 1          | 1   | 1 | 1                       | 0    | 0    |

| 0          | 0   | Х | Х                       | Х    | X    |

# 2. Availability of Independent *dv<sub>DS</sub>/dt* and *di<sub>D</sub>/dt* Control

In section II-A-1, the threshold condition for independent control of turn-off  $dv_{DS}/dt$ and  $di_D/dt$  was derived. Subsequently, the control circuit was designed based on the aforementioned threshold condition. However, the threshold condition was derived considering the following assumptions:

a) The  $\Delta t$  (total delay in the feedback loop and OTPT) is fixed.