# High Performance Embedded Solutions for Memory and Compute Intense

Applications

BY

UMER I. CHEEMA

B.Sc. Electrical Engineering, University of Engineering & Technology, Lahore, Pakistan, 2008

M.S. Electrical & Computer Engineering, University of Illinois at Chicago, 2014

### THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2016

Chicago, Illinois

## **Defense Committee:**

Ashfaq Khokhar, Advisor Rashid Ansari, Chair & Co-advisor Wenjing Rao Hulya Seferoglu John Lillis, Computer Science Copyright by

Umer I. Cheema

2016

Dedicated to my parents: Sajida and Iftikhar

## ACKNOWLEDGMENTS

My time at UIC has been a tremendous learning experience not only in academics but also in all other aspects of life. I owe my success to all my teachers throughout my academics. First of all, I would like to thank my PhD advisor, Professor Ashfaq Khokhar, for his consistent feedback and support throughout my PhD. He let me chose an independent path which was tougher but I got to work on something that I really enjoyed and learned much more during the process than I would have otherwise. I would also like to thank my co-adviser, Professor Rashid Ansari, for his consistent support especially after Professor Khokhar left UIC.

I would also like to thank my thesis Committee members Prof. Wenjing Rao, Prof. Hulya Seferoglu and Prof. John Lillis, for their feedback and encouraging comments. I got to work with Prof. Wenjing Rao as a Teaching Assistant as well as a student. I took a lot of inspiration from her teaching methods as well as the work ethics.

I would like to thank Prof. Vahe Caliskan, for entrusting me to teach key undergraduate courses and his consistent help and support during my time as course instructor. Thanks to Prof. Robert Becker for the wonderful learning experience I had as his Teaching Assistant. I would also like to thank all the professors I took my PhD course work with: Prof. Grygory Turon, Prof. Masud Chowdhury, Prof. Ajay Kshemkalyani, Prof. Prasad Sistla, Prof. Mitchell Theys, Prof. Tadao Murata, Prof. Shantanu Dutt and Prof. Michael Stroscio. Throughout my stay at UIC, I had the opportunity to interact with some amazing people. I would like to acknowledge Gregory Nash for the discussions about the trends in industry related to my

### ACKNOWLEDGMENTS (Continued)

thesis. His knowledge in the field helped me chose the right tools for my research. I had a great interaction with Mohamed Hefeida - the senior. Observing him go through the PhD process, gave me inspiration and a better understanding of the process. I regret the accident we had in racket ball game that gave him a lot of pain. Mohamed Ali was my lab mate as well as apartment mate for the longest. I didnt get to see him a lot because of his off-campus commitments but I learned a lot from him in multiple domains. To Kamran Lodhi, we had some great road trips together and his spicy cooking was always enjoyable. To Ansab Ali, who always had quality high-end games that I could enjoy on his computer. To Fahad Saeed, for being a great example and inspiration throughout my PhD. To Fadi Almasalha, for the help and support when I first came to Chicago. I would also like to thank my lab-mates: Xi Xu, Yasaman Keshtkarjahromi, Nazanin Makkinejad and Shafagh Kamkar for the time we spent together. The ECE department staff - Erica Plys, Agustina Alvarado, Ala Wroblewski, Beverly Miller, Mona Hurt, Evelyn Reyes, Mihai Bora, Martha Salinas, George Ashman and Harold Sosa - were very helpful in the administrative matters. I would also like to thank my fellow graduate students - Pitamber Shukla, Jian Xu, Mehak Gill, Narueporn Nartasilpa and Soumik Sen - who did a great job assisting me in teaching so I could focus well on my research. Some other friends I had good time with were Ahmad Khalil, Muzammil Rafique, Farukh Ijaz, Talal Haider, Ahsan Shahid, Sumra Bari and Rasheed Abdulkader.

Coming to Chicago from the other side of the globe was initially an overwhelming experience. My uncle, Zafar Singhera and his family, Arusa and Fakhar, made this transition relatively easier. The supply of tasty food from California was a life saver during the early days. My

### **ACKNOWLEDGMENTS** (Continued)

uncle has been an inspiration for me right from my child hood and his consistent guidance and support played a vital part in my academics. Next, I would like to thank my family. It is really hard to find the words to thank them for their contribution in my life. To my sisters: Aafia, whose motivational quotes kept my morale up throughout the course of this work. Sobia, the best help and source of feedback I had all along my academics. Qudsia, for her endless stories and jokes whenever I felt down. To Shahid and my nephews, Abdullah and Rayan, for the refreshing talks. To my parents Sajida and Iftikhar, the best human beings in my life. Their unconditional love, support and hard-work is the reason behind any success that I had and I dedicate this thesis to them.

UIC

### ACKNOWLEDGMENTS (Continued)

### **Contribution of Authors**

I would like to acknowledge Prof. Ashfaq Khokhar for his feedback related to the selection of the compute intense problems addressed in this work. His feedback helped improve arbitration aspect of Re-gridding architecture discussed in chapter 2 and scalability aspect of matrix inversion architecture in chapter 3. Prof. Rashid Ansari and Prof. Ashfaq Khokhar gave consistent feedback on improving the presentation of the proposed solutions. Gregory Nash helped in selecting the tools for the experimentation. His feedback helped improve the architecture of FpMA units as well as the openCL implementation for Re-gridding architecture in chapter 2.

# TABLE OF CONTENTS

## **CHAPTER**

# PAGE

| 1        | INTRODUCTION |                                                                |

|----------|--------------|----------------------------------------------------------------|

|          | 1.1          | Heterogeneous Computing Platforms                              |

|          |              | 1.1.1 Design Space for Heterogeneous Computing Platforms 2     |

|          |              | 1.1.2 Heterogeneous Computing Architectures in Embed-          |

|          |              | ded Systems                                                    |

|          | 1.2          | FPGAs as a High-performance Computing Platform 6               |

|          |              | 1.2.1 Programmability                                          |

|          |              | 1.2.2 Application domains                                      |

|          | 1.3          | Contributions                                                  |

|          | 1.4          | Thesis organization                                            |

| <b>2</b> | RE-GR        | IDDING ARCHITECTURE FOR ACCELERATING NON-                      |

|          |              | <b>PRM FAST FOURIER TRANSFORM</b>                              |

|          | 2.1          | Introduction                                                   |

|          |              | 2.1.1 Spectral Sampling Trajectories                           |

|          |              | 2.1.2 Re-Gridding or Data-Translation                          |

|          | 2.2          | Related Work                                                   |

|          | 2.3          | Proposed Re-Gridding Architecture                              |

|          |              | 2.3.1 Points Representation                                    |

|          |              | 2.3.2 Data-translator Components                               |

|          |              | 2.3.3 Data-flow through the System                             |

|          | 2.4          | Hardware Implementation                                        |

|          |              | 2.4.1 Optimized Verilog Based Implementation                   |

|          |              | 2.4.2 OpenCL Implementation                                    |

|          |              | 2.4.3 Comparison of Implementations                            |

|          | 2.5          | Comparison with Related Work                                   |

|          |              | 2.5.1 Verilog Implementation                                   |

|          |              | 2.5.2 OpenCL Implementation                                    |

|          | 2.6          | Conclusions and Future Work                                    |

| 3        | HARD         | WARE EFFICIENT ARCHITECTURE FOR MATRIX                         |

|          | INVER        |                                                                |

|          | 3.1          | Introduction                                                   |

|          | -            | 3.1.1 Gauss-Jordan Elimination Algorithm                       |

|          | 3.2          | Related Work                                                   |

|          | 3.3          | Hardware Optimization using Modified Gauss-Jordan Algorithm 67 |

|          |              | 3.3.1 Pipeline Utilization                                     |

|          |              | -                                                              |

# TABLE OF CONTENTS (Continued)

## **CHAPTER**

|   | 3.4     | Proposed Architecture and Data-flow                                                                                                                     |

|---|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |         | $3.4.1 \qquad \text{Data-flow}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                        |

|   |         | $3.4.2 \qquad \text{Scalability} \dots \dots$     |

|   | 3.5     | Performance Analysis                                                                                                                                    |

|   |         | 3.5.1 Performance comparison with related work 75                                                                                                       |

|   | 3.6     | Hardware Complexity Analysis                                                                                                                            |

|   | 3.7     | Experimental Setup and Results                                                                                                                          |

|   | 3.8     | Conclusions and Future Work8080                                                                                                                         |

| 4 | A HIGH  | PERFORMANCE ARCHITECTURE FOR COMPUT-                                                                                                                    |

|   | ING BU  | <b>RROWS-WHEELER TRANSFORM ON FPGAS</b> 89                                                                                                              |

|   | 4.1     | Background                                                                                                                                              |

|   | 4.2     | Related Work                                                                                                                                            |

|   | 4.3     | Flowthrough FIFO based technique for computing BWT in                                                                                                   |

|   |         | Hardware                                                                                                                                                |

|   | 4.4     | Proposed architecture and data-flow                                                                                                                     |

|   |         | 4.4.1 Suffix Block and Address Generator                                                                                                                |

|   |         | 4.4.2 Parallel Suffix Sorter                                                                                                                            |

|   |         | 4.4.3 FIFO Network                                                                                                                                      |

|   |         | 4.4.4 BWT index generator $\dots \dots \dots$           |

|   | 4.5     | Complexity Analysis                                                                                                                                     |

|   |         | 4.5.1 Hardware Complexity Analysis                                                                                                                      |

|   |         | 4.5.2 Time Complexity Analysis                                                                                                                          |

|   | 4.6     | Experimental Setup & Results 100                                                                                                                        |

|   | 4.7     | Summary                                                                                                                                                 |

| 5 | AN FPO  | GA BASED HIGHLY PIPELINED AND SCALABLE                                                                                                                  |

|   | ARCHIT  | <b>TECTURE FOR MEDIAN FILTERING</b> 107                                                                                                                 |

|   | 5.1     | Introduction $\dots \dots \dots$                        |

|   | 5.2     | Related Work 109                                                                                                                                        |

|   | 5.3     | Proposed Architecture and Data flow                                                                                                                     |

|   |         | 5.3.1 Row Sorter $\ldots \ldots \ldots$ |

|   |         | 5.3.2 Sorted-Row Buffers 111                                                                                                                            |

|   |         | 5.3.3 Merger block $\ldots \ldots 114$                              |

|   |         | 5.3.4 Data-flow $\dots \dots \dots$                     |

|   | 5.4     | Results and Discussion                                                                                                                                  |

|   | 5.5     | Conclusion and Future Work 120                                                                                                                          |

| 6 | CONCL   | USION AND FUTURE DIRECTIONS                                                                                                                             |

|   | CITED I | LITERATURE 126                                                                                                                                          |

# TABLE OF CONTENTS (Continued)

| CHAPTER  |  | PAGE |

|----------|--|------|

| APPENDIX |  | 138  |

| VITA     |  | 142  |

# LIST OF TABLES

| TABLE |                                                                                                                                           | PAGE         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Ι     | COMPARISON BETWEEN DEDICATED HARDWARE AND CPU<br>BASED SOLUTIONS                                                                          | 3            |

| II    | THROUGHPUTS FOR VARIOUS SIZES OF TILE, CONVOLUTION WINDOW AND TARGET SET $T$                                                              | 41           |

| III   | POWER AND PERFORMANCE FOR DIFFERENT TRAJECTO-<br>RIES                                                                                     | 46           |

| IV    | PERFORMANCE FOR LARGE MATRIX SIZES IN TERMS OF NUMBER OF CLOCK CYCLES                                                                     | 77           |

| V     | PERCENTAGE REDUCTION IN HARDWARE RESOURCES FOR<br>FLOATING-POINT COMPUTATION UNITS COMPARED TO PIPE<br>IMPLEMENTATION OF GJ               | ELINED<br>78 |

| VI    | PERFORMANCE FOR VARIOUS MATRIX SIZES                                                                                                      | 79           |

| VII   | COMPARISON OF HARDWARE COMPLEXITY BETWEEN PAR-<br>ALLEL SORTER IN AND PARALLEL SUFFIX SORTER USED IN<br>OUR PROPOSED ARCHITECTURE FOR BWT | 100          |

| VIII  | PERFORMANCE COMPARISON OF PROPOSED BWT ARCHI-<br>TECTURE WITH WEAVESORTERAND PARALLEL SORTER FOR<br>A STRING OF SIZE 128 AND LCP = 8      | R<br>105     |

| IX    | THROUGHPUT IN TERMS OF IMAGE SLICE RATE FOR VAR-<br>IOUS NUMBER OF <i>MEDIANPIPES</i>                                                     | 121          |

## LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                                                                                                                                                                                                                | PAGE |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | Heterogeneous Computing platform                                                                                                                                                                                                                                                                                                                                                                                               | 2    |

| 2      | Design Space for Heterogeneous Computing platforms                                                                                                                                                                                                                                                                                                                                                                             | 5    |

| 3      | Complexity of Embedded Software. Source: (1) $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                     | 6    |

| 4      | Example of heterogeneous SoC architecture for mobile devices                                                                                                                                                                                                                                                                                                                                                                   | 7    |

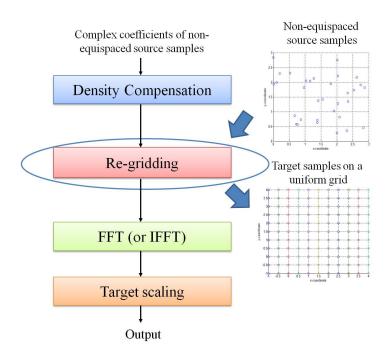

| 5      | NuFFT algorithm flow                                                                                                                                                                                                                                                                                                                                                                                                           | 16   |

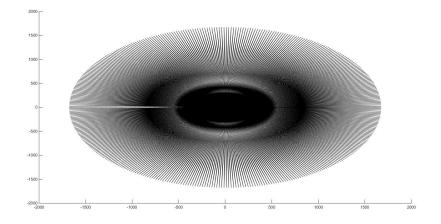

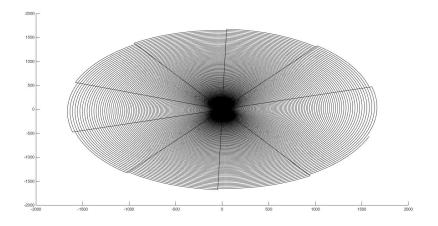

| 6      | Radial Trajectory. (Generated using $(2)$ )                                                                                                                                                                                                                                                                                                                                                                                    | 19   |

| 7      | Spiral Trajectory. Generated using $(2)$                                                                                                                                                                                                                                                                                                                                                                                       | 20   |

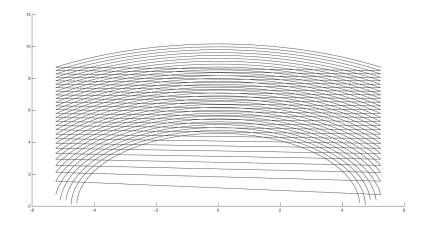

| 8      | Polar/Curvilinear trajectory. Generated using (3) $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                | 21   |

| 9      | Cartesian Trajectory                                                                                                                                                                                                                                                                                                                                                                                                           | 22   |

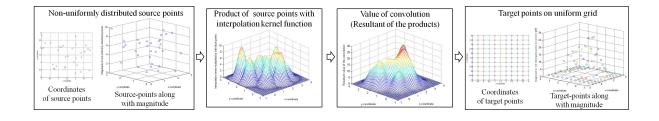

| 10     | Visual Representation of the Re-gridding process                                                                                                                                                                                                                                                                                                                                                                               | 22   |

| 11     | Pseudo code for Re-gridding processes in 2-dimension. The values of $s_i$ and $t_k$ are denoted by $v(s_i)$ and $v(t_k)$ respectively. $(s_{i_x}, s_{i_y})$ and $(t_{k_x}, t_{k_y})$ denote the respective co-ordinates.                                                                                                                                                                                                       | 24   |

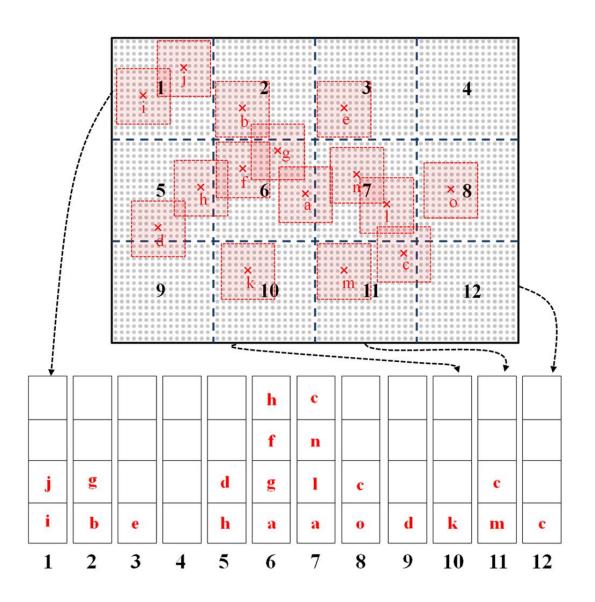

| 12     | Mapping between Tiles and point FIFO. The boundaries of the tiles are<br>shown by dotted blue line and tiles are numbered from 1 - 12. Grey<br>dots indicates the target points, crosses indicates the source points and<br>dotted red box indicates the convolution widow for each source point.<br>The FIFOs at the bottom are shown filled with the source points and<br>have the same index as the tile they correspond to | 29   |

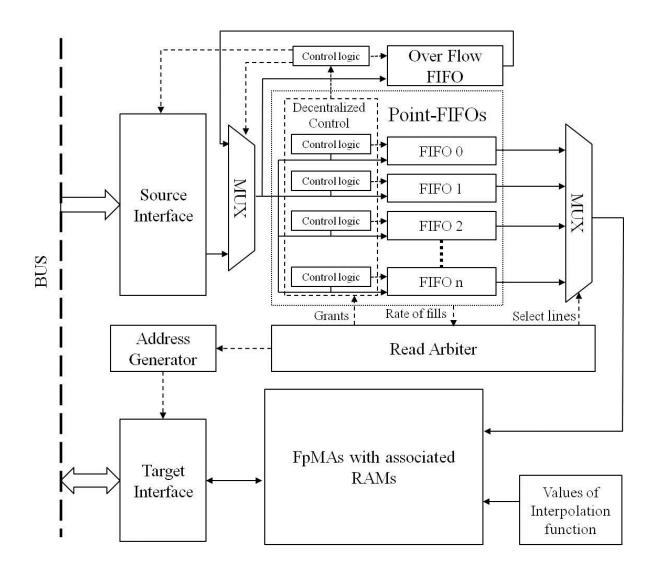

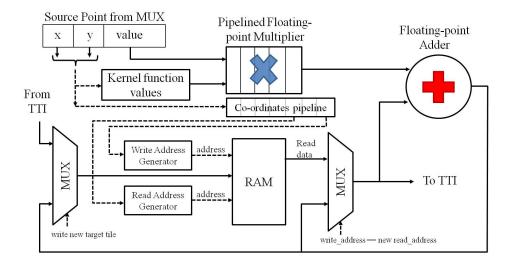

| 13     | The proposed Re-Gridding (Data Translator) architecture depicting the data-flow through its components. The solid lines indicate the data flow and dotted lines indicate control lines.                                                                                                                                                                                                                                        | 30   |

## **FIGURE**

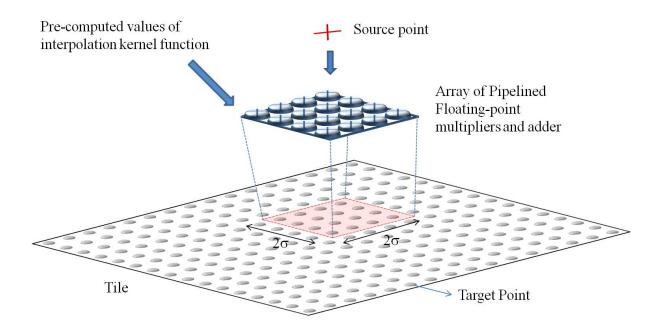

| 14 | The convolution operation of the source point with the interpolation kernel function to update the target point values. The red box on the tile indicates the convolution window.                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 15 | Logical connection of Floating point Multiplier and Adder (FpMA) units<br>to target points in fetched tile indicated by color coding: (a) Array of<br>FpMAs units, each box represents an FpMA unit (cell). The co-ordinates<br>in each box indicates the index of the FpMA unit in a 2-d array format<br>(b) A tile of size 8 x 8. Each box represents a target point of the tile. The<br>co-ordinates in each box indicate the co-ordinate of target point in the<br>2-d tile. For clarity, logical connection of (0,0) FpMA unit is indicated<br>with dotted line as well | 35 |

| 16 | Architecture of the proposed Pipelined Floating Multiplier and Adder (FpMA) unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37 |

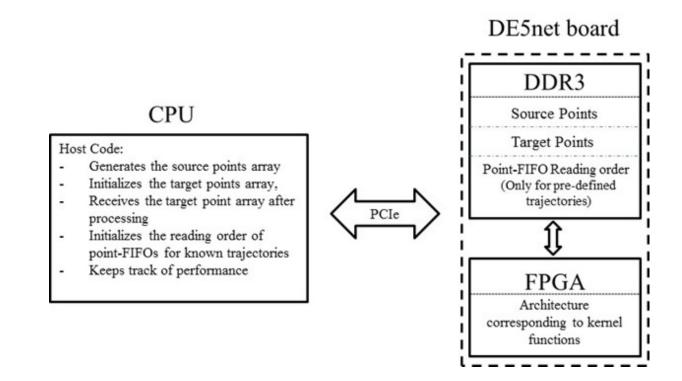

| 17 | OpenCL based Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43 |

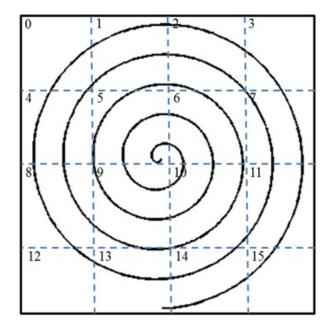

| 18 | Reading Order of Point-FIFOs could be decided a priori based on the known Trajectory. The figure shows the target frame divided into 16 tiles.                                                                                                                                                                                                                                                                                                                                                                                                                               | 44 |

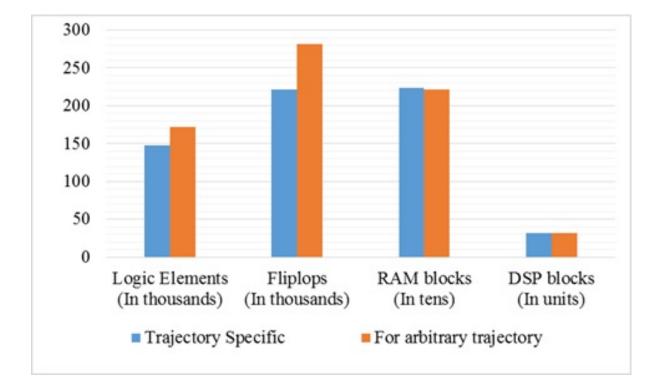

| 19 | Comparison of Hardware Resources for TSA and GA based Architectures<br>for target set size of $1024 \times 1024$ , tile size of $256 \times 256$ , $\alpha = 4$ and $\sigma = 2$                                                                                                                                                                                                                                                                                                                                                                                             | 47 |

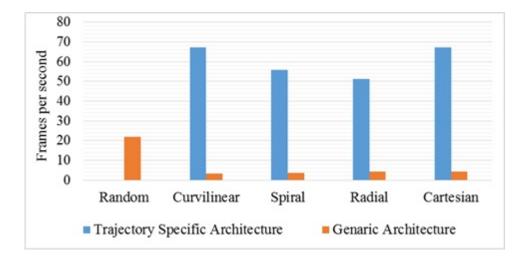

| 20 | Throughput comparison for trajectory specific architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48 |

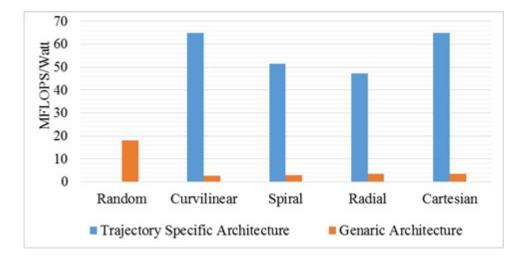

| 21 | Throughput comparison for trajectory specific architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49 |

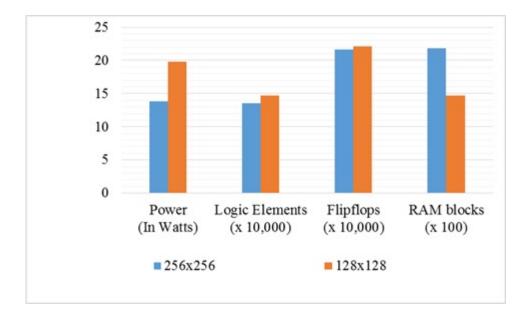

| 22 | Comparison of Power Consumption and Hardware Resources for tile size of $256 \times 256$ and $128 \times 128$ when the size of target point set is $512 \times 512$                                                                                                                                                                                                                                                                                                                                                                                                          | 50 |

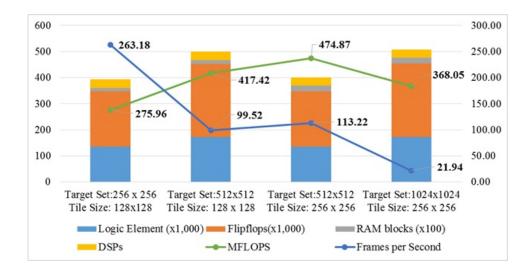

| 23 | Scalability of Hardware Resources, MFLOPS and throughput with the target set size and tile size for GA based architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

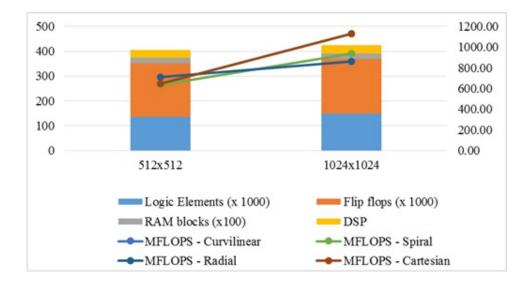

| 24 | Scalability of Hardware Resources, MFLOPS with the target set size for TSA based architecture. The vertical axis on left indicates the count for resources and the vertical axis on right is for MFLOPS.                                                                                                                                                                                                                                                                                                                                                                     | 52 |

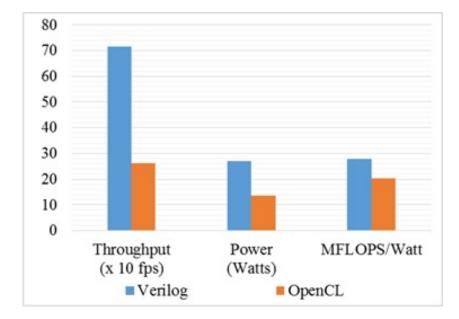

| 25 | Comparison of OpenCL implementation with Optimized Verilog based implementation for a target set of size $256 \times 256$ , $\alpha = 4$ and $\sigma = 2$                                                                                                                                                                                                                                                                                                                                                                                                                    | 53 |

## **FIGURE**

## PAGE

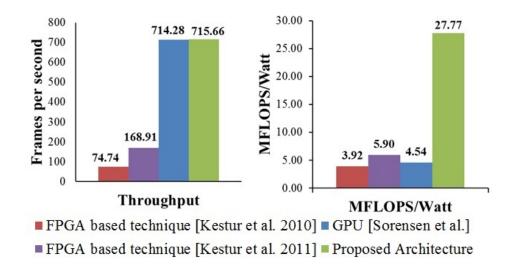

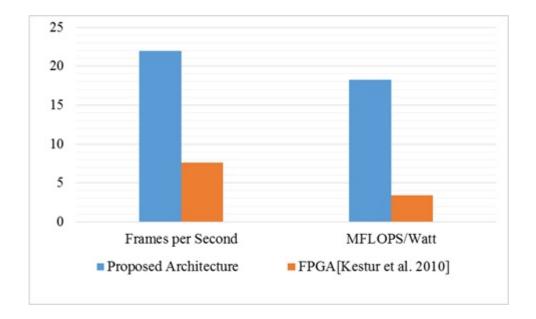

| 26 | Performance comparison of the verilog implementation of the proposed<br>architecture with existing FPGA (4; 5) and GPU (6) based techniques<br>for a target point set of $256 \times 256 \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                                                     | 56 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

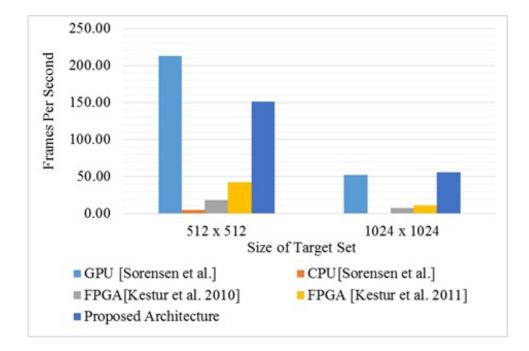

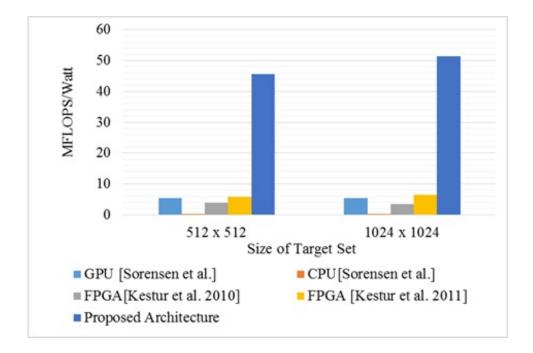

| 27 | Throughput comparison of Spiral Trajectory with related work $\ . \ . \ .$                                                                                                                                                                                                                                                                                                | 57 |

| 28 | Comparison of Power efficiency for Spiral Trajectory with related work                                                                                                                                                                                                                                                                                                    | 58 |

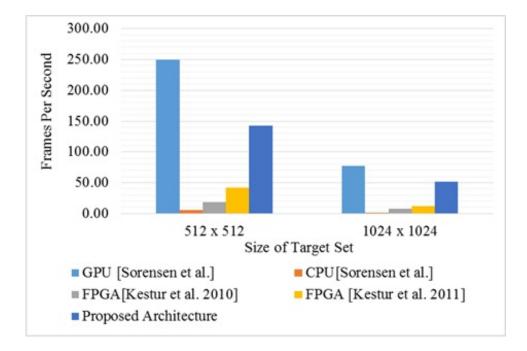

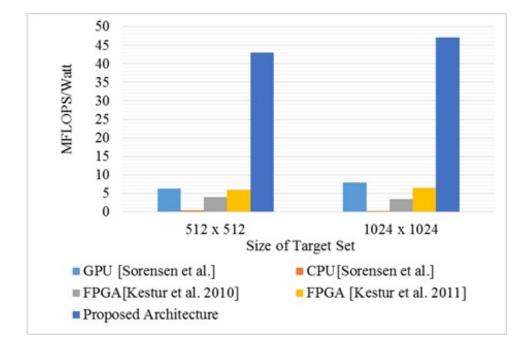

| 29 | Throughput comparison of Radial Trajectory with related work                                                                                                                                                                                                                                                                                                              | 59 |

| 30 | Comparison of Power efficiency for Radial Trajectory with related work                                                                                                                                                                                                                                                                                                    | 60 |

| 31 | Comparison of throughput and power efficiency for Random trajectory and a target set of size $1024 \times 1024$                                                                                                                                                                                                                                                           | 61 |

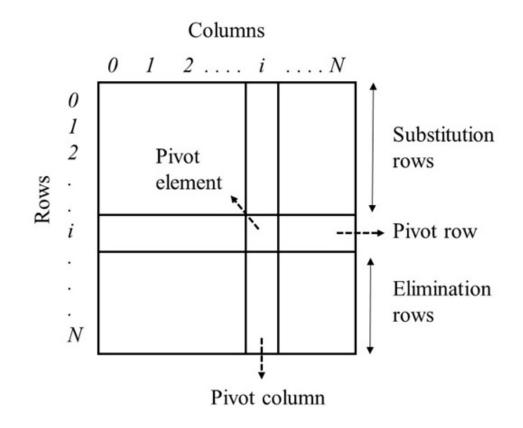

| 32 | An $N \times N$ matrix at the $i^{th}$ iteration $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                       | 68 |

| 33 | Pseudo-code Modified Gauss-Jordan Algorithm                                                                                                                                                                                                                                                                                                                               | 70 |

| 34 | Steps to find invert of a sample $3 \times 3$ matrix. The augmented matrix is<br>shown along with the contents of the memory. The reciprocal is found<br>over three steps. The values in green indicate the values that required<br>for further computation and are stored in the memory. Values in red<br>indicate the values that are no longer required in computation | 82 |

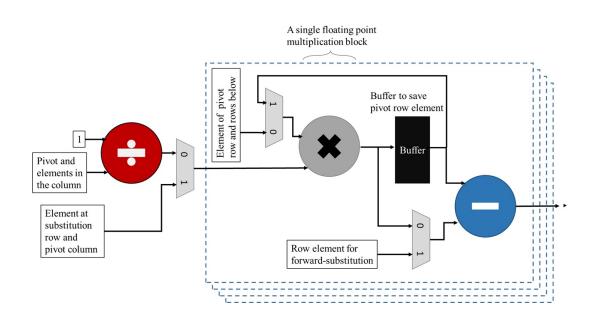

| 35 | Simplified architecture of pipelined Implementation of Gauss-Jordan Al-<br>gorithm. Two floating-point multiplication elements are required per row.                                                                                                                                                                                                                      | 83 |

| 36 | Simplified data-flow of Pipelined Implementation for Modified Gauss-<br>Jordan Algorithm. A single floating-point multiplication is required per<br>row as compared to two for the pipelined implementation of original<br>Gauss Jordan algorithm (Figure 35)                                                                                                             | 84 |

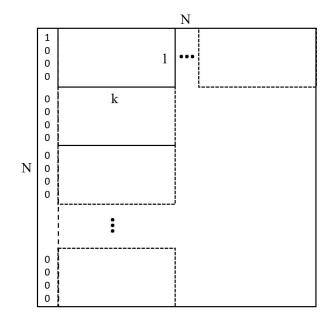

| 37 | Computational flow scalability                                                                                                                                                                                                                                                                                                                                            | 85 |

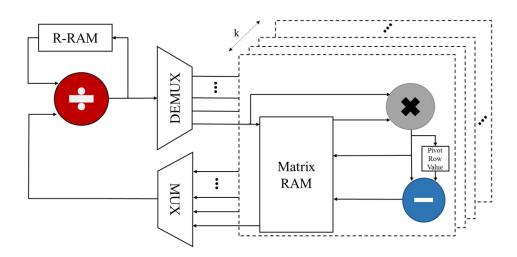

| 38 | Block diagram of the data path                                                                                                                                                                                                                                                                                                                                            | 85 |

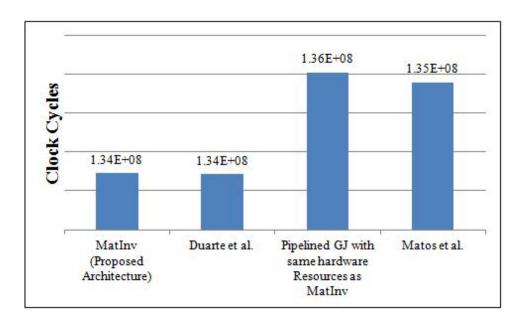

| 39 | Comparison of proposed architecture (InvArch) $(k = 8)$ against Duarte et al. (7) $(k = 8)$ , Matos et al (8) $(b = 8)$ and pipelined GJ implementation with same hardware resources as our proposed architecture $(k = 8)$ for a 1024 × 1024 matrix                                                                                                                      | 00 |

|    | for a $1024 \times 1024$ matrix                                                                                                                                                                                                                                                                                                                                           | 86 |

## **FIGURE**

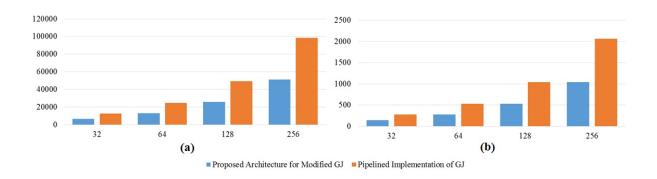

| 40 | Comparison of the hardware resources required for implementing floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | point blocks for different values of $k$ . (a) gives the number of Adaptive Look-Up Tables (ALUT)s and (b) gives the number of DSP blocks. The numbers are for the area-optimized implementation of Altera Floating point units on Startix IV FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87  |

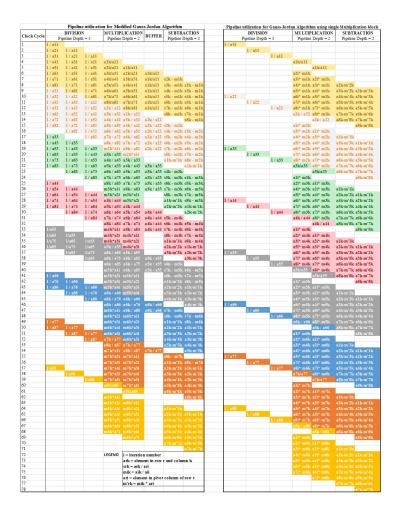

| 41 | Comparison of pipeline-utilization for modified-gauss jordan algorithm (left) with Gauss-jordan algorithm utilizing same number of floating point multiplication units (right). Iterations are indicated with distinct colors. Note that we assume number of NE blocks to be 8 in this figure i.e., 8 multiplication and subtraction units. During the $i^{th}$ iteration, for forward-elimination, result of normalized pivot ( $m_{ik} = a_{ik}/a_{ii}$ ) is buffered to be eliminate the elimination rows. For back-substitution, normalized pivot row element is available in time for the first 7 iterations but needs a single cycle stall for the last iteration. For same hardware resources, the pipeline on right needs stall cycles every iteration | 88  |

| 42 | Visual illustration of BWT: input string $s$ along with Matrix $M$ , matrix $Q$ and the Burrows-Wheeler Transform (BWT) $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90  |

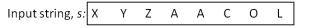

| 43 | Limited sized suffices for a Single Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96  |

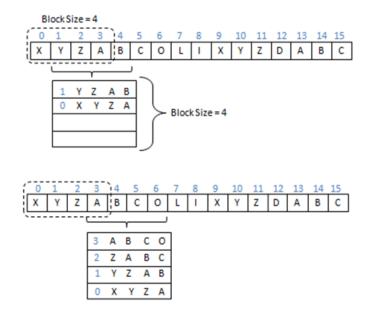

| 44 | Connectivity of FIFOs between two stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 98  |

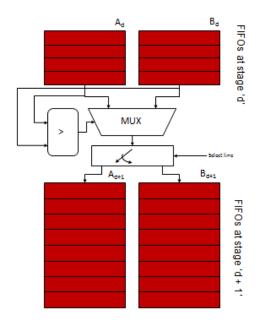

| 45 | Dataflow through the FIFO pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 99  |

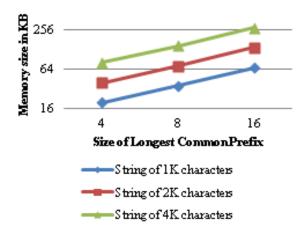

| 46 | Effect of the size of Longest Common Prefix (LCP) on the total memory used on pipleline of FIFOs for different string lengths.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101 |

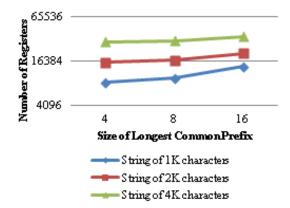

| 47 | Effect of size of Longest Common Prefix (LCP) on the number of Reg-<br>ister consumed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 102 |

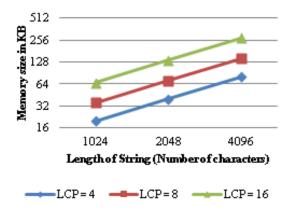

| 48 | Effect of the length of String on the total memory used on pipleline of FIFOs for different different sizes of LCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 103 |

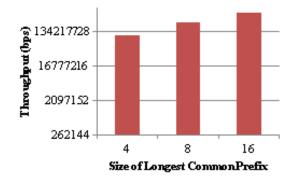

| 49 | Effect of LCP on Throughput using a fixed string of size two thousand characters. Longer LCP corresponds to more hardware complexity but higher throughput.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 103 |

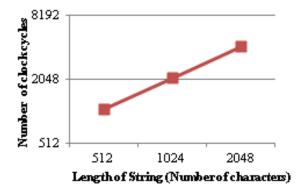

| 50 | Performance (in terms of number of clock cycles) for various length of strings having fixed $LCP = 16 \dots $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 104 |

## FIGURE

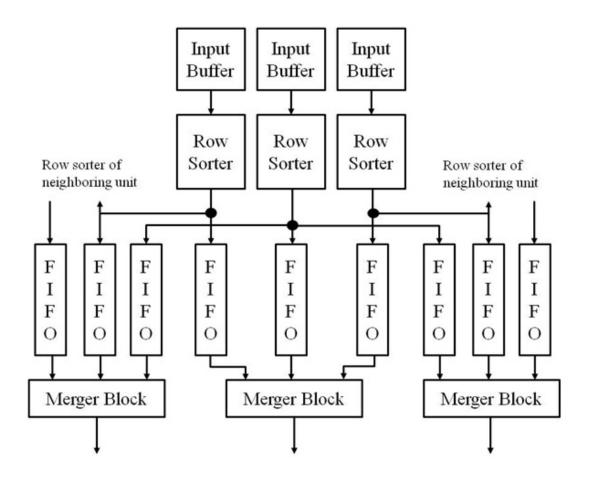

| 51 | Block Diagram of three <i>medianPipes</i>                                                                                                                                                                                                                                                                                                                                                                                 | 112 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

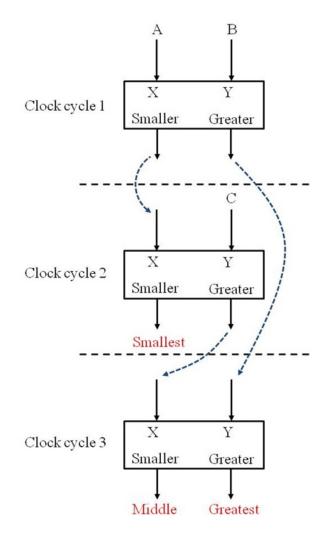

| 52 | First stage sorting using a single comparator                                                                                                                                                                                                                                                                                                                                                                             | 113 |

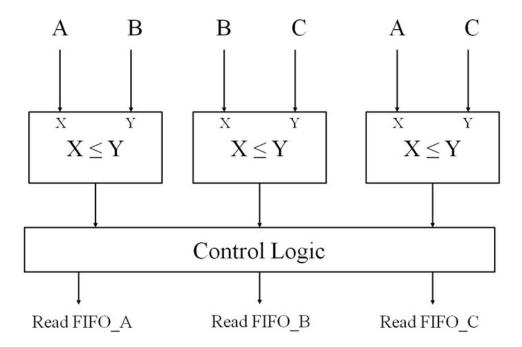

| 53 | Merger Block using three Comparators                                                                                                                                                                                                                                                                                                                                                                                      | 114 |

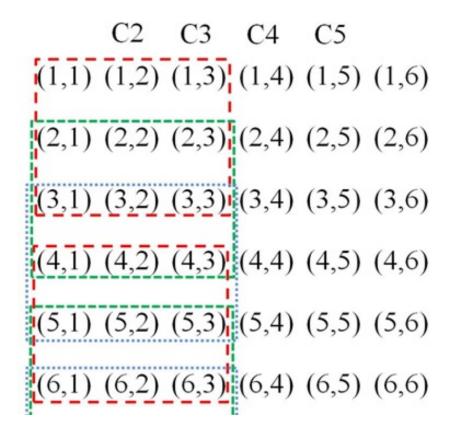

| 54 | Parallel computation of median values in column $C_2$ using two <i>medianPipes</i> . The ordered pairs $(R, C)$ represent a pixel, where $R$ and $C$ represents row and column respectively. Rows $R1 - R6$ are sorted in parallel. Merging sorted rows at $R_1$ , $R_2$ and $R_3$ compute the median value at $(2, 2)$ . $R_2$ , $R_3$ and $R_4$ compute median at $(3, 2)$                                              | 116 |

| 55 | Computation for median values across the columns. Since a single col-<br>umn of image slice is read from the external memory, if the computation<br>of median values for $C_2$ starts at $i^{th}$ cycle, the computation for $C_3$ will<br>start at $(i+1)^{th}$ , $C_4$ at $(i+2)^{th}$ and so on. The <i>medianPipes</i> dedicated<br>to the columns are re-used once the median values for the columns are<br>computed | 117 |

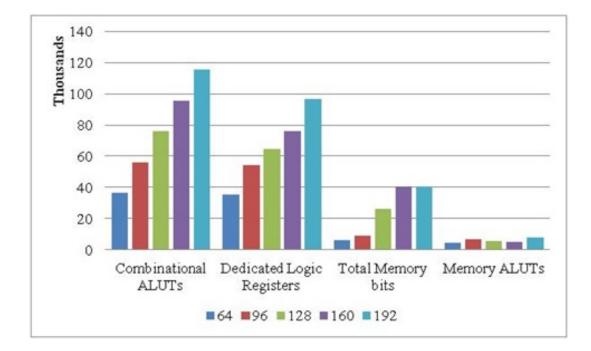

| 56 | Resource usage for various number of <i>medianPipes</i>                                                                                                                                                                                                                                                                                                                                                                   | 118 |

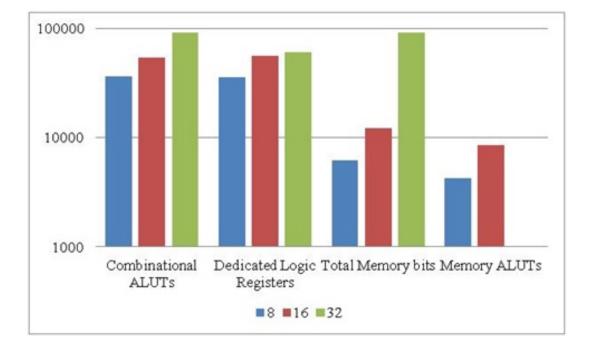

| 57 | Resource usage for pixel sizes of 8, 16 and 32 bits                                                                                                                                                                                                                                                                                                                                                                       | 119 |

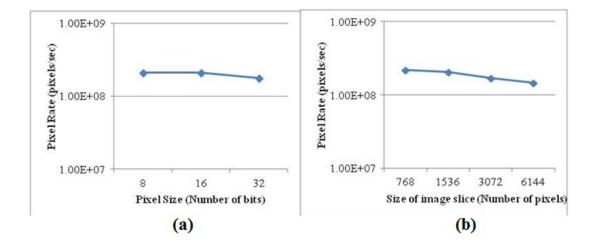

| 58 | (a) Trend in pixel rate with respect to pixel size using 128 median pipes<br>for 768 pixels(b) Trend in pixel rate with respect to image slice size<br>(using 8-bit pixel)                                                                                                                                                                                                                                                | 120 |

# LIST OF ABBREVIATIONS

| ALUT | Adaptive Look-up Tables             |

|------|-------------------------------------|

| BWT  | Burrows Wheeler Transform           |

| CS   | Compressed Sensing                  |

| CT   | Computed Tomography                 |

| DDR  | Double Data Rate                    |

| DSP  | Digital Signal Processing           |

| FFT  | Fast Fourier Transform              |

| FIFO | First-In-First-Out                  |

| FPD  | Floating-point Division             |

| FPM  | Floating-point Multiplication       |

| FPS  | Floating-point Subtraction          |

| FPGA | Field Programmable Gate Array       |

| FpMA | Floating-point Multiplier and Adder |

| GA   | Generic Arbiter                     |

| GJ   | Gauss Jordan                        |

| GPU  | Graphics Processing Unit            |

| IoT  | Internet of Things                  |

# LIST OF ABBREVIATIONS (Continued)

| LCP    | Longest Common Prefix                     |

|--------|-------------------------------------------|

| MAC    | Multiply and Accumulate                   |

| MFLOPS | Mega Floating-point Operations per Second |

| MRI    | Magnetic Resonance Imaging                |

| MUX    | Multiplexer                               |

| NE     | Normalization and Elimination             |

| NuDFT  | Non-uniform Discrete Fourier Transform    |

| NuFFT  | Non-uniform Fast Fourier Transform        |

| RAM    | Random Access Memory                      |

| SAR    | Synthetic Aperture Radar                  |

| SoC    | System-on-Chip                            |

| TSA    | Trajectory Specific Arbiter               |

| VLSI   | Very Large Scale Integration              |

## SUMMARY

The use of application-specific architectures has gained popularity in implementing solutions to many compute intense tasks in recent years due mainly to the performance and power limitations associated with high-end processor based systems. Considering their superior performance at lower energy requirements, such targeted solutions have found applications in a number of domains including Embedded Systems, Big-Data processing in Data centers, Computer Network Security, Medical Imaging and Internet of Things (IoT). These application specific hardware solutions could be used as stand-alone computation devices or as part of a heterogeneous computing system. Heterogeneous Embedded Systems, in the form of System-on-Chip (SoC), are used in applications ranging from smart hand-held devices, cars, drones to numerous other battery-operated electronic devices. Their higher performance-to-power ratio for compute intense tasks, like video processing, make them an ideal fit for battery-operated devices. In computer networks domain, specialized architectures are designed for real-time Deep Packet Inspection at high speed for network security. These hardware solutions also power the energyefficient data centers for big data processing and storage. With the growing interest in the Cloud-centric IoT, there is a high potential for using power-efficient heterogeneous systems for sensing, analysis and visualization of tremendous amount of data associated with IoT. At the IoT node level, design space exploration of the hybrid (CPU-FPGA-GPU) nodes are already being explored.

### SUMMARY (Continued)

Considering the tremendous potential of application specific hardware solutions in diverse range of applications, this thesis targets development of efficient solutions for various memory and compute-intense applications. We specifically target FPGAs as the computing platform considering the power-efficiency and the enormous design space associated with the platform due to its inherent flexibility. The hardware solutions proposed as part of this thesis have shown improved performance at reduced power compared with existing techniques.

The first computationally complex task we consider is the re-gridding process in Non-uniform Fast Fourier Transform (NuFFT). Some applications of NuFFT include Synthetic Aperture Radar (SAR), Computed Tomography (CT), and Magnetic Resonance Imaging (MRI). At the heart of the NuFFT task is a Gridding algorithm that maps non-equispaced data points onto a uniform grid using an interpolation function. This interpolation step, also referred to as re-gridding or data-translation, is known to consume 88 – 90% of the overall computation time of NuFFT. The dissertation proposes a novel FPGA based architecture for the memory and compute intense re-gridding process. The proposed architecture is based on the novel use of customizable hardware components such as FPGA block memory in First-In-First-Out (FIFO) configuration, fill-status based arbiter, distributed storage of grid-points and an array of pipelined single precision floating point multipliers and adders. The proposed solution exhibits high performance over a wide range of configurations, data sizes and spectral sampling trajectories. The architecture targets a generic solution for unknown trajectories and a trajectory-specific variant that targets well known trajectories in MRI and SAR. Compared with existing FPGA-based solutions, throughput is improved by over 9.6 times whereas compu-

## SUMMARY (Continued)

tational power efficiency (in terms of MFLOPS/Watt) is improved by over 15 times. Compared with GPU-based techniques, over 9.6 times higher MFLOPS/watts was achieved at a comparable performance.

Second, the thesis proposes an efficient architecture (*InvArch*) for computing matrix inversion using Gauss-Jordan Elimination method. The proposed architecture exploits parallelism through pipelined floating-point computational units and reduces the number of floating-point multiplication units required compared with the existing pipelined implementations. The reduction in multiplication units results in over 80% reduction in hardware for floating point computation units. The architecture performs in-place inversion and provides scalability across the rows and columns. Hardware efficiency is achieved by reaping benefit from regularity in computation and better utilization of pipelined computational resources. Multiple rows are normalized within an iteration of Gauss-Jordan algorithm that allows reduction in number of floating-point multiplication units in the elimination step. In addition to implementing the architecture, an analytical performance model is also developed for *InvArch* and some related works. *InvArch* achieves performance comparable to reference architectures in terms of clock cycles and throughput while using significantly less hardware resources.

Third, an FPGA based architecture for Burrows Wheeler transform (BWT) has been proposed. BWT has applications in diverse areas such as compressed string matching, biological sequence analysis, error correction, and channel encoding. Numerous efforts have been made to improve the performance of BWT in software and hardware. Its use in real-time applications such as deep packet inspection and channel coding requires efficient hardware implementations

### SUMMARY (Continued)

that must yield high throughput. We explore novel hardware techniques to compute BWT. Our techniques are based on using a limited length of suffixes, a parallel suffix sorter, and an efficient First-In-First-Out (FIFO) memory pipeline to sort these suffixes. The hardware complexity analysis shows that our technique scales linearly with the length of string and the claim is verified by the hardware synthesis results. In terms of performance, our technique outperforms the existing hardware-based techniques by over four times.

Fourth, a novel, FPGA-based, highly pipelined and scalable architecture (*MedianPipe*)for median filtering has been proposed. Median filters and its variants are widely used for noise suppression in image processing. All variants of median filter depend on the computation of median values. *MedianPipe* is a highly pipelined architecture and hence an ideal fit for FPGAs. Multiple *MedianPipe* modules are used depending on the size of image slice. The overall hardware complexity of proposed architecture scales linearly with image-slice size. The architecture for *MedianPipe* is based on the principle of merge sort and uses a median window of size 3 x 3. Without loss of generality, the pixels of an image slice are assumed to be read in a column major format. All the median values within the column of the image slice can be computed in parallel using multiple *MedianPipes*. The computation of median values in the following column is delayed by a clock cycle. Hardware resources scale linearly by varying the number and size of pixels. The pixel rate achieved for various pixel sizes is well above 124 MHz which is the standard for 1080p High-Definition.

Finally, the thesis is concluded by suggesting future directions for research based on the proposed solutions.

## CHAPTER 1

### INTRODUCTION

Processors had an enormous performance gain in 1990s and early 2000s due to the steady increase in clock frequency. Technology issues like power consumption, heat dissipation, leakage currents and signal propagation delays limit the increase in clock frequency beyond certain limits. Apart from clock frequency, another front for improving the performance of processing systems was to introduce parallelism at instruction level. But due to high data and control dependency of instructions in a program, instruction-level parallelism cannot solely be relied upon to achieve high performance demands in future. By exploiting parallelism at the threadand data-level, and employing multiple low frequency processing cores with higher power efficiency enabled the processing systems achieve high-performance demands. In the multi/many core era, the performance improvement is achieved using multiple, relatively simple cores instead of single complex processor and by expressing the parallelism in the code itself. Although the performance of the processing systems is increasing, computational demands of research, software development and scientific computing are also becoming more complex.

#### 1.1 Heterogeneous Computing Platforms

Due to the performance and power limitations of the high-end processors, heterogeneous computing platforms have gained popularity in recent years. Since no processing core is an ideal fit for all computational tasks, the focus has shifted towards designing systems to achieve better

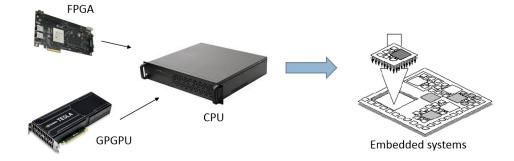

Figure 1. Heterogeneous Computing platform

performance for certain work loads. Computationally intense applications are mapped on to dedicated hardware solutions based on platforms like ASICs, GPUs and FPGAs. Owing to the ability of these solutions to provide orders of magnitude higher performance compared with the optimized implementations on general purpose processor cores at a lower power consumption (9), the use of these dedicated hardware accelerators is increasing in all fronts of complex computing. The performance, power and cost benefits at running complex tasks are outweighing the inherent disadvantage of additional programming effort required. A summary of comparison between general CPU-based and dedicated hardware solutions is given in Table I.

#### 1.1.1 Design Space for Heterogeneous Computing Platforms

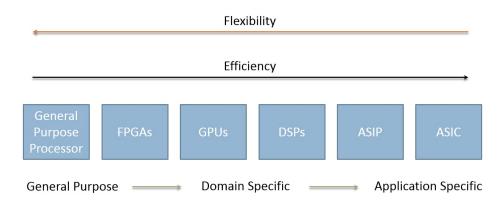

Design space for heterogeneous computing platforms can be roughly represented as shown in Figure 2. General purpose processor (or CPU) is the most flexible computing platform capable of running software for any application. But this flexibility comes at the cost of efficiency. Application software is executed in the form instructions and performance is improved

## TABLE I

# COMPARISON BETWEEN DEDICATED HARDWARE AND CPU BASED SOLUTIONS

| Metric               | Dedicated hardware solution           | CPU based                 |

|----------------------|---------------------------------------|---------------------------|

| Performance          | - Memory bandwidth dedicated for data | Limitations:              |

|                      | - No control latencies due to jump    | - Dark Silicon            |

|                      | and branch                            | - Clock frequency Scaling |

| Ease and Flexibility | Improved in recent years              | Better                    |

| of Programming       |                                       |                           |

| Energy-efficiency    | Better in term os total energy        |                           |

| Cost                 | GPUs and FPGAs have bridged the gap   | Better                    |

by adding parallelism at Instruction, Data, Thread and Core level. As we move towards the right in Figure 2, computing platforms become less flexible but more domain-specific. FPGAs are reconfigurable devices that are capable of implementing high-performance, power-efficient application-specific custom implementations for the application at hand. The added flexibility of reconfigurability in these platforms give them an additional benefit compared to all other computing platforms. GPUs, in general, have greater computing power compared to FPGAs and CPUs. Compared with CPUs, instead of having extensive logic for flow-control and data caching, a bulk of processing nodes are added that makes them an ideal fit for computationally intense parallel tasks. Digital Signal Processors (DSPs) have domain-specific instruction set and specialized associated hardware. Flexibility is lower compared with CPUs and GPUs because writing application software requires detailed knowledge about the underlying hardware. Application-Specific Instruction set Processor (ASIP) has customizable instruction set where ASIP designer not only defines a part of instruction set but also the hardware associated for these custom instructions. Application Specific Integrated Circuits (ASIC) on the extreme are application-specific, fixed and non-flexible solutions that have the best power, form-factor and performance efficiency compared with other computing platforms. Since the architecture is fixed any change in application at hand requires redesign of ASIC. Cost and time of the overall design cycle for ASICs is one major concern for solutions based on ASICs.

### 1.1.2 Heterogeneous Computing Architectures in Embedded Systems

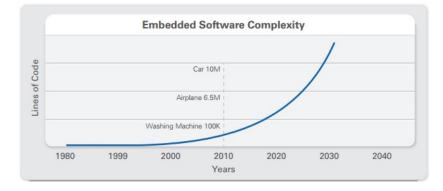

Complexity of embedded software has been increasing tremendously in recent years (Figure 3) and hence the performance expectations from embedded systems are also increasing. For

Figure 2. Design Space for Heterogeneous Computing platforms

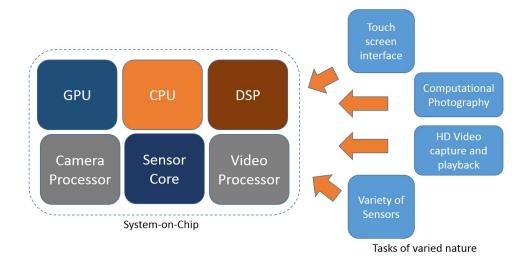

example, in mobile devices, a processing unit has to serve an increasing number of varied applications like computational photography, High-Definition (HD) video capture and playback, interface with touch-screen and other wide range of sensors. As most of these applications are expected to run in parallel, a single Central Processing Unit (CPU) cannot serve all these applications efficiently.

In recent years, mobile devices employ System-on-Chip (SoC) based processing units that have application-specific solutions for various classes of applications. An example of one such SoC is *snapDragon* from Qualcomm (10) that utilizes dedicated processing cores for graphics processing, sensor interfacing, computational photography and video playback as shown in Figure 4.

The growth of embedded systems is much higher compared with other computing platforms like desktop computers (11). As the future of computing is shifting towards embedded systems

Figure 3. Complexity of Embedded Software. Source: (1)

and the increased reliance of embedded systems on heterogeneous SoCs indicate the great importance of heterogeneous architectures in computing in future.

#### 1.2 FPGAs as a High-performance Computing Platform

FPGAs were traditionally used for prototyping. Due to the improvement in VLSI technology coupled with FPGAs inherent configurable nature attracted their use in acceleration of compute and data intense applications. Reconfiguration allows the architecture to adapt according to the change in computation demands. Another advantage of FPGAs is their lower power consumption compared to GPUs.

Some of the major factors that allow FPGAs to achieve hardware acceleration compared to general-processor based software solutions are (12):

• Compared with traditional processor based system there is no need for fetching instructions from the memory and hence memory bandwidth is completely allocated for data

Figure 4. Example of heterogeneous SoC architecture for mobile devices

- Parallelism can be achieved by generating multiple copies of processing units. Compared to software technique, this can be viewed as loop unrolling.

- Straight-forward implementation of basic blocks of codes incurs no additional delays

- There are no latencies related to the control instructions like jumps and branches. Datapaths and control units are implemented in hardware that select the output based on control logic

### 1.2.1 Programmability

Compute Unified Device Architecture (CUDA) and OpenCL are the two major programming frameworks for GPUs. These programming frameworks provide abstraction from the underlying hardware. For FPGAs, Hardware Description Languages (HDLs) Verilog and VHDL, are the two main tools for describing custom hardware. In recent years, FPGA vendors have provided support for high level languages such as Impulse C, Handel C and Mitrion C (13). Lately, FPGA vendors have also provided support to program FPGA platforms using selected features of the OpenCL programming framework. Efforts have also been made to standardize various aspects, like interfaces, in reconfigurable computing and various communities like OpenFPGA (14) and Center for High-Performance Reconfigurable Computing (15) have been developed for this purpose. The standardized interfaces would allow easy interfacing of FPGA solutions to any system.

Considering the advances in hardware and the programmability of FPGAs along with promise of high performance-to-power ratio motivates energy-efficient and high-throughput hardware solutions for a wide range of complex computational tasks on FPGAs. We look at some of the areas of applications for the hardware accelerators.

#### 1.2.2 Application domains

This section provides overview of some domains that benefit from the hardware accelerators.

#### **Big-Data Processing in Data centers**

FPGAs have been successfully used in data-centers to accelerate Big-data services in data centers. Microsoft's Catapult project (16) explored the use of FPGAs to improve performance and power-efficiency of various tasks in the data centers. Since GPUs are also capable of providing massive parallelism, their use was also explored but the high power consumption of current high-end GPUs made them unfit for conventional data-centers. Also, latency-sensitive ranking tasks mapped better on FPGAs compared to GPUs. A medium scale FPGA deployment resulted in 95% increase in throughput of ranking workload compared with software solution and added only 10% overhead in power consumption and less than 30% overhead to cost of individual server. The study concluded FPGAs to be a viable path forward towards continued improvement in cost and capability of servers especially considering the power and technology barriers in high-end processors.

#### Internet of Things

Deployment of IoT implies massive increase in the number of devices communicating with each other as well as with the data centers through network communication infra-structure. This will result in massive increase in the computing performance and power requirements in the data centers. As discussed earlier, FPGA based solutions have already proved to be viable path in improving the performance of data centers. At the network communication level, there will be a tremendous increase in bandwidth requirements and hence higher need of energy-efficient network communication and security. FPGAs being energy-efficient and highperformance computational device, is capable of playing a significant part in improving the network communication and security. At the device and IoT gateways level, power-efficient compute solutions will be required especially for the battery operated devices. Considering the reconfigurable nature and low-power requirements of FPGAs, they are capable of playing significant role at this level also. The promise of FPGAs at the node level is well-recognized by tech industry giants. Intel, in 2014, announced an Atom-FPGA hybrid to target the IoT applications (17).

#### **Computer Network Security**

The scale of computer networks have been increasing continuously and rapidly. The future with IoT, due to the addition of high number of heterogeneous devices, protocols and network traffic, would necessitate the use of fast, real-time network security techniques. FPGAs have already been found useful in real-time security of Computer Networks using Deep Packet Inspection for intrusion detection (18). Their use in network security is expected to increase manyfold.

### **Digital Signal Processing**

Advances in hardware accelerator technology have extensively expanded the application domain in Digital Signals Processing (DSP). The functional efficiency of hardware and programmability of software renders configurable platforms like FPGAs attractive to be used in wide range of DSP applications including video, audio, speech and control. Due to the abundance of programmable logic, various functional units of DSP systems can be directly realized in hardware. Fine-grained parallelism, which is often required for high-sampling rates and distributed computing in DSP applications, can also be extracted utilizing the abundant configurable logic available. FPGA based designs should be highly pipelined in order to achieve better clock frequency. Many operations in DSP applications, like image and speech processing, are capable of being highly parallelized and pipelined. This renders FPGAs a naturally suited platform for such applications (19).

Recent advancements in FPGA architecture to include special hardware for floating point arithmetic (20) has helped FPGAs overcome the earlier disadvantage of handling the floating point arithmetic. The added hardware is highly pipelined that allows FPGAs to operate at high clock frequencies.

### **Computational Biology**

The volume of available genetic data is doubling every six months (21) and hence the conventional computing systems have not been able to to keep up. Sequence alignment is one such computationally intense application in computational biology that has benefited from hardware accelerators. Smith Waterman algorithm is one fundamental sequence alignment algorithm that is implemented using dynamic programming and has a quadratic computational complexity in software. When implemented in hardware, it achieves linear computational complexity due to the massive parallelism provided by the FPGAs (21).

### Sensor Systems and Sensor Networks

In sensor systems, the sensors having capabilities such as self-diagnostics and decisionmaking are called smart sensors. Smart sensors are sometimes implemented using a embedded FPGA-based device and benefit from the small size, low power consumption and high computational accuracy of FPGA based devices (22). Other applications of FPGA include Wireless Sensor Networks (WSNs) where they are used for reducing the amount of data-transmissions and providing flexibility at the sensor node (22).

### 1.3 Contributions

This thesis reaffirms the tremendous potential of targeted hardware accelerators to provide high-performance and energy-efficient solutions to a wide range of data, memory and compute intense tasks in various application domains. Some key contributions are listed below:

- 1. A novel memory-optimized and power-efficient architecture to accelerate the memory and compute intense re-gridding process in NuFFT (23; 24): Re-gridding step is known to be the most time-consuming task (over 90 % of the whole process) in the computation of NuFFT. Re-gridding involves multiplication of each source point with an interpolation kernel function. Various practical trajectories were considered for the sampling of source points and high throughputs were achieved for wide range of configurations. Compared with GPU implementations, comparable throughputs were achieved at much lower power consumption. In addition to targeting arbitrary trajectory, proposed architecture was extended to target known trajectories in MRI and SAR applications. Compared with existing FPGA based techniques, up to 15 times better power efficiency was achieved in terms of MFLOPS/Watt at up to 7.35 times the throughput. Compared with GPU based technique, up to 9.6 times better power efficiency was achieved at comparable throughput.

- 2. A novel and hardware efficient architecture for matrix inversion (25): The architecture targets Gauss-Jordan elimination method for matrix inversion and is based on normalizing multiple rows in an iteration benefiting from the pipelined nature of floating point blocks and thereby reducing the number of multiplication units required. This results in 80% reduction in hardware resources for floating point computational logic compared to the existing pipelined implementation. The proposed architecture also provides better scalability and hardware efficiency at comparable performance. An analytical model was also developed for the proposed architecture as well as a scalable version for the architecture proposed in (7).

- 3. A high-performance hardware technique for the computationally intense Burrows-wheeler-Transform (26): The use of Burrows-Wheeler Transform (BWT) in real time applications requires efficient hardware implementations that must yield high throughput. A high performance hardware technique to compute BWT on an FPGA has been proposed. The hardware and time complexity of the proposed technique scale linearly with the length of input string.

- 4. A highly pipelined FPGA based architecture for median filtering (27): Various variants of median filters have been a key component for noise reduction in image processing. Median filter is the core process in all these variants. Efficient hardware implementations of median filter is hence highly desirable. A highly pipelined architecture for median filtering has been proposed as part of this thesis. The proposed architecture scales linearly with hardware resources and pixel sizes and achieves Pixel rates higher than those required for standard 1080p HD video.

### 1.4 Thesis organization

Chapter 2 introduces NuFFT and its applications followed by the description of the griding algorithm used in the computation of NuFFT. The proposed architecture for known and arbitrary trajectories, is described by explaining various functional components and the dataflow. Verilog and OpenCL based Experimental setup is described. At the end of the chapter, comparison between optimized Verilog and OpenCL based solution is made and the proposed architecture is compared with GPU and other FPGA based solutions. Chapter 3 describes hardware-efficient architecture for Gauss-Jordan based Matrix Inversion. It also gives an analytical model for the proposed architecture and some related work for comparison purposes.