## Design of a Frequency Counter for Mass-sensing Film-Bulk Acoustic

Resonators

BY

VALENTINO ZEGNA BARUFFA Laurea, Politecnico di Torino, Turin, Italy, 2012

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2014

Chicago, Illinois

Defense Committee:

Igor Paprotny, Chair and Advisor Alan Feinerman Claudio Passerone, Politecnico di Torino To my grandfather,

the best man I've ever known.

## ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor Prof. Igor Paprotny, for his guidance throughout this work. His constant support has been of fundamental importance in order for me to accomplish my research goals.

My deepest gratitude also goes to my advisor Prof. Claudio Passerone at Politecnico di Torino, who gave me the possibility to undertake this research work at UIC.

A special thanks goes to my laboratory mates of the Micromechatronic Systems Laboratory, in particular Emmanuel Onyema, for the help they gave me during my year in Chicago.

Eventually, I would like to thank my family and my friends from the bottom of my heart, for the unwavering support they always gave me during this experience in the United States.

VΖΒ

# TABLE OF CONTENTS

| CHAPTI   | ER             |                                                | PAGE             |

|----------|----------------|------------------------------------------------|------------------|

| 1        | INTRO          | DDUCTION                                       | 1                |

| <b>2</b> | FREQ           | UENCY COUNTER BASICS                           | 5                |

|          | 2.1            | Direct Frequency Counter                       | 5                |

|          | 2.2            | Input Considerations                           | 8                |

|          | 2.3            | Time Base Oscillator Considerations            | 11               |

|          | 2.4            | Frequency Measurement Error Analysis           | 15               |

| 3        | DOWN           | N-CONVERSIONS TECHNIQUES                       | 19               |

|          | 3.1            | Prescaling                                     | 20               |

|          | 3.1.1          | Prescaler Topologies                           | 22               |

|          | 3.2            | Heterodyne Conversion                          | 27               |

|          | 3.2.1          | Passive Mixers                                 | 32               |

|          | 3.2.2          | Active Mixers                                  | 34               |

|          | 3.2.3          | Mixer Performance Metrics                      | 35               |

| 4        | FBAR           | FREQUENCY MONITOR DESIGN                       | 41               |

|          | 4.1            | Overall System's Functionality                 | 41               |

|          | 4.2            | Microcontroller Section                        | 45               |

|          | 4.3            | Input Conditioning Stage                       | 54               |

|          | 4.4            | UART-RS232 Section                             | 60               |

|          | 4.5            | Prescaler Front-End Section                    | 65               |

|          | 4.6            | Mixer Front-End Section                        | 71               |

|          | 4.7            | Power Management                               | 82               |

| 5        | EXPE           | RIMENTAL DATA AND VERIFICATION                 | 94               |

|          | 5.1            | Errors And Calibration                         | 94               |

|          | 5.2            | Input Sensitivity And Frequency Bandwidth      | 99               |

| 6        | PRESC<br>PARIS | CALING COUNTER VS. HETERODYNE COUNTER CO<br>ON | <b>M-</b><br>104 |

| 7        | CONC           | LUSIONS                                        | 109              |

|          | CITED          | DLITERATURE                                    | 111              |

|          | VITA .         |                                                | 113              |

# LIST OF TABLES

| TABLE |                                                                            | PAGE |

|-------|----------------------------------------------------------------------------|------|

| Ι     | TYPICAL ERRORS SPECIFICATIONS OF THE FOUR TYPES<br>OF OSCILLATORS          | 15   |

| II    | FUNCTION TABLE FOR MC12080                                                 | 68   |

| III   | FUNCTION TABLE FOR MC12093                                                 | 69   |

| IV    | POWER SUPPLY CURRENT FOR DIFFERENT ICS                                     | 84   |

| V     | RESOLUTIONS FOR DIFFERENT DEVICES AND GATE TIMES                           | 90   |

| VI    | NUMBER OF MEASUREMENTS PER HOUR, BASED ON SLEEP<br>TIME AND MEASURING TIME | 91   |

| VII   | HETERODYNE VS. PRESCALING COUNTER SPECIFICATIONS<br>COMPARISON             | 106  |

| VIII  | DESIGN SOLUTION 1                                                          | 107  |

| IX    | DESIGN SOLUTION 2                                                          | 108  |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                | PAGE |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | Schematic drawing (top view) of the air-microfluidic channels of our MEMS PM sensor. The channels are shown in dark grey, while the through-wafer holes are in black [1].      | 2    |

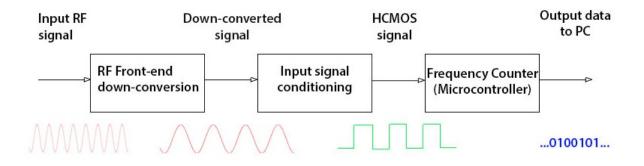

| 2      | Block diagram of FBAR frequency monitor                                                                                                                                        | 3    |

| 3      | Basic block diagram of a frequency counter [5]                                                                                                                                 | 6    |

| 4      | Major elements of a counter's input circuitry [5]                                                                                                                              | 8    |

| 5      | AC coupling is used to remove the DC content of the input signal, if present [5]                                                                                               | 9    |

| 6      | The signal is counted if and only if it crosses both boundaries of the hysteresis window. In this way, any noise present on the input signal cannot cause false triggering [5] | 10   |

| 7      | Equivalent circuit of the crystal [5]                                                                                                                                          | 12   |

| 8      | Effect of aging on frequency stability [5]                                                                                                                                     | 14   |

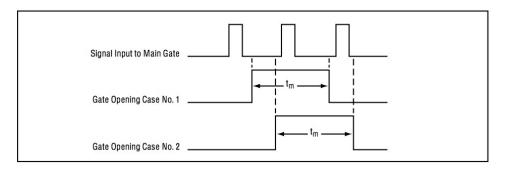

| 9      | The same gate time $t_m$ may provide different readings because the input signal is not synchronized with the main gate signal [5]                                             | 16   |

| 10     | Block diagram of prescaling counters [5]                                                                                                                                       | 21   |

| 11     | Johnson counter, 1:2 prescaler [7]                                                                                                                                             | 22   |

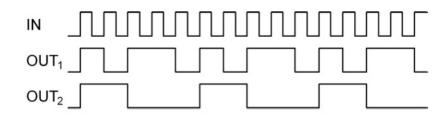

| 12     | Timing diagram for Johnson counter [7]                                                                                                                                         | 23   |

| 13     | 1:3 prescaler [7]                                                                                                                                                              | 23   |

| 14     | Timing diagram for 1:3 prescaler [7]                                                                                                                                           | 24   |

| 15     | Modulo-2/3 dual-modulus prescaler circuit [7]                                                                                                                                  | 25   |

| 16     | Modulo- $4/5/6/7$ 2-bits prescaler circuit [7]                                                                                                                                 | 26   |

# LIST OF FIGURES (Continued)

# **FIGURE**

# PAGE

| 17 | Timing diagram for modulo- $4/5/6/7$ prescaler in 1:5 mode [7]             | 27 |

|----|----------------------------------------------------------------------------|----|

| 18 | Block diagram of the heterodyne down-converting counters                   | 28 |

| 19 | The mixing process                                                         | 29 |

| 20 | Definition of down-conversion and up-conversion [14]                       | 31 |

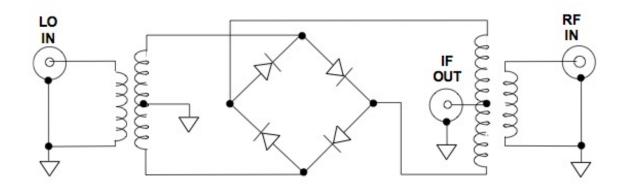

| 21 | Double-balanced diode-ring mixer.                                          | 33 |

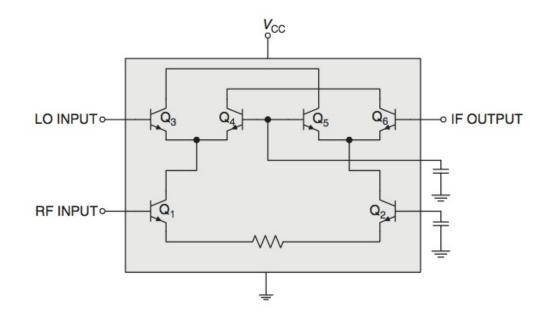

| 22 | A simplified depiction of a Gilbert cell integrated mixer                  | 34 |

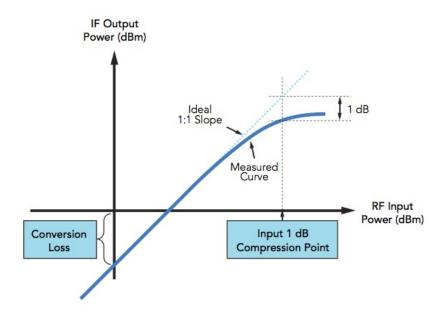

| 23 | Graphical representation of 1 dB compression point [14]                    | 37 |

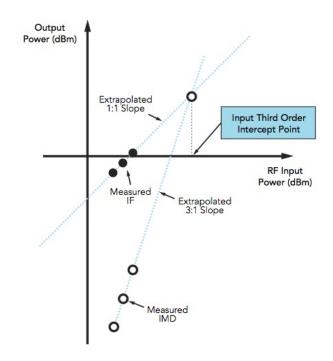

| 24 | Graphical representation to derive input third order intercept point [14]. | 40 |

| 25 | Block diagram of the frequency counter system.                             | 42 |

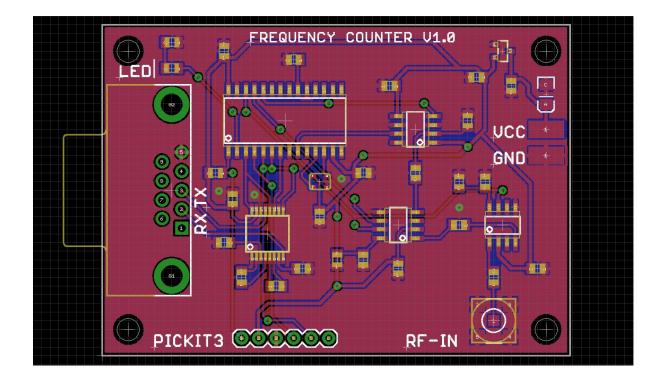

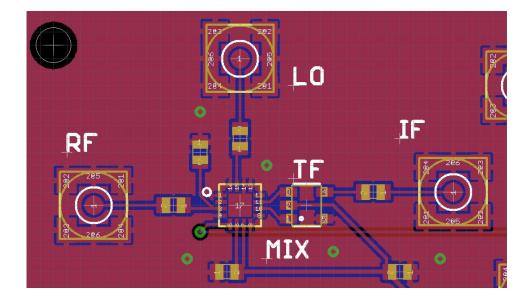

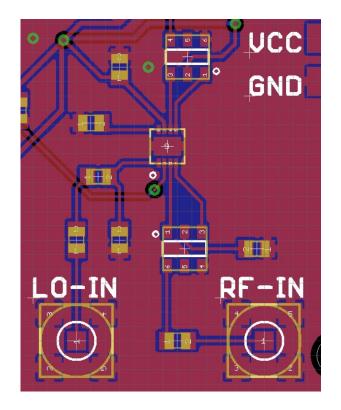

| 26 | PCB layout of the frequency counter with down-converting prescaler         | 44 |

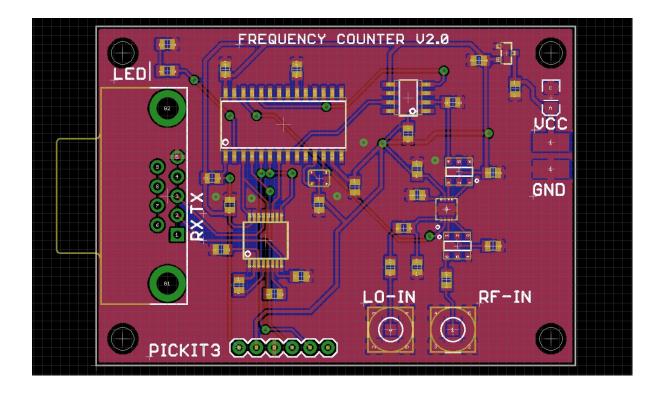

| 27 | PCB layout of the frequency counter with down-converting mixer             | 45 |

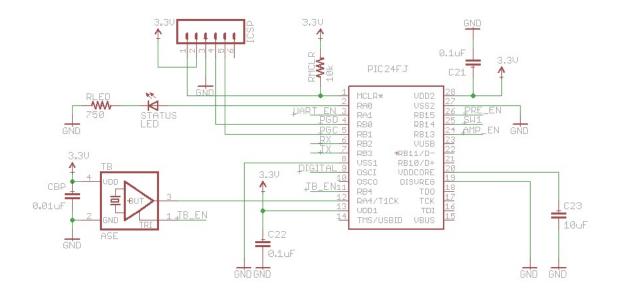

| 28 | Microcontroller section schematic                                          | 46 |

| 29 | Power supply section schematic                                             | 46 |

| 30 | Microcontroller PCB layout.                                                | 47 |

| 31 | Power supply PCB layout.                                                   | 48 |

| 32 | 16-bit Timer1 module block diagram                                         | 50 |

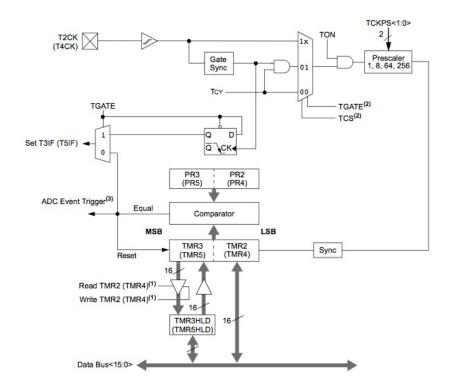

| 33 | 32-bit Timer2/3 module block diagram                                       | 53 |

| 34 | Basic comparator model                                                     | 55 |

| 35 | MAX941 in non-inverting comparator configuration.                          | 57 |

| 36 | MAX941 output stage circuitry                                              | 58 |

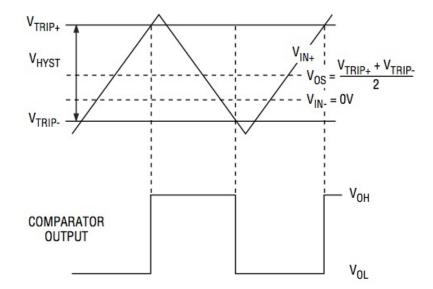

| 37 | MAX941 input and output waveforms, with hysteresis                         | 59 |

## LIST OF FIGURES (Continued)

PAGE

FIGURE

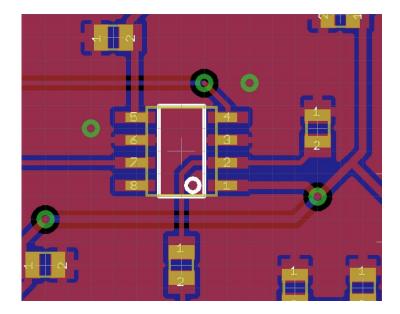

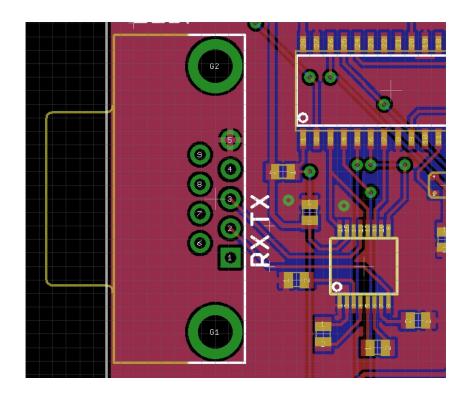

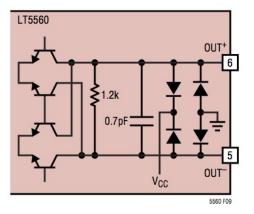

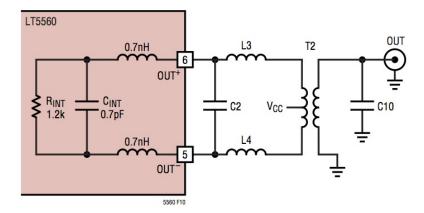

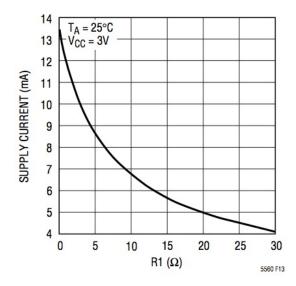

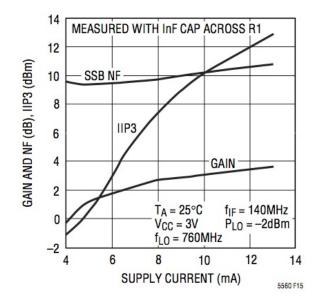

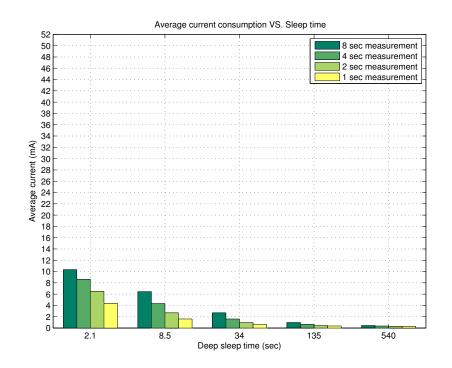

#### MAX941 PCB layout. Typical operating circuit with MAX3221 transceiver. MAX3221 PCB layout. Typical operating circuit with MC12080 prescaler. Composite prescaler made with two MC12093 ICs in cascade configuration. PCB layout for MC12080 prescaler. PCB layout for MC12093 prescaler. Schematic for down-converting application (1MHz-20MHz IF) with LT5522. Schematic for down-converting application (1MHz-20MHz IF) with LT5560. RF input schematic for LT5560 [20]. LO input schematic for LT5560 [20]. IF output small-signal model with external matching for LT5560 [20]. Typical supply current vs. R1 value [20]. 900MHz down-converting mixer gain, noise figure and IIP3 vs. supply PCB layout for LT5560 mixer. Power management effect on average power supply current consumption. Average current consumption VS. deep sleep time simulation, for heterodyne counter. Average current consumption VS. deep sleep time simulation, for prescal-

# LIST OF FIGURES (Continued)

# FIGURE

# PAGE

| 58 | Frequency stability specifications for the Abracon ASTX-H11 [21]                                                         | 94  |

|----|--------------------------------------------------------------------------------------------------------------------------|-----|

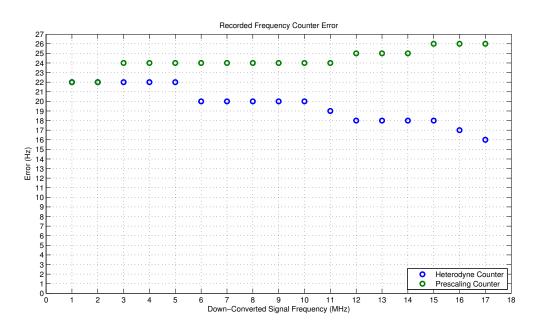

| 59 | Recored FBAR frequency monitor error. The plot shows the error for a 1 second measurement, averaged over 10 measurements | 98  |

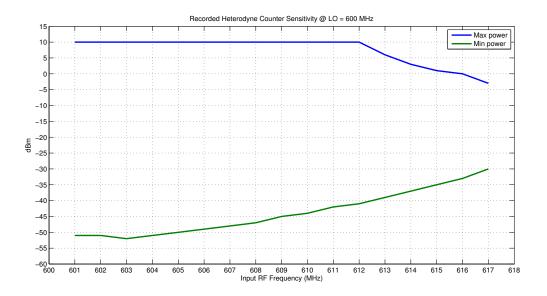

| 60 | Recorded input sensitivity for heterodyne counter @ $\mathrm{LO}=600$ MHz                                                | 101 |

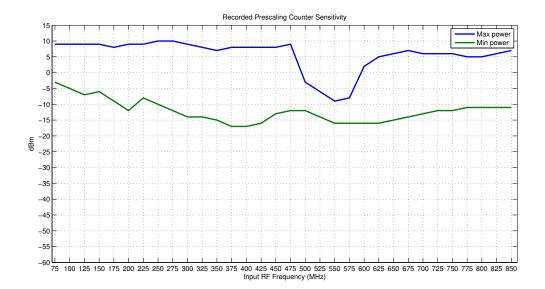

| 61 | Recorded input sensitivity for prescaling counter.                                                                       | 102 |

# LIST OF ABBREVIATIONS

| PM   | Particulate Matter                         |  |  |

|------|--------------------------------------------|--|--|

| FBAR | Film Bulk Acoustic Resonator               |  |  |

| MEMS | Microelectromechanical Systems             |  |  |

| RF   | Radio Frequency                            |  |  |

| AC   | Alternate Current                          |  |  |

| DC   | Direct Current                             |  |  |

| RTXO | Room Temperature Crystal Oscillator        |  |  |

| TCXO | Temperature Compensated Crystal Oscillator |  |  |

| OCXO | Over Controlled Crystal Oscillator         |  |  |

| IC   | Integrated Circuit                         |  |  |

| DBM  | Double-Balanced Mixer                      |  |  |

## SUMMARY

Particulate matter (PM) is a kind of air-borne pollutant to which smog, diesel exhaust, dust and smoke belong. Fine particle  $(PM_{2.5})$  pollution is especially damaging to our health. Due to their small size these particles can lodge into the alveoli by deeply penetrating into our respiratory system, contributing to several health problems such as reduced lung functionality, bronchitis, and heart attacks. While there is increasing demand for  $PM_{2.5}$  monitoring, the prevailing equipment is fairly bulky and expensive, which limits the possibilities for widespread, fine granularity sensing. Portable PM sensors are needed to allow for better identification of pollution sources, health awareness, and pollution control. In order to achieve this goal a MEMS air-microfluidic sensor is used, which measures the concentration of the particulates by the rate of the frequency shift of a mass-loaded film bulk acoustic resonator (FBAR). As particles are deposited onto the exposed surface of the resonator, the additional mass lowers its resonant frequency[1]. The main goal of this dissertation thesis is to design and realize a very low power portable RF frequency counter which operates with the MEMS air-microfluidic sensor in order to correctly measure the concentrations of airborne PM. The whole design is realized on a PCB board and it is specifically designed for small form factor and low power so that it can be seamlessly integrated with a mobile device such as a smartphone or a laptop.

## CHAPTER 1

#### INTRODUCTION

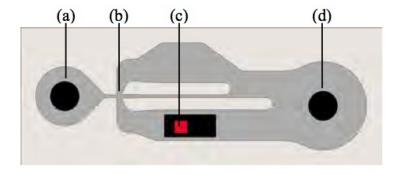

The goal of this dissertation thesis is to design a portable, low cost frequency counter which can operate at very low power with an input signal coming from a FBAR resonator which senses PM in the atmosphere. Nowadays, higher spatial density monitoring is needed due to the increasing awareness of the negative health impacts of PM. Commercially available PM sensors are expensive and have a large form factor, which does not allow integration into a portable device designed to perform personal PM exposure level monitoring. The MEMS PM sensor developed by Paprotny et al.[1] is about two orders of magnitude smaller than any commercially available PM sensor: this enables easy integration into a portable platform for personal  $PM_{2.5}$ monitoring. The schematic drawing of Figure 1 shows the functions of our MEMS PM sensor. The main goal of the air channels (shown in dark grey) is to separate the airflow into two airflows, one containing particles with aerodynamic diameter smaller than 2.5  $\mu$ m (fine particles) and the other one containing particles with a larger aerodynamic diameter (coarse particles). This is achieved since air enters into the channels through the inlet (a), then the inertial size separator (b) (also called VI) divides particles by size. The coarse particles are ejected through the exhaust (d), while fine particles are removed from the airstream by thermophoresis and deposited on the exposed surface of a mass-sensing FBAR (c). The concentration of  $PM_{2.5}$  particles in the airstream can be inferred by the rate of change in the resonant frequency of the FBAR: this is made possible by the fact that the  $PM_{2.5}$  concentration in the airstream is proportional to the rate of particle deposition onto the FBAR.

Figure 1. Schematic drawing (top view) of the air-microfluidic channels of our MEMS PM sensor. The channels are shown in dark grey, while the through-wafer holes are in black [1].

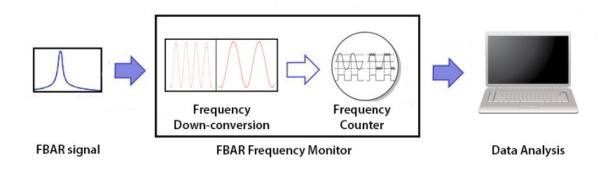

The signal coming from the PM sensor has been measured to have a central frequency of about 611 MHz, with output power -5 dBm. This frequency is subjected to change when the FBAR is mass-loaded and it senses  $PM_{2.5}$  particulates in the environment. What we are interested in is to measure this frequency shift, which will tell us what is the pollution rate of change with respect to time in the environment under test. In order to achieve this goal we need to design a frequency counter, whose task is to collect frequency measurements of the PM sensor signal. The collected data will be sent to a laptop, in order to be analyzed and visualized on a graphical display. Since the frequency coming from the sensor is centered around 611 MHz, a direct frequency counting is not feasible with cheap and low-power ICs because these circuits cannot work at such high frequency. In order to perform a high frequency measurement it is necessary to have a RF down-conversion front-end which must be placed between the PM sensor and the actual frequency counter. Doing so, the bandwidth of a cheap and low-power frequency counter can be extended to a much higher one and the signal can be easily counted. The overall FBAR frequency monitor block diagram is shown in Figure 2.

Figure 2. Block diagram of FBAR frequency monitor.

As we can see, the FBAR frequency monitor is composed of two main blocks: the first one is the front-end which reduces the input signal's frequency, while the second one is a standard frequency counter. Our design must be low cost and low power, therefore the main device used to count the frequency is a microcontroller. As we all know, microcontrollers are devices that cannot work with signals much higher than 20 MHz, thus if we want to work with higher frequencies we need to find out a down-conversion method for reducing the input signal's frequency in order to keep it within the operating range. Hence, the main goal is to find a technique that lets us reduce the input frequency without losing the information carried by the signal and resulting in the minimum possible loss in resolution and accuracy. For this work, two popular down-conversion techniques have been implemented and tested in the final devices: prescaling and heterodyne conversion. Prescaling is a technique that involves dividing the frequency of a signal by means of a *prescaler*, which can be found as an integrated circuit (IC). Heterodyne conversion is a more complex technique that makes use of a *mixer* in order to take the sum and the difference of two input frequencies: the first input frequency is the frequency to be counted, while the second one is provided by a stable and high quality local oscillator. By choosing the appropriate frequency for the local oscillator, one can down-convert the RF input signal frequency within the operating range of the actual frequency counter. We will highlight the strengths and weaknesses of the two down-conversion methods described above, with focus on comparing them in order to find the best solution for our specific application. The design space will be explored in order to find the solution that meets the desired power-constraints without losing accuracy and resolution, keeping the price as low as possible in order for the device to be affordable for the average consumer.

## CHAPTER 2

## FREQUENCY COUNTER BASICS

RF frequency counters and timers are digital electronic devices which measure the frequency of a RF input signal. They operate by counting the number of events within a well known period or by measuring a period by counting the number of some precisely timed events. A very stable quartz crystal oscillator is usually used to generate the time periods within which events are counted, or the precisely timed events. Nowadays it is possible to find simple frequency counters, designed with state-of-the-art digital components, that can measure frequencies up to 500 MHz by exploiting a direct counting approach[4]. In the following sections we are going to analyze and compare the two main counting techniques, which are called *direct counting* and *reciprocal counting*.

#### 2.1 Direct Frequency Counter

The direct frequency counter exploits a *direct counting* approach in order to perform related frequency measurements. The direct counting approach is the simplest one and it was the first to be ever used for commercial counters. The frequency f of periodic signals can be expressed as in Equation 2.1:

$$f = \frac{n}{t} \tag{2.1}$$

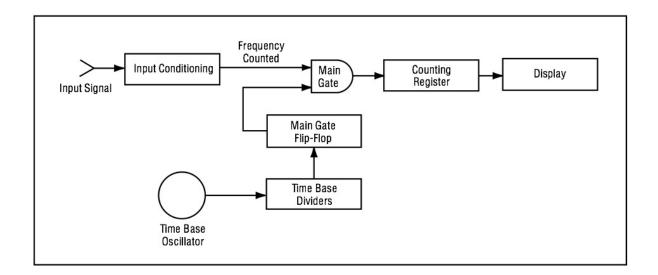

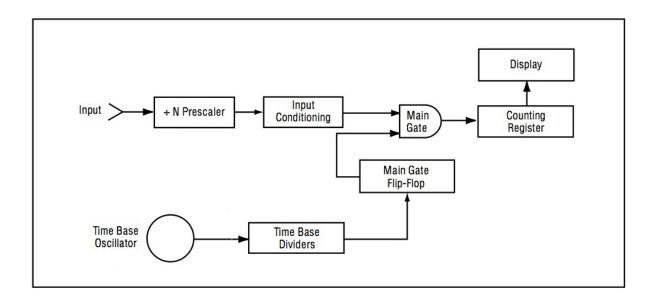

where n represents the number of cycles of the periodic signal that occur in the time interval t. Usually t is set to 1 second so that the frequency can be expressed in *cycles per second*, or *Hertz*  (Hz). More generally, the frequency of a signal is measured by counting a number of cycles and dividing it by the time interval during which the measurement has been performed. The basic block diagram of a frequency counter in direct counting configuration is shown in Figure 3.

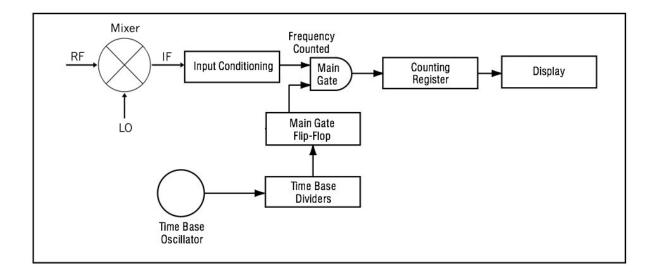

Figure 3. Basic block diagram of a frequency counter [5].

Within the conventional frequency counter we can observe several main blocks:

• *Input Conditioning*: The input signal is initially converted into a digital square wave representation in order to be compatible with the counter's internal digital circuitry. This is usually achieved by means of a Schmitt trigger circuit to avoid the generation of spurious

pulses due to noise in the input signal. Trigger levels and sensitivity are controlled within this section.

- *Time Base*: From equation Equation 2.1 it is possible to show that the accuracy and resolution of a frequency measurement is strictly related on the accuracy in which the gate time t is generated. For this reason, commercially available counters make use of a very precise crystal oscillator as the Time Base element[5]. Many low cost instruments can be used with a higher quality external oscillator for improved performance, while expensive high quality instruments may be provided with an oven controlled crystal oscillator (OCXO), which is way more precise and expensive than a standard XO.

- Time Base Dividers and Flip-Flop: The Gate Time enabling signal for the Main Gate is generated by dividing the Time Base oscillator signal using the Time Base Dividers and then feeding it into a flip-flop. The time t of equation Equation 2.1 corresponds to the Gate Time. Common gate times are 0.01, 0.1, 1, and 10 seconds. Shorter Gate Times let output data to be refreshed faster, the drawback is that the counting accuracy is decreased.

- *Main Gate*: The precisely generated Gate Time signal is fed into one input of the Main Gate, while the input signal coming from the input conditioning section is fed into the second input. The resultant output from the Main Gate is a pulse train which last for a precise amount of time equal to the Gate Time itself, so that pulses are counted by the Counting Register during the time the Main Gate is kept open by the Gate Time signal.

• Counting Register: The input signal frequency is computed by taking the value stored into the Counting Register and dividing it by the selected Gate Time. For instance, if value stored in the Counting Register is 50000 and the Gate Time is 1 s, then the measured input signal frequency is 50000 Hz. The counted frequency can be visualized on a display or sent to another electronic device for further data manipulations.[5]

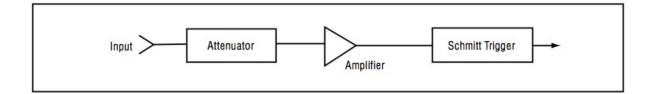

#### 2.2 Input Considerations

The input conditioning stage usually consists of some basic blocks such as an attenuator, an amplifier and a Schmitt trigger as shown in Figure 4. The attenuator and the amplifier are employed in order to fully exploit the available dynamic range, while The Schmitt trigger is employed to convert the input signal from an analog representation into a digital one compatible with the counter's internal digital circuitry. There are many critical aspects to take into account in order to properly condition the input signal, what follows next is a description of the problems that may appear and the solution to solve them.

Figure 4. Major elements of a counter's input circuitry [5].

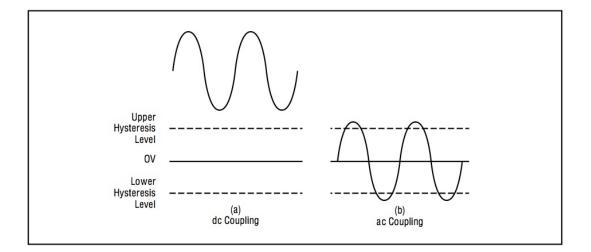

• AC-DC Coupling: Signals with a DC content can be counted only if some kind of AC coupling is provided in the input conditioning section. The effect of AC coupling is clearly shown in Figure 5.

Figure 5. AC coupling is used to remove the DC content of the input signal, if present [5].

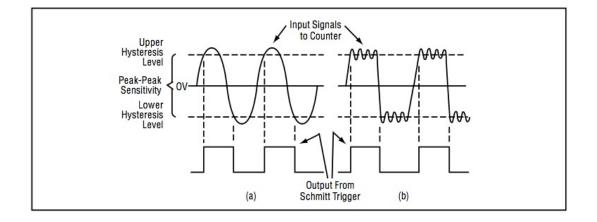

• Sensitivity: The counter's sensitivity is defined as the minimum voltage that the input signal must reach in order to be counted. The sensitivity is determined by the input impedance, the amplifier gain and the amplitude of the Schmitt trigger hysteresis window. The input sensitivity must be carefully optimized during the design process because noise on the input signal can cause false triggering if the the front end is highly sensitive. The effect of having a hysteresis level is shown in Figure 6.

Figure 6. The signal is counted if and only if it crosses both boundaries of the hysteresis window. In this way, any noise present on the input signal cannot cause false triggering [5].

• Dynamic Range: The dynamic range can be defined as the linear operating range of the input amplifier. A highly linear input amplifier is not needed since we are not interested in the waveform itself but only in its frequency. With a well designed amplifier it is not a problem to exceed the dynamic range since no false counts will take place. However, exceeding the dynamic range is not good practice since, in case of input impedance drop, the amplifier response speed could decrease due to saturation effects. Input protection

is usually provided in order to do not exceed the damaging level of the input amplifier. Conventional protection often are not enough in case of fast transients on a 50 $\Omega$  input, therefore several commercial counters are equipped with high speed fuses in order to provide further protection.

- Attenuators: The dynamic range of the input should not be exceeded, for this reason attenuators are provided for large level signals. Standard step attenuators with fixed values such as X1, X10 and X100 are usually employed for wide dynamic range inputs, even though it is also possible to find counters with variable attenuators on low dynamic range input because of their capability of variably attenuating noisy signals in order to generate an optimal signal amplitude while minimizing noise.

- Input Impedance: A 1MΩ input impedance with a sensitivity of 25 mV to 50 mV is usually preferred for frequencies up to 10 MHz because sources connected to the input will not be loaded and the 35 pF shunt capacity will have small effect. On the other hand, a 50Ω impedance input with low shunt capacity is preferred for frequencies beyond 10 MHz because the shunt capacity of high impedance inputs rapidly reduces the input impedance beyond this frequency. A sensitivity from 20 mV to 25 mV is usually employed with 50Ω inputs in order to avoid noise and related problems.

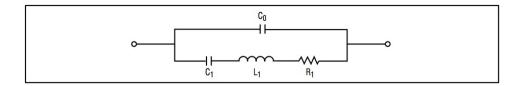

#### 2.3 Time Base Oscillator Considerations

The time base oscillator represents the source of the precise gate time t as defined in Equation 2.1. Virtually every modern frequency counter employs a quartz crystal as the oscillating element because of its good performance/price ratio. A quartz crystal oscillator can be modeled with an equivalent electrical circuit, as shown in Figure 7. The physical properties of the crystal determine the values of  $R_1$ ,  $C_1$ ,  $L_1$ , and  $C_0$ . In order to obtain a tuned circuit, an external variable capacitance is typically added. The frequency of a crystal oscillator is temperature sensitive because of the L, C and R elements.

Figure 7. Equivalent circuit of the crystal [5].

Three main families of crystal oscillators are available:

- Room Temperature Crystal Oscillator (RTXO): these oscillators have the highest frequency change over temperature. Pretty good stabilities can be achieved by choosing a proper crystal cut during the manufacturing process. Typical high quality RTXO may have a stability over temperature of about 2.5 parts per million (ppm) in the range from 0°C to 50°C.

- Temperature Compensated Crystal Oscillator (TCXO): A cheap and effective method to compensate for frequency changes due to temperature variation is to add some external capacitance or passive component to the tuned circuit, with opposite temperature coef-

ficient with respect to the internal one. A typical high quality TCXO offers an order of magnitude improvement in frequency stability with respect to a RTXO, with a frequency stability of 0.5 ppm over 0°C to 50°C.

• Oven Controlled Crystal Oscillator (OCXO): in this type of oscillator, the crystal is embedded in an oven which actively compensates for temperature variations in the environment surrounding the crystal. A typical frequency stability for a high quality OCXO may be around 0.007 ppm over 0°C to 50°C. An OCXO may take 24 hours or more after turn-on to achieve its specified stability, however most high-end counters employing an OCXO have a feature that allows the oven to be powered whenever the power line is connected even if the counter is not turned on. In this way it possible to avoid the need for the warm-up phase and retrace. This is the most precise, expensive and power hungry type of crystal oscillator, therefore it can be found only on very high-end counters.

The accuracy of the oscillator frequency can be affected by additional factors other than temperature variations, which can be defined as follows:

• Effect of Line Voltage Variations: any variation in the power supply voltage causes a variation in the oscillator frequency. The stability with respect to line voltage variation is typically expressed within 10% of line voltage variation. High quality voltage regulators are usually incorporated in the counter in order to reduce this kind of error, however very high line voltage stability is not needed since the frequency error due to line voltage variation.

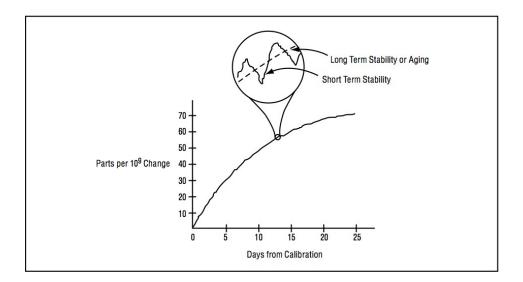

- Aging Rate or Long Term Stability: aging is a cumulative frequency drift due to the change of the physical properties of the crystal with respect to time, as shown in Figure 8, which is usually specified in terms of frequency change per month since temperature and other effects would mask the amount of aging over shorter time periods. The higher the quality of the crystal used, the lower the effect of aging.[5].

- Short Term Stability: it is related to random frequency changes and phase fluctuations present in the oscillator signal. Any specification of short term stability must include the averaging or measurement time involved since it is spectrally related. The effect of this noise is inversely proportional to the averaging (or measuring) time, so that the larger the measuring time the lower the noise.[5].

Figure 8. Effect of aging on frequency stability [5].

#### TABLE I

|                              | RTXO                             | TCXO                            | Switching OCXO                   | Proportional OCXO                |

|------------------------------|----------------------------------|---------------------------------|----------------------------------|----------------------------------|

| Temperature                  | $< 2.5 \cdot 10^{-6}$            | $< 5 \cdot 10^{-7}$             | $< 1 \cdot 10^{-7}$              | $< 7 \cdot 10^{-9}$              |

| $(0^{\circ}C - 50^{\circ}C)$ |                                  |                                 |                                  |                                  |

| Line Voltage                 | $< 1 \cdot 10^{-7}$              | $< 5 \cdot 10^{-8}$             | $< 1 \cdot 10^{-9}$              | $< 1 \cdot 10^{-10}$             |

| (10%  change)                |                                  |                                 |                                  |                                  |

| Aging                        | $< 3 \cdot 10^{-7} / mo$         | $< 1 \cdot 10^{-7} / mo$        | $< 1 \cdot 10^{-7}/mo$           | $< 1.5 \cdot 10^{-8} / mo$ or    |

|                              |                                  |                                 |                                  | $<5\cdot 10^{-10}/day$           |

| Short Term                   | $< 2 \cdot 10^{-9} \mathrm{rms}$ | $< 1 \cdot 10^{-9} \text{ rms}$ | $< 5 \cdot 10^{-10} \text{ rms}$ | $< 1 \cdot 10^{-11} \text{ rms}$ |

| (1  sec avg.)                |                                  |                                 |                                  |                                  |

TYPICAL ERRORS SPECIFICATIONS OF THE FOUR TYPES OF OSCILLATORS

All the oscillator characteristics described before are summarized in Table I, they are collected by considering typical specifications of high quality commercially available oscillators. The total time base oscillator error is computed by adding together all these individual sources of error. However, the frequency deviation due to time base error is only one of the several sources of error for a frequency counter, which are going to be described in the following section.

#### 2.4 Frequency Measurement Error Analysis

The first source of measurement error is represented by the propagation delay of the physical main gate, also called *switching time*: the time window in which the main gate is open is affected by the switching time. This error is often referred to as *switching error*. It is clear that the switching error will be significant only if the switching time is significantly large compared to the period of the highest frequency that must be counted. While the switching error can be

minimized by allowing longer times, we still have other relevant sources of errors. The most relevant sources of measurement error for a frequency counter can be summarized into the following four categories:

• Quantization Error: Any electronic counter has a  $\pm 1$  count ambiguity in the least significant digit. This ambiguity occurs because the internal clock frequency and the input signal are not coherent between each other, as shown in Figure 9. In other words, the quantization error represents the minimum input frequency change detectable by the counter. The quantization error can be expressed as:

$$Q_{err} = \frac{1}{t_m} Hz \tag{2.2}$$

Where  $t_m$  represents the gate time. A longer gate time results in a smaller quantization error. This also represents the *resolution* of the system.

Figure 9. The same gate time  $t_m$  may provide different readings because the input signal is not synchronized with the main gate signal [5].

• *Time Base Error*: Any difference between the actual time base frequency and its nominal one induces a measurement error, which is the due to the cumulative effect of all the individual time base errors described in Section 2.3 and it is expressed in parts per million (ppm).

The overall frequency measurement error  $(FM_e)$  can be expressed as the sum of the quantization error  $(C_e)$  and the time base error factor  $(TBF_e)$ :

$$FM_e = \pm C_e \pm TBF_e \ [Hz] \tag{2.3}$$

The relative frequency measurement error due to  $\pm 1$  count ambiguity for a 1 second gate time can be therefore expressed as:

$$\frac{\Delta f}{f} = \frac{\pm 1}{f_{in}} \tag{2.4}$$

Where  $f_{in}$  represents the frequency of the input signal. From Equation 2.4 it's easy to show that the relative frequency measurement error due to  $\pm 1$  count becomes smaller for high input signal frequencies. For instance, if we consider a 10 MHz input signal we can compute the relative frequency measurement error due to  $\pm 1$  count ambiguity for a 1 second gate time, which comes out to be:

$$\frac{\Delta f}{f} = \frac{\pm 1}{f_{in}} = \frac{\pm 1}{10 \cdot 10^6} = \pm 1 \cdot 10^{-7} \tag{2.5}$$

For the purpose of this example we can assume a time base error of 1 ppm, i.e.  $TB_e = \pm (1 \cdot 10^{-6})$ . If we consider again a 10 MHz input signal then the measurement error introduced by the time base will be:

$$TBF_e = TB_e \cdot f_{in} = \pm (1 \cdot 10^{-6}) \cdot 10^7 \ Hz = \pm 10 \ Hz \tag{2.6}$$

In this particular case we get that the  $\pm 1$  quantization error is masked by the time base error, which is one order of magnitude bigger. If the input frequency would be below 1 MHz then the  $\pm 1$  count error would become dominant over the time base error[5].

## CHAPTER 3

#### DOWN-CONVERSIONS TECHNIQUES

The upper limit on the frequency bandwidth of a counter is determined by the speed of the digital logic employed in the design. The designer of frequency counters must look for some kind of down-conversion techniques if it is necessary to extend the range of his counter beyond the available 500 MHz range. It is possible to find state-of-the-art commercial counters that work with very sophisticate down-conversion techniques, high-speed digital devices and extremely precise time base oscillators. Some of them can work with frequencies up to 40 GHz, giving resolutions up to 12 digits thanks to interpolation and mathematical analysis based on statistical models<sup>[4]</sup>. The main issue is that they are designed to work in a laboratory's environment, therefore they are not portable, consume a huge amount of power and are very expensive. This not a problem if the user can afford one and it is possible to connect the instrument to a main power supply, however it becomes not feasible if the main goal is to work with a cheap device that must be USB or battery-powered for low power applications. In the following sections we are going through the details of two main down-conversion techniques, which are called *prescaling* and *heterodyne conversion*. Both of them have been implemented and tested on our final devices. The PCB designs and experimental results are shown in Chapter 4 and Chapter 5, respectively.

## 3.1 Prescaling

The speed of the main gate switches and the counting registers represent an upper limit on the accuracy of a frequency measurement at high input frequencies. The simplest possible technique that is employed in order to increase the bandwidth of a frequency counter is called *prescaling*, which is simply implemented by adding a *prescaler* (also called frequency divider) in the input signal path. The prescaler is an electronic device used to divide the frequency of a high frequency signal by a factor N, thus reducing its frequency to a lower one . Modern prescalers can operate in the GHz range[6][7], obviously the upper limit in frequency that a counter can reach will be the maximum frequency at which the prescaler can operate. In a frequency counter the prescaler may condition the input signal before applying it to the main gate, as shown in Figure 10. The prescaler can also be placed before the input conditioning stage.

Figure 10. Block diagram of prescaling counters [5].

Typical modern prescaler are designed with division factors in powers of 2, usually going from 2 up to 256. With a prescaler, the frequency response of a counter can be easily increased by a factor N. However, the gate time must be N times longer in order for the counting register to accumulate the same number of counts that would be accumulated in a counter without any prescaler in the front-end. Therefore, prescaling involves a tradeoff: a slower and cheaper internal digital logic can be used, at the expense of an additional device (i.e. the prescaler) and a slower frequency measurement[5]. For instance, assume to use a direct frequency counter as shown in Figure 3. For a 1 second gate time, the quantization error will be  $\pm 1$  Hz. If a modulo-64 prescaler is placed before the counter, the quantization error for the same gate time will be  $\pm 64$  Hz. In order to get a  $\pm 1$  Hz quantization error with a modulo-64 prescaler we need a gate time of 64 seconds.

### 3.1.1 Prescaler Topologies

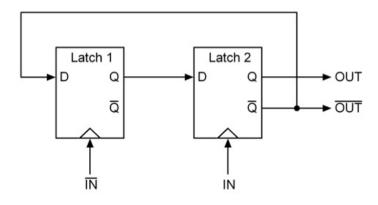

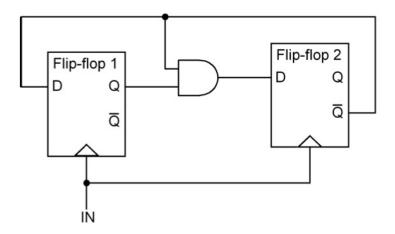

A Johnson counter is an easy and popular implementation of a 1:2 prescaler[8]. As shown in Figure 11, two D-latches are coupled in a loop and clocked by inverse clocks.

Figure 11. Johnson counter, 1:2 prescaler [7].

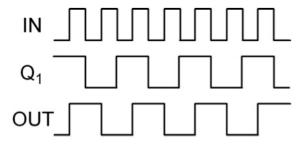

When IN goes low the signal  $\overline{OUT}$  is being transferred to the output of the first latch, and transferred further to OUT when IN goes high again. This is shown in the timing diagram of Figure 12. OUT inverts every time IN goes high, and thus the frequency is divided by two. Figure 13 shows a 1:3 prescaler circuit utilizing two flip-flops and an AND gate. Both flip-flops

Figure 12. Timing diagram for Johnson counter [7].

are being clocked at the rising edge of IN. The following logic function is obtained:

$$\overline{Q_2}(n+1) = \overline{Q_1(n)\overline{Q_2}(n)} = \overline{\overline{Q_2}(n-1)\overline{Q_2}(n)} = Q_2(n-1) + Q_2(n)$$

(3.1)

Figure 13. 1:3 prescaler [7].

As can be seen from the timing diagram of Figure 14, the circuit swallows one extra period of the input signal per output period compared to the Johnson counter.

Figure 14. Timing diagram for 1:3 prescaler [7].

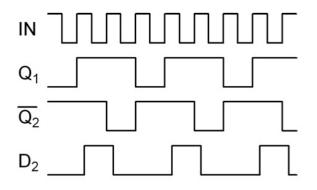

It is also possible to combine the two previous topologies in a new one which lets the user to chose between a 1:2 and a 1:3 prescaler. This is called a dual-modulus prescaler[9] and it is shown in Figure 15. This circuit divides the frequency of the input signal by either 2 or 3, depending on the logic state of the control signal M. When M is low the output of the OR-gate will be controlled directly by  $Q_1$ , and the circuit will operate in the same way as the previously described 1:3 circuit. When M is set to high the output of the OR-gate will be high independent of the output of the first flip-flop, thus the output of the first AND-gate follows  $\overline{Q_2}$ . On every rising edge of IN,  $\overline{Q_2}$  will be inverted, and thus the frequency is divided by 2.

Figure 15. Modulo-2/3 dual-modulus prescaler circuit [7].

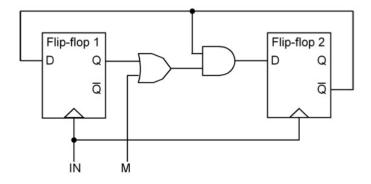

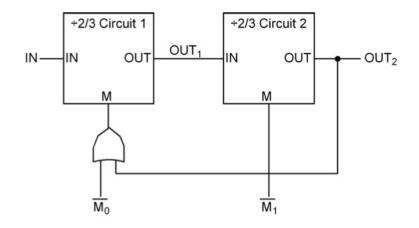

By cascading two or more dual-modulus prescalers one can obtain a multi-modulus prescaler. An example of how this can be done is shown in Figure 16. The circuit consists of two of the modulo-2/3 circuits described above coupled in series. The modulus control signals are binary weighted, so the period of the output signal will be as shown in Equation 3.2, the resulting prescaler can divide on moduli ranging from 4 to 7.

$$T_{OUT_2} = T_{IN} \cdot (2^2 + 2^1 \cdot M_1 + 2^0 \cdot M_0) \tag{3.2}$$

To achieve this there is an OR-gate on the M input of the first prescaler which allows this circuit to work in 1:3 mode only once per  $OUT_2$  period. Note that it is the inverses of the modulus control signals that are applied at the inputs, in order to achieve the given function for the output period since the cells that are used divide by 2 when M = 1 is applied and by 3 when M = 0 is applied.

Figure 16. Modulo-4/5/6/7 2-bits prescaler circuit [7].

A timing diagram for this circuit in 1:5 mode is shown in Figure 17 ( $M_1M_0 = 01$ ). This circuit can easily be extended to a *n*-bits prescaler by cascading *n* modulo-2/3 prescalers and gating the modulus control signal for each of them through an OR-gate together with the *OUT* signal from all the following modulo-2/3 prescaler circuits[7].

Figure 17. Timing diagram for modulo-4/5/6/7 prescaler in 1:5 mode [7].

# 3.2 Heterodyne Conversion

Heterodyning is a radio signal processing technique in which a new frequency is generated by mixing two frequencies[10][11][12]. With this technique, usually employed in demodulation and modulation of radio and microwave signals, it is possible to shift the harmonic content of a signal into a completely new frequency range, thus getting an output signal at a higher or lower frequency but without losing the information carried by the input signal[11]. In its simplest form, two frequencies are combined in a nonlinear device such as a diode, a transistor or a vacuum tube, usually called a mixer[12]. Figure 18 shows the block diagram of a frequency counter that exploits the heterodyne down-conversion technique.

Figure 18. Block diagram of the heterodyne down-converting counters.

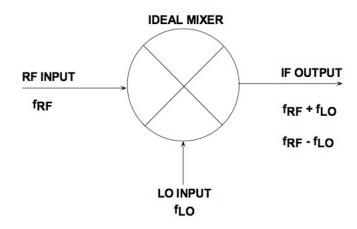

Figure 19 shows the basic diagram of an ideal mixer. A mixer has two input ports, which are called Radio Frequency (RF) and Local Oscillator (LO), and one output port called Intermediate Frequency (IF). In frequency counters, one of the two input frequencies of the mixer is provided by a high-stability local oscillator signal, while the other one is of course the signal whose frequency must be counted.

Figure 19. The mixing process.

The task of a mixer is to take the signal coming into the port RF and to mix it with the one coming into the port LO, thus producing an IF output signal. The frequency of the signal IF consists of both the sum and the difference between the two input frequencies[13], as shown in Equation 3.3.

$$f_{IF} = f_{RF} \pm f_{IF} \tag{3.3}$$

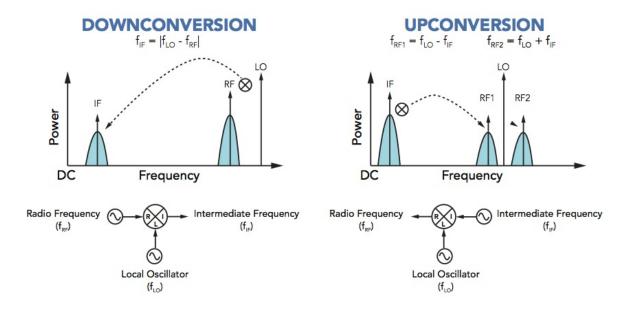

Typically, a square wave signal or a sinusoidal continuous wave (CW) signal is used to drive the LO port, depending on the particular application. The LO signal can be seen as the gate of the mixer, i.e. the mixer is active when the LO signal has a large voltage and not active when LO has a small voltage. It is possible to use the RF port either as an input or an output, depending on the mixer mode of operation. We are talking about *down-conversion* if the desired output

frequency is lower than the input one: in this case, the RF represents the second input and IF is the output. This is exactly how we desire the mixer to perform in a heterodyne frequency counter. It is also possible to use the mixer in a *up-conversion* configuration, where the output frequency is higher than the input one. In this case, IF is used as the second input and RF is the output. Figure 20 shows a spectral representation of down-conversion and up-conversion. The mixer's symbol identifies which is the input frequency. In down-conversion the input is RF, which is combined with LO, while in up-conversion the input is IF, which combined with LO provides the output up-converted frequency RF. The dashed arrow indicates in which direction the input frequency is shifted.

Figure 20. Definition of down-conversion and up-conversion [14].

As we can see from Figure 20, RF and IF have broad spectra since they are information bearing signals. When a down-frequency conversion is performed, all the information carried by RF is translated to the IF output. It is clear that mixers must be carefully designed in order to perform frequency transformations without distorting the original information carried by the input signal[14]. The strength of this technique is that there is no loss in resolution and very small loss in accuracy if the local oscillator has a very high stability, therefore an accurate frequency measurement can be obtained even when the input frequency is reduced by a big factor. Modern mixers are designed by employing Schottky diodes, GaAs FETs, BJTs and CMOS transistors. Schottky diodes are used for high performance applications while CMOS and FETs are used in high volume applications because of their lower cost and higher density[14].

### 3.2.1 Passive Mixers

Passive mixers typically use Schottky diodes as nonlinear elements, or FETs as passive switches. The most common form of mixer is represented by a single diode, where both the LO and RF signals are applied at the anode. The LO must be a strong signal that forces the diode to be open or closed, thus chopping the small signal RF. Real diodes posses some amount of turn-on transition time, moreover the diode transconductance is modulated by the RF signal (even if the RF signal is very small). Because of these issues, additional mixing products appear at the mixer output, which are called *spurs*[14]. A real diode produces all possible harmonic mixing components, both odd and even, as shown in Equation 3.4.

$$f_{IF} = N f_{LO} \pm M f_{RF} \ (N \ and \ M \ are \ all \ integers) \tag{3.4}$$

We are only interested in a single output frequency (i.e. N = M = 1) therefore te existence of all the other harmonics represents a problem. For this reason, modern high-performance mixers are designed by making use of circuit simmetry in order to create *balance*. A basic scheme of a double-balanced mixer (DBM)[13] is shown in Figure 21, which is simply a diode ring.

Figure 21. Double-balanced diode-ring mixer.

The principle of operation is exactly the same as before, where the LO signal switches the diodes ON and OFF while the RF signal is alternately sent through the diodes. DBM are commercially available as surface-mount packages, with embedded diodes and transformers[15]. Real-world DBMs reduce nearly 75% of all spurs, since only odd N and odd M harmonics reach the IF port. Hence, a balanced mixer offers several advantages like very good isolation among all ports, high conversion efficiency, common mode signal rejection and cancellation of most intermodulation products[14]. The drawback is that passive mixers don't provide any gain, instead they show a conversion loss of about 7 dB. This loss is due to the internal resistance of the diodes, port impedance mismatches and the 3 dB wasted in filtering out the undesired output frequencies[15]. DBMs can work up to 8 GHz and beyond by using Schottky diodes, therefore they are suitable for very high performance applications.

# 3.2.2 Active Mixers

The diode-ring mixer is not suitable for fabrication using integrated circuit technologies. The diodes can be replaced by four transistors, which can essentially perform the same switching function[16]. This is the basis of the Gilbert cell circuit[17], which basic scheme is shown in Figure 22.

Figure 22. A simplified depiction of a Gilbert cell integrated mixer.

The RF signal is fed into the base of Q1, while the LO signal is input into the base of Q3. The LO signal forces Q3 and Q6 in ON/OFF state while Q4 and Q5 are always turned ON. This causes the mixing of RF and LO thus generating the output IF[17]. The strong LO signal forces the transistors to operate in their nonlinear region while the small RF signal operates within their linear region. The devices of choice for Gilbert cells can be BJTs, CMOS and GaAs FETs[13], which allow these kind of mixers to be monolithically fabricated and packaged into very small surface-mount ICs. Gilbert cells commonly work with RF frequencies up to 5.8 GHz and IF up to 2 GHz. Active mixers offer many advantages over passive mixers: they provide conversion gain instead of insertion loss, require less LO drive power, are less sensitive to port terminations (i.e., the LO input typically does not require an external buffer amplifier and the IF does not require a di-plexer), have better LO-to-IF isolation and produce less spurs. The drawback is that they have a poor IP3, a higher Noise Figure (NF) and the need of a power supply voltage and a series blocking capacitor at the RF, IF, and LO ports to remove DC components[15].

#### 3.2.3 Mixer Performance Metrics

Commercial mixers are characterized by a set of parameters which may have different importance depending on the specific applications in which they are used. The performance of a mixer cannot be judged by just looking at its specifications, the system designer must take care of every single parameter in order to understand if the mixer is suitable for performing the required task. For instance, active mixers provide gain between the RF and IF ports, while passive mixers don't. Passive mixers and active mixers also have different power requirement for the LO port. Moreover, some mixers have a higher dynamic range than other, which means that they can operate in linear region for higher input power levels. The main mixer metrics are listed below.

• Conversion loss: it can be expressed as the power level difference between the input RF signal and the output IF signal, as shown in the following equation:

$$CL = P_{RF} - P_{IF} \tag{3.5}$$

where  $P_{RF}$  and  $P_{IF}$  are in dBm and CL is in dB. Conversion loss is the benchmark mixer metric because it correlates closely with other metrics like isolation and 1 dB compression[14].

Active mixers have an internal amplifier in one or more of the three signal paths, when the amplifier is in the RF or IF path, it generally provides IF output power that is greater than the RF input power. Therefore, *conversion gain* is specified instead of conversion loss[18].

• 1 dB compression: the conversion loss of a mixer is constant when the mixer works in linear region, regardless of the RF input power. This implies that if the RF power level is increased by 1 dB then also the IF power level will increase by 1 dB. This linear relationship between the RF and IF power levels does not hold anymore if the RF power level grows above a certain threshold. Hence, the 1 dB compression point can be defined as the RF power level needed in order to increase the conversion loss by 1 dB from its ideal

value. This situation is clearly shown in Figure 23. The 1 dB compression point represents the upper limit of the dynamic range and it is a measure of the mixer's linearity[14].

Figure 23. Graphical representation of 1 dB compression point [14].

• *Isolation*: it can be mathematically expressed as the power level difference between the input signal power on one port and the leaked power measured on another port. For instance, let's assume to apply a signal with a known frequency and power at the LO

port and to measure the power at the RF port at that frequency, then the isolation can be computed as in Equation 3.6 and it is expressed in dB.

$$P_{ISO\ (L-R)} = P_{IN\ @LO} - P_{OUT\ @RF}$$

(3.6)

There are three types of isolation, which are called LO-RF, LO-IF and RF-IF[14]. LO-RF isolation indicates the power leakage from the LO to the RF port: this is critical for downconversion applications because the LO power could leak into the RF port, thus interfering with the RF amplifier or causing cross-channel interferences. LO-IF isolation indicates the power leakage from the LO into the IF port. If there is poor LO-IF isolation it is possible that the LO frequency contaminate the IF circuitry when their frequencies are close each other. Moreover, poor LO-IF isolation may cause problems in the conversion loss flatness. The last isolation metric is the RF-IF, which is not a main concern of system designers because the RF and IF powers are usually some orders of magnitude smaller than the LO power.

• Noise Figure (NF): it can be expressed as the difference in dB between the noise power level at the input of the mixer and the one at the output. If the mixer is driven with a proper LO power level then the NF can be approximated by the conversion loss[15]. When talking about mixers, the noise figure denotes the lower bound in the dynamic range. For this reason it is extremely important to choose a mixer with the lowest possible conversion loss for low power applications[18]. • Multi-tone intermodulation distortion (IMD): it is a form of common-mode mixing that appears when two or more harmonics enter the RF port and mix with each other and the LO signal, thus creating some distortion at the IF output. Multi-tone IMD can be a problem if the interference harmonics fall within the IF bandwidth of the receiver. This represents a theoretical upper limit on the receiver's dynamic range[18]. For instance, assume that two closely spaced signals  $f_{RF1}$  and  $f_{RF2}$  enters the RF port and nonlinearly inter modulate with  $f_{LO}$ . The relationship between the input frequencies and the thirdorder harmonics at the IF port are shown in Equation 3.7 and Equation 3.8:

$$Interference_1 = 2f_{RF1} - f_{RF2} - f_{LO} \tag{3.7}$$

$$Interference_2 = 2f_{RF2} - f_{RF1} - f_{LO} \tag{3.8}$$

These interference harmonics overlap with the desired down-converted signal in frequency domain. Hence, the SNR of the output signal is degraded because no filtering can separate the interference harmonics from the desired one[14].

• Intercept point: the figure of merit for multi-tone performance is referred as two-tone IMD, or more simply by the acronym IP3. Fundamental mixing tones (i.e. M = 1 and N = 1 in Equation 3.4) grow with a 1:1 slope with respect to the RF input power, while higher order RF harmonics grow by a M:1 slope. The interference harmonics shown in Equation 3.7 and Equation 3.8 grow by a 3:1 slope, this the reason why they are called third-order IMD products. The situation is clearly depicted in Figure 24. The IP3 is the

point at which the input power line (with 1:1 slope) intersects the interference line (with 3:1 slope). The IP3 is a theoretical extrapolated point since a real mixer would compress before the two lines actually cross each other. However, the impact of third-order IMD products can affect the performance of a system even when the RF power level is below the 1 dB compression point[14]. For this reason it is possible to conclude that a higher IP3 level indicates a better quality mixer.

Figure 24. Graphical representation to derive input third order intercept point [14].

# CHAPTER 4

### FBAR FREQUENCY MONITOR DESIGN

In this chapter we are going through the details of designing a low power microcontrollerbased frequency counter. First we are going to analyze the overall system's functionality, then we will go through the different sections in order to have an accurate description of what is the role of each component in the design. At the end we will analyze the PCB layouts and their components in order to understand how the design will be finally implemented on a real electronic board. The PCB layout has been carried out in CadSoft EAGLE PCB Design Software (v6.6.0).

#### 4.1 Overall System's Functionality

The basic block diagram of the frequency counter is shown in Figure 25. We can identify and define the following functional blocks:

• *RF front-end*: The front-end section is the most challenging section of the whole system. Its role is to take a RF high frequency input signal coming from the PM sensor (in the order of 611 MHz) and reduce its frequency so that the microcontroller is able to work with the new frequency. The frequency limitation is not only dependent on the maximum frequency that the input pins of the microcontroller can handle, but also on the maximum frequency at which the input conditioning stage can operate. In order to get reliable frequency measurements we want the microcontroller to work with frequencies lower than

Figure 25. Block diagram of the frequency counter system.

20 MHz. This is when the down-conversion electronics come into play because the input frequency must be reduced by 580 MHz or even more, without distorting or losing the fundamental information contained in the original signal, i.e. its harmonic content.

• Input conditioning: The input conditioning section has the task to convert the analog input signal to a digital one so that the new voltage levels are compatible with the operating voltages of the microcontroller's input pins. What we need is a CMOS level signal in the range 0 to VCC, where VCC is the power supply voltage of the microcontroller. This is achieved by means of a *comparator* used in a *zero-cross detector* configuration. More simply, when the input signal's voltage goes above 0 then the comparator outputs a signal at a voltage VCC, when the input signal goes below 0 then the comparator outputs a signal at voltage 0. It's important to notice that the input signal must be AC coupled in order for the comparator to properly work. We will discuss the details of the input conditioning block in Section 4.3.

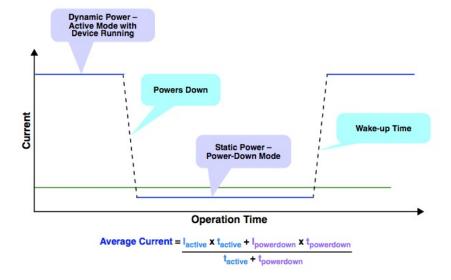

• *Microcontroller section*: This is the computational core of the whole system. The microcontroller has multiple tasks: it performs the frequency counting of the input signal, it outputs data to a computer via UART protocol and it is responsible for the power management of the whole system. Minimum power consumption is achieved using low-power features embedded in the microcontroller and by implementing a smart power management for all the ICs present in the system. The power management is driven by the operation of the frequency counter, in the sense that every IC is powered up when it is strictly necessary, while it is placed in stand-by mode when not needed in order to minimize power consumption. The microcontroller itself enters *Deep Sleep mode* when it is not performing any frequency measurement and it is waken up only when a measurement has to be performed.

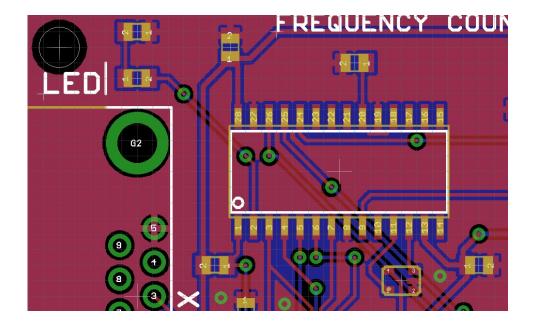

The microcontroller has been set to work as a direct frequency counter. The choice has been made because of limitations in the maximum clock frequency at which the microcontroller can work with an external oscillator. As we already discussed in Section ??, reciprocal counters are the best choice for measuring frequencies lower than the time base frequency, and work best for low frequency measurement. In this case, the input frequency that we are going to measure can go up to 17 MHz, which is higher (or too much close) to the external time base frequency. In conclusion, the direct counting approach is the most effective and simple to implement technique. The PCB layout for the two devices is shown in Figure 27 and Figure 26.

Figure 26. PCB layout of the frequency counter with down-converting prescaler.

The designed devices have been implemented on standard 2-layers PCBs with FR-4 substrate, 0.062 inches thickness and 1 oz copper plate.

Figure 27. PCB layout of the frequency counter with down-converting mixer.

### 4.2 Microcontroller Section

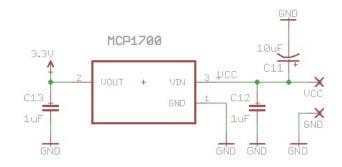

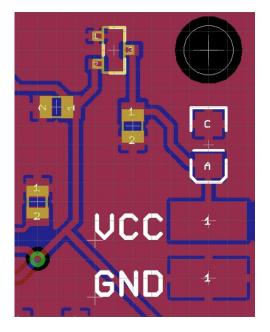

The microcontroller and all its related components are shown in the schematic of Figure 28, while the PCB layout is shown in Figure 30. Figure 29 and Figure 31 show the power supply section with the 3.3V voltage regulator that feeds the whole system. The chosen microcontroller for this design is the PIC24FJ64GB002, a 16-bit MCU Flash microcontroller manufactured by Microchip Technology Inc<sup>®</sup>.

Figure 28. Microcontroller section schematic.

Figure 29. Power supply section schematic.

Figure 30. Microcontroller PCB layout.

Figure 31. Power supply PCB layout.

The schematics of Figure 28 and Figure 29 show all the basic connections and components that the PIC needs in order to properly work:

- The ICSP header, used for connecting the programmer to the microcontroller (the programmer is a PICKit3 manufactured by Microchip Technology Inc<sup>®</sup>).

- The MCP1700, a CMOS LDO voltage regulator able to deliver up to 250 mA of current while drawing a 1.6 μA quiescent current. The maximum input voltage is specified at 6.0V, therefore it represents a good device for battery-powered systems. In our design the MCP1700 provides the power to the whole system, with an output voltage of 3.3V. The

power supply is provided by a battery pack situated under the board, which contains 3 AA batteries for a total input voltage of 4.5V.

- The ASTX-H11, a TCXO manufactured by Abracon Corporation<sup>®</sup>, is used as the accurate Time Base for the frequency measurement. This TCXO has been chosen for it's good price and availability, as well as high frequency stability, low power consumption (maximum 4 mA of supply current) and small SMD form factor. It has a HCMOS output which makes it perfectly suitable for this kind of applications. Another very useful characteristic of this is TCXO is the ability to put it into *Tri-State mode*, which allows the output port to assume a high impedance state, thus removing the output from the circuit. In Tri-State mode the power consumption is reduced to a minimum.

- The Status LED is used to signal to the user when a frequency measurement is being performed. For instance, if a frequency measurement is set to last 1 second then the LED will be on for 1 second, and it will be turned off as long as the PIC runs in sleep mode. If there is no input signal or the input signal's amplitude is lower than the sensitivity of the counter, the Status LED will remain powered on to signal to the user that the measurement cannot be performed because of a problem with the input signal.

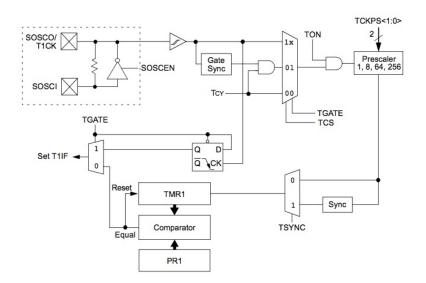

Although the PIC is provided with several peripherals, we are only interested in few of them which are three timers and the UART module. The PIC24F is provided with five 16-bit timers called TMR1, TMR2, TMR3, TMR4 and TMR5. We are not going to use TMR4 and TMR5, therefore they will be disabled as well as all the other unused peripherals. The TMR1 module is a 16-bit timer that can operate in three modes: Timer, Synchronous Counter and Asynchronous Counter. What we are interested in is the third mode of operation, which is the Asynchronous Counter. TMR1 is set to count rising edge events on the pin number 13, which is called T1CK. As we can see from Figure 28, the Time Base's output is connected to T1CK. It's clear that TMR1 will be responsible for generating the accurate gate time during which the frequency measurement will be performed. The gate time is controlled via interrupts, and it is defined by the user. TMR1 is provided with a period register called PR1, as we can see in Figure 32, which is used to set the value at which we want TMR1 to overflow. A comparator is present

Figure 32. 16-bit Timer1 module block diagram.

between TMR1 and PRD1, the comparator is used to signal when TMR1 overflows by means

of a control bit called T1IF. This is one of the bits present in the *interrupt controller register* map: if interrupts are enabled for TMR1 and T1IF is set then an interrupt will be raised when TMR1 overflows. In other words, we exploit the interrupt routine in order to understand when the measurement is over. Moreover, TMR1 is provided with a modulo-1/8/64/256 prescaler, which is used to reduce the input clock frequency coming into the TMR1 module.

In order to set a desired gate time it's necessary to take into account the clock frequency and perform an easy computation. The value to put into PRD1 is computed by means of Equation 4.1:

$$PRD1 = \frac{t_g \cdot f_{CLK}}{Prescaler \ Value} \tag{4.1}$$

Where  $f_{CLK}$  is the frequency of TMR1's source clock (which in our case is the ASTX-H11),  $t_g$  is the desired gate time expressed in seconds and *Prescaler Value* is the division factor of the prescaler associated to TMR1. In our design we are using a 16 MHz TCXO as a source clock for TMR1, and the prescaler is set to modulo-256. If we want a gate time of 1 second then the value to put into PRD1 will be:

$$PRD1 = \frac{1 \cdot 16 \cdot 10^6}{256} = 62500 \tag{4.2}$$

Once we set PRD1 = 62500 then TMR1 will overflow when it reaches the value 62500. This is going to happen after 1 second from when TMR1 is started, since we decided that our gate time is  $t_g = 1 \ s$ . The upper-bound in the time base's frequency is given by the maximum value that TMR1 can reach multiplied by the maximum prescaler's divide ratio:

$$f_{TB_{max}} = (2^{16} - 1) \cdot 256 = 16.77696 \ MHz \tag{4.3}$$

Hence, no oscillator faster than 16.77696 MHz can be used for this design. The lower the external clock frequency, the higher gate time we can get. For instance, a 8 MHz time base will let us generate gate times up to 2 seconds, or even longer gate times for lower clock frequencies. The other modules we are interested in are TMR2 and TMR3, which are 16-bit registers that can be combined together in order to be used as a single 32-bit timer, called TMR2/3. When used in 32-bit configuration they can operate in three modes: 32-bit timer or 32-bit synchronous counter. We are interested in the third mode of operation, which is the 32-bit synchronous counter. The block diagram of TMR2/3 is shown in Figure 33. TMR2/3 has the fundamental task of counting our input frequency, which is of course the down-converted signal coming from the input conditioning section. Since TMR2/3 can only operate as a synchronous counter, i.e. it can only count the internal clock cycle and no external one, the input signal must be given to a clock port of the PIC, which in this case is the OSCI port at pin 9, as shown in Figure 28. This implies that the input signal is used as a clock source for our system but, as we will see later, this doesn't affect code execution since no instructions are executed while the microcontroller is performing the frequency measurement. The period register PRD2/3 has the exact same functionality as PRD1 for TMR1. In this case we want TMR2/3 to overflow when it reaches the maximum possible value, even though overflow will never happen since the maximum value that a 32-bit counter can reach is  $2^{32} = 4294967296$ , which would represent a frequency of about 4.3 GHz.

Figure 33. 32-bit Timer2/3 module block diagram.

The last important thing to discuss about TMR2/3 is that the instruction cycle for a PIC24F is 2 clock cycles, therefore the system operating frequency is  $F_{cy} = F_{osc}/2$ . This implies that

TMR2/3 will count the input frequency divided by 2. This is the same of having a modulo-2 prescaler in the input signal's path. As a consequence, the resolution of a measurement decreases by a factor of 2 for the same gate time, i.e. from  $\pm 1$  Hz down to  $\pm 2$  Hz for a 1 second gate time. This has to be carefully taken into account in the design stage, for instance let's assume that we are using a modulo-64 prescaler in order to down-convert the RF input signal; the resulting resolution for a 1 second gate time will be  $\pm 64$  Hz, as we discussed in Section 3.1, but since the signal is further divided by 2 than the final resolution will be  $\pm 128$ Hz. The work-around for bringing the resolution back to its original value consists in doubling the measurement time. This is not strictly needed if the final resolution is acceptable by the user's point of view. We will discuss the tradeoff between resolution and power consumption in Chapter 6.

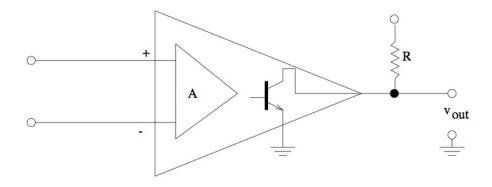

#### 4.3 Input Conditioning Stage

In order to translate the voltage levels of the input signal to the CMOS level needed by the input pin of the PIC we make use of a *comparator*. The simplest form of a comparator is a high-gain differential amplifier which is not used with negative feedback. A comparator can be made with an op-amp, which can go into positive or negative saturation depending on the difference of the two input voltages. Hence, the basic function of a comparator is to determine which one of its own two inputs has the larger voltage. Even if the two inputs differ by a fraction of a mV, the comparator will always go into saturation because its open-loop gain typically exceeds 100000. A comparator can be implemented by employing an ordinary op-amp or a particular IC specifically designed to be used as a comparator, with very fast response. The output circuit

of a comparator is more flexible than the one of an op-amp because usually comparators have an open-collector output with grounded emitter, while op-amps use a push-pull output stage to swing between the supply voltages. It is enough to provide the output of the comparator with a pull-up resistor, connected to an external voltage, in order to get an output swing from  $V_{DD}$ to ground. The basic comparator is shown in Figure 34.

Figure 34. Basic comparator model.

If v- is connected to ground and the input signal is applied to v+ then the output swings from  $V_{DD}$  to ground when the input signal goes negative. In this case the comparator converts an analog input signal into a digital output. This is equivalent to a 1-bit analog to digital converter (A/D or ADC). The external pull-up resistor completes the comparator's output circuit by providing a load resistor to the collector of the output transistor. The value of the resistor is not critical because the output operates as a saturated switch, therefore values between a few hundreds of ohms and a few thousands of ohms are typical. Small values improve the immunity to noise and the switching speed, at the expense of a higher power dissipation. Comparators are never used with negative feedback because they are not stable in this configuration. Usually comparator circuits employ positive feedback in order to ensure that only the two extreme output states are utilized and nothing in between. Moreover, without negative feedback there is no need to do compensation, i.e. there is more gain at high frequency, which translates in a faster response. Finally, it is possible to optimize comparators for speed at the expense of linearity.

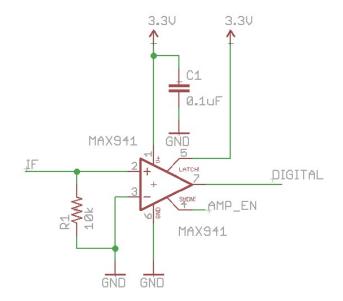

Figure 35. MAX941 in non-inverting comparator configuration.

Comparators, like op-amps, are readily available as ICs chips such as the MAX941 that we used in our design. The MAX941 is used as a non-inverting comparator and its schematic is shown in Figure 35. As we can see, the power supply goes from  $V_{DD} = 3.3V$  to ground. This means that the digital output will swing from 0 to 3.3V.

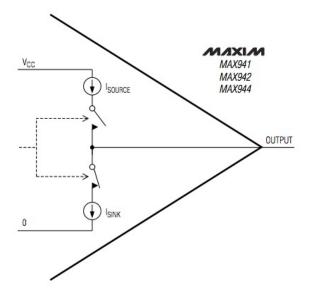

The MAX941 contains a current-driven output stage, as shown in the model of Figure 36. This device is suited for direct interface with CMOS or TTL logic because its output pulls to within 0.4V of either supply rail without the need of an external pull-up resistor.

Figure 36. MAX941 output stage circuitry.

The MAX941 is provided with an internal hysteresis, which ensures a glitch-free output switching even with noisy or slow input signals. The hysteresis window is shown in Figure 37, where the  $V_{TRIP}$  points represents the boundaries of the differential input voltage required in order for the output of the comparator to change state.

Figure 37. MAX941 input and output waveforms, with hysteresis.

The width of the hysteresis windows can be expressed as the difference between the upper and lower  $V_{TRIP}$  points.  $V_{OS}$  represents the center of the hysteresis zone. The typical value for  $V_{TRIP}$  is 1mV. This is very useful because we don't want the comparator to trigger on noise if there is no input signal coming from the RF front-end section. If the input signal's amplitude is too small or if there's no input signal, the frequency counter simply get stuck and the status LED will remain on in order to signal to the user that the measurement can't be performed because of the absence of a valid input signal.

The PCB layout for the MAX941 comparator is shown in Figure 38, where pin 2 is the input

and pin 7 is the output which is fed to the PIC24F. Pin 4 is the shut-down signal, which is driven by the microcontroller.

Figure 38. MAX941 PCB layout.

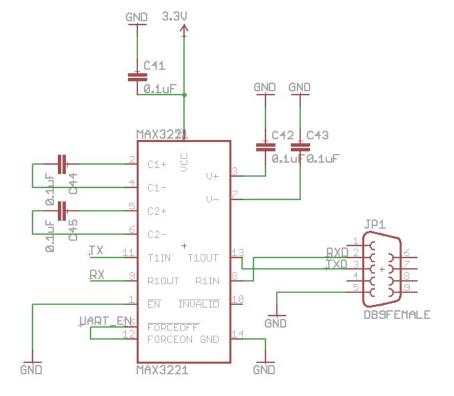

### 4.4 UART-RS232 Section

UART stands for Universal Asynchronous Receiver Transmitter, it is a hardware device used to translate data between a parallel representation to an asynchronous serial one, or viceversa. Most modern computers employ a serial port that makes use of standard protocol known as RS-232, which is a specific type of UART that sends out data at voltages different from the usual TTL levels. PIC24F microcontrollers usually have 2 UART modules called UART1 and UART2. These two modules are controlled by several registers such as the UxBRG, the UxMODE and the UxSTA. The UxBRG establishes the baud rate of the communication by means of a clock prescaler. The UxMODE is used to turn the module ON and OFF. The UxSTA is the status register, which can be used to check all the current conditions of the module. A data buffer for both transmission and reception is also present. It is possible to load up to 4 bytes of data in the transmission buffer, that will be sent one at a time by the module. Also the receiver buffer is 4 bytes in size. The hardest part is establishing the timing. The first thing to figure out is the instruction clock frequency  $F_{CY}$  before proceeding. In the PIC24F family,  $F_{CY}$  is equal to the system's clock frequency divided by 2, as already explained in Section 4.2. Once  $F_{CY}$  has been computed, the register called UxBRG has to be updated in order to determine the correct baud rate for the UART module. It is possible to set the module in high speed or standard speed mode. For this particular application we can safely use the module in standard speed mode by clearing the BRGH bit of the UxMODE register. The UxBRG value must be computed using Equation 4.4 for standard speed mode:

$$BRGx = \frac{F_{CY}}{16 \cdot Baud \ Rate} - 1 \tag{4.4}$$

In our design we have have a clock frequency of  $F_{osc} = 8 \ MHz$  provided by the internal FRC oscillator, with no PPL, and no clock divide. The Baud Rate has been chosen to be 9600, therefore the content of the BRGx register is computed as in Equation 4.6:

$$F_{cy} = \frac{F_{osc}}{2} = \frac{8 \cdot 10^6}{2} = 4 \cdot 10^6 \ Hz \tag{4.5}$$

$$BRGx = \frac{4 \cdot 10^6}{16 \cdot 9600} - 1 = 25.04 \simeq 25 \tag{4.6}$$

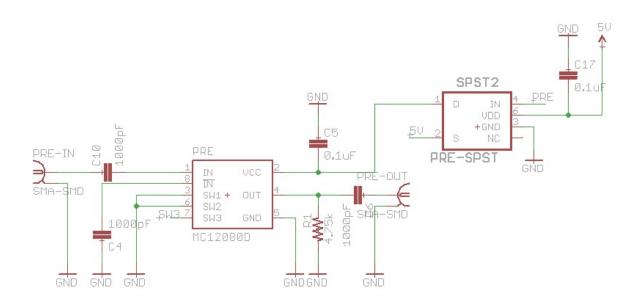

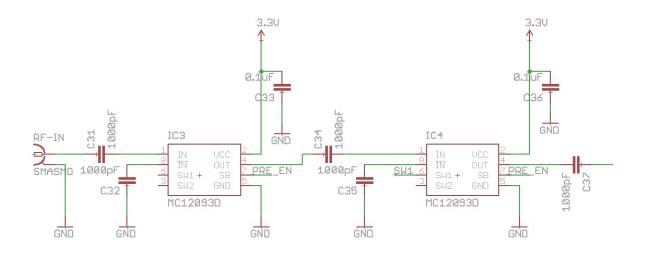

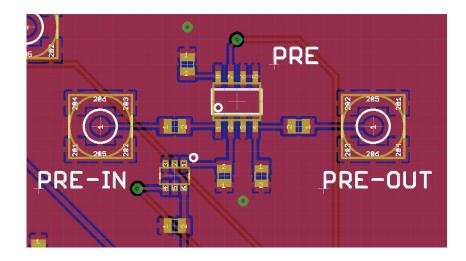

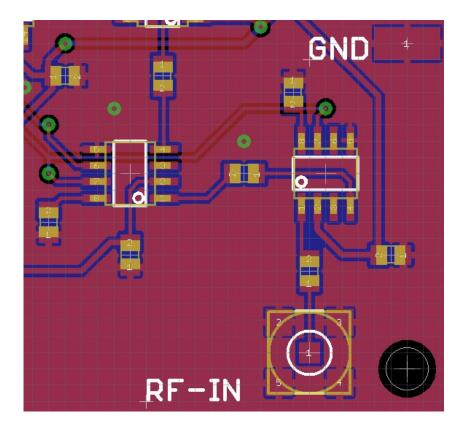

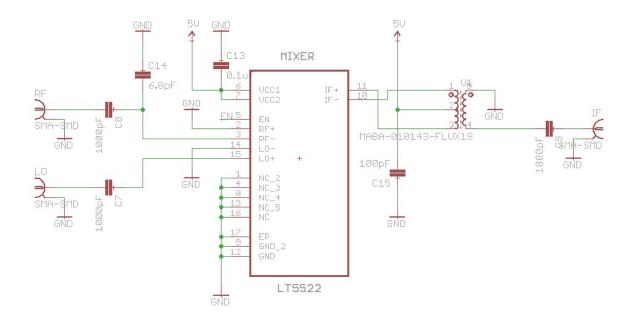

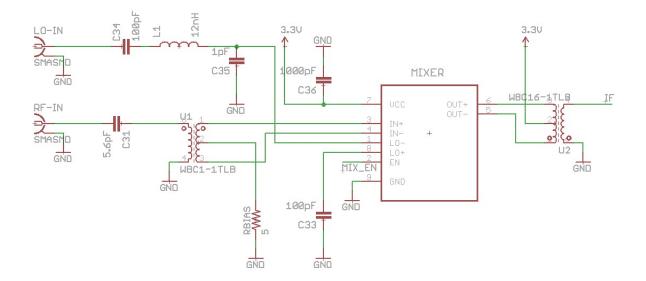

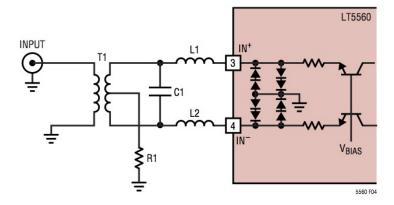

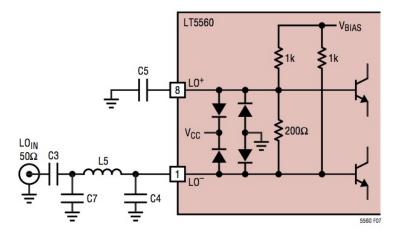

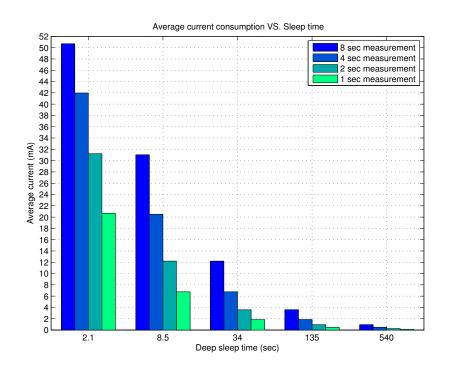

The value is rounded to 25 because the register UxBRG works with integers only. It doesn't make any significant difference because the value of 25 only means that the timing will be off by a small amount, not enough to consistently get an error.