### Hardware Obfuscation Using Physically Unclonable Functions Against IC Piracy

BY

SOROUSH KHALEGHI B.S., Sharif University of Technology, 2012 M.S., University of Illinois at Chicago, 2017

#### THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2018

Chicago, Illinois

Defense Committee:

Wenjing Rao, Chair and Advisor Zhichun Zhu Zhao Zhang Igor Paprotny John Lillis, Computer Science Copyright by

Soroush Khaleghi

2018

To Sepideh,

And my parents, Sima and Hassan.

#### ACKNOWLEDGMENTS

First of all, I would like to thank my advisor Dr. Wenjing Rao for everything she has done for me. Her encouragement, inspiration, patience, and valuable hints and advice helped shape this work. Her considerations for both keeping in mind the big picture of research and digging deep into the technical details, as well as her emphasis on effective writing and presentation were critical in every step of my Ph.D. I always enjoyed the regular research meetings with Dr. Rao on various research ideas, as well as our conversations on a broader range of topics. Over the past six years, she has taught me a great deal, both professionally and personally. Particularly, her contagious positive attitude, which in my opinion was the special ingredient in making her a great advisor, is a lesson that I will never forget.

I want to extend my appreciation to Dr. Zhichun Zhu, Dr. Zhao Zhang, Dr. Igor Paprotny, and Dr. John Lillis for serving on my dissertation committee. I would also like to thank Dr. Amit Ranjan Trivedi for his guidance during my preliminary examination.

I also want to thank all my wonderful professors and teachers over the many years of my studies. Particularly, I want to thank Dr. Yue Yin for her great support and guidance on our educational collaboration focusing on computational thinking. I would also like to thank Dr. Natasha Devroye for her valuable insights that helped me get a deeper understanding of my research topics by looking at them from a different perspective.

I shared many pleasant moments with my fellow group members over the years: Soumya Banerjee, Jian Xu, Paolo Vinella, and Kai Da Zhao. Their feedback and insights helped improve this work.

#### **ACKNOWLEDGMENTS** (Continued)

I always consider myself to be very lucky for having many wonderful friends. I want to thank them all for creating the most meaningful moments of my life. Particularly, I want to thank Alborz Rezazadeh, Ali Javadi, Amir Hosseinipour, Bahareh Abbasi, Dorsa Fahimi, Ehsan Asgari, Hadi Pouransari, Hossein Mirghasemi, Mehdi Sharifzadeh, Mohammad Bavarian, Nasim Mobasheri, Sadegh Salehi, Zia Ghiasi, and Zaeim Mehraban.

I am forever indebted to my parents for their devotion and everlasting love. My mother, Sima, has devoted her entire life to raising me and my three siblings to be happy and successful. No words can describe how thankful I am to her. I often wish that I had made the movie "It's a wonderful life", so that I could dedicate it to her, for all her sacrifice. I am also grateful to my father, Hassan, who taught us to always seek and do the right thing by his own way of life. I owe a lot of who I am to him, for his wisdom and support. I would also like to thank my siblings. My older brothers, Sina and Salman, have made every single step of my life a lot easier than it was for theirs. They have been sources of comfort from far away by offering me their continuous help, support, guidance, and inspiration. I am also thankful to my dear little sister, Dr. Saba, for her love and support and generosity. Sanam and Sina opened their warm home to us for an entire summer while expecting my lovely nephew, Kian.

Finally, I want to thank the love of my life, the kindest person I have ever known, and my best friend: Sepideh. None of this would have been possible without your endless love, support, and patience. Thank you!

### PREFACE

This dissertation is an original intellectual product of the author, Soroush Khaleghi. All of the work presented in this dissertation was performed at the University of Illinois at Chicago. The work has been presented and published in (Khaleghi et al., 2015), (Khaleghi et al., 2016), (Khaleghi and Rao, 2018). The research work was funded by NSF Grant CNS-1149661

Soroush Khaleghi October 22, 2018

#### **CONTRIBUTION OF AUTHORS**

The contents of Chapter 2 was published in (Khaleghi et al., 2015). Wenjing Rao, my adviser, was the lead investigator in this project. I was responsible for coming up with the idea, formalizing the problem, proposing the solutions, designing the experiments, and writing of the paper. Kai Da Zhao was responsible for performing the experiments and analyzing the data.

The contents of Chapter 3 was published in (Khaleghi et al., 2016). Wenjing Rao, my adviser, was the lead investigator in this project. I was responsible for conceptualizing the idea, formalizing the problem, designing the framework and writing of the paper. Paolo Vinella was responsible for performing the experiments as part of his M.Sc. thesis at University of Illinois at Chicago. Soumya Banerjee contributed to manuscript edits.

The contents of Chapter 4 was published in (Khaleghi and Rao, 2018). Wenjing Rao, my adviser, was the lead investigator in this project. I was responsible for coming up with the idea, formalizing the problem, proposing the solutions, designing and performing the experiments, as well as writing of the paper.

# TABLE OF CONTENTS

## **CHAPTER**

### PAGE

| 1 | INTRODUCTION                                                             |                                                               |  |

|---|--------------------------------------------------------------------------|---------------------------------------------------------------|--|

|   | 1.1                                                                      | Overview                                                      |  |

|   | 1.2                                                                      | Previous Works                                                |  |

|   | 1.2.1                                                                    | MUX-based implementation of obfuscation schemes               |  |

|   | 1.3                                                                      | Attack Models and Assumptions                                 |  |

|   | 1.3.0.1                                                                  | Algorithmic attacks on obfuscated design files                |  |

|   | 1.3.0.2                                                                  | Physical attacks on unlocked chips                            |  |

|   | 1.4                                                                      | Organization                                                  |  |

| 2 |                                                                          | DE ODEUSCATION THROUCH ENTANCI EMENT ACAINST                  |  |

| 2 | HARDWARE OBFUSCATION THROUGH ENTANGLEMENT AGAINST<br>ALGORITHMIC ATTACKS |                                                               |  |

|   | 2.1                                                                      | <b>I</b> troduction         17                                |  |

|   | 2.1                                                                      | Previous Works                                                |  |

|   | 2.2                                                                      | Preliminaries and Motivation: Design Withholding Framework 21 |  |

|   | 2.3                                                                      | e e                                                           |  |

|   | 2.3.1                                                                    |                                                               |  |

|   | 2.3.2                                                                    |                                                               |  |

|   | 2.3.3<br>2.4                                                             |                                                               |  |

|   | 2.4<br>2.4.1                                                             | e                                                             |  |

|   | 2.4.1                                                                    | 6                                                             |  |

|   | 2.4.2<br>2.5                                                             | 8                                                             |  |

|   |                                                                          |                                                               |  |

|   | 2.6                                                                      | Conclusions                                                   |  |

| 3 | A NEW W                                                                  | VAY OF CONSTRUCTING STRONG PUFS                               |  |

|   | WITH ST                                                                  | <b>T-MRAM AS A CASE STUDY</b>                                 |  |

|   | 3.1                                                                      | Introduction                                                  |  |

|   | 3.2                                                                      | Preliminaries                                                 |  |

|   | 3.2.1                                                                    | General concepts of a PUF 39                                  |  |

|   | 3.2.1.1                                                                  | Weak PUFs         40                                          |  |

|   | 3.2.1.2                                                                  | Strong PUFs                                                   |  |

|   | 3.2.2                                                                    | STT-MRAM devices                                              |  |

|   | 3.2.3                                                                    | An STT-MRAM based weak PUF 43                                 |  |

|   | 3.3                                                                      | A Strong PUF Based on STT-MRAM 44                             |  |

|   | 3.3.1                                                                    | Motivation                                                    |  |

|   | 3.3.2                                                                    | Architecture                                                  |  |

|   | 3.3.3                                                                    | Analysis                                                      |  |

|   | 3.4                                                                      | Evaluation                                                    |  |

# TABLE OF CONTENTS (Continued)

## **CHAPTER**

| 3.5     | Strong PUF Beyond STT-MRAM                           |

|---------|------------------------------------------------------|

| 3.5.1   | Case study of a RO-based strong PUF                  |

| 3.6     | Conclusions                                          |

| INTEGR  | ATING STRONG PUFS INTO THE HARDWARE OBFUSCATION      |

| FRAME   | WORK AGAINST LEAKED KEYS                             |

| 4.1     | Introduction                                         |

| 4.2     | Preliminaries                                        |

| 4.2.1   | Machine learning attacks against strong PUFs         |

| 4.2.2   | Weak PUF-based hardware obfuscation                  |

| 4.3     | Motivation                                           |

| 4.4     | A Strong PUF-based Hardware Obfuscation              |

| 4.5     | Security Analysis                                    |

| 4.5.1   | Attack model                                         |

| 4.5.2   | Attack analysis upon a leaked key                    |

| 4.5.2.1 | PUF characterization of chips in open market         |

| 4.5.2.2 | PUF characterization of chips at manufacturing stage |

| 4.5.2.3 | SAT-based attacks                                    |

| 4.5.3   | Attack complexity                                    |

| 4.6     | Cost and Implementation Discussion                   |

| 4.6.1   | Hardware cost complexity                             |

| 4.6.2   | PUF reliability                                      |

| 4.6.3   | Performance overhead                                 |

| 4.7     | Evaluation                                           |

| 4.8     | Conclusion                                           |

| CONCLU  | USION                                                |

| APPEND  | DICES                                                |

| Appen   | ndix A                                               |

| CITED L | LITERATURE                                           |

| VITA    |                                                      |

# LIST OF TABLES

| <b>TABLE</b> |                                                                      | PAGE |

|--------------|----------------------------------------------------------------------|------|

| Ι            | Using weak PUFs vs strong PUFs in an obfuscation framework: an ideal |      |

|              | scenario is marked out                                               | . 65 |

# LIST OF FIGURES

| <b>FIGURE</b> |                                                                                                                                                                                                                       | PAGE |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

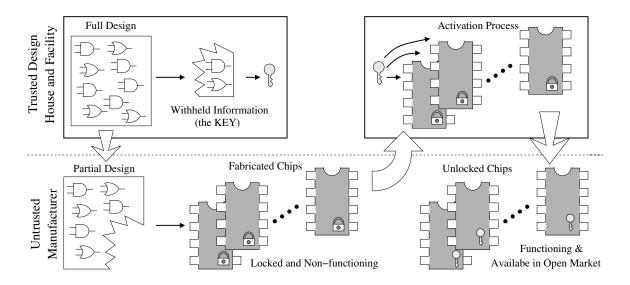

| 1             | Illustration of the design-manufacturing flow assumed by the obfuscation-<br>based schemes                                                                                                                            | 4    |

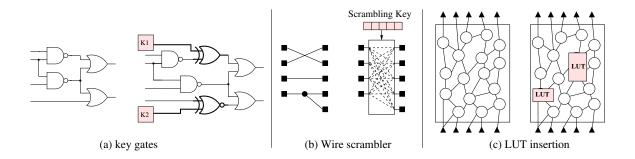

| 2             | (a) The content of K1 and K2 obfuscates the functionality of the circuit; (b) wiring interconnects are scrambled for obfuscation purposes; (c) obfuscation by replacing logic functions with LUTs.                    | 5    |

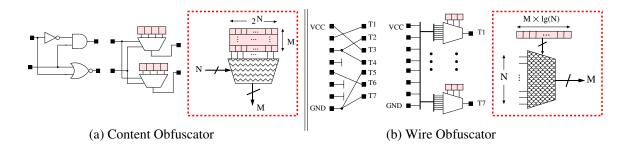

| 3             | Two MUX-based obfuscation implementations with examples and general forms                                                                                                                                             | 7    |

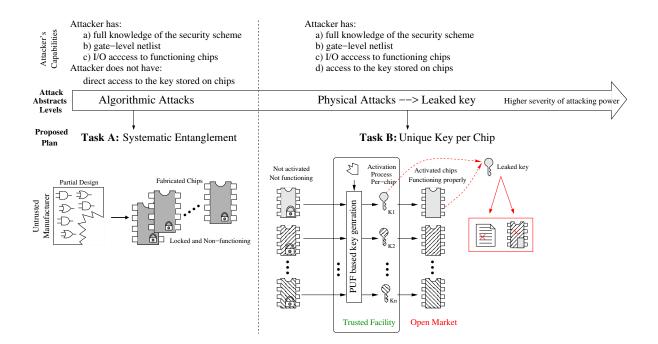

| 4             | An overview of attack models, assumptions, and the proposed defensive mechanisms                                                                                                                                      | 9    |

| 5             | Examples of algorithmic attacks on: (a) a Content Obfuscator (b) a Wire Obfuscator                                                                                                                                    | 11   |

| 6             | An example, where a part of a design (including 2 inputs and 1 output) is replaced with a LUT on chip.                                                                                                                | 22   |

| 7             | Withholding a multi-output function to elevate each attack from NP-Complete to NP-Hard complexity.                                                                                                                    | 24   |

| 8             | External Entanglement: a) the original withheld function; b) designer's cost (LUT size) kept low with the help of an Obfuscator; c) the attacker has to solve a much larger number of cells, due to the entanglement. | 27   |

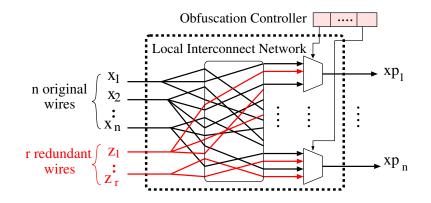

| 9             | General structure of a programmable Obfuscator.                                                                                                                                                                       | 28   |

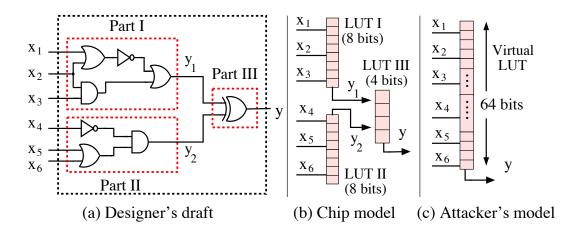

| 10            | Internal Entanglement: a) a large withheld piece is decomposed into 3 smaller pieces; b) Using three interlocking small LUT's to shrink the hardware cost; c) the large virtual LUT remained for attacker to solve.   | 30   |

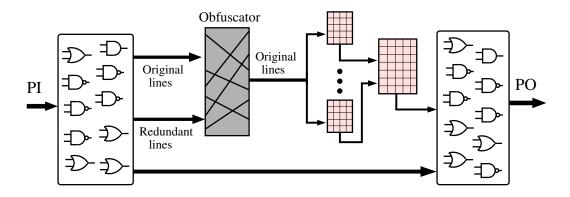

| 11            | Applying both External Entanglement and Internal Entanglement                                                                                                                                                         | 32   |

# LIST OF FIGURES (Continued)

## **FIGURE**

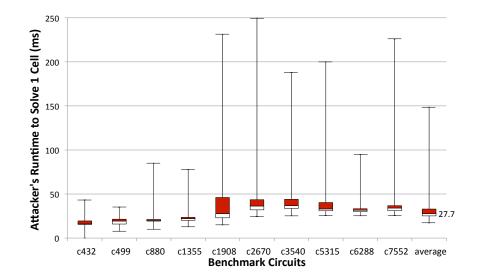

| The minimum, first quartile, median, third quartile, and maximum runtime<br>for an attacker to solve an input pattern for each cell, in the case of withholding<br>one piece of design with a single-output (NP-Complete complexity) over all<br>possible single-output functions.                                                                                                         | 33                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

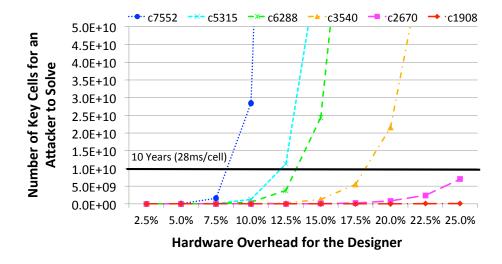

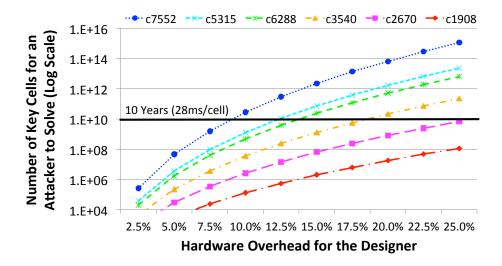

| Attacking cost vs. Hardware cost for the Internal Entanglement scheme                                                                                                                                                                                                                                                                                                                      | 34                                                                                                                                                                                                                 |

| Attacking cost (Logarithmic Scale) vs. hardware overhead for the Internal Entanglement scheme.                                                                                                                                                                                                                                                                                             | 35                                                                                                                                                                                                                 |

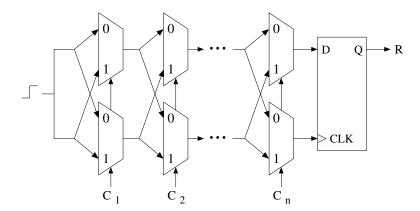

| Arbiter PUF circuit: two delay paths are created based on the challenge ( $C_1$ to $C_n$ ). Depending on the arrival times of the rising edge at the inputs of the D-FF (arbiter), the response ( $R$ ) could become either "1" or "0".                                                                                                                                                    | 41                                                                                                                                                                                                                 |

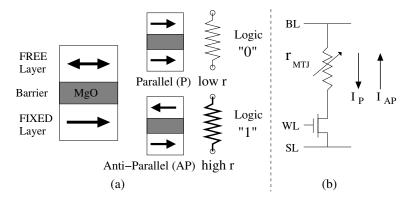

| (a) MTJ device structure and its resistance model; (b) The complete struc-<br>ture of an STT-MRAM cell                                                                                                                                                                                                                                                                                     | 42                                                                                                                                                                                                                 |

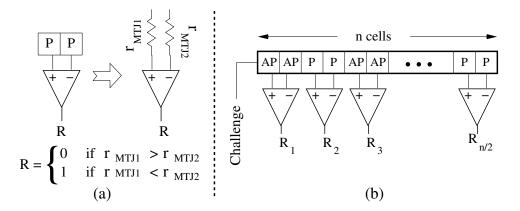

| An STT-MRAM based weak PUF: (a) The main idea: comparing the re-<br>sistances of two identical cells with the same magnetization; (b) The complete<br>architecture of the PUF.                                                                                                                                                                                                             | 43                                                                                                                                                                                                                 |

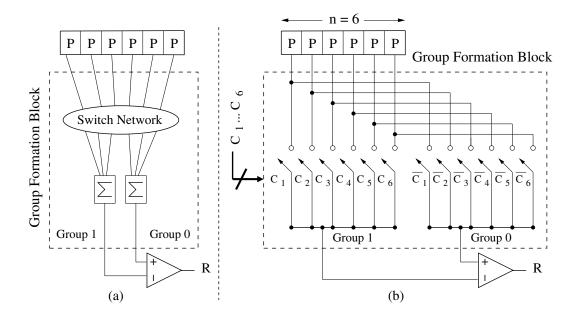

| (a) The idea of forming 2 groups to increase the number of CRPs; (b) An example architecture for implementing the Group Formation Block for a PUF with 6 cells.                                                                                                                                                                                                                            | 46                                                                                                                                                                                                                 |

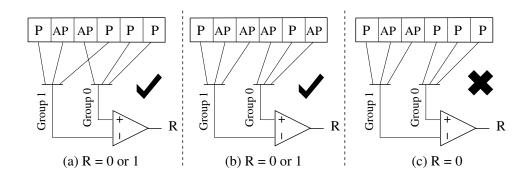

| (a)(b) Examples of valid CRPs by changing the bit patterns and group for-<br>mations; (c) An invalid CRP: Group 1 with two <i>AP</i> 's and one <i>P</i> has a higher<br>resistance than Group 0 with three <i>P</i> 's                                                                                                                                                                    | 48                                                                                                                                                                                                                 |

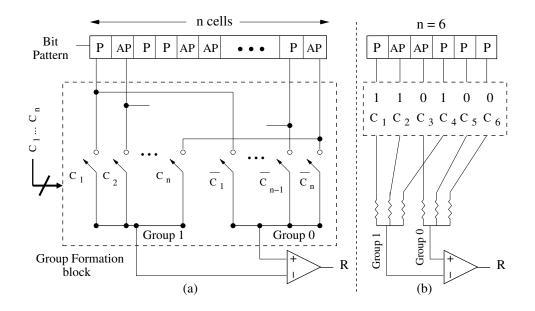

| (a) The overall architecture of the proposed strong PUF; (b) An example for n=6: each group has two <i>P</i> 's and one <i>AP</i> .                                                                                                                                                                                                                                                        | 49                                                                                                                                                                                                                 |

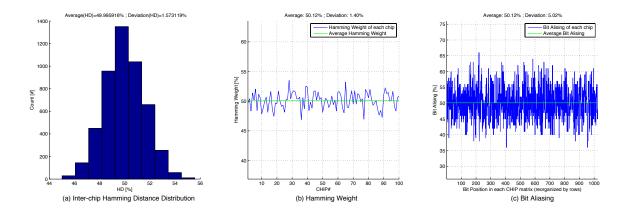

| The quality of the proposed strong PUF with respect to three parameters:<br>(a) Inter-chip Hamming distance: measuring the randomness among different<br>chips; (b) Hamming weight: measuring the randomness among various bits of<br>a same response within a same chip; (c) Bit aliasing: measuring the random-<br>ness for each response bit among various responses within a same chip | 51                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>for an attacker to solve an input pattern for each cell, in the case of withholding one piece of design with a single-output (NP-Complete complexity) over all possible single-output functions</li></ul> |

# LIST OF FIGURES (Continued)

## **FIGURE**

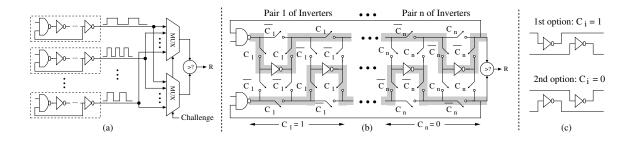

| 22 | (a) RO-based weak PUF circuit: the frequencies of two ROs are compared to form the response bit $R$ ; (b) The proposed Strong PUF based on the idea of group formation: each Inverter in every pair belongs to one of the two ROs; The highlights correspond to the first and the last pair of Inverters for $C_1 = 1$ and $C_n = 0$ ; (c) The two options for each pair of Inverters $(1 \le i \le n)$                                                                                     | 54 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

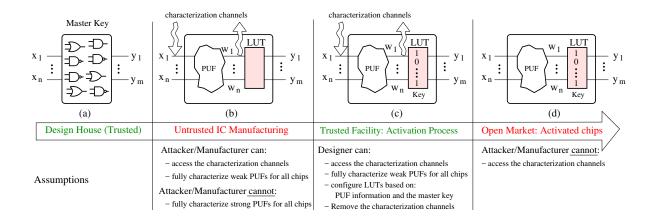

| 23 | Flow of PUF-based hardware obfuscation: (a) A part of the design with <i>n</i> inputs and <i>m</i> outputs is selected to be withheld as the master key. (b) The chip model with a PUF and a LUT, coupled to replace the master key. The manufactured chips based on this model will not be functional until activated by the designer. (c) The designer configures the LUT for each chip based on the behavior of the PUF to match the master key. (d) Activated chips in the open market. | 61 |

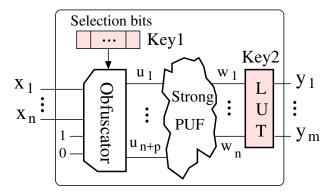

| 24 | The architecture of the proposed scheme: by assigning Key1 for each chip, a permutation of the original wires appears at $n$ inputs of the PUF, and the other $p$ inputs of the PUF are set with arbitrarily specified values. Only a subset of the PUF with $n$ inputs and $n$ outputs will be used by the designer. The LUT (Key2) is programmed to compensate for the unique behavior of the PUF. The unique key per chip is $\langle \text{Key1}, \text{Key2} \rangle$ .                | 66 |

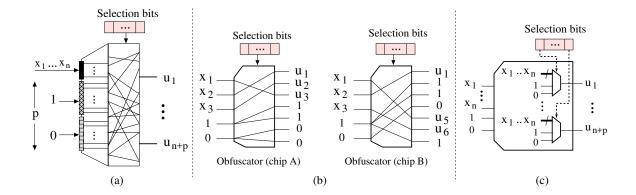

| 25 | (a) Obfuscator: By specifying the Selection bits, a permutation of $n$ original wires, as well as $p$ fixed values (0 or 1) will appear at the output of the block;<br>(b) Examples of an Obfuscator block (with $n = 3$ and $p = 4$ ) to allow the designer to select any subset of the CRP space during the activation process without revealing it to the attacker at the manufacturing stage; (c) A possible MUX-based implementation of the Obfuscator                                 | 67 |

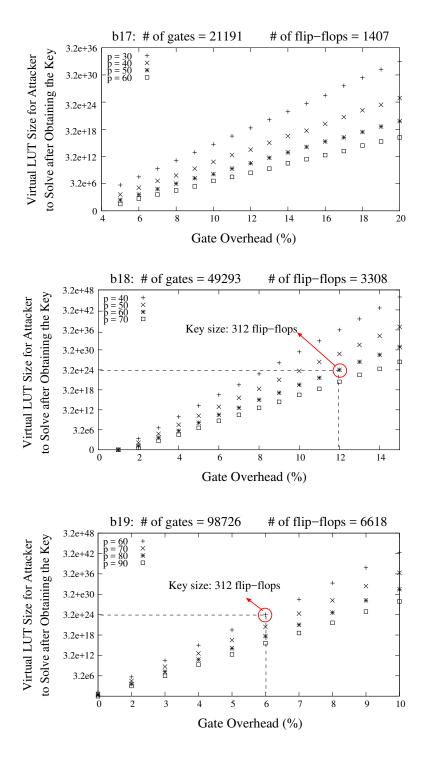

| 26 | The cost to attack vs. hardware overhead of the proposed scheme for dif-<br>ferent circuits.                                                                                                                                                                                                                                                                                                                                                                                                | 75 |

# LIST OF ABBREVIATIONS

| IC   | Integrated Circuit                                |

|------|---------------------------------------------------|

| IP   | Intellectual Property                             |

| NP   | Nondeterministic Polynomial                       |

| LUT  | Look-up Table                                     |

| ATPG | Automatic Test Pattern Generation                 |

| CRP  | Challenge-Response Pair                           |

| PUF  | Physically Unclonable Functions                   |

| ECC  | Error Correcting Code                             |

| MUX  | Multiplexer                                       |

| IEEE | Institute of Electrical and Electronics Engineers |

| UIC  | University of Illinois at Chicago                 |

#### SUMMARY

The goal of this thesis is to establish a theoretical foundation and defensive mechanisms against integrated circuit (IC) piracy. IC piracy is defined as the practice of an untrusted manufacturer to produce illegal copies of IC chips, or to steal the intellectual property of the IC design via reverse engineering approaches. IC piracy prevention is especially challenging, as the potential attackers are in the very strong position of chip manufacturers, having accesses to the design details and controls to the final production process.

The proposed work aims at the *hardware obfuscation* based prevention strategy: an "obfuscated" IC design given to the untrusted manufacturer will yield chips that are "locked" (non-functioning), until being "unlocked" (configured correctly) in a trusted facility. The obfuscation strategy mimics that of an encryption process, ensuring that some critical information (analogous to the key) of the design is not revealed to the untrusted manufacturer. During the "unlocking" process (analogous to decryption) in a trusted facility, the key is used to restore the chips to their correct functionality.

Currently, many obfuscation approaches exist, yet they mostly present various ad-hoc choices of obfuscation target, and are based on heuristic methods. There lacks a theoretically sound and provably secure foundation to address the two main categories of attacks: 1) *algorithmic attacks* applied on the obfuscated design, that could potentially crack the keys efficiently, and 2) *physical attacks* applied on the unlocked chips, aiming at reading out the keys directly from the on-chip memory cells.

The goal of this work is to achieve an IC piracy prevention paradigm similar to modern cryptography, in their reliance on the secrecy of a key alone, rather than that of the scheme itself, as well as their

#### **SUMMARY** (Continued)

provable defense strength via imposing prohibitively high attacking cost, measured by computational complexity. This will lay the basic principles for a future "Design-Against-Piracy" paradigm, similar to the widely used "Design-For-Test" practices in IC industry today.

The proposed work aims at simultaneously *expanding the control of a designer*, and *restraining the control of an attacker*, throughout the IC design and fabrication process. This is approached in the following ways: 1) novel primitives are introduced with the representational power to unify the existing obfuscation schemes, and based on which quantitative analysis of attack and defense costs are possible to carry out; 2) by systematic entangling the various obfuscation primitives in a hierarchical manner, a strong defense mechanism can be built to ensure that the cost of algorithmic attacks (in terms of computational complexity) can be raised exponentially, while the designer's cost (in terms of hardware overhead on chip) only increases linearly; 3) against the worst-case scenario of combined algorithmic and physical attacks, a preventive architecture is proposed to deliver a unique key per chip, via the engagement of Physically Unclonable Functions (PUFs) into the obfuscation paradigm. This will ensure that even a completely leaked key cannot be used for piracy purposes. Overall, the deliverable security (in terms of attack costs) and defense costs (as overhead on the designer's side) can be quantitatively modeled, analyzed, and proved, in an asymptotic manner, making it suitable for the scalability of IC design, serving a strong basis for a "design against piracy" framework.

The research work in this thesis will deliver an overall strong foundation of hardware security to actively prevent IC piracy with the following guarantees:

### **SUMMARY** (Continued)

- Any attackers (even in the strongest position of a manufacturer) cannot crack the design or unlock the chips within a reasonable amount of time, and such attacking cost is in full control of the designer.

- 2. Any wrong key cannot unlock a chip to function, and even in the extreme cases of a completely leaked key, the security of the original design can be nonetheless protected, as the unique key one chip can neither unlock any other chip, nor be used to reverse engineering to gain information of the original design.

#### **CHAPTER 1**

#### **INTRODUCTION**

Parts of this chapter have been presented in (Khaleghi et al., 2015), (Khaleghi et al., 2016), (Khaleghi and Rao, 2018). Copyright © 2015, 2016, 2018, IEEE.

#### 1.1 Overview

The goal of the proposed work is to develop a theoretically sound foundation against the threat of integrated circuits (IC) piracy (Rostami et al., 2013) (Roy and Koushanfar, 2008), (Torrance and James, 2011). IC piracy usually refers to an untrusted manufacturer producing more chips than authorized to sell at a marginal cost, or stealing the intellectual property of the design via reverse engineering techniques. These threats have emerged due to the globalization of the semiconductor industry. According to the Semiconductor Industry Association (SIA), counterfeiting costs U.S semiconductor industry over \$7.5 billion per year (Office, 2011).

Using the paradigm of modern cryptography as an analogy, if the original IC design file is considered as a plain-text "message", then a successful prevention framework should ensure that security relies solely on the secrecy of a key, not that of the scheme or the encrypting algorithms. Similarly, the strength of a defense mechanism should rely on imposing a prohibitive attacking cost: cracking of a key is provably infeasible in a limited time.

However, the reality of IC piracy prevention is far from achieving such a goal. Most existing approaches are ad-hoc based, lacking of theoretical principles, fine-grained quantitative models, and provable results. Furthermore, there lacks a similar foundation which serves as the basis to the approaches,

as in the case of modern cryptography paradigm. This is partially because the challenges of IC piracy are relatively new, but more importantly, IC piracy has its unique challenges that have no parallels in the software domain.

Essentially, IC piracy has to deal with a very strong potential attacker in the position of an untrusted manufacturer, who is usually at the final stage of the production chain to fabricate the chips, and has access to the majority, if not the entire design in details <sup>1</sup>.

Furthermore, an IC piracy prevention framework cannot be achieved by a straightforward adoption of the established encryption schemes. **First**, one cannot simply apply, say, RSA (Rivest et al., 1978) encryption, onto a design file (treating it as a plaintext message), because then the encrypted file becomes useless for fabrication of any chips: the transformation imposed by RSA (and other encryption algorithms) onto the original design file does not yield a valid format of description of any chip, let alone a desired "locked chip". In the context of IC piracy prevention, since the design files are used to describe a chip product (which has a well-defined functionality), and the potential attacker is in the position of the manufacturer, a "properly encrypted" design file should still yield the valid, intended chip products, except that these chips (manufactured according to the "encrypted" design file) should be "locked" in their functionalities, until some key is applied to "unlock" them. Such a requirement (encryption of a design yielding locked chips) is the unique attribute of the IC piracy prevention paradigm. **Second**, the abilities and tools of the attacker in the position of manufacturer are significant: the potential attackers

<sup>&</sup>lt;sup>1</sup>It is true that the format of the design that is made available to the manufacturer (such as the final layout form) might be quite different from a human-understandable one (such as the high-level behavioral description), yet powerful tools are available to perform reverse engineering practices to extract design information and steal intellectual properties (Torrance and James, 2011) (Chipworks, 2012), (DARPA, 2012), (Fleet and Dransfield, 1998).

are essentially endowed with the job of fabricating the chips, so they should always have access to most (if not all) details of the design, and controls to the process. In addition, they have possess powerful tools to perform side channel attacks, or invasive attacks, physically, on legally unlocked chips. **Finally**, if a *common* key is used across all the fabricated chips, then such a key (that must be stored on every chip) becomes the most vulnerable part of the entire obfuscation mechanism. In other words, a leaked key from side-channel attack can be used to unlock other chips, thus compromising the entire security mechanism.

#### 1.2 Previous Works

Against IC piracy, a number of approaches have been proposed to embed in the design or on chip some forms of a designer's watermark, or a buyer's signature, such that illegal copies of a design or unauthorized chips can be detected and used in litigation to prove the ownership of that design or the source of piracy (Kahng et al., 1998a), (Koushanfar et al., 2005), (Kahng et al., 1998b), (Lach et al., 1998), (Rostami et al., 2013), (Caldwell et al., 2004), (Holcomb et al., 2009), (Ruhrmair et al., 1011), (Rostami et al., 2013). Such schemes can *passively detect* IC piracy practices, yet cannot *actively prevent* IC piracy from occurring. Although watermarking and fingerprinting schemes provide mechanisms for detection of illegal copies in case of litigation, they cannot prevent reverse engineering or unauthorized manufacturing of a design in the first place.

*Obfuscation*-based approaches (Roy and Koushanfar, 2008) (Rajendran et al., 2012b) (Alkabani and Koushanfar, 2007) (Chakraborty and Bhunia, 2008) (Chakraborty and Bhunia, 2009) (Rostami et al., 2013) (Baumgarten et al., 2010) (Khaleghi et al., 2015) (Zamanzadeh and Jahanian, 2013) follow such a preventive flow, with the main idea of "concealing / withholding" an important part of the design

Figure 1: Illustration of the design-manufacturing flow assumed by the obfuscation-based schemes

(which essentially constitutes the "key"), so that no manufactured chip can function correctly (thus considered "locked"), until being "activated" in a trusted facility, by restoring the missing part of the design into the chips. Then, the chips are considered "unlocked" and can be made available to the open market. As long as no direct access is available to read out the re-installed keys in the unlocked chips, an attacker cannot restore the entire design, or deliver any functioning chips without the knowledge of the key. Since the designer is the only one with the withheld information (thus the entire design) and controls the unlocking process for every chip, untrusted manufacturers are prevented from conducting IC piracy. Fig. 1 illustrates the overall flow of such obfuscation based schemes.

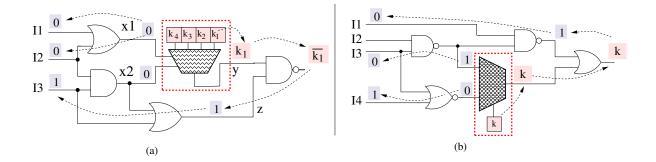

Fig. 2(a) shows an example of an obfuscation scheme from (Roy and Koushanfar, 2008)(Rajendran et al., 2012b), which allows the designer to configure the negation of any wires in a post-manufacturing stage. This is achieved by inserting additional XOR/XNOR gates, called *key gates*, on selected lines

Figure 2: (a) The content of K1 and K2 obfuscates the functionality of the circuit; (b) wiring interconnects are scrambled for obfuscation purposes; (c) obfuscation by replacing logic functions with LUTs.

of the original design, and use a 1-bit memory cell to control the negation of the other input of the key gate. The key gate thus acts as a configurable NOT gate, depending on the bit stored in the memory. For a manufactured circuit to function as the original design, the content of the memory cells connected to the key-gates must be configured correctly in the post-manufacturing stage (K1 = 0 and K2 = 1 in the case of Fig. 2(a)). Such memory configuration becomes the key and should be kept as a secret from the potential attackers (untrusted manufacturer).

Fig. 2(b) shows a different example of obfuscation, named *scrambling*, where the designer can choose to withhold key information about any interconnect configurations (Zamanzadeh and Jahanian, 2013). Fig. 2(b) shows the original connections of some wires, and then obfuscation is performed by replacing the interconnect configuration with a *Scrambler*. The scrambler in this example allows the 4 input lines and the 5 outputs to be connected in arbitrary ways, so that the correct configuration remains unknown to the attacker without having access to the content of the scrambling key, which will be applied after the manufacturing of the chips.

Fig. 2(c) shows a last example of obfuscation scheme using reconfigurable logic insertion to allow the designer to withhold any general function block in the design (Baumgarten et al., 2010) (Khaleghi et al., 2015). Here, various functional parts of the original design are replaced by Look-Up Tables (LUTs). These LUTs consist of memory cells which will eventually be configured to be the truth-table of the functions that were replaced, in the post-manufacturing stage, to restore the correct functionality of the chips.

#### 1.2.1 MUX-based implementation of obfuscation schemes

A key insight derived from a broad examination across various obfuscation approaches is that the memory cells (holding the "key") on chip usually provide controls to select, among multiple possibilities, the "correct" configuration, for an "unlocked" chip. The configuration possibilities could take various forms, such as the truth-table of a logic function 2(c), or how wires are connected together 2(b). Theoretically, with *k* selection bits, one can control / select among  $2^k$  choices, and this is the functionality of the fundamental digital logic building block of multiplexers (MUXs).

Based on the way of how a MUX is used in the context of various hardware obfuscation schemes, two categories of MUX-based implementation of obfuscation schemes exist, depending on where the key cells will be located. We therefore denote them as Content Obfuscator, used for implementing the obfuscation scheme shown in 2(c), and Wire Obfuscator, used for implementing the obfuscation scheme shown in 2(b).

Fig. 3(a) shows an example (of using LUT to obfuscate a 2-input / 2-output function) and the general form of a *Content Obfuscator*, that can be used to implement any general ways of using LUTs to replace an *N*-input / *M*-output logic function, including the key-gate based and LUT-based obfuscation

Figure 3: Two MUX-based obfuscation implementations with examples and general forms

approaches (Roy and Koushanfar, 2008) (Rajendran et al., 2012b) (Bao and Wang, 2014) (Rajendran et al., 2012a) (Baumgarten et al., 2010) (Khaleghi et al., 2015). The peripheral circuit is then connected to the MUX via the *N* select lines and *M* outputs, while the total number of  $M \times 2^N$  bit key cells (essentially forming the truth-table of a LUT) are located at the input lines of the MUX. The size (and therefore hardware costs) of a Content Obfuscator grows exponentially to its input width *N*.

Fig. 3(b) shows an example (of configuring interconnects between 8 inputs and 7 outputs) and the general form of a *Wire Obfuscator*, that can be used to implement the general interconnect mapping configurations between N and M ends. To choose from N potential input bits,  $l_g(N)$  cells are needed at the select lines of a MUX. When M output bits are needed to be chosen from the N input bits, a total of  $M \times l_g(N)$  key cells are needed, positioned at the select lines. This is a typical "multiplexing" model to provide "configurable switching" control ability, and can be used to model the wiring scramble obfuscation schemes (Zamanzadeh and Jahanian, 2013). When using MUXes to implement the mapping, the key cell values are located on the select lines of the MUX, and the peripheral circuits are connected to the MUX via the N input lines and M output lines. The number of key cells of a Wire Obfuscator grows

in logarithm scale to the input width N, while the MUX overhead (in terms of hardware cost) grows linearly to the input / output width (N, M).

#### **1.3** Attack Models and Assumptions

Despite the variety in their approaches, a common strategy among the existing hardware obfuscation schemes is to replace a certain piece of design information by a configurable module, eventually implemented with (tamper-resistant) memory cells on a chip. The post-manufacturing stage of configuring such memory cells makes it possible for the designer to both conceal / withhold some crucial design information from the potential attackers, as well as unlock fabricated chips. While most obfuscation approaches try to ensure that the required effort for an attacker to obtain the correct key is computation-ally hard, significant challenges still remain, as most approaches, as well as the selection of obfuscation targets, are ad-hoc based (Roy and Koushanfar, 2008) (Rajendran et al., 2012b) (Bao and Wang, 2014) (Rajendran et al., 2012a) (Alkabani and Koushanfar, 2007) (Baumgarten et al., 2010) (Zamanzadeh and Jahanian, 2013), making them susceptible to various attacks.

Assuming the strongest type of attackers, in the position of a manufacturer, we categorize the attacks into two types: 1) algorithmic attack on the partially available obfuscated design file, and 2) physical attack on an unlocked chip, as is illustrated in Fig. 4.

Rather than focusing on a specific set of detailed attack types and assumptions, we focus on an abstract level of attack taxonomy to provide a basis for defense mechanisms. For example, a number of different techniques can be applied in attempt to read out the content of the key memory cells on-chip, such as side-channel attacks or UV radiation, yet instead of proposing schemes to deal with each form

Figure 4: An overview of attack models, assumptions, and the proposed defensive mechanisms

of the attacks specifically, based on their physical access mechanisms, the proposed research will focus on how to ensure that an assumed leaked key will render useless for the attacker.

For algorithmic attacks, we assume that the attacker possesses: a) complete knowledge of the security scheme, b) gate-level netlist of the design, except for the obfuscation information, c) input / output access to some legally unlocked chips. The attacker is also assumed to possess powerful simulation tools and computation abilities. However, here the attacker is assumed to *not* have direct access to the keys on-chip. These assumptions are commonly recognized and adopted by many of the IC protection schemes, assuming a tamper-resisitant on-chip memory module to be used for the keys (Roy

9

and Koushanfar, 2008), (Rajendran et al., 2012b), (Chakraborty and Bhunia, 2008), (Chakraborty and Bhunia, 2009), (Baumgarten et al., 2010) (Khaleghi et al., 2015) (Zamanzadeh and Jahanian, 2013).

For the next stage of physical access attack category, the attacker is assumed to have everything from above in the algorithmic attack category. In addition, the attacker can gain *full* content of the key cells of a chip.

#### **1.3.0.1** Algorithmic attacks on obfuscated design files

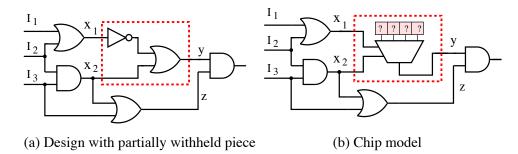

Via *brute-force attack*, as is shown to a Content Obfuscator in Fig. 5(a), an attacker needs to solve for all of the  $2^4 = 16$  possible patterns of the key, which is exponential to the key size and input size, and employ a verification process for every potential key pattern. The verification process involves, in the worst case scenario, applying all the possible input combinations (from 000 to 111 of  $2^3 = 8$ in this example), to both the simulated design (with the potential key), and the unlocked chip, for comparison. A mismatch will indicate the key pattern to be wrong, while a matching takes all the input patterns to validate a correct key pattern. Therefore, any obfuscation scheme with a Content Obfuscator is generally effective against brute-force attacks, by imposing a prohibitively expensive computational cost (exponential to both the key size and the input size) to the attacker.

Unfortunately, an attacker equipped with a partially available design and an unlocked chip can resort to the more effective *algorithmic attack*, by focusing on **one key cell at a time**. The main idea is to use an input combination that can successfully "isolate" one target key cell, and propagate its value towards the outputs. In the example shown in Fig. 5(a), if an input combination can "activate" the address of key cell  $k_1$ , and propagate the value cell to the primary output, then the value of  $k_1$  can be obtained by observing the output of the legally unlocked chip. If each key cell can be cracked this way, then the

Figure 5: Examples of algorithmic attacks on: (a) a Content Obfuscator (b) a Wire Obfuscator

number of trials for the attacker will be reduced to the size of the key - a complete collapse from the brute-force attack complexity.

Fig. 5(a) shows the process of algorithmic attack for finding such an input combination to crack  $k_1$ . In order to activate the address of  $k_1$ , the attacker needs to use an input combination that makes x1 = x2 = 0. Based on the available design, it can be deduced that there are two input combinations for (I1, I2, I3) that can satisfy this condition: (0,0,0) or (0,0,1), as both patterns will select the value of  $k_1$  to appear on wire y. However, to ensure that  $k_1$  can be propagated all the way to the primary output, (0,0,0) does not qualify, because the signal at y will eventually be blocked by z = 0. On the other hand, input combination (0,0,1) can successfully reveal  $\bar{k_1}$  to the primary output. In general, using algorithmic attacks to solve for a particular key cell of a Content Obfuscator, one needs to solve for the primary input combination, such that: 1) the address for the key cell is selected, and 2) the value (or its negation) of the cell can be propagated to one of the primary outputs.

A similar attack can be performed on a Wire Obfuscator, shown in Fig. 5(b). In this example, since the key is connected to the selector of the MUX, there is no direct way to send it to the output of the MUX. However, the attacker can try to send a pair of opposite values (1 and 0) to the input lines of the MUX, and observe the value on the output to deduce the bit at the selection line. One way to achieve this in the example shown in Fig. 5(b) is by making I3 = 0 and I4 = 1, and then set I1 = 0 to drive the value of *k* to the output end.

Such an algorithmic attack has been shown to be equivalent to the "Automatic Test Pattern Generation (ATPG)" problem, which is a classical NP-Complete problem in the domain of digital testing (Abramovici et al., 1990)<sup>1</sup>. Due to its NP-Complete complexity, sometimes it is assumed that algorithmic attack poses a high cost for the attackers.

However, while it is true that each run of the the algorithmic attack is either NP-Complete or NP-Hard (Abramovici et al., 1990) (Rajendran et al., 2012b) (Erb et al., 2013), our preliminary research data verify that it is dangerous for a protection scheme to rely solely on the hardness of such NP-Complete/NP-Hard problems, per se, because even though such problems can take exponentially scaled time to solve *in the worst case* they could be easily solvable in some of the best cases, when constraints are not stringent (Khaleghi et al., 2015). The need of systematically introduced entanglement against algorithmic attacks is shown in Fig. 12: To perform algorithmic attacks on content obfuscator, while some of the worst cases could take up to 250ms to solve one key cell, the median runtime of all the benchmarks is as little as 27.7ms. Furthermore, due to its important application in chip testing, many

<sup>&</sup>lt;sup>1</sup>ATPG by itself is concerned with finding an input pattern that can distinguish between the correct circuit and a faulty circuit, assuming a fault occurring at a particular location.

powerful tools and heuristic algorithms are available to tackle the ATPG problem effectively. For instance, a SAT-based algorithmic attack has been shown to be successful in retrieving the full / partial key from a fabricated chip (Subramanyan et al., 2015) efficiently.

#### **1.3.0.2** Physical attacks on unlocked chips

The algorithmic attack assumes the attacker to have access to the input/output of an unlocked chip, but no access to the key memory cells. Such an assumption is held by most obfuscation schemes, emphasizing that the memory cells where the key is stored on chip can be made tamper-resistent. However, physical access attacks do pose a powerful threat when the attackers are equipped with strong tools and abundant funds (Joye, 2009) (Stanojlovic and Petkovic, 2010) (Samyde et al., 2002) (Rakers et al., 2001) (Tiri et al., 2002) (Moore et al., 2003) (Iyengar et al., 2016) (Rostami et al., 2013) (Skorobogatov, 2009) (Skorobogatov, 2010). Even if only a portion of all the key cells are gained, in a statistical way, such information could still be used to aid the algorithmic attack to accelerate the cracking of the rest of the key tremendously. Even though such physical attacks are harder to carry out, and their results are probabilistic rather than deterministic, their existence has to be taken into account and modeled with their strongest form, to provide a solid ground of defense mechanisms. For the proposed research, we categorize the physical attack approaches based on *what* they are able to achieve, in the obfuscation paradigm, rather than *how* they are carried out.

Write-in of Key cells: A *write-in* attack is defined as for an attacker to set the value of some key cells of an unlocked chip, independent of the ability to read out their values. This is possible, as there needs to be a mechanism for the designer to write in the key into all the chips in the post-manufacturing stage. The same mechanism to write-in might be exposed to the attacker, even if the designer tries

to remove the channel after the unlock process, because strong invasive schemes are possible from a manufacturer, such as a hidden write-access at the manufacturing stage, or via advanced tools such as radiation, etc. (Skorobogatov, 2009) (Skorobogatov, 2010).

Such write-in access can be used to efficiently help an algorithmic attack: an attacker can try out a specific value (say 1) by writing it into the key cell of an unlocked chip A, and then test it out for a number of input combinations and against another unlocked chip B with the correct key. During this process, a single mismatch can verify that the trial value (1 for example) of the target key cell is wrong, and therefore the true key value should be the opposite (in this case 0). In the case that no mismatches are found for a while, the inserted value is likely to be the actual content of the target cell, and the attacker can write in the opposite value into the same cell to seek for a mismatch as verification. This way, the attacker has a large probability of cracking a portion of the key cells within a limited number of trials.

**Read-Out of Key cells:** Undoubtedly, the most desirable ability from an attacker's point of view is to read out the values of key cells, from an unlocked chip. This is possible for powerful attackers - to probe and read out the content of the key memory directly, with approaches such as Side-Chanel attacks despite being expensive and inexact, to at least read out a portion of the key (Joye, 2009) (Stanojlovic and Petkovic, 2010) (Samyde et al., 2002) (Rakers et al., 2001) (Tiri et al., 2002) (Moore et al., 2003) (Jyengar et al., 2016) (Rostami et al., 2013).

In the extreme case of a completely leaked key, assuming a common key is used to obfuscate all the chips, the attacker achieves the ultimate goal of cracking the obfuscation scheme: an untrusted manufacturer can then fabricate more chips and directly use the leaked key to unlock them for sale. Overall, regardless of the various ways that an attacker might have to read out the content of the protected memory on chip, such a capability needs to be considered in a worst-case scenario, to construct a provably strong defensive mechanism.

#### 1.4 Organization

The organization of this dissertation is as follows. Chapter 2 deals with the algorithmic attacks by proposing a novel protection scheme, called Entanglement: 1) the algorithmic attacks are prevented by forcing the attacker to solve a huge number of problems of high computational complexity; 2) the attack cost (in terms of computational complexity) is quantitatively controllable at the designer's end, with low hardware overhead: while the cost of attack can be increased exponentially, the hardware overhead imposed on the designer's side grows only linearly.

Chapter 3 lays out the foundation for preventing the physical attacks by proposing the idea of "group formation" to exploit the nano-scale analog disorders of devices for making "strong" Physically Unclonable Functions (PUFs). PUFs are an emerging technology that could play the key roles in various security applications. Depending upon the size of its truth-table, i.e., the search space for an attacker to fully specify its behavior, a PUF can be categorized as either "weak" or "strong". This chapter presents a scheme for making a strong PUF based on Spin-Transfer Torque Magnetic RAM (STT-MRAM), an emerging nano-electronic memory device. In the end, this chapter sheds light on how to make a strong PUF in general, by extending the idea of group formation beyond the STT-MRAM devices.

Chapter 4 proposes a *strong* PUF-based hardware obfuscation scheme to effectively prevent IC piracy even in the case of a leaked key from some activated chip. To ensure that each chip has a unique key, PUFs have been proposed to be integrated with hardware obfuscation. Such a paradigm

is constrained to use *weak* PUFs, because, to uniquely set the key (the content of the configurable module) for each chip, the designer needs to fully characterize the PUFs for all the chips. In this chapter, we argue that a powerful attacker in the position of a manufacturer can fully characterize all the weak PUFs, and use any leaked key to break the obfuscation framework. This chapter proposes to employ *strong* PUFs (with *huge* search space of truth-table) into the obfuscation framework, against such an attacker/manufacturer. While it is impossible for an attacker to fully characterize the strong PUFs, the main challenge becomes ensuring that the designer does not need to bear the burden of fully characterizing the strong PUFs to generate a unique key per-chip. This is achieved by employing an *Obfuscator* block into the design, which enables the designer to select an arbitrarily subset of the strong PUF to work, while guaranteeing that the architecture does not reveal to the attacker/manufacturer of the choices made by the designer.

Chapter 5 concludes this dissertation.

#### CHAPTER 2

# HARDWARE OBFUSCATION THROUGH ENTANGLEMENT AGAINST ALGORITHMIC ATTACKS

Parts of this chapter have been presented in (Khaleghi et al., 2015). Copyright © 2015, IEEE.

#### 2.1 Introduction

In the past, the IC industry involved the vertical chain of chip manufacturing model, where all the steps, such as design, synthesis, verification, fabrication and test of IC's, were carried out in presumably trustable facilities. However, the continuous decrease in feature sizes imposes the huge cost of upgrading fabrication facilities to meet the growing technological requirements for modern IC fabrication. Furthermore, due to the increased time-to-market pressure for many high-speed and low-power IC's, it is no longer feasible for companies to carry out all the levels of design single-handedly (Roy and Koushanfar, 2008). This has led to the formation of a series of pure contract silicon foundries that specialized in IC fabrication. Consequently, many renowned semiconductor companies have become completely fab-less today.

Globalization of the semiconductor industry has raised serious concerns about trustworthy hardware. Since IC designers no longer have complete control over the manufacturing process, a design is prone to various "hardware attacks", such as *IC Piracy* and *Reverse Engineering* (Roy and Koushanfar, 2008), (Torrance and James, 2011): IC piracy usually refers to an untrusted manufacturer, producing more chips than authorized at a marginal cost, and selling them illegally. Furthemore, an untrusted manufacturer can also steal the design information by employing various reverse engineering techniques.

A strong IC protection scheme must be resilient to a powerful attacker (in the position of a manufacturer), with strong knowledge, tools, and facilities. Similarly to the modern cryptography schemes, hardware security should rely solely on the secrecy of a certain key, rather than the secrecy of the scheme itself. Based on these assumptions, we adopt the following threat models:

- *Who is the attacker? When does the attack happen?* We assume the attacker enters after the creation of the gate-level netlist. It could be any party in the untrusted IC manufacturing chain, which has access to any forms of a design (such as layout, mask, etc.) that is revealed during these stages.

- *What is the goal of the attacker?* We assume that the attacker aims to either gain knowledge of the design (reverse engineering), or produce illegal copies of the functioning IC's (piracy).

- What are accessible by the attacker? How does it attack? We assume the attacker to have: 1) the complete knowledge of the gate-level netlist; either by direct access from the IC design or by reverse engineering of the layout, mask, or a manufactured IC. 2) the power of performing simulation, modifying the design, and manufacturing IC's according to a modified design; 3) full knowledge of the security scheme, except for some "key" that can be kept secret by the designer;

4) access to functional IC's, purchased from the open market, which have been activated by the designer.

The Design Withholding category of techniques work by selecting and replacing a small portion of the design with a reconfigurable block, so that the manufactured chips will not function properly, until they are activated in a trusted facility (Baumgarten et al., 2010), (Zamanzadeh and Jahanian, 2013). Generally, the most powerful way for an attacker to recover the withheld piece is to apply algorithmic attacks on the available part of the design. This actually translates into the practice of solving a number of problems of NP-Complete or higher complexities. We argue that purely relying on the complexity of such problems does not form a strong protection foundation, as these problems might be solvable in a short amount of time under many non-worst-case scenarios.

The proposed work in this chapter substantially strengthens the framework of Design Withholding by what we refer to as *Entanglement*. The proposed scheme does not rely on the difficulty for an attacker to solve some problems of high complexities, but rather, on the exponentially boosted **number** of such problems that an attacker has to solve. Entanglement gives the designer the full control of scaling up the attacking cost **exponentially**, at a **linearly** increased hardware cost.

Two ways of Entanglement are proposed: 1) the "External Entanglement" technique can exponentially boost the *number* of NP-Complete/NP-Hard problems needed for an attacker to solve, for a *small* withheld function of a design; 2) the "Internal Entanglement" technique decomposes a *large* withheld function into *multiple* pieces, such that the necessitated hardware on the designer's side is efficiently shrunk, while the attacking cost remains huge as that of the original withheld large piece.

#### 2.2 Previous Works

IC Piracy and Reverse Engineering are highly difficult to address, because of the strong position of an untrusted manufacturer: the manufacturer is in full control of analyzing and modifying the design at the final stage for manufacturing. Unsurprisingly, existing IC protection techniques proposed in the past are mostly passive or ad-hoc solutions.

In the category of *watermarking*-based approaches, a designer's watermark is embedded upon fabrication and cannot be removed from the IC. When an illegal copy of a design is found, the designer will retrieve the watermark in litigation to claim the ownership of that design (Kahng et al., 1998a) (Koushanfar et al., 2005) (Kahng et al., 1998b) (Lach et al., 1998), (Rostami et al., 2013). *Fingerprinting1* techniques work by embedding both the designer's watermark and the buyer's signature in the design. Not only can the designer claim the ownership of a design, but it can also reveal the source of piracy by retrieving the buyer's signature (Caldwell et al., 2004) (Holcomb et al., 2009) (Ruhrmair et al., 1011). Such schemes can passively provide mechanisms for detection of illegal copies, yet cannot *prevent* reverse engineering or IC Piracy from occurring.

*Obfuscation*-based approaches, on the other hand, aim at "hiding" the design from potential attackers with extra obfuscating hardware, so that no manufactured IC can function correctly, unless being activated by its designer. Since the designer is the only one who knows the correct key, it can control the number of functioning IC's, and prevent untrusted manufacturer from conducting IC piracy (Roy and Koushanfar, 2008),(Rajendran et al., 2012b), (Alkabani and Koushanfar, 2007), (Chakraborty and Bhunia, 2008) (Chakraborty and Bhunia, 2009). Most obfuscation-based approaches try to ensure that the required effort for an attacker to obtain the correct key is computationally impractical. However, since the entire design, despite being obfuscated, is available to the manufacturer, if the attacker is able to identify the part of the design dedicated for the obfuscation purpose, a functioning IC might be pro-

duced by discarding the obfuscating circuitry entirely, thus bypassing the difficult path of searching for the key to unlock the obfuscated design.

The category of *withheld*-based approaches, on the other hand, try to ensure that the entire design is not made available to the manufacture, thus taking away the opportunity for the attacker to gain the full knowledge of the design. Usually, some part of the design is replaced with several lookup-tables (LUT's), which will be configured in a trusted facility after manufacturing of the chips (Baumgarten et al., 2010), (Bao and Wang, 2014). Another technique in a similar direction works by withholding a part of the wiring topology during the design process, and inserting the correct wiring topology after fabrication (Zamanzadeh and Jahanian, 2013).

In fact, the obfuscation-based techniques can be covered in the withheld-based framework, making it easier to use the latter to develop theoretical foundation for trustworthy schemes. Furthermore, as opposed to the obfuscation-based approaches where the entire (obfuscated) design is made available the manufacturer, some parts of the design are never given to the manufacturer in the withheld-based approaches. This provides a stronger position for the withheld-based approaches to take away the opportunity for piracy and reverse engineering. Nonetheless, as we will show in the next section, the withheld-based techniques are susceptible to a category of algorithmic attacks, called *ATPG-based* attacks, and are not scalable due to the imposed hardware overhead on the designer's side.

## 2.3 Preliminaries and Motivation: Design Withholding Framework

In this section, we provide the models for the Design Withholding framework as a basis to build up the proposed Entanglement schemes. We also present the models and costs on both the attacker's side and the designer's side.

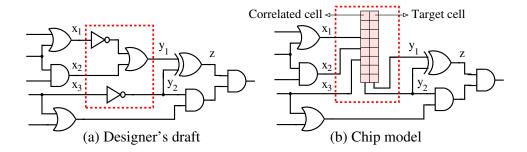

Figure 6: An example, where a part of a design (including 2 inputs and 1 output) is replaced with a LUT on chip.

## 2.3.1 Withholding a single-output function

Suppose the circuit in Fig. 6(a) is an original design that needs to be fabricated, with a part of the design (shown in the rectangle) to be withheld from the manufacturer. Since the withheld piece is a Boolean function ( $y = x_1 + x_2$ ) with 2 inputs and 1 output, it can be replaced by a 4:1 lookup table (LUT) on chip, as is shown in Fig. 6(b). Without the correct content of the LUT, none of the manufactured chips will work as designed, until the LUT is configured inside a trusted facility, according to the withheld function.

To recover the original design, an attacker needs to find the key: the content of the LUT. For the chips on the market that have been activated, there is no direct access for the attacker to probe or observe the securely stored content of the LUT. Nonetheless, the attacker does have access to the primary inputs and outputs of such legally activated chips.

With the help of a fully activated chip and the partially available design (everything except for the withheld part), the attacker can perform an "ATPG-based" attack. For example, in order to find out

the value of the first cell in the LUT, the attacker needs to first activate its address by finding an input combination that makes  $x_1 = x_2 = 0$ . There are two input combinations that can satisfy this condition:  $(I_1 = I_2 = I_3 = 0)$  or  $(I_1 = I_2 = 0, I_3 = 1)$ . Both patterns can select the value of the first memory cell to the wire y. The next job of the attacker is to make sure that this value at y is propagated to the primary output of the circuit. It turns out that the first input combination  $(I_1 = I_2 = I_3 = 0)$  would not work: it will block the propagation of signal y, i.e., the primary output of the circuit would be dominated by the value of the other input bit of the final AND gate (signal z), which is 0. On the other hand, the other input combination  $(I_1 = I_2 = 0, I_3 = 1)$  can successfully reveal the first bit of the LUT to the primary output.

In general, for every single bit of the LUT, the attacker needs to solve for the primary input combination, such that: 1) the address for the specific cell is selected, and 2) the value of this cell can be propagated (in its original or negated form) to one of the primary outputs. If such an input combination can be found, it can be applied to the primary inputs of the activated chip, and the content of the target cell will be revealed at the output end of the activated chip.

This problem is equivalent to the classical problem of Automatic Test Pattern Generation (ATPG) in IC testing, which is of NP-Complete complexity (Abramovici et al., 1990). In general, for every single bit of the LUT, an attacker has to perform such an "ATPG-based" attack, with the goal of finding a certain combination of the primary inputs to "stimulate" a cell, while at the same time, "propagate" the cell's content to one of the primary outputs. This process can be done for every cell in parallel, to finally recover the withheld function of the design.

Figure 7: Withholding a multi-output function to elevate each attack from NP-Complete to NP-Hard complexity.

## 2.3.2 Withholding a multiple-output function

Fig. 7(a) shows an example of withholding a multiple-output function with 3 inputs  $(x_1, x_2, x_3)$  and 2 outputs  $(y_1 \text{ and } y_2)$ . Accordingly, a LUT with 16 memory cells is required to replace the 2-output withheld function (8 cells for each output), as is shown in Fig. 7(b).

We argue that the change from a single-output to a multiple-output function has made a qualitatively different problem to solve for an attacker. This is due to the *correlation* between the multiple output bits  $(y_1 \text{ and } y_2)$ . For example, as is shown in Fig. 7(b), in order to find the value of the right column of the first address in the LUT (shown as the "Target cell"), the attacker needs to solve the primary inputs to: 1) activate the address of  $x_1 = x_2 = x_3 = 0$ , and 2) propagate the value of the Target cell from  $y_1$  to the primary output of the circuit. However, any input combination that activates the Target cell at  $y_1$  would also activate the cell of the left column at  $y_2$  (shown as the "Correlated cell") at the same time. The value of this cell is unknown to the attacker, despite the fully specified primary inputs. Due to the correlation between these two cells, an attacker cannot solve each of them independently, or in parallel.

Instead, each has to be modeled as a distinct unknown variable in the ATPG algorithm to be solved at the same time.

Propagating the value of the Target cell in the presence of the unknown values of many Correlated cells is qualitatively different, and a harder problem to address, because keeping track of all the unknown values' symbolic computation simultaneously will quickly become intrackable as the number of unknown values increases. Alternatively, if the attacker does not keep each unknown as a dedicated variable, the computation will quickly lose precision, because to too many signals of unknown values are mingled together. For example, the attacker cannot determine the output of the XOR gate (signal z), because both of the inputs of this gate ( $y_1$  and  $y_2$ ) have unknown values. In other words, as opposed to the case of a single-output function, the attacker cannot propagate the value of the Target cell ( $y_1$ ) to the next level (z), due to the unknown Correlated cell ( $y_2$ ) that is not accessible by the attacker.

Such an ATPG problem with unknown values is of NP-Hard complexity (Erb et al., 2013), and is significantly harder than the single-output function case, which is of NP-Complete complexity. Furthermore, it is also shown that most existing deterministic ATPG tools are not able to handle such tasks efficiently (Erb et al., 2013).

### 2.3.3 Challenges for design withholding framework

In this section, we provide the cost analysis for the designer (in terms of hardware) and for the attacker (in terms of computational complexity) to crack the Design Withholding scheme.

Assuming that the withheld function has *n* inputs  $\{x_1, x_2, ..., x_n\}$  and *m* outputs  $\{y_1, y_2, ..., y_m\}$ , it can be modeled by an LUT with *n* selection lines (addressing to  $2^n$  memory cells), and *m* output lines. Accordingly,  $2^n \times m$  memory bits are needed, in addition to the MUXes, constituting the hardware cost for the designer. On the other hand, an attacker has to solve  $2^n \times m$  problems, each with NP-Complete (for m = 1) or NP-Hard (for m > 1) complexity.

However, it is dangerous for a protection scheme to rely solely on the hardness of NP-Complete/NP-Hard problems, per se, because even though such problems can take exponentially scaled time to solve in the worst case, they could be easily solvable in some of the best cases, when constraints are not stringent (Fujiwara and Toida, 1982). Consequently, there is no guarantee that an attacker, aided by powerful ATPG tools, cannot obtain the desired information within a reasonable time limit.

In order to achieve a theoretically sound barrier, the designer should rely on the *number* of NP-Complete/NP-Hard problems for an attacker to solve, rather than the difficulty of solving the problems itself. Scaling up the number of such problems essentially means to increase the number of memory cells to crack. Since the memory stores the truth table of the withheld function, the increase in the number of memory cells is exponential to the size of the withheld function. However, the hardware cost for the designer to implement the withheld piece grows at the same exponential rate, making it unrealistic for a designer to bear the cost.

As an example, if the designer wants to double the number of ATPG-based attacks by withholding one more input signal (thus doubling the truth table of the original plan), the size of LUT would double to be  $2^{n+1} \times m$ . Such a doubling in search space of the attacker is achieved at the cost of doubling the hardware on each chip. This is apparently not a scalable approach to deliver a desired level of security.

## 2.4 Entanglement

In this section, we propose two *Entanglement* techniques: 1) drastically increase the cost of the attacker for a small withheld function, without boosting the hardware overhead; 2) drastically decrease the

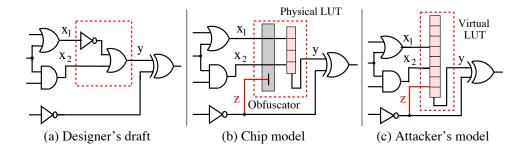

Figure 8: External Entanglement: a) the original withheld function; b) designer's cost (LUT size) kept low with the help of an Obfuscator; c) the attacker has to solve a much larger number of cells, due to the entanglement.

hardware cost of a large withheld function, while maintaining the high cost to attack. In both schemes, the computational complexity for an attacker to recover the withheld information is quantitatively controllable at the designer's end. Furthermore, while the cost of attack can be scaled up exponentially, the hardware overhead grows only linearly on the designer's side.

# 2.4.1 External entanglement

As we discussed in the previous section, an ideal protection scheme must force an attacker to recover a huge truth table, while the imposed hardware overhead on the designer should be much less. The main idea of achieving such a goal is by introducing some "noise" or redundancy, such that one can virtually enlarge the search space for an attacker. This can be achieved if the attacker cannot distinguish between the added redundant part ("noise") and the original withheld piece ("signal"). In other words, if the attacker lacks some crucial information to identify the small subset of "signal" among the "noise", it will have to treat them the same way and solve them all. Meanwhile, the designer, with the full knowledge of the signal/noise distinction, is able to pay the small cost with respect to the signal part

Figure 9: General structure of a programmable Obfuscator.

only. If such a scheme can be developed at a low hardware overhead, it can successfully achieve the goals of IC piracy and reverse engineering prevention.