Design and Optimization of GaN-Based Power Semiconductor Transistors

BY

ALBERT COLON B.S., University of Illinois at Chicago, 2012

## THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2017

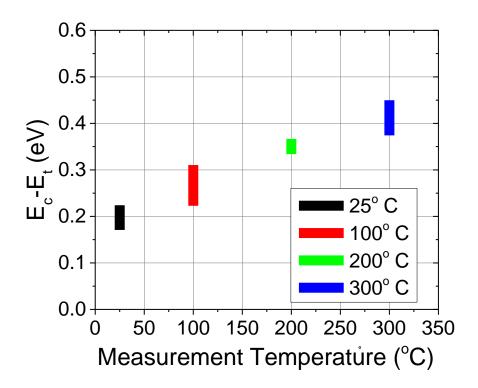

Chicago, Illinois

Defense Committee:

Junxia(Lucy) Shi, Chair and Advisor Michael Stroscio Vitali Metlushko Antonio DiVenere, Nanotechnology Core Facility Ralu Divan, Argonne National Laboratory

To My Parents and Girlfriend, Adriana Macias

#### ACKNOWLEDGEMENTS

There are many people I have encountered in my studies that have been fundamental to the success of this thesis. First, I would like to express my gratitude toward my advisor, Dr. Lucy Shi. She has been a constant source of support, guidance and inspiration. Her utmost patience, understanding and confidence have been instrumental for me and completion of this thesis would not have been possible without her. I also thank Dr. Michael Stroscio and Dr. Vitali Metlushko for being on both my committee and excellent instructors in both undergraduate and graduate courses, shaping my education.

I would also like to thank all the staff at Argonne's Center for Nanoscale Materials but most notably Dr. Ralu Divan and Liliana Stan. They have been a great source of knowledge, encouragement and examples. I would also like to thank Ralu for being on my committee.

Dr. Antonio DiVenere and Dr. Seyoung An who have helped me tremendously at UIC working at the Nanotechnology Core Facility. Dr. Seyoung An who has shown me a different perspective of cleanroom tools and learning from him has been truly a pleasure and Dr. Antonio DiVenere for both being on my committee and for all the long helpful discussions we have had.

I am also extremely grateful to the folks at NXP semiconductors especially Dr. Bruce Green and Dr. Karen Moore. I sincerely appreciate all their advice and support throughout my graduate career. They have truly kept me on track with my research progress.

I would also like to thank my fellow labmates for all their help and discussions: Chenjie Tang, Nathaniel Nicandro and Xiaowei Wang, as well as all the graduate assistants at NCF, whom I've worked with: Khodr Maamari, Jacek Lechowicz, Tejumade Durowade, Tara Foroozan and Nick Anderson. They have kept me sane throughout graduate studies and I have appreciated all the time spent together.

#### **ACKNOWLEDGMENTS** (continued)

I would also like to thank all the staff at Cornell's NanoScale Science and Technology Facility, especially Mike Skvarla. During my early years as a graduate student, he was patient enough with me to teach me about work in the cleanroom.

Also on the list is all the helpful administrative staff at UIC's ECE department: Mona Hurt, Ala Wroblewski, Tina Alvarado, Erica Plys, Martha Salinas, Evelyn Reyes, Beverley Miller and Mihai Bora.

Lastly, I am extremely grateful for the love, support and guidance from all my family and my girlfriend. They have been with me through it all; through the dark and low times as well as the happy best times.

AC

## **CONTRIBUTIONS OF AUTHORS**

Chapter 3 is published in Elsevier (Solid State Electronics) having co-authors of my advisor. Chapter 4 and Chapter 5 are both published in AIP Publishing LLC (Journal of Vacuum Science & Technology B and Journal of Vacuum Science & Technology A, respectively) having co-authors consisting of Liliana Stan, Ralu Divan and my advisor. In both cases, Liliana Stan helped me with the deposition of the various insulators using atomic layer deposition and x-ray diffraction measurements and Ralu Divan assisted with other fabrication aspects including electron beam lithography and dry-etching. However, all figures and writing in these letters are originally my own. Permission for re-use of Chapters 3, 4 and 5 are all located in Appendix C under C.1, C.2 and C.3, respectively. All other chapters in this thesis is un-published work.

## **TABLE OF CONTENTS**

## **CHAPTER**

| 1. | INTRODUCTION |                                                       |     |  |  |  |  |

|----|--------------|-------------------------------------------------------|-----|--|--|--|--|

|    | 1.1.         | Overview of GaN-Technology                            | 1   |  |  |  |  |

|    | 1.2.         | Organization of Chapters                              | 4   |  |  |  |  |

|    | 1.3.         | Introduction to Ohmic Contacts                        |     |  |  |  |  |

|    | 1.3.1.       | Literature Review on ohmic contacts                   | 8   |  |  |  |  |

|    | 1.3.2.       | Ohmic Contact Pre-Metallization Processing            | 8   |  |  |  |  |

|    | 1.3.3.       | Ohmic Contact Metal Deposition                        | 11  |  |  |  |  |

|    | 1.3.4.       | Ohmic post-metal processing                           | 15  |  |  |  |  |

|    | 1.4.         | Introduction to Dielectrics                           |     |  |  |  |  |

|    | 1.4.1.       | Background on interface trap density extraction       | 16  |  |  |  |  |

|    | 1.4.2.       | Metal-Insulator-Semiconductor Capacitor               | 17  |  |  |  |  |

|    | 1.4.3.       | High-κ Dielectrics                                    | 26  |  |  |  |  |

|    | 1.4.4.       | 0                                                     |     |  |  |  |  |

|    |              |                                                       |     |  |  |  |  |

| 2. | OHM          | IC CONTACT OPTIMIZATION                               | 31  |  |  |  |  |

| 2. | 2.1.         | Titanium/Aluminum for Ohmic Contacts                  |     |  |  |  |  |

|    | 2.2.         | Silicon in Ti/Al/Ni/Au Stack                          |     |  |  |  |  |

|    | 2.3.         | Ohmic Recess                                          | 41  |  |  |  |  |

|    | 2.4.         | Gold-Free Contacts                                    | 44  |  |  |  |  |

|    | 2.5.         | Conclusions                                           | 48  |  |  |  |  |

|    |              |                                                       |     |  |  |  |  |

| 3. | HIGH         | Ι-κ INSULATING MATERIALS FOR AlGaN/GaN METAL INSULAT  | ſOR |  |  |  |  |

|    | SEMI         | CONDUCTOR HETEROJUNCTION FIELD EFECT TRANSISTORS      | 49  |  |  |  |  |

|    | 3.1.         | Introduction                                          | 49  |  |  |  |  |

|    | 3.2.         | Experiment                                            | 51  |  |  |  |  |

|    | 3.3.         | Device Characteristics                                | 53  |  |  |  |  |

|    | 3.3.1.       | MISHFET                                               | 53  |  |  |  |  |

|    | 3.3.2.       | MISHCAP                                               | 60  |  |  |  |  |

|    | 3.3.3.       | Interface Trap Characterization                       | 63  |  |  |  |  |

|    | 3.4.         | Conclusions                                           | 68  |  |  |  |  |

|    |              |                                                       |     |  |  |  |  |

| 4. | INVE         | STIGATING COMPOSITIONAL EFFECTS OF ATOMIC LAYER       |     |  |  |  |  |

|    | DEPC         | SITION TERNARY DIELECTRIC Ti-Al-O ON MISH CAPACITOR   |     |  |  |  |  |

|    | STRU         | CTURE FOR GATE INSULATION OF InAIN/GaN and AlGaN/GaN. | 69  |  |  |  |  |

|    | 4.1.         | Introduction                                          | 69  |  |  |  |  |

|    | 4.2.         | Experimental                                          | 71  |  |  |  |  |

|    | 4.3.         | Results and Discussion                                | 74  |  |  |  |  |

|    | 4.4.         | Conclusions                                           | 83  |  |  |  |  |

# TABLE OF CONTENTS (continued)

| <u>CHAPTER</u> |                                                |                                                                                                                                                                                                                                       | <u>PAGE</u>                            |

|----------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5.             | FOR T                                          | RPORATION OF AI OR Hf IN ATOMIC LAYER DEPOSITION TI<br>ERNARY DIELECTRIC INSULATION OF InAIN/GaN AND<br>I/GaN MISH STRUCTURE<br>Introduction<br>Experimental<br>Results and Discussion<br>Conclusions                                 | 85<br>85<br>89<br>91                   |

| 6.             | ENHA<br>6.1.<br>6.2.<br>6.3.<br>6.4.<br>6.4.1. | GaN TRANSISTOR OFF-STATE BREAKDOWN VOLTAGE<br>NCEMENT BY PASSIVATION<br>Introduction<br>Experimental<br>Passivation Layer Choice<br>Results and Discussion<br>Low-Voltage DC Performance<br>Off-State Breakdown Voltage<br>Conclusion | 107<br>107<br>110<br>112<br>112<br>115 |

| 7.<br>Cited    | 7.1.<br>7.2.                                   | LUSIONS AND FUTURE WORK<br>Conclusion<br>Future Work                                                                                                                                                                                  | 119<br>120                             |

|                | ndices<br>Appen<br>Appen<br>Appen              | dix A<br>dix B<br>dix C<br>dix D                                                                                                                                                                                                      | 137<br>138<br>149<br>158               |

| Vita           |                                                |                                                                                                                                                                                                                                       | 181                                    |

## LIST OF TABLES

| <u>TABLE</u> | PAGE                                                                                                                                                                                                                                      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι.           | LIST OF REPORTED REACTIVE ION ETCHING PROCESS<br>PARAMETERS WHICH MAY BE USED FOR OHMIC CONTACT<br>PRE-METALLIZATION TREATMENT ON GAN                                                                                                     |

| Π.           | COMPARISONS OF RECENT OHMIC CONTACT SCHEMES USING<br>THE REGROWTH METHOD FOR INALN/GAN DEVICES AND<br>THEIR RESULTING CONTACT RESISTANCE                                                                                                  |

| 111.         | LIST OF REPORTED GOLD-FREE OHMIC CONTACTS ON GAN<br>SEMICONDUCTORS LISTED WITH THEIR RESPECTIVE<br>PROCESSING CONDITIONS AND RESULTS                                                                                                      |

| IV.          | LIST OF OHMIC CONTACTS ON GAN USING EITHER SI OR GE TO<br>IMPROVE THE CONTACT RESISTANCE14                                                                                                                                                |

| V.           | LIST OF VARIOUS INSULATORS DEPOSITED ON GAN-<br>MATERIALS AND THEIR RESPECTIVE EXTRACTED INTERFACE<br>TRAP DENSITIES. LISTED, IS ALSO THE D <sub>IT</sub> EXTRACTION<br>TECHNIQUE                                                         |

| VI.          | DEPOSITION RATE CALIBRATION ON THE VARIAN E-BEAM<br>EVAPORATOR                                                                                                                                                                            |

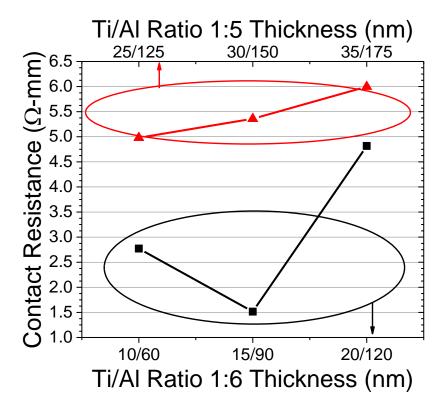

| VII.         | LIST OF THE TWO DIFFERENT TI:AL RATIOS USED (1:5 AND 1:6)<br>AND THE TESTED RESPECTIVE THICKNESSES FOR OHMIC<br>CONTACTS USING THE TI/AL/MO/AU STANDARD STACK                                                                             |

| VIII.        | SUMMARY OF LOWEST CONTACT RESISTANCES MEASURED<br>USING A THIN LAYER OF SI IN THE STANDARD STACK<br>TI/AL/NI/AU ON ALGAN/GAN SUBSTRATES                                                                                                   |

| IX.          | ETCHING RECIPES TESTED FOR OHMIC RECESS PROCESS<br>USING AN OXFORD ICP-RIE SYSTEM                                                                                                                                                         |

| х.           | GOLD-FREE OHMIC RECESSED CONTACTS WITH RAPID<br>THERMAL ANNEALING AMBIENT CONDITIONS VARIED. THE<br>ANNEALING WAS PERFORMED AT 450° C FOR 30 S                                                                                            |

| XI.          | LIST OF OPTIMIZED OHMIC CONTACTS PROCESSING ON GAN.<br>METAL THICKNESSES AND ANNEALING CONDITIONS WERE<br>OPTIMIZED FOR THE LISTED METALLIZATION TYPE                                                                                     |

| XII.         | ALD FILMS PROCESSING CONDITIONS, THICKNESS AND<br>COMPOSITION. 1:0 RATIO IS THE REFERENCE TIO <sub>2</sub> FILM. TIO <sub>2</sub><br>AND AL <sub>2</sub> O <sub>3</sub> RATIO WAS VARIED TO PRODUCE DIFFERENT AL-<br>CONTENT IN THE FILMS |

## LIST OF TABLES (continued)

## **TABLE**

## PAGE

## LIST OF FIGURES

## **FIGURE**

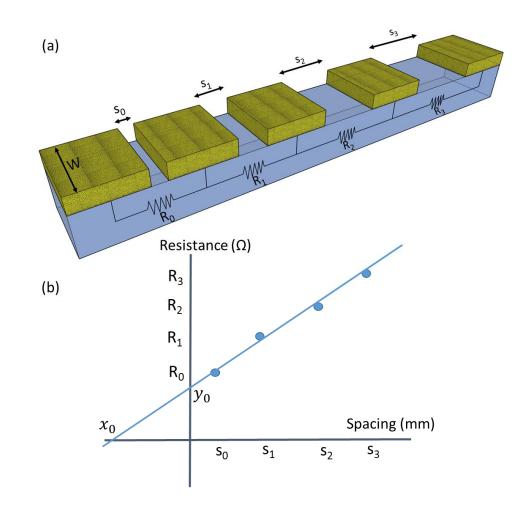

| 1.  | Figure 1. (a) Cross-sectional schematic of TLM rectangular patterns with different spacing and their respective resistances and (b) modeling resistance vs spacing to extract contact resistance             | 7  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

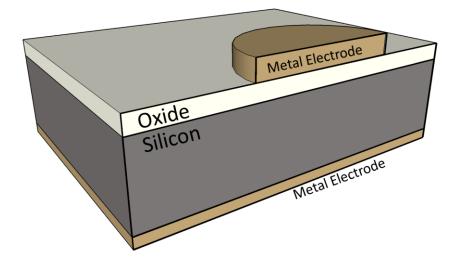

| 2.  | Figure 2 Cross-sectional schematic of a vertical Metal-Oxide-<br>Semiconductor (MOS) capacitor structure typically fabricated for Si-based devices.                                                          | 18 |

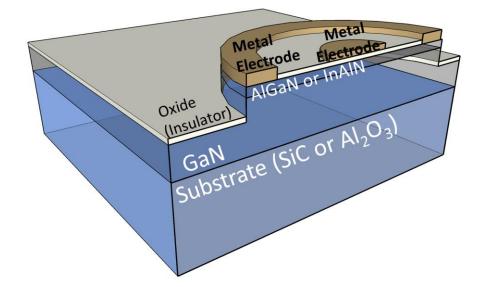

| 3.  | Figure 3 Cross-sectional schematic of a lateral Metal-Oxide (or Insulator)-<br>Semiconductor Heterostructure (MOSH or MISH) capacitor structure<br>typically fabricated for GaN-based devices                | 18 |

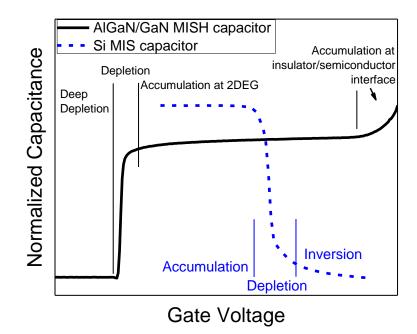

| 4.  | Figure 4 Comparison of a 100 kHz capacitance-voltage sweep of a HfO <sub>2</sub> /AlGaN/GaN MISH-capacitor (black curve) with a HfO <sub>2</sub> /Si MIS-capacitor (blue curve).                             | 20 |

| 5.  | Figure 5 Interface trap density activation energy distribution profile within AlGaN bandgap revealed using temperature-varied conductance method                                                             | 23 |

| 6.  | Figure 6 Optimizing the Ti:Al ratio and thicknesses. All samples were<br>annealed under the same conditions and the best measured contact<br>resistances are shown                                           | 34 |

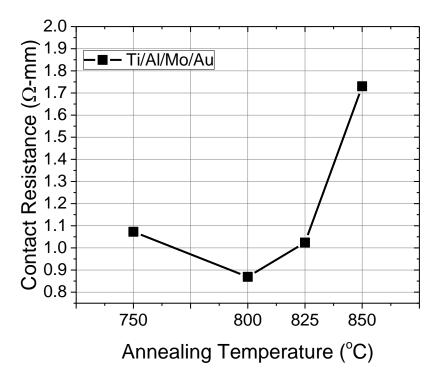

| 7.  | Figure 7 Optimizing the annealing temperature for the Ti/Al/Mo/Au ohmic contact scheme. Annealing temperature was varied while time and ambient were held constant for 30 s in N <sub>2</sub> , respectively | 35 |

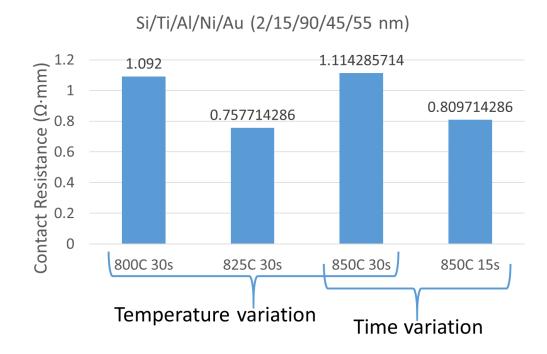

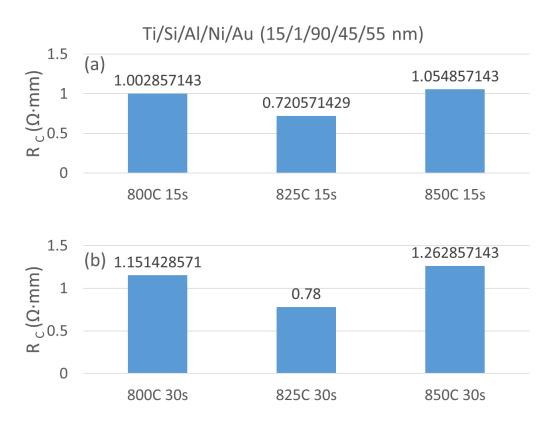

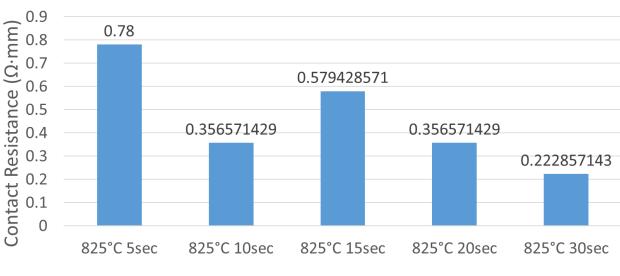

| 8.  | Figure 8 Optimizing the Si/Ti/Al/Ni/Au (2/15/90/45/55 nm) ohmic contact annealing conditions on AlGaN/GaN.                                                                                                   | 37 |

| 9.  | Figure 9 Optimizing the Ti/Si/Al/Ni/Au (15/2/90/45/55 nm) ohmic contact annealing conditions on AlGaN/GaN.                                                                                                   | 38 |

| 10. | Figure 10 Optimizing the Si/Ti/Al/Ni/Au (2/15/90/45/55 nm) ohmic contact annealing conditions on AlGaN/GaN                                                                                                   | 39 |

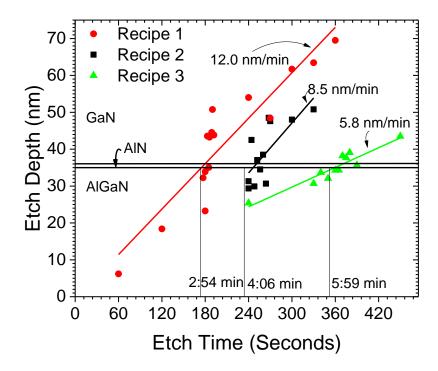

| 11. | Figure 11 ICP-RIE etch profiles for removal of AlGaN barrier layer in recessed-ohmic technology.                                                                                                             | 42 |

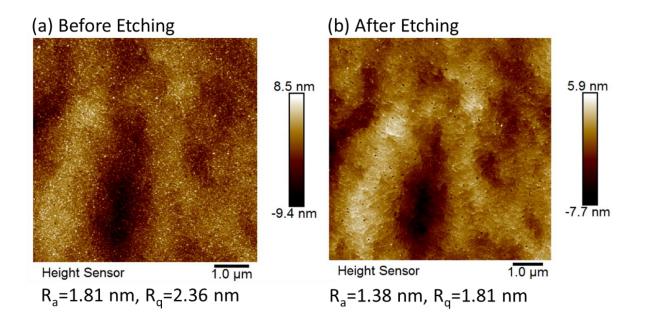

| 12. | Figure 12 Surface roughness comparison before and after the ohmic-recess etching using Recipe #3.                                                                                                            | 43 |

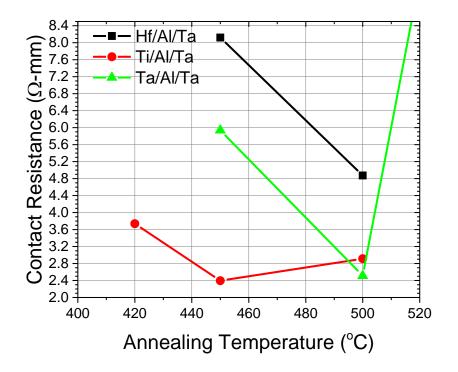

| 13. | Figure 13 Annealing temperature optimization for gold-free recessed ohmic contacts on AlGaN/GaN substrates.                                                                                                  | 45 |

| <u>FIGURE</u> |                                                                                                                                                                                                                                                                                                                                                     | <u>PAGE</u> |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

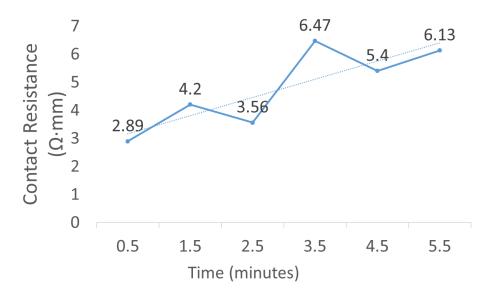

| 14.           | Figure 14 Ti/Al/Ta (15/90/20 nm) gold-free contacts with recessed ohmic annealing time optimization. Annealing temperature was held constant at 450° C using a vacuum/forming gas ambient                                                                                                                                                           | 47          |

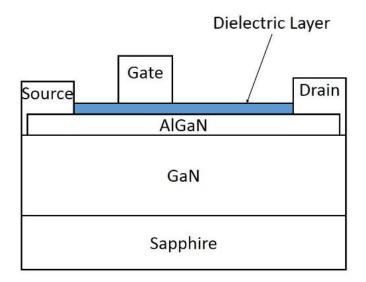

| 15.           | Figure 15 Schematic cross-sectional view of MISFET structure.                                                                                                                                                                                                                                                                                       | 53          |

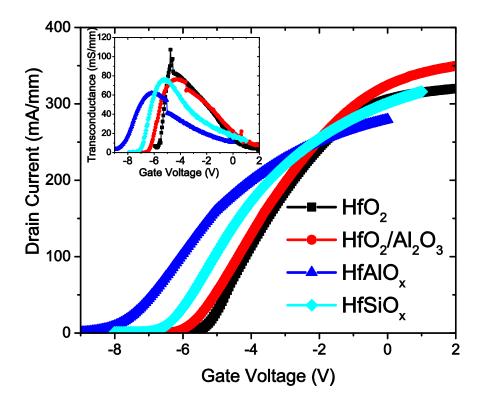

| 16.           | Figure 16 Drain current, $I_d$ , vs. gate voltage, $V_g$ , of each of the samples.<br>The inset shows transconductance. Drain bias was held at 5 V during the measurement while gate voltage was swept.                                                                                                                                             | 54          |

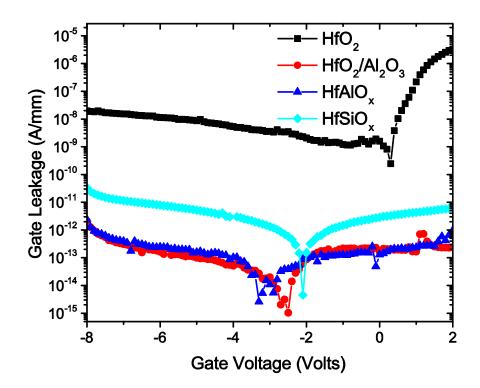

| 17.           | Figure 17 Gate leakage of each of the samples. $HfAlO_x$ and $HfO_2/Al_2O_3$ show ultra-low leakage levels, followed by the $HfSiO_x$ sample, while $HfO_2$ showed the worst leakage current                                                                                                                                                        | 55          |

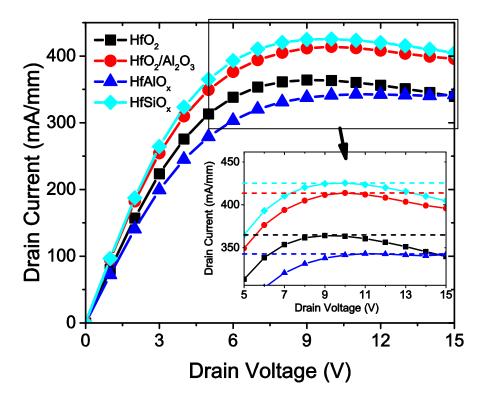

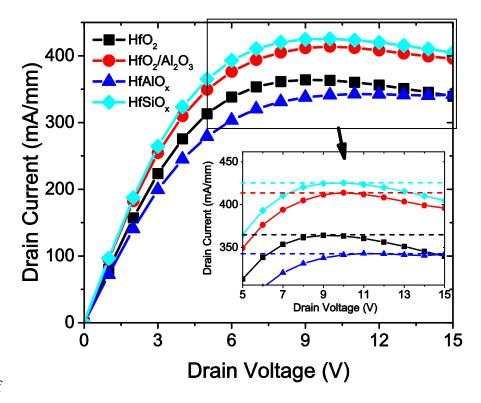

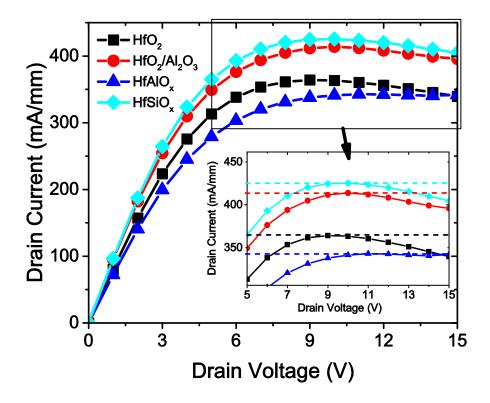

| 18.           | Figure 18 DC drain current vs. drain voltage for HfO <sub>2</sub> , HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> , HfAlO <sub>x</sub> , and HfSiO <sub>x</sub> . Only $V_g = 6$ V is plotted here for clarity. The inset shows a zoomed in portion of the curves beyond $V_d = 5$ V                                                             | 58          |

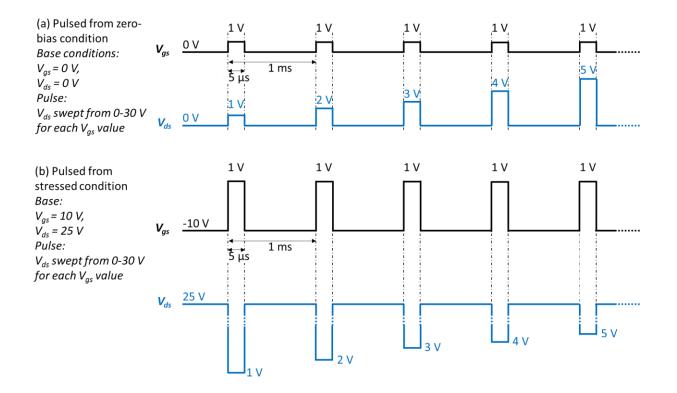

| 19.           | Figure 19 Pulsed I-V timing setup for MISHFETs                                                                                                                                                                                                                                                                                                      | 59          |

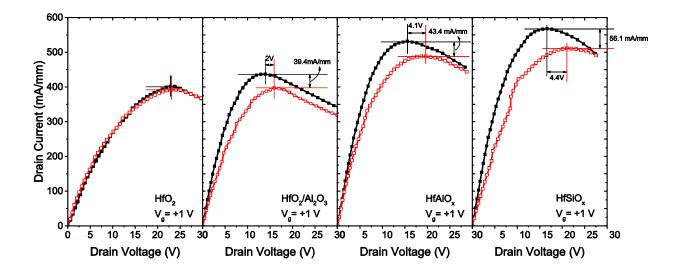

| 20.           | Figure 20 Pulse measurements of drain current vs. drain voltage for $HfO_2$ , $HfO_2/Al_2O_3$ , $HfAlO_x$ , and $HfSiO_x$ (left to right). Only $V_g = 1$ V is plotted here for clarity. Black solid figured curves are pulsed from a zero-bias condition and the red hollow figured curves are pulsed from a stressed condition.                   | 60          |

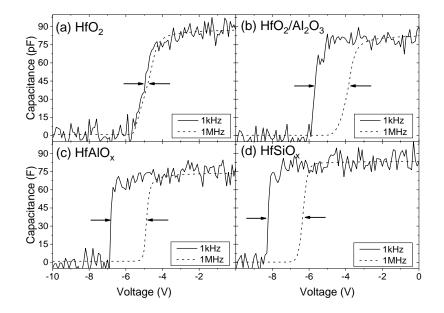

| 21.           | Figure 21 High frequency (1MHz, dashed line) and low frequency (1kHz, solid line) C-V curves of (a) $HfO_2$ , (b) $HfO_2/Al_2O_3$ , (c) $HfAlO_x$ and (d) $HfSiO_x$ . Voltage was swept from -10 V to 0 V and was measured in the dark.                                                                                                             | 61          |

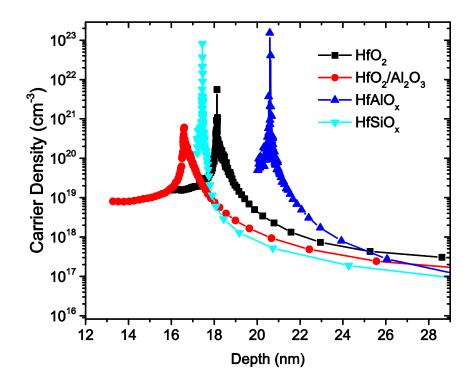

| 22.           | Figure 22 Carrier density, $N_{C-V}$ , as a function of depth. HfAlO <sub>x</sub> and HfSiO <sub>x</sub> show the largest carrier density between all the samples                                                                                                                                                                                   | 63          |

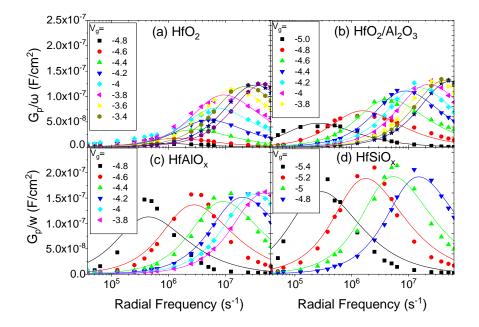

| 23.           | Figure 23 Conductance, $G_p/\omega$ , as a function of radial frequency for (a) HfO <sub>2</sub> , (b) HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> , (c) HfAlO <sub>x</sub> and (d) HfSiO <sub>x</sub> samples. Solid shapes are the measured results and the lines are the fitted curves from which D <sub>it</sub> and $\tau$ are extracted. | 64          |

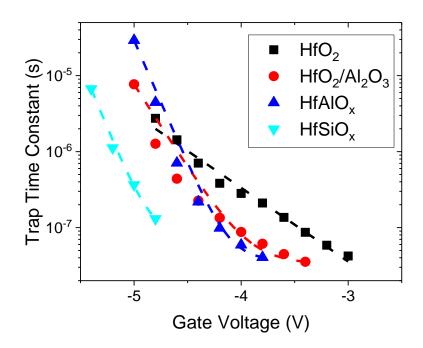

| 24.           | Figure 24 Trap time constants as a function of applied gate voltage. HfO <sub>2</sub> sample shows exponential dependence on gate voltage but the other samples show a deviation from this dependence                                                                                                                                               | 66          |

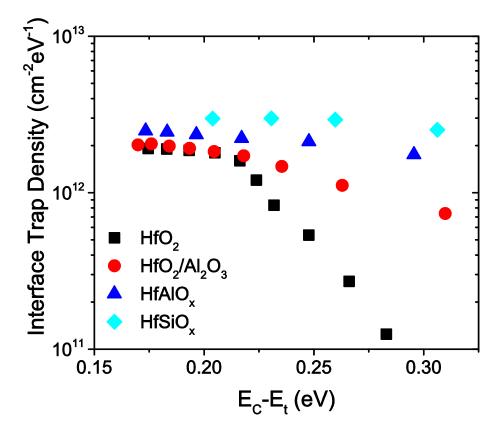

| 25.           | Figure 25 Interface Trap density as a function of activation energy                                                                                                                                                                                                                                                                                 | 67          |

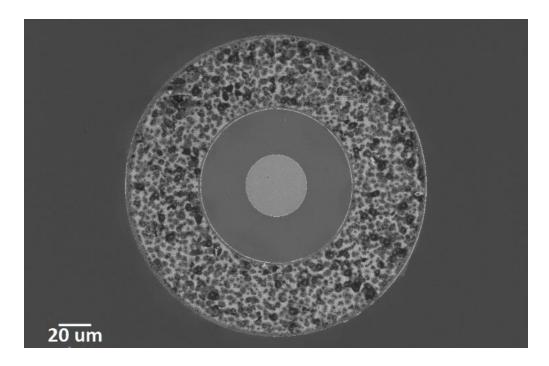

| 26.           | Figure 26 SEM image of the fabricated circular MISH capacitor                                                                                                                                                                                                                                                                                       | 73          |

# <u>FIGURE</u>

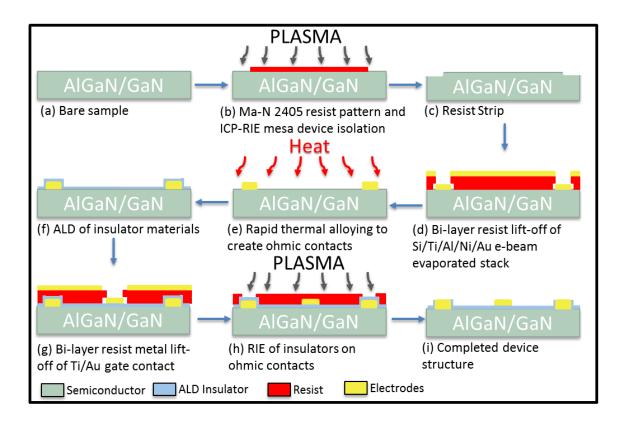

| 27. | Figure 27 Schematic cross-section of MISH capacitor fabrication steps. (a)<br>AlGaN(InAlN)/GaN starting epi-wafer. (b) Mesa device isolation is<br>achieved by ICP-RIE using a Cl <sub>2</sub> -based plasma. (c) Resist is stripped from<br>the surface. (d) Lift-off of ohmic metals deposited by E-Beam<br>evaporation. (e) Rapid thermal annealing at 825° C for 30 s in N <sub>2</sub> ambient<br>to create ohmic contact. (f) ALD of ternary insulator materials. (g) Lift-off<br>of gate electrode. (h) RIE of ALD film over ohmic metals. (i) Completed<br>device |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

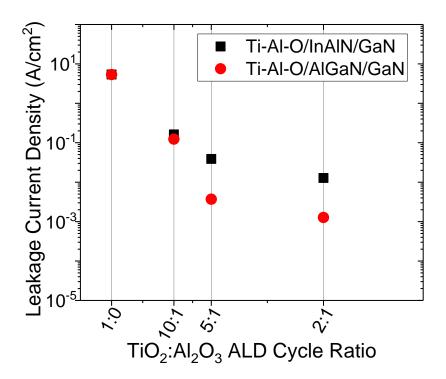

| 28. | Figure 28 Leakage current density of the ALD grown Ti-Al-O on<br>InAlN/GaN and AlGaN/GaN as a function of TiO2:Al2O3 ALD cycle<br>ratio measured at a gate bias of -1V                                                                                                                                                                                                                                                                                                                                                                                                    |

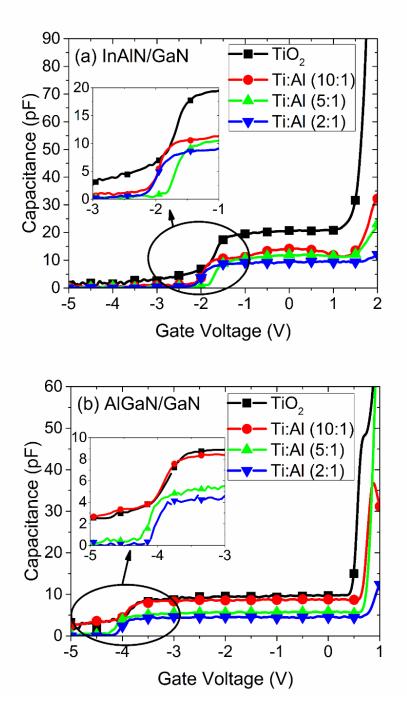

| 29. | Figure 29 (a) C-V sweep from +2 to -5 V for the dielectrics measured on InAlN/GaN. (b) C-V sweep from +1 to -5 V for the dielectrics measured on AlGaN/GaN. Both are measured using an AC signal with 10 kHz frequency, 10 mV amplitude and .05 V step size. The insets show a closer view of the depletion region sweeps                                                                                                                                                                                                                                                 |

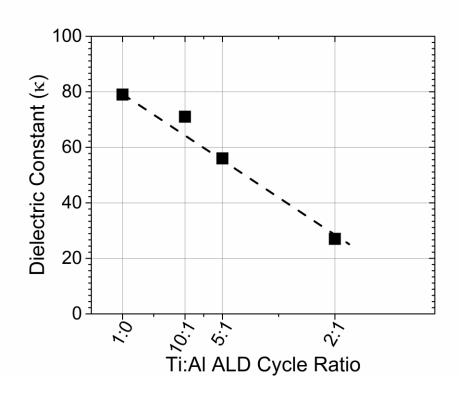

| 30. | Figure 30 Calculated dielectric constants of the Ti-Al-O films as a function of TiO <sub>2</sub> :Al <sub>2</sub> O <sub>3</sub> ALD cycle ratio. Dielectric constant of the TiO <sub>2</sub> is 79 while even at a (2:1) ratio, dielectric constant is maintained at a relatively high value of 27                                                                                                                                                                                                                                                                       |

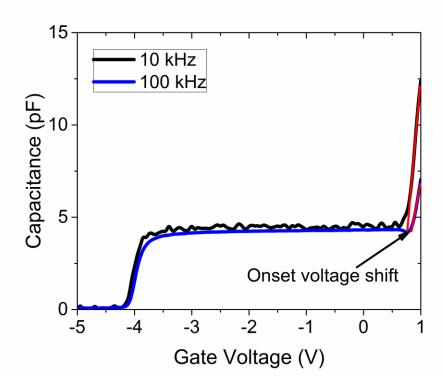

| 31. | Figure 31 C-V sweep of TiO <sub>2</sub> :Al <sub>2</sub> O <sub>3</sub> (2:1) sample measured from<br>AlGaN/GaN MISH capacitor. Based on the onset voltage shift measured<br>from different frequencies in the 2 <sup>nd</sup> slope, trap density values are<br>extracted. Similar plots are measured for InAlN/GaN capacitors but only<br>this plot is shown for clarity                                                                                                                                                                                                |

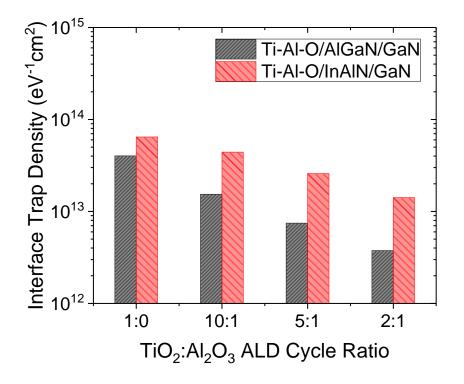

| 32. | Figure 32 Interface Trap Density measured from the various MISH capacitor structures. The Ti-Al-O dielectric films on InAlN/GaN appear to have larger interface trap density values compared to their AlGaN/GaN counterparts. Trap densities decrease and show improvement with decreasing TiO <sub>2</sub> :Al <sub>2</sub> O <sub>3</sub> ratio                                                                                                                                                                                                                         |

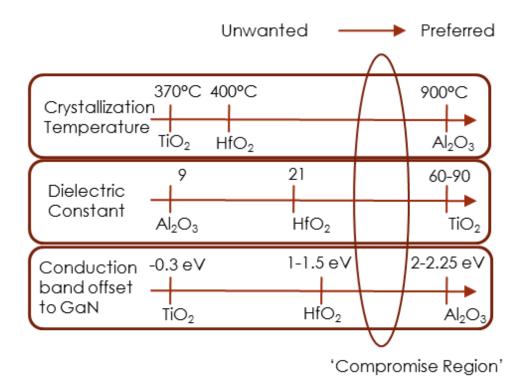

| 33. | Figure 33 Diagram representing some properties of commonly used dielectrics TiO <sub>2</sub> , HfO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> . Desired insulator properties include high crystallization temperature, large dielectric constant, and large conduction band offset to the semiconductor. Mixing TiO <sub>2</sub> with Al <sub>2</sub> O <sub>3</sub> or HfO <sub>2</sub> creates ternary compounds Ti-Al-O or Ti-Hf-O, which may provide adequate tradeoffs in these respective properties under the 'Compromise Region'                             |

| <u>FIGURE</u> | PAGE                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

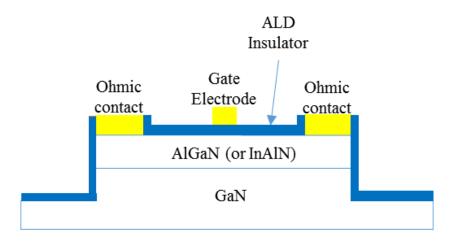

| 34.           | Figure 34 Cross-sectional schematic of AlGaN(InAlN)/GaN MISH-<br>Structure                                                                                                                                                                                                                                                                                                       |

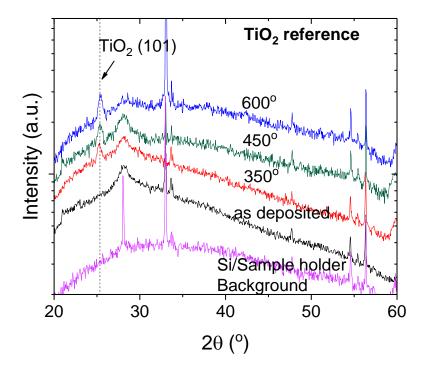

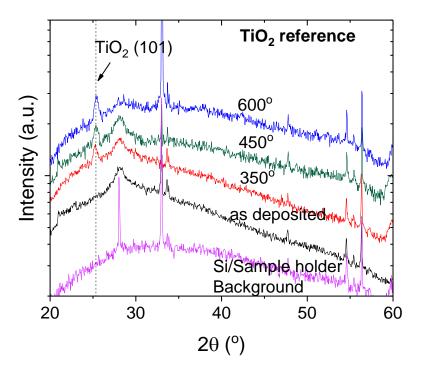

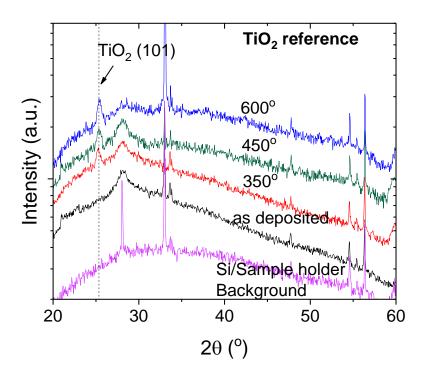

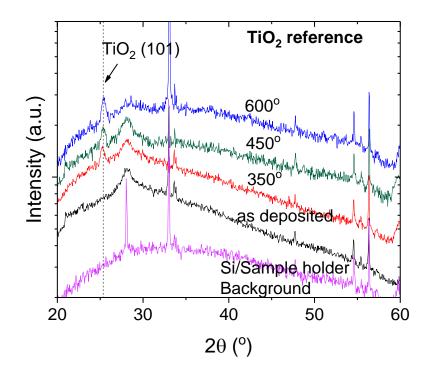

| 35.           | Figure 35 XRD spectra of the $TiO_2$ reference sample. The bottom<br>spectrum is a background scan from Silicon substrate and sample holder.<br>Thereafter spectra correspond to as-deposited, annealed at 350° C,<br>annealed at 450° C, and annealed at 600° C films                                                                                                           |

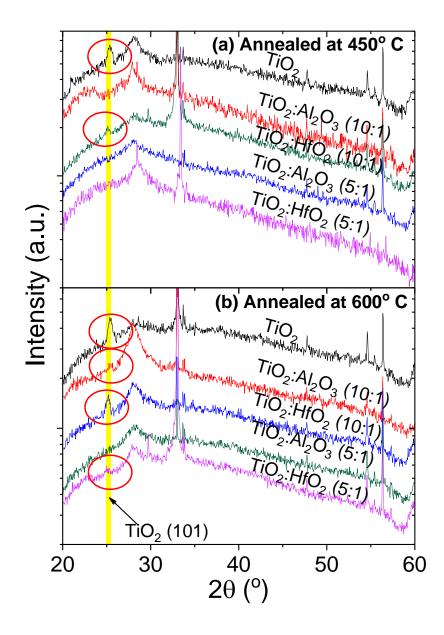

| 36.           | Figure 36 XRD spectra of post-deposition annealed films. (a) After annealing at 450° C. (b) After annealing at 600° C                                                                                                                                                                                                                                                            |

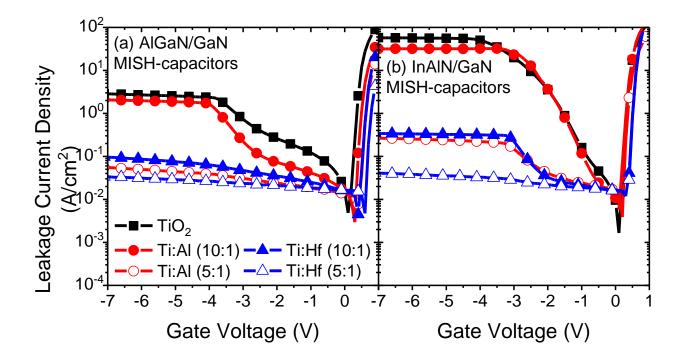

| 37.           | Figure 37 Leakage current density of the ALD grown TiO <sub>2</sub> (black curves),<br>Ti-Al-O (red curves) and Ti-Hf-O (blue curves) on (a) AlGaN/GaN and<br>(b) InAlN/GaN as a function of gate voltage                                                                                                                                                                        |

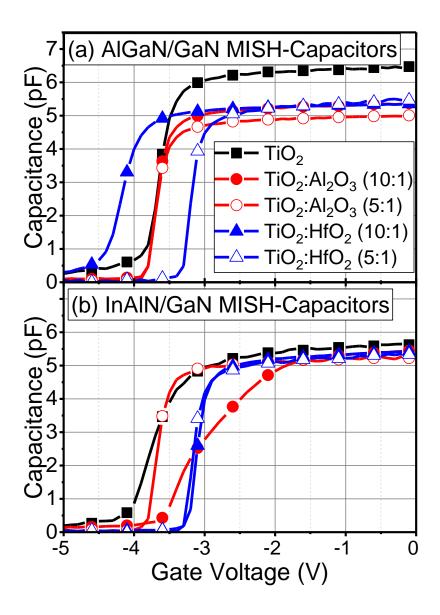

| 38.           | Figure 38 C-V sweeps from 0 V to -5 V for the dielectrics measured on (a) AlGaN/GaN and (b) InAlN/GaN MISH capacitors. Measured using an AC signal with 1 MHz frequency, 10 mV amplitude and .05 V step size 100                                                                                                                                                                 |

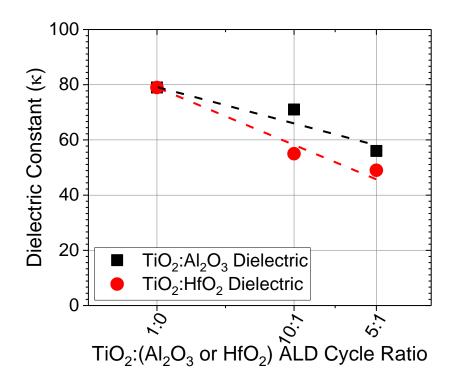

| 39.           | Figure 39 Calculated dielectric constants of the Ti-Al-O and Ti-Hf-O films<br>as a function of TiO <sub>2</sub> :Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> ALD cycle ratio. The dielectric<br>constants are maintained at a relatively high value of 56 for TiO <sub>2</sub> :Al <sub>2</sub> O <sub>3</sub><br>(5:1) and 49 for TiO <sub>2</sub> :HfO <sub>2</sub> (5:1) |

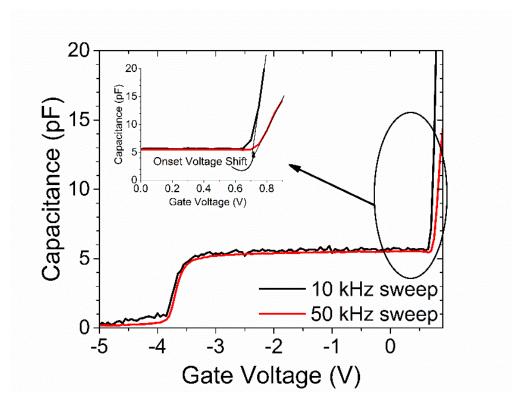

| 40.           | Figure 40 Full C-V sweep of TiO <sub>2</sub> :HfO <sub>2</sub> (5:1)/AlGaN/GaN MISH capacitor. The inset shows further detail on the 2 <sup>nd</sup> slope's onset voltage shifts. Similar curves are measured for the rest of the MISH capacitors but are not shown                                                                                                             |

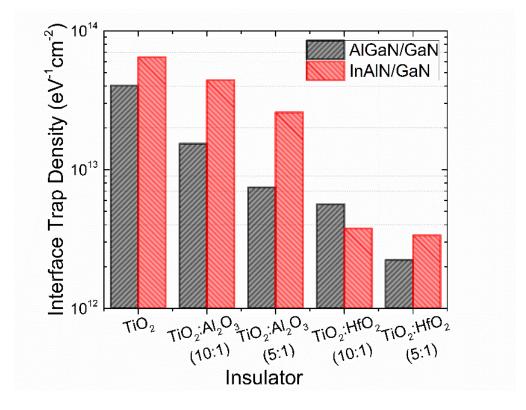

| 41.           | Figure 41 Interface Trap Density measured from the various MISH capacitor structures through frequency-dependent C-V sweeps                                                                                                                                                                                                                                                      |

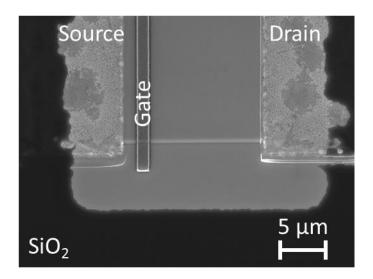

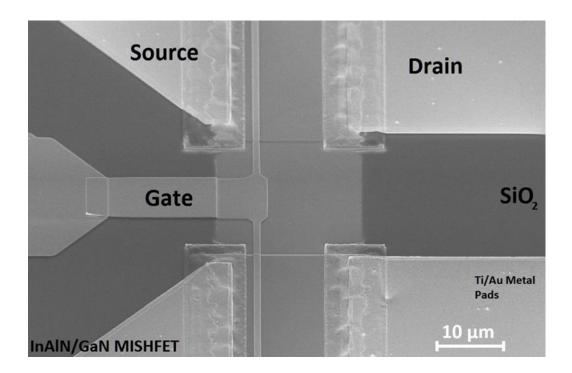

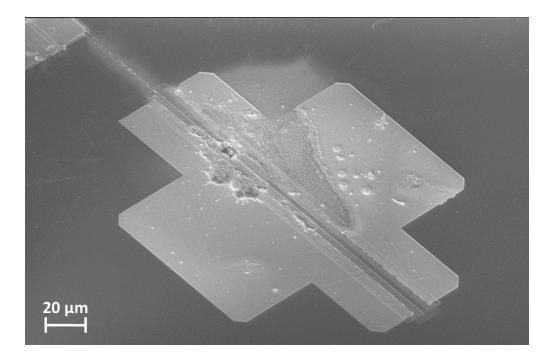

| 42.           | Figure 42 SEM image of InAlN/GaN MISHFET half-way through the fabrication process (i.e. post field oxide etching)                                                                                                                                                                                                                                                                |

| 43.           | Figure 43 SEM image of completed 2-finger gated InAlN/GaN MISHFET 109                                                                                                                                                                                                                                                                                                            |

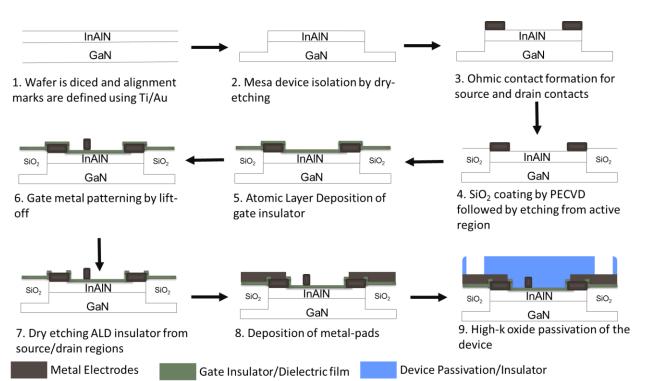

| 44.           | Figure 44 Cross-sectional schematic showing InAlN/GaN transistor device fabrication process                                                                                                                                                                                                                                                                                      |

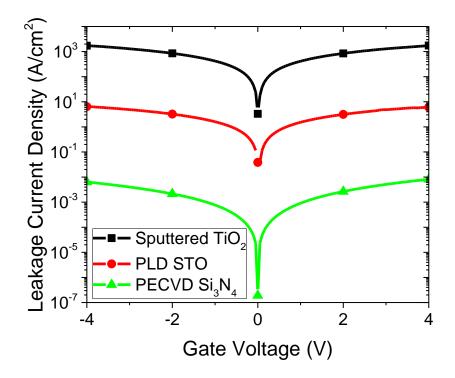

| 45.           | Figure 45 Leakage current density of select dielectric films which are candidates for transistor passivation materials                                                                                                                                                                                                                                                           |

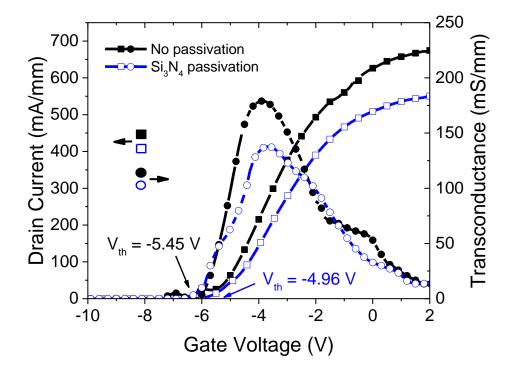

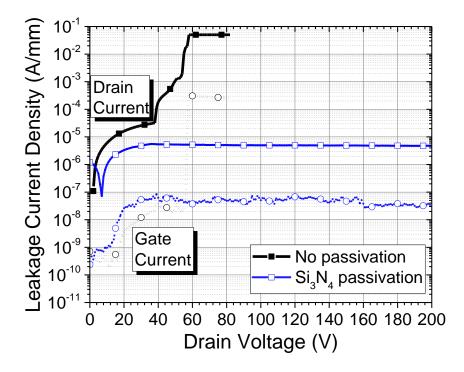

| 46.           | Figure 46 Transfer curves of InAlN/GaN transistors with (hollow-blue symbols) and without (solid-black symbols) the $Si_3N_4$ passivation                                                                                                                                                                                                                                        |

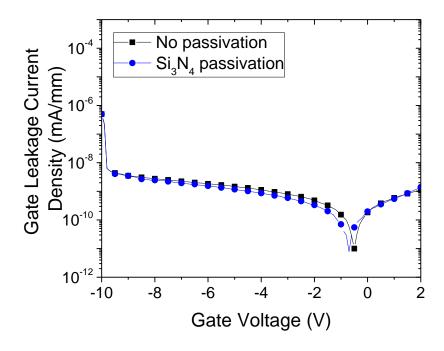

| 47.           | Figure 47 Gate leakage current density for InAlN/GaN transistors with and without $Si_3N_4$ passivation                                                                                                                                                                                                                                                                          |

| <u>FIGURE</u> | PAGE                                                                                                                                                                                                                                                                         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

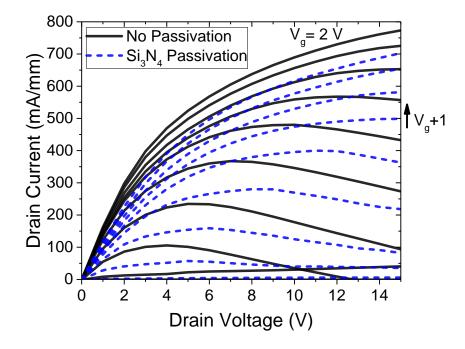

| 48.           | Figure 48 'Family of Curves' $(I_d-V_d)$ measured using gate voltage bias<br>starting from $V_g = -6$ V incrementing $+1$ V up to $V_g = 2$ V. Comparing<br>transistors with (dashed blue line) and without (solid black line) Si <sub>3</sub> N <sub>4</sub><br>passivation |

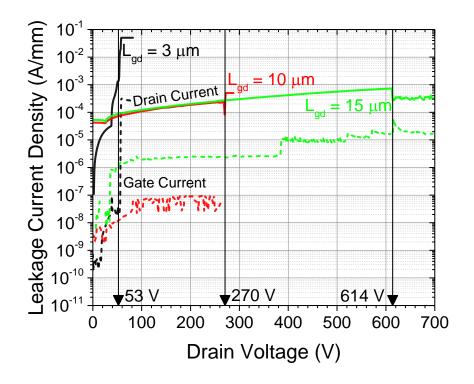

| 49.           | Figure 49 Breakdown voltage scaling with gate-to-drain spacing of<br>InAlN/GaN MISHFETs without a capping/passivating dielectric layer                                                                                                                                       |

| 50.           | Figure 50 SEM image of InAlN/GaN MISHFET after device destruction during breakdown measurements                                                                                                                                                                              |

| 51.           | Figure 51 Effects of passivation/capping an InAlN/GaN MISHFET on off-<br>state breakdown voltage                                                                                                                                                                             |

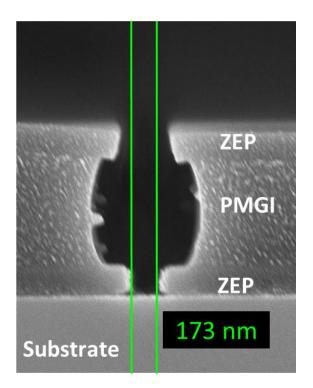

| 52.           | Figure 52 Electron beam lithography tri-layer resist stack after development for T-Gate definition                                                                                                                                                                           |

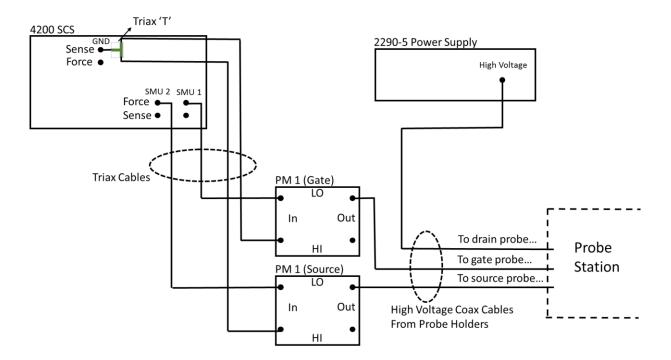

| 53.           | Figure 53 Instrument setup for 3-terminal high-voltage breakdown FET measurements                                                                                                                                                                                            |

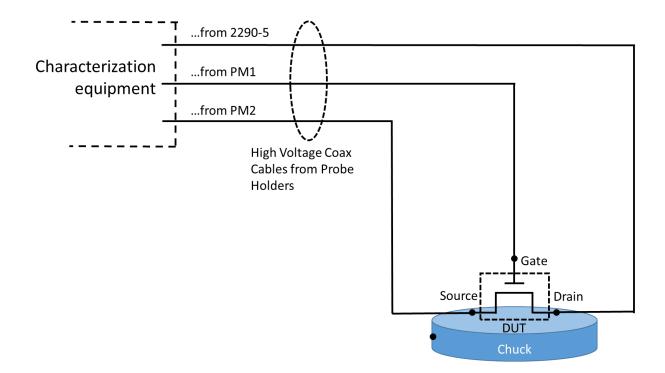

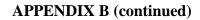

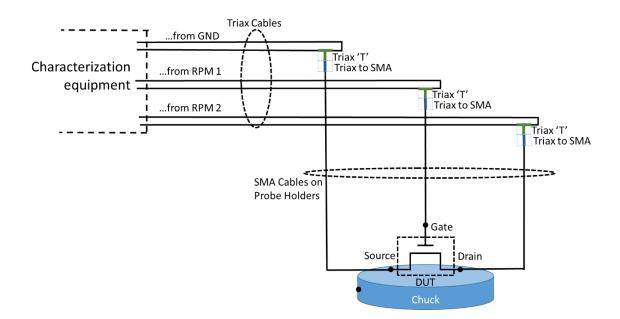

| 54.           | Figure 54 Probe station setup for 3-terminal high-voltage breakdown FET measurements                                                                                                                                                                                         |

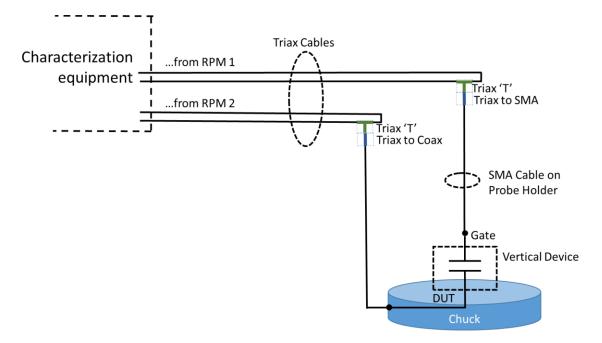

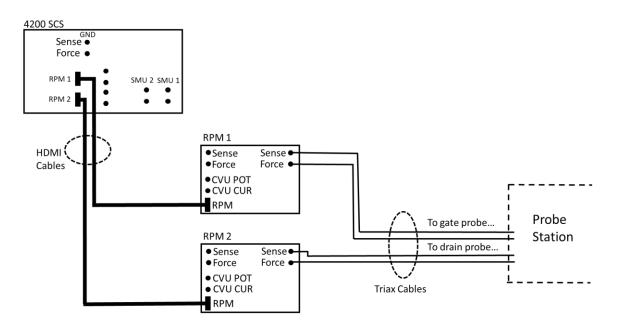

| 55.           | Figure 55 Instrument setup for 3-terminal FET measurements                                                                                                                                                                                                                   |

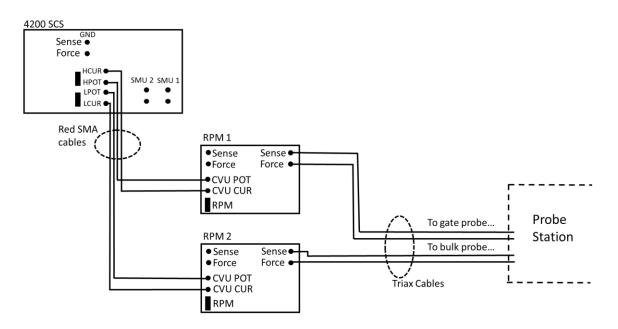

| 56.           | Figure 56 Probe station setup for 3-terminal FET measurements                                                                                                                                                                                                                |

| 57.           | Figure 57 Instrument setup for capacitance-voltage measurements                                                                                                                                                                                                              |

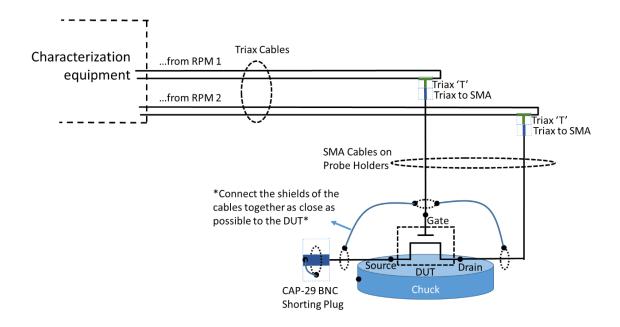

| 58.           | Figure 58 Probe station setup for lateral capacitors measurement                                                                                                                                                                                                             |

| 59.           | Figure 59 Probe station setup for vertical capacitors measurement                                                                                                                                                                                                            |

| 60.           | Figure 60 Instrument setup for pulsed I-V measurements                                                                                                                                                                                                                       |

| 61.           | Figure 61 Probe station setup for pulsed I-V measurements                                                                                                                                                                                                                    |

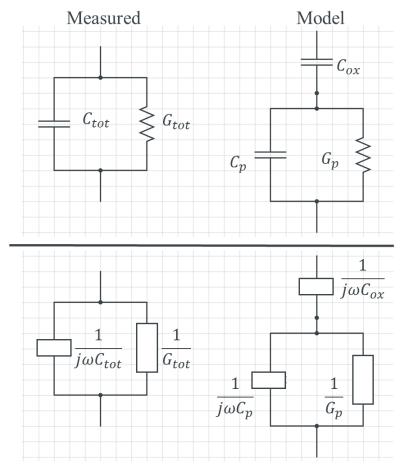

| 62.           | Figure 62 Conductance method model for trap density extraction                                                                                                                                                                                                               |

## LIST OF ABBREVIATIONS

| AC      | Alternating Current                                                  |

|---------|----------------------------------------------------------------------|

| AFM     | Atomic Force Microscopy                                              |

| ALD     | Atomic Layer Deposition                                              |

| BOE     | Buffered Oxide Etch                                                  |

| CV      | Capacitance-Voltage                                                  |

| DC      | Direct Current                                                       |

| EBL     | Electron Beam Lithography                                            |

| FET     | Field Effect Transistor                                              |

| HEMT    | High Electron Mobility Transistor                                    |

| HV      | High Voltage                                                         |

| ICP-RIE | Inductively Coupled Reactive Ion Etching                             |

| MBE     | Molecular Beam Epitaxy                                               |

| MIS     | Metal Insulator Semiconductor                                        |

| MISHCAP | Metal Insulator Semiconductor Heterojunction Capacitor               |

| MISHFET | Metal Insulator Semiconductor Heterojunction Field Effect Transistor |

| MOCVD   | Metal Organic Chemical Vapor Deposition                              |

| MOS     | Metal Oxide Semiconductor                                            |

| PDA     | Post Deposition Anneal                                               |

| PECVD   | Plasma Enhanced Chemical Vapor Deposition                            |

| PM      | Protection Module                                                    |

| PR      | Photo Resist                                                         |

| PVD     | Physical Vapor Deposition                                            |

| RF      | Radio Frequency                                                      |

| RIE     | Reactive Ion Etching                                                 |

| RPM     | Remote Pulse Unit                                                    |

| RTA     | Rapid Thermal Anneal                                                 |

| RTP     | Rapid Thermal Processing                                             |

| SCS     | Semiconductor Characterization System                                |

| SEM     | Scanning Electron Microscopy                                         |

| SMU     | Source Measure Unit                                                  |

| XPS     | X-ray Photoelectron Spectroscopy                                     |

| XRD     | X-Ray Diffraction                                                    |

| XRR     | X-Ray Reflectance                                                    |

#### SUMMARY

Gallium Nitride, a viable candidate to advance current technology in high-voltage and high frequency transistors, has seen a boom in research advancements within the last couple of decades. However, compared to Si-based transistors, fabrication processing technology is still in its infancy. Key areas in the metal insulator semiconductor heterojunction field effect transistors (MISHFET) are still inhibiting demonstration of GaN's theoretical limits in terms of transistor performance. In this dissertation, I tackle several topics concerning the MISHFET structure to improve transistor electrical performance.

Through fabrication and testing of design-conscious GaN-based devices, I study various aspects in the MISHFET structure. I begin by optimizing the metal-semiconductor contact, rather the ohmic contact. Realizing a low-contact resistance process is delicately dependent a wide array of processing conditions. I delve into various promising techniques such as recessed-contacts, gold-free processing and metal thicknesses dependency. Moreover, contacts on both AlGaN/GaN and InAlN/GaN were studied. The lowest contact resistance achieved here showed a minimum contact resistance of 0.14  $\Omega$ ·mm and 0.17  $\Omega$ ·mm on AlGaN/GaN and InAlN/GaN substrates, respectively.

Next, I study various high- $\kappa$  insulators in the metal-insulator-semiconductor structure. The insulator's quality may be a severe bottleneck for transistors. Criteria such as excess leakage current and high interfacial defect densities can seriously degrade device performance in both RF operation and breakdown voltage. Thus, I investigate several insulators on GaN and correlate device performance metrics with insulator qualities. By tuning the elemental composition of the insulators, we can control and improve several key factors concerning insulating materials. Overall, I found that HfO<sub>2</sub>-based insulators provide lowest insulator/semiconductor interface

## **SUMMARY** (continued)

defects within the insulators studied here, however, these films are generally electrically leaky. By creating ternary insulators such as  $HfAlO_x$ , an AlGaN/GaN transistor demonstrated ultra-low leakage on the order of  $10^{-12}$  A/mm.

Lastly, a technique to improve off-state breakdown voltage of an InAlN/GaN transistor was also briefly experimentally verified. By capping the transistor with an insulator with defined qualities, breakdown voltage was improved by more than 400 % of a normally-on InAlN/GaN transistor, compared to the un-passivated device.

## 1. INTRODUCTION

## 1.1. Overview of GaN-Technology

During the mid-20th century investigation of solid-state electronics, many semiconducting materials were under intense research to use for the promising newly discovered transistor at Bell Laboratories[1]. However, due abundancy of Silicon and the ability to grow a high-quality oxide (SiO<sub>2</sub>), Silicon led the transistor revolution into the 21<sup>st</sup> century. Silicon, however, is reaching its theoretical limitations in terms of speed, power density and applications. III-V semiconductors have been researched since the discovery of GaAs in the early 1950s but have been severely limited due to poor material synthesis techniques. Within the recent decades with the developments of Metal Organic Chemical Vapor Deposition (MOCVD) and Molecular Beam Epitaxy (MBE), the quality of compound semiconductors has drastically improved and thus is becoming a serious candidate to replace Silicon technology.

Gallium Nitride (GaN) is a wide and direct bandgap semiconductor. Moreover, nitrides exhibit strong spontaneous and piezoelectric polarization charges, thus, by growing a stress-inducing 'doped' barrier layer on GaN, a high concentration of electrons (sheet charges) are accumulated at the GaN surface. The high density of electrons at the GaN surface are referred to as the 2-Dimensional Electron Gas (2DEG). The 2DEG, thereby, can be used as a highly conducting channel that may be manipulated by external electric fields. The heterojunction such as described is not the first time the world has seen it. AlGaAs/GaAs HEMT transistors operate under similar principles. However, the GaAs system relies on piezoelectric polarization only to induce a 2DEG while GaN systems have the additional spontaneous charges. Moreover, GaN's wide bandgap (3.4 eV) properties allow for more robust applications which require high-power.

One of the major demands in highly efficient solid state electronics include 'clean' energy Electric Vehicles (EV). The large power handling requirements EV's exhibit require semiconductors with wide bandgaps such as SiC or GaN [2]. SiC is currently dominating the market mainly due to the ability to grow larger single crystal wafers, however, GaN having a slightly larger critical field breakdown and much higher electron mobility is surely a serious contender. Besides high power applications, the ability to form a high-mobility 2DEG with GaN heterojunctions makes it an attractive material for fast switching applications such as power amplifiers in Long Term Evolution (LTE) wireless communication networks [3]. Furthermore, the advantageous wide bandgap nature creates electronics that can be used outer space where background radiation easily damages Si-based electronics [4]. Lastly, GaN enabled the invention of the blue LED which was awarded the 2014 Nobel Prize in Physics [5]. Nonetheless, there are countless applications for GaN-material where it excels performance making it a highly robust and serious contender to replace Si-technology.

So you may ask yourself, 'Since GaN seems like such a great material, why hasn't it dominated the market yet?'. Well, GaN does not come without its' caveats. From the synthesis of GaN single-crystal wafers, the process becomes extremely costly. To date, a 2" single-crystal GaN wafer costs \$2,500 while it's possible to purchase a 4" Si-wafer for a mere \$15. Ohmic contact formation is a very complex process as well. Typical ohmic contacts require a multi-layered metal stack of Ti/Al/Ni/Au followed by a high temperature alloying to induce ohmic behavior. There are several problems with the current process. 1. The complexity of the metal stacks in terms of relative thicknesses may be cumbersome. 2. For GaN to be accepted in current Si-fabrication facilities, gold must not be present. 3. Any high temperature processing should be avoided to minimize processing complexity and prevent any damage to high-temperature sensitive

structures. and 4. Contact resistance should be as minimal as possible. In essence, there is much research necessary on the ohmic contacts formation for GaN. Typical GaN transistors are normally-on devices, meaning a negative gate voltage must be applied to 'turn off' the device. To reduce electrical circuits configuration complexities, transistors in the normally-off regime would be preferred. Unlike the high-quality oxide found in SiO<sub>2</sub>/Si systems, GaN does not have the same advantages. Typically, high defect densities are found for insulators on GaN. Lastly, current GaN-based devices are far from reaching theoretical breakdown voltage performance. In summary, there is much work required to further improve and mature GaN processing for it to dominate the semiconductor markets.

In this dissertation, I tackle most of these issues through several experiments except for GaN growth. While I mostly focused on insulators on GaN during my graduate career, I will also go into detail on ohmic contacts, normally-off approaches, and high voltage performance.

## 1.2. Organization of Chapters

I have organized the chapters based on transistor fabrication hierarchy. Although all steps in a fabrication process are important, key issues involved in the process include ohmic contact formation for source/drain electrodes, gate insulation/passivation in the metal-insulatorsemiconductor structure and device passivation/encapsulation. In Chapter 2, I delve into techniques to improve metal contacts on GaN. I spent a lot of effort into optimizing the process here since 'good' metal contacts are of utmost importance for optimal transistor performance. Chapters 3, 4 and 5 discusses several aspects of gate insulators. I discuss several important parameters concerning dielectrics such as temperature stability, band offsets, interface trapped charge, etc. Lastly, Chapter 6 discusses a technique studied by Chenjie Tang, and shown experimentally here, to improve 3-terminal off-state breakdown voltage of a type of GaN transistor. Each chapter discussed here stands on its' own and may be read separately from the rest.

## 1.3. Introduction to Ohmic Contacts

Ohmic contacts on compound semiconductors such as GaAs or GaN require a complex process to induce ohmic behavior. Metal-semiconductor junctions may act one of two ways. The first is rectifying, which is when the contact exhibits diode-like current conduction, namely schottky contact. The other is non-rectifying, or ohmic, when the junction can conduct current in forward or reverse directions. Typical ohmic contacts on GaN requires a process as follows. 1. Multi-layered metal stack deposition of Titanium, Aluminum, Molybdenum (or Nickel), and Gold. 2. High temperature rapid thermal annealing between 800° to 860° for 30 seconds in Nitrogen gas ambient. The purpose of the first two metals, Ti and Al, are required to form successful contact to the semiconductor. When depositing these metals, it is important to choose the optimal respective thicknesses and ratio of thickness. The 3<sup>rd</sup> metal, either Mo or Ni, is used as a diffusion barrier layer between Au and Al. It is believed that during the high temperature processing, these two material intermix to form Al-Au 'blobs' causing the rough surface morphology seen on ohmic contacts. The 4th metal, typically a noble metal such as Au, is used for electrical contact either by probes or wire bonding. After deposition of the metals, a high temperature rapid thermal annealing is required to induce ohmic behavior. This is an utmost critical process dependent on temperature, time and ambient gas. Typical processing requires at least 800° C for 15-30 seconds in nitrogen gas ambient.

Low ohmic contact resistance is desired to reduce power consumption. Furthermore, large contact resistances degrade the maximum attainable current densities in transistor structures. Other desirable properties include low-temperature contact formation, gold free-technology and low roughness contacts. During the high temperature processing required for the standard stack, inevitably, the 2DEG becomes damaged in the process and thus leads to lower carrier densities

and lower carrier mobility. Moreover, when designing the process flow, one must be wary of any potential damage to the structure during exposure to high-temperature such as gate dielectrics which typically have low-temperature stabilities. Gold-free processing is desirable since no gold is allowed in Silicon fabrication facilities; gold can easily contaminate Silicon-based devices. Thus, for GaN processing to be incorporated in Silicon fabrications facilities, it can't require any gold-processing. Lastly, low-roughness contacts are desired for ultra-scaled devices. During the high temperature annealing, the metal alloying causes rough surface morphology which translates to lateral roughness. When dealing with ultra-scaled devices where source, gate and drain contacts are separated in sub-micron dimensions, the surface roughness may lead unwanted electrical shorts. Careful design and techniques are required to be able to achieve these properties with ohmic contacts.

A common technique to characterize the contact resistance is known as the Transfer Length Model (TLM) or Transmission Line Model. This requires rectangular contacts of width, W, with different spacing between each pad; s<sub>0</sub>, s<sub>1</sub>, s<sub>2</sub> and so on. The design is depicted in Figure 1. Based on a linear fitting of the measured points, it is possible to extract sheet resistance ( $R_s [\Omega/\Box]$ ), contact resistance ( $R_c [\Omega \cdot mm]$ ), and specific resistivity ( $\rho [\Omega \cdot cm^2]$ ) by extrapolating to find y-intercept (y<sub>0</sub>), x-intercept (x<sub>0</sub>) and the slope (m) and using the following equations:

$$R_{s}[\Omega/\Box] = W \times m$$

$$R_{c}[\Omega \cdot mm] = \frac{y_{0}}{2} \times m$$

$$\rho [\Omega \cdot cm^{2}] = \frac{R_{c}^{2}}{R_{s}}$$

Figure 1 (a) Cross-sectional schematic of TLM rectangular patterns with different spacing and their respective resistances and (b) modeling resistance vs spacing to extract contact resistance.

#### 1.3.1. Literature Review on ohmic contacts

There has been much progress within the research community on ohmic contacts for GaN semiconductors. However, due to the complex process required, there is much room for error and thus there is a large variation on the reported results. The typical ohmic contact stack of Ti/Al/Ni/Au yields contact resistances in the range of 0.7 to 1.0  $\Omega$ ·mm on AlGaN/GaN. There are many techniques studied to reduce the contact resistance. Processing techniques can be divided into three sections, all of which will be discussed, 1. pre-metallization 2. metal deposition and 3. post metal processing.

## 1.3.2. Ohmic Contact Pre-Metallization Processing

Pre-metallization processing includes any steps taken before metal-deposition. This includes any plasma exposures using reactive ion etching (RIE) with the aim of lowering resulting contact resistance and reducing the temperature required for ohmic behavior during annealing. SiCl<sub>4</sub> has been shown to decrease ohmic contact resistance on both InAlN [6, 7] and AlGaN [8, 9] by creating defects in the semiconductor such as nitrogen vacancies, which act as n-type carriers. For example, as reported in [7], using a low temperature anneal (600° C) for the Ti/Al/Ni/Au stack, the authors compared the contacts with and without RIE treatment which resulted in a contact resistance of 1 and 12  $\Omega$ ·mm, respectively. However, SiCl<sub>4</sub> is not a commonly used gas and so may be unavailable for use in many cleanroom facilities. Thus, there are other reported plasma chemistries used to achieve the same effect. Various reported etching properties are summarized on Table I. Most processes reported utilize a very slow etch rate or no etching in the case of [10] to create the defects necessary for successful ohmic contacts. In many of the reported cases, the authors report a contact resistance < 0.5  $\Omega$ ·mm, however, low-temperature annealing is not always achieved, or perhaps, not reported.

# Table I List of reported reactive ion etching process parameters which may be used for ohmic contact pre-metallization treatment on GaN.

| Ref  | Etching<br>Tool            | Plasma<br>Chemistry | Gas<br>Flow<br>Rates<br>(sccm) | Process<br>Pressure<br>(mTorr) | ICP/RF<br>Power<br>(or<br>Voltage) | Etch<br>Rate<br>(Å/min) | Substrate          | Metal Stack | Annealing<br>Temperature<br>(C) | Contact<br>Resistance<br>(Ω∙mm) |

|------|----------------------------|---------------------|--------------------------------|--------------------------------|------------------------------------|-------------------------|--------------------|-------------|---------------------------------|---------------------------------|

| [11] | Samco<br>200iP<br>ICP-RIE  | SiCl4               | 3                              | 1.9                            | 50/20 W                            | 12.5                    | GaN and AlGaN      | N/A         | N/A                             | N/A                             |

| [10] | Samco<br>200iP<br>ICP-RIE  | BCl3<br>SiCl4       | 5                              | 1.9                            | 100/0 W                            | 0                       | GaN(cap)/AlGaN/GaN | Ti/Al/Ni/Au | 870°                            | 0.41<br>0.17                    |

| [12] | Oxford<br>PlasmaLab<br>RIE | SiCl4               | 10                             | 25                             | 0/-300<br>V                        | N/A                     | GaN and AlGaN/GaN  | N/A         | N/A                             | N/A                             |

| [13] | N/A                        | C12                 | 10                             | 5                              | 60 W/-<br>300 V                    | 6                       | AlGaN/GaN          | Ti/Al/Ni/Au | 870°                            | 0.27                            |

| [8]  | N/A                        | SiCl4               | 10                             | 25                             | 0/-100<br>V to<br>400V             | N/A                     | AlGaN/GaN          | Ti/Al/Mo/Au | 850°                            | 0.2                             |

| [9]  | N/A                        | SiCl4               | N/A                            | N/A                            | 0/-300<br>V                        | N/A                     | AlGaN/GaN          | Mo/Al/Mo/Au | 500°                            | 0.11                            |

| [6]  | N/A                        | SiCl4               | 10                             | 25                             | 0/-300<br>V                        | N/A                     | InAlN/GaN          | Mo/Al/Mo/Au | 650°                            | 0.15                            |

| [7]  | N/A                        | SiCl4               | N/A                            | N/A                            | N/A                                | N/A                     | InAlN/GaN          | Ti/Al/Ni/Au | 600°                            | 1.0                             |

Another elaborate process some researchers have reported using involve completely etching the barrier layer followed by regrowth using molecular beam epitaxy (MBE) of highly doped GaN and finally metallization using a simple structure, such as Ti/Au, with no annealing required. Some of the reported results are listed on Table II. The etching is achieved using a SiO<sub>2</sub> or SiN<sub>x</sub> mask to completely etch the barrier layer by RIE. Afterwards, the sample is loading in a MBE system to regrow a highly-doped n-type GaN layer which is highly conductive (regrowth thickness was mentioned to be 40 nm). Next, a bilayer metal stack (e.g. Ti/Au) is deposited and patterned by the lift-off process followed by the removal of the etching mask. There is no high temperature processing required to form the ohmic contact and results in extremely low contact resistances in the range of  $0.1 \Omega$ ·mm for InAlN/GaN. However, the process is rather complex and requires the costly operation of MBE.

| Table II. Comparisons of recent ohmic contact schemes using the regrowth method for |

|-------------------------------------------------------------------------------------|

| InAlN/GaN devices and their resulting contact resistance.                           |

| Ref  | Ohmic pre-<br>metallization | Ohmic Metal Stack | Thermal Annealing<br>Temperature (°C) | Contact<br>Resistance<br>(Ω∙mm) |

|------|-----------------------------|-------------------|---------------------------------------|---------------------------------|

| [3]  | n+-GaN regrowth             | Mo/Au             | Non-alloyed                           | 0.1                             |

| [14] | n+-GaN regrowth             | Ti/Au             | Non-alloyed                           | 0.16                            |

| [15] | n+-GaN regrowth             | Ti/Au             | Non-alloyed                           | 0.16                            |

| [16] | n+-InGaN regrowth           | N/A               | N/A                                   | 0.13                            |

#### 1.3.3. Ohmic Contact Metal Deposition

After any pre-metallization processing are complete on the ohmic contact step, comes the metal deposition. Typically, metal deposition is accomplished by electron-beam evaporation which is a physical vapor deposition (PVD) process. Although sputtering is also available as an adequate deposition method, patterning of the films may prove to be difficult since the lift-off process is problematic with sputtered films and masked etching is difficult with so many layers present in the ohmic stack.

Design of respective thicknesses and ratio of the metal films are extremely important for low-contact resistance as previously mentioned. However, there are many reported metal stack variations with impressive results. For ease of discussion, I will divide the various contacts into 3 subsections with many results falling into other categories: gold free, complex structures (6 or more layers), and Si or Ge incorporation.

Gold-free contacts typically involve refractory metals (such as Ta, Hf, W) as a capping laying instead of gold. Some report successful results using the standard first two metals Ti/Al, while others report low resistance through some other variation using Ta. Some excellent reports with low contact resistances using gold-free processing is reported in Table III. As discussed previously, the contacts with plasma etching prior to metallization exhibits low temperature annealing required for ohmic behavior. Other contacts listed in the table require the typical high temperature of  $> 800^{\circ}$  C.

# Table III List of reported Gold-Free ohmic contacts on GaN semiconductors listed with their respective processing conditions and results.

| Ref         | Pre-<br>metallization<br>treatment          | Substrate          | Metal Stack       | Metal<br>Thicknesses<br>(nm) | Annealing<br>Conditions                     | Contact<br>Resistan<br>ce<br>(Ω∙mm) | Specific<br>Contact<br>Resistance<br>(Ω·cm2) |

|-------------|---------------------------------------------|--------------------|-------------------|------------------------------|---------------------------------------------|-------------------------------------|----------------------------------------------|

| [17]        | Cl <sub>2</sub> -based<br>recess            | GaN(cap)/AlGaN/GaN | Ta/Al/Ta          | N/A                          | $600^{\circ}$ C for 240s in N <sub>2</sub>  | 0.2                                 | N/A                                          |

| [18]        | None                                        | GaN(cap)/AlGaN/GaN | Ta/Si/Ti/Al/Ni/Ta | 5/5/20/120/40/30             | 850°C for 30s in N <sub>2</sub>             | 0.22                                | $0.78 \cdot 10^{-6}$                         |

| [19]        | None                                        | AlGaN/GaN          | Ta/Si/Ti/Al/Ni/Ta | N/A                          | 800°C for 30s in N <sub>2</sub>             | 0.24                                | $1.25 \cdot 10^{-6}$                         |

| [20]        | Recess                                      | GaN(cap)/AlGaN/GaN | Ti/Al/W           | 60/100/30                    | $870^{\circ}C$ for $30s$ in $N_2$           | 0.49                                | $6.5 \cdot 10^{-6}$                          |

| [21]        | None                                        | GaN(cap)/AlGaN/GaN | Ti/Al/Ni/Pt       | 20/100/40/50                 | 975°C for 30s in N <sub>2</sub>             | 0.6                                 | N/A                                          |

| [22]        | Recess                                      | AlGaN/GaN/AlGaN    | Ti/Al/TiN         | N/A                          | $550^{\circ}$ C for 90s in N <sub>2</sub>   | 0.62                                | N/A                                          |

| [23]        | None                                        | AlGaN/GaN/AlGaN    | Ti/Al/W           | 20/100/20                    | $600^{\circ}$ C for $60s$ in N <sub>2</sub> | 0.65                                | N/A                                          |

| [24]        | Cl <sub>2</sub> -based recess               | GaN(cap)/AlGaN/GaN | Ti/Al/Ti/TiN      | 30/150/30/50                 | $600^{\circ}$ C for 30s in N <sub>2</sub>   | 0.81                                | N/A                                          |

| [25]        | None                                        | AlGaN/GaN          | Ti/Al/W           | 40/100/60                    | 875°C for 30s in N <sub>2</sub>             | 0.93                                | N/A                                          |

| [26]        | None                                        | AlGaN/GaN          | Ti/Al/Ti/TiN      | 20/120/45/120                | 870°C for 45s in N <sub>2</sub>             | 2.1                                 | $35 \cdot 10^{-6}$                           |

| [27,<br>28] | None                                        | InAlN/GaN          | Hf/Al/Ta          | 15/200/20                    | 600°C                                       | 0.58                                | $6.75 \cdot 10^{-6}$                         |

| [29]        | Cl <sub>2</sub> /Ar-based recess            | AlGaN/AlN/GaN      | Ta/Al/Ta          | 20/280/100                   | N/A                                         | .34                                 | N/A                                          |

| [30]        | None                                        | GaN(cap)/AlGaN/GaN | Ta/Al/Ta          | 10/280/20<br>10/140/20       | $550^{\circ}C$ for $60s$ in $N_2$           | .06<br>.26                          | N/A<br>N/A                                   |

| [31]        | None                                        | InAlN/AlN/GaN      | Ta/Al/Ta          | N/A                          | 550°C in N <sub>2</sub>                     | 0.64                                | N/A                                          |

| [17]        | Cl <sub>2</sub> -based<br>recessed<br>ohmic | GaN(cap)/AlGaN/GaN | Ta/Al/Ta          | 3.5/100/10                   | <600°C for 4min in N2                       | 0.2                                 | N/A                                          |

Besides gold-free ohmic contacts, another method to reduce the contact resistance is by inserting a thin layer of either Si or Ge in the stack. Silicon and Germanium are both n-type dopants for GaN with specific growth conditions. During MOVPE epitaxial growth of  $n^+$ -GaN, silane (SiH<sub>4</sub>) or the more reactive disilane (Si<sub>2</sub>H<sub>6</sub>) gases are used to obtain a Si-doped layer. For Ge-doping, GeH<sub>4</sub> gas is commonly used, although it has been shown it is 10 times less efficient doping compared to Silicon [32]. Similar results were shown for MOCVD growth [33]. Since Si and Ge are typical n-type dopants for GaN, inserting these materials in the metal stack may lead to diffusion of carriers into the substrate leading to better ohmic contacts. There have been several structures studied and are summarized on . For some reported technologies, depositing Si or Ge prior to metal stack results in better contacts, while in others, deposition as the second layer shows better results. The following references also consider several other variables such as thicknesses, annealing temperatures and thus, only the best results from each study are tabulated.

| Ref  | Pre-<br>metallization<br>treatment | Substrate                      | Metal Stack       | Metal Thickness<br>(nm) | Annealing<br>Conditions                                            | Contact<br>Resistance<br>(Ω∙mm) | Specific<br>Contact<br>Resistance<br>( <b>Ω·cm</b> <sup>2</sup> ) |

|------|------------------------------------|--------------------------------|-------------------|-------------------------|--------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------|

| [18] | None                               | GaN(cap)/AlGaN/GaN             | Ta/Si/Ti/Al/Ni/Ta | 5/5/20/120/40/30        | 850°C for 30s in N <sub>2</sub>                                    | 0.22                            | $0.78 \cdot 10^{-6}$                                              |

| [19] | None                               | AlGaN/GaN                      | Ta/Si/Ti/Al/Ni/Ta | N/A                     | $800^{\circ}$ C for $30s$ in $N_2$                                 | 0.24                            | $1.25 \cdot 10^{-6}$                                              |

| [34] | Cl4-based<br>recessed<br>ohmic     | Si-doped GaN                   | Ge/Cu/Ge          | N/A                     | 600°C for 60s in N <sub>2</sub><br>(>400°C ohmic)                  | N/A                             | $10 \cdot 10^{-6}$                                                |

| [19] | None                               | AlGaN/GaN                      | Ta/Si/Ti/Al/Ni/Ta | N/A                     | 800°C for 30s in N <sub>2</sub>                                    | 0.24                            | $1.25 \cdot 10^{-6}$                                              |

| [35] | None                               | InAlN/GaN                      | Ti/Si/Al/Si/Mo/Au | N/A                     | $850^\circ C$ for 30s in $N_2$                                     | 0.12                            | $0.387 \cdot 10^{-6}$                                             |

| [36] | None                               | GaN(cap)/AlGaN/AlN/GaN         | Si/Ti/Al/Mo/Au    | 5/20/80/35/50           | 780°C for 60s in N <sub>2</sub>                                    | 0.45                            | N/A                                                               |

| [37] | SiCl <sub>4</sub><br>exposure      | AlGaN/GaN                      | Ti/Si/Al/Si/Mo/Au | 15/10/60/10/35/50       | $850^{\circ}$ C for 30s in N <sub>2</sub>                          | 0.16                            | 0.677·10 <sup>-6</sup>                                            |

| [38] | SiCl <sub>4</sub> exposure         | AlGaN/GaN                      | Si/Ti/Al/Mo/Au    | 5/15/60/35/50           | $850^{\circ}C$ for $30s$ in $N_2$                                  | 0.31                            | N/A                                                               |

| [39] | None                               | n <sup>+</sup> AlGaN/AlGaN/GaN | Si/Ti/Al/Cu/Au    | 3/85/50/80/100          | $800^{\circ}$ C for $30s$ in $N_2$                                 | N/A                             | $38 \cdot 10^{-6}$                                                |

| [40] | None                               | GaN(cap)/AlGaN/GaN             | Si/Ti/Al/Mo/Au    | 1/15/90/45/55           | 800°C for 30s                                                      | 0.18                            | $1 \cdot 10^{-6}$                                                 |

|      | none<br>Cl <sub>2</sub> -based     | InAlN/GaN                      |                   |                         | 840°C for 15s in N <sub>2</sub><br>835°C for 15s in N <sub>2</sub> | 0.30<br>0.34                    |                                                                   |

| [41] | recessed<br>ohmic                  | InAlGaN/GaN                    | Si/Ti/Al/Ni/Au    | 2/20/100/40/50          | 860°C for 18s in N <sub>2</sub>                                    | 0.23<br>0.31                    | N/A                                                               |

| [42] | none<br>None                       | AlGaN/GaN                      | Si/Ti/Al/Ni/Au    | N/A                     | 800°C for 30s                                                      | 0.23                            | $1.06 \cdot 10^{-6}$                                              |

Table IV List of ohmic contacts on GaN using either Si or Ge to improve the contact resistance.

#### 1.3.4. Ohmic post-metal processing

Lastly, post metal processing is also extremely important to achieve low-contact resistance. As noted earlier, a high temperature annealing is required to induce ohmic behavior and as we have seen in the previous sections, there are several different temperatures research groups have found has worked for them. It is desirable to refrain from any processing with temperatures >870° C as damage to the 2DEG becomes highly unstable, thus limiting its' performance as a transistor. The amount of time the contacts are annealed are also important. Typically, this ranges from 15 s up to 1 or 2 min. Although some researchers have reported a two-step annealing process yields better results [43], more commonly a single step is sufficient and desirable. Lastly, ambient gas during annealing plays a key role as well. Most modern-day rapid thermal annealing systems have the options of N<sub>2</sub>, Ar, O<sub>2</sub>, forming gas (N<sub>2</sub>/H<sub>2</sub>) and vacuum as the ambient condition. There are several reports using the first three mentioned gases (N<sub>2</sub>, Ar and O<sub>2</sub>) but limited information on those using vacuum.

To conclude, there is many variables when developing the process for ohmic contacts on GaN. The most important goals to consider include: low-contact resistance, low-temperature annealing, gold-free technology and 'smooth' surface morphology. The best reports thus far utilize GaN-regrowth using MBE to yield contact resistance as low as 0.1  $\Omega$ ·mm on InAlN/GaN [3, 14, 15], however, the high cost associated with operation of MBE yields it impractical.

## 1.4. Introduction to Dielectrics

## 1.4.1. Background on interface trap density extraction

In the metal-oxide-semiconductor field effect transistor (MOSFET) structure, the oxide layer plays a key role on transistor performance. In the early days of semiconductor research, Silicon dominated the market since it had an excellent ability to grow a highly stable and compatible oxide layer, i.e. SiO<sub>2</sub>. Exposure of a clean Silicon lattice to oxygen ambient, either by water vapor or O<sub>2</sub> gas (i.e. wet or dry oxidation), consumes part of the Silicon structure to form SiO<sub>2</sub> compound. This compound is an excellent insulator with the obvious purpose to use in the MOSFET structure. Moreover, the number of defects at the interface between Si-SiO<sub>2</sub> is of excellent quality. However, GaN does not share these qualities, thus, other types of insulators have been widely studied. As researchers began fabricating and measuring GaN-based MISHFETs, they found that the electrical measurements exhibit peculiar negative effects such as current collapse [44], threshold voltage instability and degradation of 2DEG mobility [45]. They attributed these negative effects to the defects at the oxide/semiconductor interface.

But what are defects and how can we measure the 'amount' of defects? Professor Dieter K. Shroder has written an excellent book describing these defects in [46] in Chapter 6. There are 4 types of defect charges in an oxide-semiconductor system, they include fixed, mobile and trapped oxide charges and interface trapped charge. The first three are within the oxide layer and some are mobile while others are fixed. These are primarily caused by growth conditions and impurities in the film. The other type of defects is interface trapped charges, which I focused my most attention to. Focusing on the atomic structure of the oxide/semiconductor layer, at the transition region (i.e. interface) there is a large density of defects present. These defects are cause by a combination of contaminants and dangling bonds (un-liked atoms in the structure). In effect, the

defects present electron/hole trap centers which will negatively influence electrical performance of the device.

There are both qualitative and quantitative methods to probe the traps at the interface. The number of traps is typically reported in amount per unit area per energy ( $cm^{-2}eV^{-1}$ ). These values physically correspond the number of traps in a unit area at a certain energy level within the semiconductor's bandgap. Different levels of energy correspond to different response times of the traps. Shallow traps, i.e. traps close to the band edges, respond quickly to electrical signals which in turn affects high-frequency operations of a device while deep level traps require more time to charge/discharge affecting mostly DC (direct current) operation.

## 1.4.2. Metal-Insulator-Semiconductor Capacitor