# HI PROF : Hardware Interface for Pipelined Reconfiguration of FPGAs

BY

ALESSANDRO VALLERO Laurea, Politecnico di Torino, Turin, Italy, 2013

## THESIS

Submitted as partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2014

Chicago, Illinois

Defense Committee:

Jon Solworth, Chair and Advisor Igor Paprotny Paolo Prinetto, Politecnico di Torino

# ACKNOWLEDGMENTS

I want to thank all LAB 6 guys from Politecnico di Torino who created a stimulating environment that has accompanied me throughout the whole duration of the thesis. Special thanks go to Dr. Pascal Trotta who has transfered to me all its knowledge about reconfiguration, Dr. Giulio Gambardella who was always available to help me and Dr. Marco Indaco who inspired different ideas. I also want to thank all my family who supported and suffered with me during these years.

AV

# TABLE OF CONTENTS

| CHAPTI   | $\overline{\mathbf{ER}}$ |                                                         | PAGE        |

|----------|--------------------------|---------------------------------------------------------|-------------|

| 1        | INTROI                   |                                                         | 1           |

|          | 1.1                      | The goals of the thesis                                 | 3           |

|          | 1.2                      | Thesis organization                                     | 4           |

| <b>2</b> | RECON                    | FIGURABLE SYSTEMS                                       | 6           |

|          | 2.1                      | Introduction to the concept of reconfigurable computing | 6           |

|          | 2.2                      | Why reconfigurable computing is promising               | 7           |

|          | 2.3                      | FPGA                                                    | 10          |

|          | 2.3.1                    | History and performance                                 | 10          |

|          | 2.3.2                    | FPGA architecture                                       | 12          |

|          | 2.3.3                    | FPGA types                                              | 15          |

| 3        |                          | OT JUST A MATTER OF RECONFIGURATION :                   |             |

|          |                          | OF THE ART                                              | 18          |

|          | 3.1                      | Reconfiguration                                         | 18          |

|          | 3.1.1                    | What is reconfiguration?                                | 19          |

|          | 3.1.2                    | Types of reconfigurations                               | 21          |

|          | 3.2                      | Reconfigurable architectures                            | 24          |

|          | 3.2.1                    | Block reconfigurable architecture                       | 25          |

|          | 3.2.2                    | Pipelined reconfigurable architecture                   | 26          |

|          | 3.3                      | Hybrid reconfigurable systems                           | 27          |

|          | 3.3.1                    | Hybrid system-level architectures                       | 28          |

|          | 3.3.2                    | An OS supporting hybrid architectures                   | 31          |

| 4        | THE PR                   | <b>OPOSED HARDWARE INFRASTRUCTURE : HI PRO</b>          | <b>F</b> 34 |

|          | 4.1                      | The propsed architecture                                | 34          |

|          | 4.1.1                    | The bus-module interfaces                               | 35          |

|          | 4.1.2                    | The communication manager                               | 40          |

|          | 4.1.2.1                  | The internal bus                                        | 40          |

|          | 4.1.3                    | The configuration manager                               | 43          |

|          | 4.1.4                    | The interface with the system                           | 44          |

|          | 4.2                      | Performance of pipelined reconfiguration                | 46          |

|          | 4.3                      | Guidelines for designing a hardware module systems      | 51          |

|          | 4.4                      | Interface with the OS                                   | 56          |

|          | 4.4.1                    | The scheduler                                           | 60          |

|          | 4.4.2                    | The possibility to preempt a hardware task              | 61          |

|          | 4.4.3                    | Virtual reconfiguration space                           | 61          |

# TABLE OF CONTENTS (continued)

# **CHAPTER**

# PAGE

| 5.1     | Building the reconfigurable system |

|---------|------------------------------------|

| 5.1.1   | Target FPGA                        |

| 5.1.2   | Target board                       |

| 5.1.3   | LEON3 and GRLIB                    |

| 5.2     | Cases of study                     |

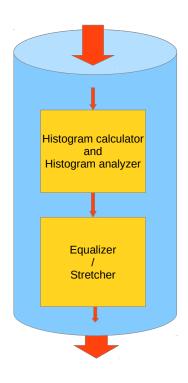

| 5.2.1   | FEMIP                              |

| 5.2.1.1 | Obtained results                   |

| 5.2.2   | SAFE                               |

| 5.2.2.1 | Obtained results                   |

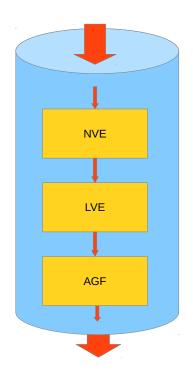

| 5.2.3   | AIDI                               |

| 5.2.3.1 | Obtained results                   |

# LIST OF FIGURES

| <b>FIGURE</b> |                                                                                                                                                                                                                                                                                               | PAGE |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

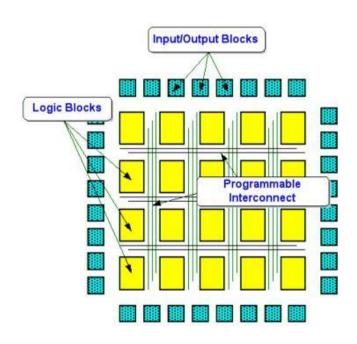

| 1             | FPGA main structure                                                                                                                                                                                                                                                                           | 12   |

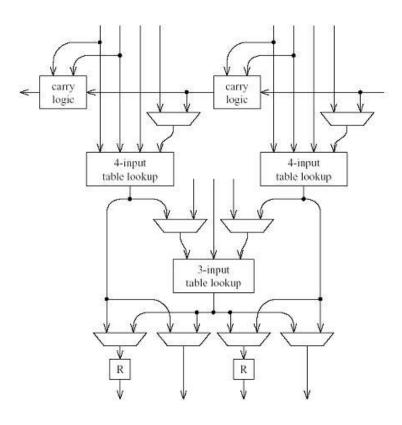

| 2             | FPGA carry chain circuit                                                                                                                                                                                                                                                                      | 14   |

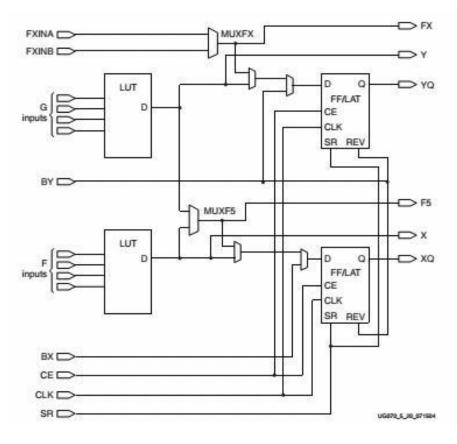

| 3             | FPGA slice of a XILINX Virtex 4                                                                                                                                                                                                                                                               | 16   |

| 4             | Communication problem between two different configurations                                                                                                                                                                                                                                    | 22   |

| 5             | Partial reconfiguration scenario                                                                                                                                                                                                                                                              | 23   |

| 6             | Partial reconfiguration example                                                                                                                                                                                                                                                               | 24   |

| 7             | A typical implementation of a block reconfigurable architecture                                                                                                                                                                                                                               | 26   |

| 8             | A pipeline reconfigurable architecture with three physical stages (a). A 3-stage physical pipeline implementing a 4-stage virtual pipeline (b). Numbers within physical pipeline stages indicate the implemented virtual pipeline stage. Shaded stages are reconfiguring for the given cycle. | 27   |

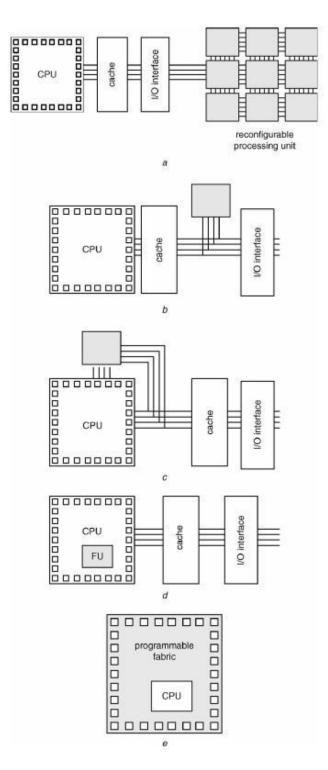

| 9             | Five classes of reconfigurable systems: $a$ ) External stand-alone process-<br>ing unit; $b$ ) Attached processing unit; $c$ ) Co-processor; $d$ ) Reconfigurable<br>functional unit; $e$ ) Processor embedded in reconfigurable fabric                                                       | 29   |

| 10            | Summary of system architectures                                                                                                                                                                                                                                                               | 30   |

| 11            | The structure of HI PROF                                                                                                                                                                                                                                                                      | 36   |

| 12            | The structure of bus-module interfaces                                                                                                                                                                                                                                                        | 37   |

| 13            | The communication manager                                                                                                                                                                                                                                                                     | 39   |

| 14            | The internal bus                                                                                                                                                                                                                                                                              | 41   |

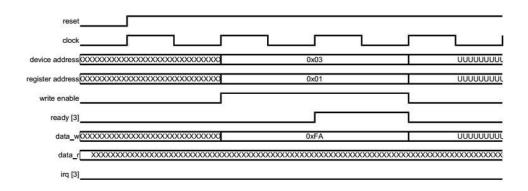

| 15            | Write operation                                                                                                                                                                                                                                                                               | 43   |

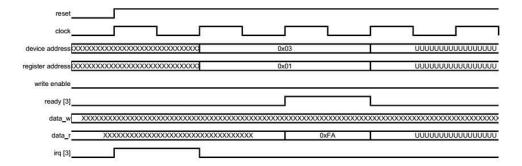

| 16            | Read operation                                                                                                                                                                                                                                                                                | 44   |

# LIST OF FIGURES (continued)

# **FIGURE**

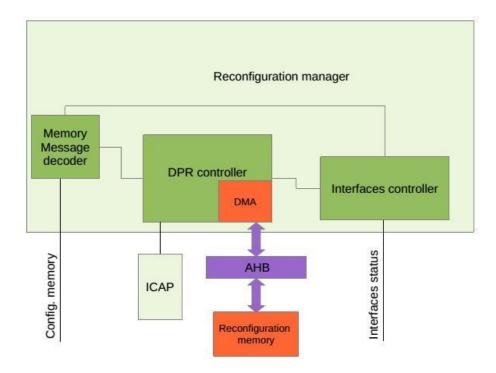

| 17 | The configuration manager                                                                                                                                                                                     | 45 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

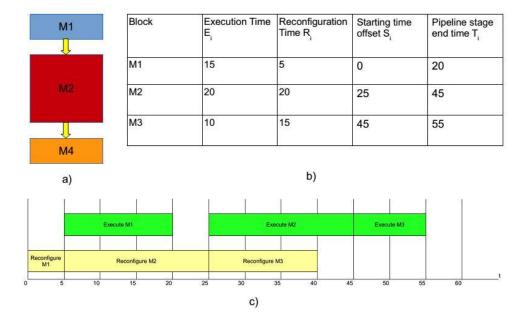

| 18 | An example is reported. a) shows the sequential modules that must be implemented. b) reports execution and reconfiguration time for each pipeline stage. c) wants to illustrate how reconfiguration is masked | 49 |

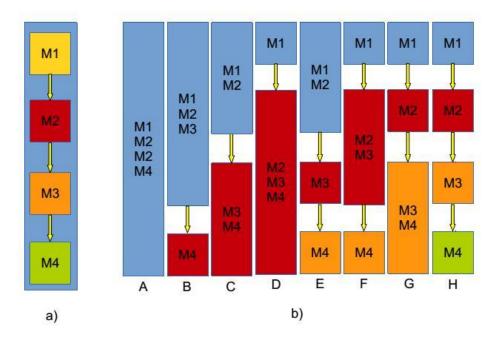

| 19 | a) The sequential sub-task of the main module M b)All the possible partitionings for main task M                                                                                                              | 52 |

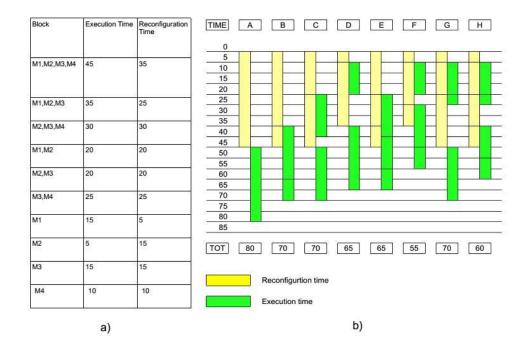

| 20 | a) The execution and reconfiguration time for every partitioned block<br>b)time needed to complete is compared among all the possible imple-<br>mentation                                                     | 53 |

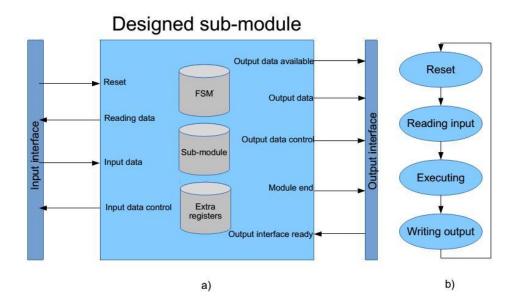

| 21 | a) The signals required by sub-modules to be interfaced with bus-module interfaces, the FSM and extra registers b)The simple FSM embedded in sub-modules implementation                                       | 56 |

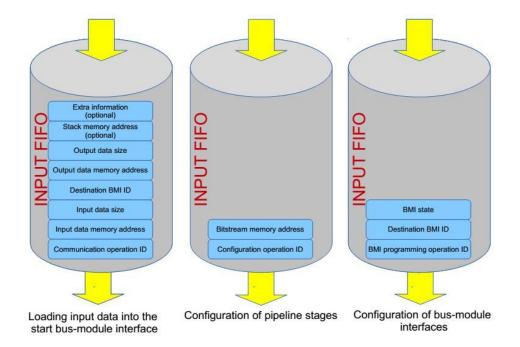

| 22 | The different protocols must be respected according to the issued oper-<br>ation when writing commands into the input FIFO                                                                                    | 58 |

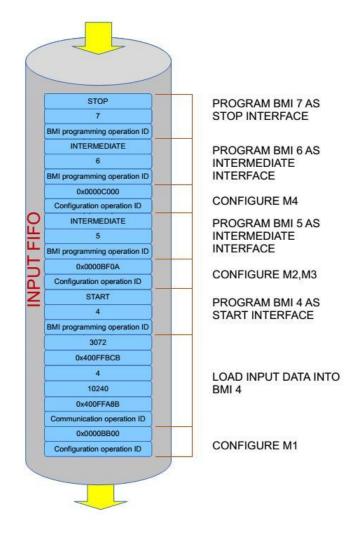

| 23 | The commands to push into the FIFO when, in the example, task M must be executed                                                                                                                              | 59 |

| 24 | Available resources in XC4VFX12 FPGA                                                                                                                                                                          | 64 |

| 25 | GR-CPCI-XC4V board                                                                                                                                                                                            | 65 |

| 26 | The bus-based SoC embedding HI PROF                                                                                                                                                                           | 66 |

| 27 | FEMIP sequential task subdivision                                                                                                                                                                             | 67 |

| 28 | Pipleined reconfiguration limitations                                                                                                                                                                         | 70 |

| 29 | What happens inside HI PROF for a 4-stages pipeline                                                                                                                                                           | 71 |

| 30 | Reconfiguration time overhead and bitstream size are analyzed for the traditional, the 4-stages and the 5-stages implementations                                                                              | 72 |

| 31 | Resources employment is analyzed for the traditional, the 4-stages and the 5-stages implementations                                                                                                           | 73 |

| 32 | These are FEMIP benefits and drawbacks intoduced by HI PROF $\ . \ .$                                                                                                                                         | 74 |

# LIST OF FIGURES (continued)

# **FIGURE**

# PAGE

| 33 | SAFE partitioning                                                                                                             | 76 |

|----|-------------------------------------------------------------------------------------------------------------------------------|----|

| 34 | Reconfiguration time overhead and bitstream size are analyzed for tra-<br>ditional, tailored and non-tailored implementations | 77 |

| 35 | Resources employment is analyzed for traditional, tailored and non-<br>tailored implementations                               | 78 |

| 36 | These are SAFE benefits and drawbacks intoduced by HI PROF                                                                    | 79 |

| 37 | AIDI partitioning                                                                                                             | 80 |

| 38 | Reconfiguration time overhead and bitstream size are analyzed for tra-<br>ditional, 3-stages and 2-stages implementations     | 82 |

| 39 | Resources employment is analyzed for traditional, 3-stages and 2-stages implementations                                       | 82 |

| 40 | These are AIDI benefits and drawbacks intoduced by HI PROF                                                                    | 83 |

# LIST OF ABBREVIATIONS

| AGF   | Adaptive Gaussian Filter                |

|-------|-----------------------------------------|

| AIDI  | Adaptive Image Denoising IP-core        |

| ASIC  | Application Specific Integrated Circuit |

| ASSP  | Application Specific Standard Product   |

| BRAM  | Block RAM                               |

| CPU   | Central Processing Unit                 |

| CLB   | Configurable Logic Blocks               |

| DCM   | Digital Clock Manager                   |

| DMA   | Direct Memory Access                    |

| DPR   | Dynamic Partial Reconfiguration         |

| DSP   | Digital Signal Processing               |

| FEM   | Feature Extraction and Matching         |

| FEMIP | Feature Extraction and Matching IP-Core |

| FIFO  | First-In First-Out                      |

| FPGA  | Field Programmable Gate Array           |

| FSM   | Finite State Machine                    |

| F+V   | Fixed-Plus-Variable                     |

# LIST OF ABBREVIATIONS (continued)

| HE      | Histogram Equalization                           |

|---------|--------------------------------------------------|

| HI PROF | Hardware Interface for Pipelined Reconfiguration |

|         | of FPGAs                                         |

| HS      | Histogram Stretching                             |

| HW      | Hardware                                         |

| IET     | Image Enhancement Technique                      |

| ΙΟ      | Input Output                                     |

| IP      | Intellectual Property                            |

| LUT     | LookUp Table                                     |

| LVE     | Local Variance Estimator                         |

| NMS     | Non-maxima suppressor                            |

| NVE     | Noise Variance Estimator                         |

| OS      | Operating System                                 |

| PC      | Personal Computer                                |

| PCB     | Printed Circuit Board                            |

| PLD     | Programmable Logic Device                        |

| PROM    | Programmable Read-Only Memory                    |

| RAM     | Random-Access Memory                             |

| RH      | Reconfigurable Hardware                          |

# LIST OF ABBREVIATIONS (continued)

| RHOS | Reconfigurable Hardware Operating System |

|------|------------------------------------------|

| RTR  | Run-Time Reconfiguration                 |

| R&D  | Research and Development                 |

| SAFE | Self Adaptive Frame Enhancer             |

| SoC  | System on Chip                           |

| SRAM | Static Random-Access Memory              |

| SW   | Software                                 |

# SUMMARY

In recent years FPGAs (Field Programmable Gate Arrays) market has grown dramatically. Increasing of performances and available resources in FPGA devices, due to technological scaling, have led many designers to adopt FPGA-based solution instead of ASIC. Thanks to the fact that FPGAs offer the possibility of reconfiguring hardware, a new concept has born: *reconfigurable computing*. Reconfigurable computing exploits FPGA to perform tasks by mean of *dynamic partial reconfiguration* (DPR). DPR allows the task of reconfiguring a particular section of an FPGA design while the remaining part is still running.

Reconfigurable computing is becoming increasingly attractive for many applications thanks to its impressive performance and flexibility. However, since development of reconfigurable systems is still a maturing field, there are a number of challenges in developing a reconfigurable system.

The goal of this work is to develop a novel hardware infrastructure to implement a highperformance flexible reconfigurable system able to leverage reconfigurable hardware in an efficient way.

## CHAPTER 1

### INTRODUCTION

In recent years FPGAs (Field Programmable Gate Arrays) market has grown dramatically. Increasing of performances and available resources in FPGA devices, due to technological scaling, have led many designers to adopt FPGA-based solution instead of ASIC (Application Specic Integrated Circuit). Lately, some FPGAs vendors, such as Xilinx and Altera, introduced in their FPGAs Partial Reconfiguration functionalities. Partial Reconfiguration allow to reconfigure only specific parts of design, instead of reconfigure the entire device. Dynamic Partial Reconfiguration (DPR) allows the task of reconfiguring a particular section of an

FPGA design while the remaining part is still running.

As a consequence, a new idea in digital systems field has raised rapidly: reconfigurable computing. Reconfigurable computing is establishing itself as a major discipline that covers various subjects of learning, including both computing science and electronic engineering. In fact, reconfigurable systems accelerate computation leveraging architectures based on a mixture of general purpose processors and reconfigurable components. Reconfigurable computing is becoming increasingly attractive for many applications thanks to its impressive performance. In fact, recent research suggests that it is a trend rather than a one-off for massive data computing applications such as image processing and floating-point operations. Moreover, thanks to the possibility of reducing power consumption, component size and count, the possibility of embedding a soft processor and the possibility to be upgraded after market, reconfigurable systems have captured the interest of embedded systems designer too.

Thanks to possibility to integrate hardware and software, hybrid systems, composed of general purpose processors and reconfigurable devices, have rapidly become of interest. In fact, research efforts were addressed to create a hardware and software layers, that is an efficient infrastructure allowing communication between CPU and reconfigurable hardware. Different system-level architecture were proposed for this pupopse (1) associated with the birth of first operating systems for reconfigurable systems(2) (3) (4). RHOSs (Reconfigurable Hardware Operating Systems) were introduced aiming to deal with hardware processes as well as mapping and scheduling functionalities. On the other hand, architectures aspire to provide a simple and efficient interface through which operating system can monitor reconfigurable hardware area. Thanks to the introduction of hardware interfaces and RHOSs, hybrid systems are improving day-by-day, promising to outperform state-of-the-art real-time and desktop computer systems.

However, since development of reconfigurable systems is still a maturing field, there are a number of challenges in developing a reconfigurable system. First challenge is to design an efficient system architecture capable of exploiting the benefits introduced by reconfigurable hardware. In particular, reconfiguration introduces a time overhead so that hardware tasks performance are influenced negatively. Moreover, because of the lack of an efficient hardware layer interface, RHOS are not being completely exploited. In fact, reconfigurable devices do not offer effective interfaces to support services such as the scheduling and mapping of tasks in the proper reconfigurable area. Secondly, a technique that maps application to a reconfigurable computing system

is still an open issue. This involves determining which parts of the application should be mapped to the reconfigurable fabric and which should be mapped to the

processor. Finally, a scheduling policy for hardware task is another question.

#### 1.1 The goals of the thesis

The goal of this work is to develop a novel hardware infrastructure to implement a highperformance flexible reconfigurable system able to leverage reconfigurable hardware in an efficient way. In particular, the thesis aims at:

- the design of a reconfigurable area architecture able to reduce reconfiguration time overhead

- giving guidelines for designing hardware applications to save the largest amount of reconfiguration time overhead

- the implementation of a system-level architecture providing flexibility of interaction between RHOS and reconfigurable modules

- the support of two new services for RHOS to improve the reconfigurable system flexibility: hardware task preemption and virtual reconfiguration

- the ease of integration of a reconfigurable unit into a bus-based SoC

#### **1.2** Thesis organization

These are the arguments treated in each chapter.

#### Chapter 2 : Reconfigurable computing

The concept of reconfigurable computing is introduced, focusing on the benefits of reconfigurable systems. Then, hybrid systems, made of general purpose processors and reconfigurable devices, are deepen. Finally, FPGAs, most popular reconfigurable devices are analyzed.

#### Chapter 3 : It is not just a matter of reconfiguration: the state-of-the-art

In this chapter, the attention is focused on reconfiguration. Reconfiguration is on open issue for reconfigurable systems, in particular for hybrid systems. The importance of reconfiguration comes from the fact it improves systems performance through flexibility, but, on the other hand, a time overhead is introduced due to the reconfiguration process. Since hybrid systems are emerging, it is necessary to create an efficient means to support reconfiguration. Different reconfigurable hardware operating systems have been proposed as a solution. After a detailed analysis on what is reconfiguration and how it works, different reconfigurable architectures are presented. It follows a treatment concerning hybrid system architectures and RHOS.

#### Chapter 4 : The proposed hardware infrastructure : HI PROF

In this chapter a novel methodology for FPGA-based reconfigurable system is discussed. The goal is to create a flexible hardware architecture for reconfigurable systems. At first, the proposed architecture is analyzed into details, focusing on benefits and drawbacks. Guidelines for implementing tasks suitable for the proposed reconfigurable architecture are then provided. In particular, the process of designing hardware modules is treated deeply. Finally, interaction between reconfigurable hardware and the OS is discussed, introducing the concept of virtual reconfiguration.

## Chapter 5 : Experimental results

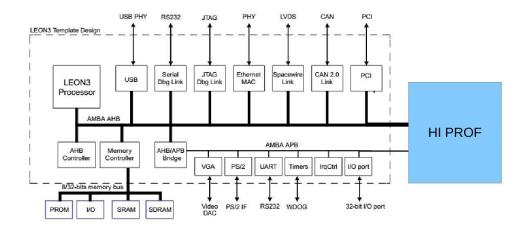

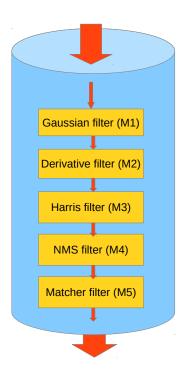

In this chapter experimental results are provided for HI PROF. In particular a reconfigurable system is set up in a SoC by means of a Virtex 4 FPGA embedding LEON3 processor. The goal of this case study is to run three image processing reconfigurable IP-core on HI PROF focusing on the design process, virtual reconfiguration space and performance. Special attention will be given to bitstream size, reconfiguration time and area overhead.

# CHAPTER 2

### **RECONFIGURABLE SYSTEMS**

In this chapter the concept of reconfigurable computing is given, focusing on the benefits introduced by reconfigurable systems. In particular, hybrid systems, made of general purpose processors and reconfigurable devices, are deepen. Finally, FPGAs, most popular reconfigurable devices are analyzed.

### 2.1 Introduction to the concept of reconfigurable computing

The idea of reconfigurable hardware belongs to Gerald Estrin and his colleagues at the University of California at Los Angeles. In the mid-1960s, they developed one of the earliest acknowledged reconfigurable computing machines, the Fixed-Plus-Variable (F+V) computer. Estrin thought reconfigurable computing as the technique to accelerate computation by means of variable configurations of specialized hardware modules in addition to a sequential processing unit. In fact, the F+V consisted of a standard processor unit that controlled many other variable units (5), (6), (7), (8).

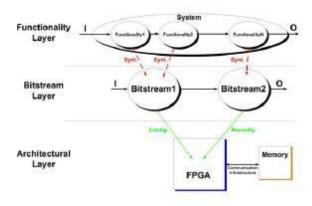

Reconfigurable systems are a computer architecture supporting reconfigurable computing. They aim at the leveraging reconfiguration so that the designed systems offer high performance through flexibility. Reconfiguration is based on two main entities: a system and a functionality. To produce output data, the system has to elaborate input according to the functionality required by the application the system runs. In fact, in a scenario where different applications have to be handled, a reconfigurable system can be thought as a system that changes at run-time according to the applications requirements.

### 2.2 Why reconfigurable computing is promising

In the computer and electronics world, there are two different ways of performing computation: hardware and software. Computer hardware, such as application-specific integrated circuits (ASICs) provide a means of addressing the processing requirements providing highly optimized resources for quickly performing critical tasks. The force point of an ASIC implementation is to provide a natural mechanism for implementing the large amount of parallelism found in applications. Their strength is the efficiency, in fact, ASICs, tailored according to the application's requirements, contain just the right mix of functional units for the target application. In other words, ASICs have the best possible performance. Despite the advantages, ASICs suffer from a long time to market and high costs (9), moreover they are permanently configured to an only-one application. As a consequence, in most of the cases, ASICs are suitable only for very high-volume applications.

On the other hand, computer software provides the flexibility to change applications and perform a huge number of different tasks. High-performance microprocessors provide an off-theshelf solution to the processing constraint, but, usually, a single processor is not fast enough, so a system composed of many processors has to be designed, introducing complexity to the design. The problem of processors is that they are not optimized for the specific application which is typical of an embedded system. As a result, their inefficiency is translated to a lack of computing performance, area efficiency and a high power consumption. Software implementation is orders of magnitude worse than an ASIC one. Moreover, the high cost of state-of-the-art processors represents an obstacle to their use in embedded systems. However, using microprocessors means a short time-to-market.

Compared to the past, today, satisfying application's requirements is becoming a challenge for designers. In fact, applications require more processing power than ever before. Applications such as streaming video, image recognition and processing, and highly interactive services are placing new demands on the computation units that implement these applications. At the same time, power consumption, manufacturing costs and time to market requirements add complexity to the system design.

To face up today-application requirements, reconfigurable hardware is coming into the computing field. In particular, the most innovative reconfigurable hardware solution is represented by Field-Programmable Gate Arrays (FPGAs). This concepts are well explained in (10):

> FPGAs are truly revolutionary devices that blend the benefits of both hardware and software. They implement circuits just like hardware, providing huge power, area, and performance benefits over software, yet can be reprogrammed cheaply and easily to implement a wide range of tasks. Just like computer hardware, FPGAs implement computations spatially, simultaneously computing millions of operations in resources distributed across a silicon chip. Such systems can be hundreds of times faster than microprocessor-based designs. However, unlike in ASICs, these computa

tions are programmed into the chip, not permanently frozen by the manufacturing process. This means that an FPGA-based system can be programmed and reprogrammed many times. However, merging the benefits of both hardware and software does come at a price. FPGAs provide nearly all of the benefits of software flexibility and development models, and nearly all of the benefits of hardware efficiency but not quite. A recent study (11) reports that moving critical software loops to reconfigurable hardware results in average energy savings of 35% to 70% with an average speedup of 3 to 7 times, depending on the particular device used. However, creating efficient programs for FPGAs is more complex than CPUs. Typically, FPGAs are useful only for operations that process large streams of data, such as signal processing, networking, and the like. An old study shows FPGAs need on average 40 times as much area, draw 12 times as much dynamic power, and run at one third the speed of corresponding ASIC implementations (12).

However, recent FPGAs seem to hopefully confirm reconfigurable hardware potentiality so that perfomance gap between ASICs and FPGAs is always decreasing. In fact, FPGAs such as the Xilinx Virtex-7 or the Altera Stratix 5 have come to rival corresponding ASIC and Application Specific Standard Product (ASSP) solutions by providing significantly reduced power, increased speed, lower materials cost, minimal implementation real-estate, and increased possibilities for re-configuration 'on-the-fly'. Despite the lack of performance, FPGAs offer several advantages compared to ASICs. While an ASIC design may take months to years to develop and have a multimilliondollar price tag, an FPGA design might only take days to create and cost tens to hundreds of dollars. In fact, a reconfigurable system can be built out of off-the-shelf components, significantly reducing the long design-time inherent in an ASIC implementation. Also unlike an ASIC, the functional units implemented in the reconfigurable fabric can change over time. This means that as the environment or usage of the embedded system changes, the mix of functional units can adapt to better match the new environment. The reconfigurable fabric in a handheld device, for instance, might implement large matrix multiply operations when the device is used in one mode, and large signal processing functions when the device is used in another mode. Typically, not all of the embedded system functionality needs to be implemented by the reconfigurable fabric. Only those parts of the computation that are time-critical and contain a high degree of parallelism need to be mapped to the reconfigurable fabric, while the remainder of the computation can be implemented by a standard instruction processor. As a result, hybrid systems, composed of processors and reconfigurable hardware, seem to be promising in real time embedded systems.

For systems that do not require the absolute highest achievable performance

or power efficiency, but that require flexibility, a short time-to-market and the ability to easily fix bugs and upgrade functionality, FPGAs are a compelling design alternative.

## 2.3 FPGA

A FPGA is an integrated circuit that can be programmed in the field one or multiple times after manufacturing. In order to implement a circuit in the FPGA a hardware descriptive language file is needed. This file is the input of a synthesis tool which generates a bitstream according to the constraints specified during the design phase. The bitstream is a binary file containing the configuration of the FPGA implementing the described circuit. In order to make the circuit run, the bitstream file is loaded into the FPGA through a configuration port.

### 2.3.1 History and performance

An introduction to the history of FPGAs can be found in (13), it is reported below:

The FPGA industry sprouted from programmable read-only memory (PROM) and programmable logic devices (PLDs). PROMs and PLDs both had the option of being programmed in batches in a factory or in the field (field programmable). However programmable logic was hard-wired between logic gates. In the late 1980s the Naval Surface Warfare Department funded an experiment proposed by Steve Casselman to develop a computer that would implement 600,000 reprogrammable gates. Casselman was successful and a patent related to the system was issued in 1992.

Some of the industry's foundational concepts and technologies for programmable logic arrays, gates, and logic blocks are founded in patents awarded to David W. Page and LuVerne R. Peterson in 1985.

Xilinx co-founders Ross Freeman and Bernard Vonderschmitt invented the first commercially viable field programmable gate array in 1985, the XC2064. The XC2064 had programmable gates and programmable interconnects between gates, the beginnings of a new technology and market. The XC2064

boasted a mere 64 configurable logic blocks (CLBs), with two 3-input lookup tables (LUTs).

The 1990s were an explosive period of time for FPGAs, both in sophistication and the volume of production. In the early 1990s, FPGAs were primarily used in telecommunications and networking. By the end of the decade, FPGAs found their way into consumer, automotive, and industrial applications.

A recent trend has been to take the coarse-grained architectural approach a step further by combining the logic blocks and interconnects of traditional FPGAs with embedded microprocessors and related peripherals to form a complete system on a programmable chip. In 2010, Xilinx Inc introduced the first All Programmable System on a Chip branded Zynq-7000 that fused features of an ARM high-end microcontroller (hard-core implementations of a 32-bit processor, memory, and I/O) with an FPGA fabric to make FPGAs easier for embedded designers to use. By incorporating the ARM processor-based platform into a 28 nm FPGA family, the extensible processing platform enables system architects and embedded software developers to apply a combination of serial and parallel processing to their embedded system designs, for which the general trend has been to progressively increasing complexity. The high level of integration helps to reduce power consumption and dissipation, and the reduced parts count vs. using an FPGA with a separate CPU chip leads to a lower parts cost, a smaller system, and higher reliability since most failures in modern electronics occur on PCBs, in the connections between chips instead of within the chips themselves.

Historically, FPGAs have been slower, less energy efficient and generally achieved less functionality than their fixed ASIC counterparts. An old study had shown that designs implemented on FPGAs need on average 40 times as much area, draw 12 times as much dynamic power, and run at one third the speed of corresponding ASIC implementations. Most recent FPGAs provide significantly reduced power, increased speed, lower materials cost, minimal implementation real-estate, and increased possibilities for re-configuration 'on-the-fly'.

Several market and technology dynamics are changing the ASIC/FPGA paradigm (14):

- Integrated circuit costs are rising aggressively

- ASIC complexity has lengthened development time

- R&D resources and headcount are decreasing

- Revenue losses for slow time-to-market are increasing

- Financial constraints in a poor economy are driving low-cost technologies

Market size of FPGA devices is increasing year by year because the performance gap with ASICs is decreasing. ASIC design is still better than FPGA-based design for area, speed and power consumption, but for many designers are switching to FPGA-based designs when it is possible. Xilinx and Altera are the current FPGA market leaders and long-time industry rivals. Together, they control over 80 percent of the market, with Xilinx alone representing over 50 percent. Other competitors include Lattice Semiconductor and Actel.

## 2.3.2 FPGA architecture

Figure 1. FPGA main structure

FPGAs are independently packaged parts marketed both as prototyping platforms and as reconfigurable alternatives to ASICs. The structure of an FPGA looks like Figure 1. About FPGA architectures is deeply analyzed in (15) and it is reported here:

> The canonical logic block is often considered to be a look-up table that takes four bits of input and generates one bit of output. By filling the table with the right bits, any four-input logic function can be realized. Various studies have suggested that four inputs is a good size for these lookup tables, trading utility (how powerful the blocks are) against utilization (what fraction of their power ends up idle) (16).

> Logic blocks in actual FPGAs tend to be more complex than a single lookup table; Figure 3 has a similar diagram for a Xilinx 4000-series logic block, which has two four-input look-up tables and an extra three input table, for a total of eleven bits of input and four bits of output (17), (18).

A dedicated carry chain circuit at the top of the Figure 2 makes it easy to gang together a line of logic blocks to form a relatively fast multi-bit adder. This diagram in fact ignores many additional details, such as the way Xilinx's two 16-bit lookup tables can be used together as 32 bits of random access memory, or the options available for controlling the clocking of the two single-bit registers. Even a complex Xilinx logic block is quite small compared to the usual functional units of a computer. But in large numbers, small logic blocks can add up to considerable computing power. The die sizes of the largest parts are generally at the boundary of what can be manufactured, but this of course is not true of the smaller parts, and the future is expected to bring only greater densities (15). FPGA is an integrated circuit that contains many, in many case more than 10,000, identical logic cells (LC) that can be viewed as standard components. Each logic cell can independently take on any one of a limited set of personalities. The individual cells are interconnected by a matrix of wires and programmable switches. A user's design is implemented by specifying the simple logic function for each cell and selectively closing the switches in the interconnect matrix. Complex designs are created by combining these basic blocks to create the desired circuit. Field Programmable means that the FPGA's function is defined by a user's program rather than by the manufacturer of the device. Depending on the particular device, the program is either burned in permanently or semi-permanently as part of a board assembly process, or is loaded from an external memory each time the device is powered up.

Figure 2. FPGA carry chain circuit

Configurable elements of an FPGA are described by (19) and are reported below:

FPGA has three major configurable elements: CLBs, input/output blocks, and interconnects. The CLBs provide the functional elements for constructing user's logic. The IOBs provide the interface between the package pins and internal signal lines. The programmable interconnect resources provide routing paths to connect the inputs and outputs of the CLBs and IOBs onto the appropriate networks (20). Each CLB contains four LC's, organized in two similar slices. Figure 3 shows a detailed view of a single slice. Virtex function generators are implemented as 4-input look-up tables, LUT's.

FPGAs can provide perfomance that can be compared to CMOS VLSI. Moreover, costs delays and drawbacks related to masked gate array are reduced in a non negligible way.

## 2.3.3 FPGA types

Since there are different types of FPGAs, choosing the proper one is a crucial point. In fact they differ from architectures and processes. Four main categories can be distinduished among CPLD: symmetrical array, row-based, hierarchical PLD, and sea-of-gates. Main differences are interconnections and the way they can be programmed. Current technologies in use are: SRAM-based, flash-based and anti-fuse-based. Depending upon the application, one FPGA technology may have features desirable for that application:

• SRAM-based: configuration data is stored in Static RAM memory cells. Since SRAM is volatile and can't keep data without power source, such FPGAs must be configured upon startup. The SRAM cells maintaining configuration require about 6 to 7 MOS per connection; these extra transistors take up extra silicon and increase area. Moreover the external memory needed to load configuration data on the internal SRAM requires extra

Figure 3. FPGA slice of a XILINX Virtex 4

board space which increases board and component cost to the overall system. The only advantage is the possibility to re-program FPGA at any time and configuration time is smaller than other solutions such Flash-based. SRAM-based FPGAs include most chips of Xilinx Virtex and Spartan families and Altera Stratix and Cyclone families. Some FPGA families, such as Xilinx Spartan-3AN family and Lattice XP2 family, have an internal flash memory that stores configuration data while FPGA is not powered and, on startup, automatically loads configuration data in SRAM cells, eliminating the need for external memory.

- FLASH-based: flash-based FPGAs use flash memory as a primary resource for configuration storage, and doesn't require SRAM; this technology has an advantage of being less power consumptive and is also more tolerant to radiation effects. Examples of Flash-based FPGA families are Igloo and ProASIC3 manufactured by Actel.

- Anti-Fuse based: an anti-fuse is put into high impedance state when it is produced. In a secondary moment, this can be programmed into both low impedance and fused state by means of high currents. Anti-fuse based FPGA can be programmed just once because a burned antifuse cannot come back into the high impedance state. Axcelerator produced by Actel is an example of anti-fuse based FPGAs.

### CHAPTER 3

# IT IS NOT JUST A MATTER OF RECONFIGURATION : STATE OF THE ART

In this chapter, the attention is focused on reconfiguration. Reconfiguration is on open issue for reconfigurable systems, in particular for hybrid systems. The importance of reconfiguration comes from the fact it improves systems performance through flexibility, but, on the other hand, a time overhead is introduced due to the reconfiguration process. Since hybrid systems are emerging, it is necessary to create an efficient means to support reconfiguration. Different reconfigurable hardware operating systems have been proposed as a solution. After a detailed analysis on what is reconfiguration and how it works, different reconfigurable architectures are presented. It follows a treatment concerning hybrid system architectures and RHOS.

### 3.1 Reconfiguration

An introduction to reconfiguration have been explained in (10) and it is reported below:

The flexibility of reconfigurable devices allows them to be customized to a wide variety of applications. Even individual applications can benefit from reconfiguration by using the hardware to perform different tasks at different times.

If not all of an application's configurations fit on the hardware simultaneously, they can be swapped in and out as needed. In some cases, the circuitry implemented on reconfigurable hardware can also be optimized based on specific run-time conditions, further improving system efficiency. The process of reconfiguring the hardware at run-time, whether to accelerate different applications or different parts of an individual application, is called run-time reconfiguration(RTR). Unfortunately, although RTR can increase hardware utilization, it can also introduce significant reconfiguration overhead. Reconfiguring the hardware, depending on its capacity and design, can be very time consuming. Modern high-end FPGAs can have tens of millions of configuration points, and writing this information can require on the order of hundreds of milliseconds (21), (22). n a reconfigurable computing system, where the compute-intensive portions of applications are implemented on reconfigurable hardware, computation and reconfiguration are mutually exclusive operations. Thus, time spent reconfiguring is time lost in terms of application acceleration. Studies estimate that, in some cases, reconfiguration time alone occupies approximately 25 to 98 percent of the total execution time of a reconfigurable computing application((23), (24), (25)).Therefore, management and minimization of reconfiguration overhead to maximize the performance of reconfigurable computing systems is essential.

At first, the process of reconfiguration discuss. Then, different configuration architectures

are presented, including those designed specifically to help reduce reconfiguration overhead.

#### **3.1.1** What is reconfiguration?

What reconfiguration is have been explained in (10) and it is reported below:

In reconfigurable devices, such as field-programmable gate arrays (FP-GAs), logic and routing resources are controlled by reprogrammable memory locations, such as SRAM or Flash RAM. Boolean values held in these memory bits control whether certain wires are connected and what functionality is implemented by a particular piece of logic. The process of loading the Boolean values into these memory locations is called reconfiguration. A specific implementation for particular memory locations in hardware defines a specific circuit and is called a configuration for a given hardware task. Runtime reconfiguration involves reconfiguring the device (loading a new set of 1s and 0s) with a different configuration (a specific sequence of 1s and 0s) from the one previously loaded in the reconfigurable hardware (RH). The specific sequence of 1s and 0s for a configuration is called bitstream. The bitstreams themselves are created by CAD software based on both the circuit design to be implemented and the architecture of the implementing RH. The architectural information is required for the design tools to know which

configuration bits control which resources and what effect a 1 has versus a 0 in each of the configuration bit locations.

There are different models of reconfiguration, that can be classified according to the following scheme (26):

- who controls the reconfiguration;

- where the reconfigurator is located;

- when the configurations are generated;

- which is the granularity of the reconfiguration;

- in what dimension the reconfiguration operates.

The first subdivision (who and where) is between external and internal reconfiguration. In the first scenario, the reconfiguration is managed by an external entity, usually a PC or a dedicated processor. Internal reconfiguration, instead, is performed completely within the FPGA boundaries; to implement internal reconfiguration, the device must have a physical dedicated component, such as the ICAP component in Xilinx FPGAs.

It follows a description taken by (27) about reconfiguration:

The generation of the configurations (when) can be done in a completely static way (at design time) by determining all the possible configurations of the system. Each module must be synthesized and all possible connections between modules and the rest of the system must be considered. Other possibilities are run-time placement of pre-synthesized modules, which requires dynamic routing of interconnection signal, or completely dynamic modules generation. This last option is currently impracticable, since it would require run-time synthesis of modules from VHDL(or other hardware description language) code, that is a process requiring prohibitive times in an online environment.

Reconfiguration can take place at very different granularity levels (which), depending on the size of the reconfigured area. Two typical approaches are small bits and module based: the first one consists in modifying a single portion of the design, such as single Configurable Logic Blocks (clb) or IO blocks parameters (28), while the second one involves the modification of a larger FPGA area by creating hardware components (modules) that can be added and removed from the system: each time a reconfiguration is applied, one or more modules are linked or unlinked from the system.

The last property is the dimension. It can be distinguished between two different possibilities: mono-dimensional (1d) and bi-dimensional (2d) reconfiguration. In a truly 2d reconfiguration it is possible to reconfigure an arbitrary portion of the FPGA without affecting the execution of the rest of the implementation. Older FPGA, instead, require that in order to reconfigure a portion of a column of reconfigurable cells the whole column must stop its operations.

### 3.1.2 Types of reconfigurations

(27) gives an overview about types of reconfigurations, it is reported below:

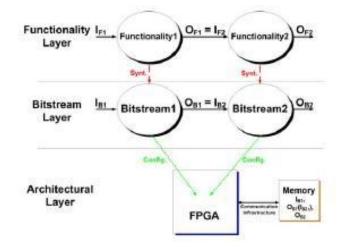

The easiest way in which an FPGA can be reconfigured is called complete. In this case the configuration bitstream, containing the FPGA configuration data, provides information regarding the complete chip and it configures the entire FPGA, that is why this technique is called complete. With this approach there are no particular constraints that have to be taken into account during the reconfiguration action, obviously that does not mean that the designer is allowed whatever he/she wants only because she/he is using a configuration technique based on a complete-reconfiguration, in fact, if two different bitstreams implement two functionalities that have to work one after the other, see Figure 4 for an example of such a scenario, the designer has to take into account where to store the data between these two configurations. The main disadvantage of an approach based on the complete

Figure 4. Communication problem between two different configurations

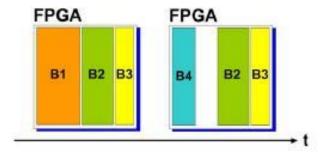

reconfiguration technique is the overhead introduced into the computation by the reconfiguration. In order to cope with this situation a partial reconfiguration approach has been proposed. Partial reconfiguration is useful for applications that require the load of different designs into the same area of the device or the flexibility to change portions of a design without having to either reset or completely reconfigure the entire device. For current FPGA devices, data is loaded on a column-basis, with the smallest load unit being a configuration bitstream frame, which varies in size based on the target device. Active partial reconfiguration of Virtex devices, or simply partial reconfiguration, is accomplished in either slave SelectMAP mode or Boundary Scan, JTAG mode. Instead of resetting the device and performing a complete reconfiguration, new data is loaded to reconfigure a specific area of the device, while the rest of the device is still in operation. The scenario shown in Figure 4 turns into the scenario proposed in Figure 5. Using an approach basedon partial reconfiguration, as the one proposed in Figure 5, the basic idea is to partition the system in a set of functionalities  $f_1, f_2, ..., f_n$  able to produce a set of bitstreams  $b_1, b_2, ..., b_n$  that are not used to reconfigure the entire system but just a known portion of it. The first bitstream is obviously a complete bitstream but the other functionalities are downloaded to reconfigure just portions of the architecture, as proposed in Figure 6. With such a scenario the reconfiguration time of a portion of the FPGA is hidden by the computation of the remaining part. According to this last statement it is easy to see that an important component is still missing in the model proposed in Figure 5 and Figure 6. In order to be able to hide the reconfiguration time it is not only necessary to partition the FPGA to obtain the ability to compute partial reconfiguration bitstream, but it is also necessary to guarantee that a reconfiguration is not going to imply a standby in the computation of the not-involved logic of the FPGA. Such a scenario brings to the definition of Dynamic Partial Reconfiguration.

Figure 5. Partial reconfiguration scenario

Dynamic partial reconfiguration is performed when the device is active. Except during some inter-design communication, certain areas of the device can be reconfigured while other areas remain operational and unaffected by the reprogramming. Up to now reconfiguration has been defined from the area and the time prospective, but there is still an important factor that can be used to classify a reconfigurable approach: the location of the controller of the reconfiguration. External reconfiguration implies that an active array may be partially reconfigured by an external device such as a Personal Computer, while ensuring the correct operation of those active circuits that are not being changed. Self or Embedded Reconfiguration extends the concept of dynamic partial reconfigurability. It assumes that specific circuits

Figure 6. Partial reconfiguration example

on the array are used to control the reconfiguration of other parts of the FPGA. Clearly the integrity of the control circuits must be guaranteed during reconfiguration, so by definition self-reconfiguration is a specialized form of dynamic reconfiguration (28). An important feature in FPGA architectures is the ability to reconfigure not only all the device but also a portion of it while the remainder of the design is still operational. Once initially configured, self-reconfiguration requires an internal reconfiguration interface that can be driven by the logic configured on the array. Starting with Xilinx Virtex II parts, this interface is called the internal configuration access port, ICAP (29). These devices can be configured by loading application specific data into the configuration. The number of frames and the bits per frame are different for the different devices of the Virtex II family. The number of frames is proportional to the CLB width of the device.

### 3.2 Reconfigurable architectures

In a dynamic partial reconfiguration scenario, reconfigurable architectures aims to organize the reconfigurable space and provide an external interface employed for the communication with general purpose processors and more in general RHOS. In this section the most popular reconfigurable architectures are presented :

- block reconfigurable architectures

- pipeline reconfigurable architecture

#### 3.2.1 Block reconfigurable architecture

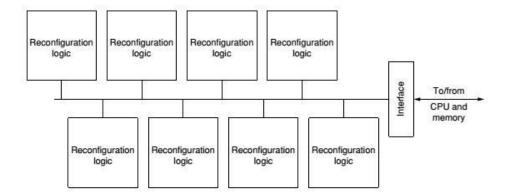

It follows a summary about block reconfigurable architecture from (10):

Block reconfigurable architectures rather than providing one large reconfigurable fabric, they are made up of multiple discrete blocks that can be used independently. Each block is named *reconfigurable slot*. In this case, each slot can contain many logic resources. An individual configuration may occupy one or more slots, but slots may not be subdivided between configurations. Blocks are connected either through a crossbar structure (30) or a bus/network (31), as shown in Figure 7. Although this would seem to describe any architecture formed from multiple connected FPGAs or FPGA cores, block reconfigurable devices have the ability to relocate configurations to different blocks at run time. Relocation is a technique that manipulate the bitstream for a block so that it is suitable for every other block. It is useful because when a module is designed, it can be implemented only for a specific block so that design phase is shorter and the number of bitstreams is smaller. For this reason, the slots of reconfigurable logic, in this style of architecture, have also been referred to as swappable logic units (SLU) (32). In the SLU architecture, a block reconfigurable design is implemented as an abstraction layer on top of a partially reconfigurable architecture to facilitate run-time relocation.

A heterogeneous multiprocessor may fit the block reconfigurable model, provided multiple blocks of reconfigurable hardware are present and configurations can be relocated between the blocks for computational flexibility. These architectures may contain a single communication network used by the configurable blocks and other resources such as microprocessors and custom circuitry. Although the Pleiades reconfigurable architecture (33) has some of these features (a heterogeneous multiprocessor with multiple reconfigurable blocks), computations are preassigned to specific resources, violating one of the requirements of the block reconfigurable category. Finally, despite the creation of a static hardware interface between software and reconfigurable hardware, this architecture does not introduce any benefit to deal with reconfiguration time overhead.

Figure 7. A typical implementation of a block reconfigurable architecture

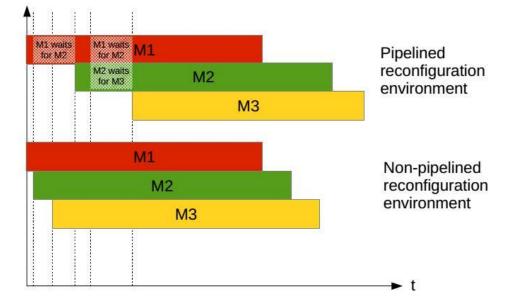

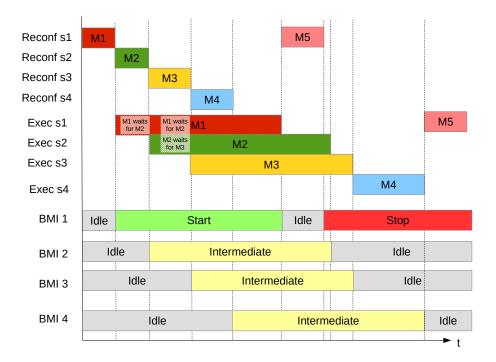

### 3.2.2 Pipelined reconfigurable architecture

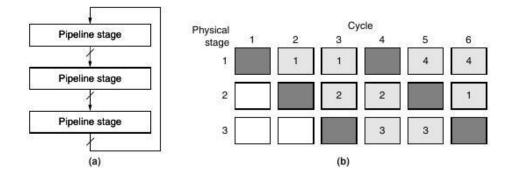

It follows a summary about pipelined reconfigurable architecture from (10):

Pipeline reconfigurable arrays use a series of physical pipeline stages to implement the virtual pipeline stages of configurations. A virtual pipeline stage can be relocated to any physical pipeline stage, and the number of virtual stages is generally not constrained by the number of physical stages. The most well-known pipeline reconfigurable architecture is PipeRench (34), which is designed to implement deeply pipelined configurations, subdivided into a set of virtual pipeline stages. At run-time, the virtual pipeline stages are assigned to physical pipeline stage computation units. These units are arranged in a unidirectional ring, as shown in Figure 8(a). Although pipeline stages may be implemented in different physical locations over time, the virtual pipeline appears fixed to its own pipeline stages, with each stage receiving input from its predecessor and generating output to its successor. As execution proceeds, configuration proceeds too so that proper computations are always guaranteed. Pipeline reconfiguration eliminates many of the difficulties of using reconfigurable hardware as virtual hardware, moreover it copes with reconfiguration time because it allows to run execution and reconfiguration concurrently. However, it places restrictions on the circuits that can be implemented as information can only propagate forward through the pipeline stages, and any feedback connections must be completely contained

Figure 8. A pipeline reconfigurable architecture with three physical stages (a). A 3-stage physical pipeline implementing a 4-stage virtual pipeline (b). Numbers within physical pipeline stages indicate the implemented virtual pipeline stage. Shaded stages are reconfiguring for the given cycle.

within a single stage. Finally, PipeRench is implemented in a custom reconfigurable fabric, so that FPGA implementation is not possible. Moreover, this architecture does not provide any interface for reconfigurable hardware and software. Figure 8(b) shows a 4-stage virtual pipeline implemented on a 3-stage physical architecture.

### 3.3 Hybrid reconfigurable systems

Recently, hybrid reconfigurable systems have captured the attention of embedded system designers. A hybrid reconfigurable system is a reconfigurable system composed of reconfigurable hardware and processors, so that it is to be preferred for several reasons. First of all, reconfigurable hardware offers flexibility and better performance than software, in terms of computational time, area and power consumption. Secondly, as stated in (35):

> FPGAs can reduce the chip count by serving as the glue logic as well as incorporating other pieces of the system. There is a wide range of available

soft and hard IP cores, including microprocessors, that allows you to pull all these functions into a single chip.

Microcontroller core can be integrated on the silicon or the designer can pour soft IP into free gates and tailor a microcontroller's size and functions to the application at hand (36), (37), (38). Finally, FPGAs vendors are supporting designers needs introducing into the market hybrid architectures composed of high performance processors and reconfigurable hardware (39).

Typically, not all of system functionality needs to be implemented by the reconfigurable fabric. Only those parts of the computation that are time-critical and contain a high degree of parallelism need to be mapped to the reconfigurable fabric, while the remainder of the computation can be implemented by a standard instruction processor. However, in a hybrid reconfigurable system, in order to meet time and power constraint and to improve the quality of service, the designer can decide to implement a task in both software and hardware In this scenario, hardware and software are merged together. As the system is running, an intelligent unit, according to run-time conditions and resources employment, can decide whether application are executed by a processor or by means of a reconfigurable unit.

#### 3.3.1 Hybrid system-level architectures

Hybrid system-level architectures have been deeply analyzed by Todman et al. (1):

A reconfigurable system typically consists of one or more processors, one or more reconfigurable fabrics, and one or more memories. Reconfigurable systems are often classified according to the degree of coupling between the reconfigurable fabric and the CPU. Compton and Hauck (40) present the

Figure 9. Five classes of reconfigurable systems: a) External stand-alone processing unit; b) Attached processing unit; c) Co-processor; d) Reconfigurable functional unit; e) Processor embedded in reconfigurable fabric.

four classifications shown in Figure 9a-d. In Figure 9.a, the reconfigurable fabric is in the form of one or more standalone devices. The existing input and output mechanisms of the processor are used to communicate with the reconfigurable fabric. In this configuration, the data transfer between the fabric and the processor is relatively slow, so this architecture only makes sense for applications in which a significant amount of processing can be done by the fabric without processor intervention. Emulation systems often take on this sort of architecture (41), (42). Figure 9.b and Figure 9.c show two intermediate structures. In both cases, the cost of communication is lower than that of the architecture in Figure 9.a. Architectures of these types are described in (34), (43), (44), (45), (46). Next, Figure 9d shows an architecture in which the processor and the fabric are very tightly coupled; in this case, the reconfigurable fabric is part of the processor itself; perhaps forming a reconfigurable sub-unit that allows for the creation of custom instructions. Examples of this sort of architecture have been described in (47), (48), (49). Figure 9.e shows a fifth organization. In this case, the processor is embedded in the programmable fabric. The processor can either be a *hard*core, or can be a *soft*core which is implemented using the resources of the programmable fabric itself. A summary of the above organizations can be found in Figure 10. Note that the bandwidth is the theoretical maximum available to the CPU Organization (a) is by far the most common, and accounts for all commercial reconfigurable platforms.

| Class                       | CPU to memory<br>bandwidth, MB/s | Shared<br>memory size | Fine grained or<br>coarse grained | Example application |

|-----------------------------|----------------------------------|-----------------------|-----------------------------------|---------------------|

|                             |                                  |                       |                                   |                     |

| processing unit             |                                  |                       |                                   |                     |

| RC2000                      | 528                              | 152 MB                | Fine grained                      | Video processing    |

| (b)/(c) Attached processing |                                  |                       |                                   |                     |

| unit/co-processor           |                                  |                       |                                   |                     |

| Pilchard                    | 1064                             | 20 kbytes             | Fine grained                      | DES encryption      |

| Morphosys                   | 800                              | 2048 bytes            | Coarse grained                    | Video compression   |

| (d) Reconfigurable          |                                  |                       |                                   |                     |

| functional unit             |                                  |                       |                                   |                     |

| Chess                       | 6400                             | 12288 bytes           | Coarse grained                    | Video processing    |

| (e) Processor embedded in   |                                  |                       |                                   |                     |

| a reconfigurable fabric     |                                  |                       |                                   |                     |

| Xilinx Virtex II Pro        | 1600                             | 1172 kB               | Fine grained                      | Video compression   |

Figure 10. Summary of system architectures

#### 3.3.2 An OS supporting hybrid architectures

Recently, reconfigurable system captured the attention in order to provide an efficient interaction between reconfigurable hardware and software. In particular, many efforts were addressed towards the management of the system. Researchers came up with a new concept, reconfigurable hardware operating system (RHOS) (4), (2), (50),(51).

What is stated in (52) is reported below:

The use of a fully-featured operating system introduces some fundamental advantages and enhancements, but also increases the SW complexity of the system, presenting new issues in resource management. One of the most important features an OS should provide is the exploitation of reconfigurable resources from different processes through multitasking and multiuser capabilities. Modern FPGAs have a reconfigurable area vast enough to allow mapping of a considerable number of IP-Cores, which might be made available to different processes at the same time, exploiting the intrinsic HW parallelism. Additionally, the OS must provide a completely free task-toresource mapping, similarly to what happens with normal HW resources (memory, IO interfaces) of the system. In (53) Wigley et al. have presented a discussion on the components of an operating system for a reconfigurable computer. These components are equivalent to the ones of a standard operating system. Instead of managing processes, they handle HW tasks, which are mapped on the reconfigurable hardware architecture.

BORPH is the first OS supporting FPGAs, here it is reported what it is explained in (2):

BORPH (2) is the first OS providing kernel support for FPGA applications by extending a standard Linux operating system. It establishes the notion of hardware process for executing user FPGA applications. Users therefore compile and execute hardware designs on FPGA resources the same way they run software programs on conventional processor-based systems.

In conventional OS terminologies, a process is usually defined as an executing instance of a program. It means that the software program represented by an executable file becomes a running process when it is executed. Each process is allocated its own unique process ID together with its executing environment. A process forms a parent-child relationship with its spawning process. BORPH extends this idea to reconfigurable computers, defining a hardware process as an executing instance of a gateware program. In other word, a hardware process is similar to a conventional software process except it may be executing on reconfigurable fabrics of the system instead of the main processor. The notion of execution domain of a process is therefore extended to include spatial information, such as the reconfigurable fabrics that this process is executing.

Scheduling reconfigurable applications is different from the traditional scheduling as reported in (53):

There are not obvious ways to preempt a hardware application due to the typical absence of the instruction fetch, decode, and, execute cycle. Thus there is no predefined point of completion in a reconfigurable application unless the designer specifically provides this.

For this reason the possibility to preempt a hardware process still needs an efficient solution and it remains an open question. Moreover, as mentioned previously, a scheduler of a reconfigurable system performs mapping and placement so that the operating system has to keep track of all the processes running in the system and which resources are associated to.

In fact, the operating system has to know which and where hardware modules are configured in the reconfigurable area and the time slice assigned to each software process. As a consequence, hardware modules can assume different states which have a physical association due to the possibility of configuring the same module in different places. The states hardware modules can assume are configuration, execution and cached state. In the configuration status, bitstream of hardware modules and input data are loaded. After the execution of a hardware process is completed, the respective hardware module is cached. This means that hardware module remains configured but there is no process associated to it, in other words, the module remains idle. It is obvious that the scheduler can decide to reconfigure a cached area, but it cannot reconfigure an area where computation is running. When the system is reset, a default configuration is loaded. At system reset the configured modules are assumed as cached.

Here the life-cycle of a hardware process is explained, focusing on what append at operating system level. As the scheduler has mapped a process to hardware, it must decide where to place the associate hardware module. At this point the monitor is updated associating both the hardware process and the hardware module to the chosen reconfigurable portion. If the module is not configured yet, that is the module is not cached, the hardware process is put into suspended processes list and configuration starts. On the contrary, if the module is cached, configuration step is not performed. As configuration finishes, input data are loaded, only if necessary. Then, the process is put into running processes list and computation begins. Next step is when execution is completed, the process is moved to finished processes list and the hardware module is cached.

# CHAPTER 4

# THE PROPOSED HARDWARE INFRASTRUCTURE : HI PROF

In this chapter a sophisticated hardware infrastructure for FPGA-based reconfigurable System on Chip is discussed. The goal is to create a flexible hardware architecture for reconfigurable systems. At first, the proposed architecture is analyzed into details, focusing on benefits and drawbacks. Guidelines for implementing tasks suitable for the proposed reconfigurable architecture are then provided. In particular, the process of designing hardware modules is treated deeply. Finally, interaction between reconfigurable hardware and the OS is discussed, introducing the concept of virtual reconfiguration.

### 4.1 The prposed architecture

Typically, a reconfigurable system is composed of four main components: the processor, the main memory, a reconfigurable hardware area and an infrastructure acting as interface between software and hardware. Software processes are executed on the processor, while IP-cores in reconfigurable area. Communication between hardware and software is usually achieved by means of a shared memory. A RHOS has the task of managing all tasks running dispatching them when needed on the reconfigurable device to off-load the main CPU.

The goal of this thesis is to improve the usage of reconfigurable hardware into hybrid systems by resorting to a flexible hardware infrastructure, HI PROF, aiming at:

- The reduction of FPGA reconfiguration time overhead exploiting a pipelined hardware infrastructure .

- The introduction for the first time in literature of the concept of Virtual Reconfiguration Space.

- Provide a set of guidelines for designers in order to develop IP-cores suitable for the proposed solution.

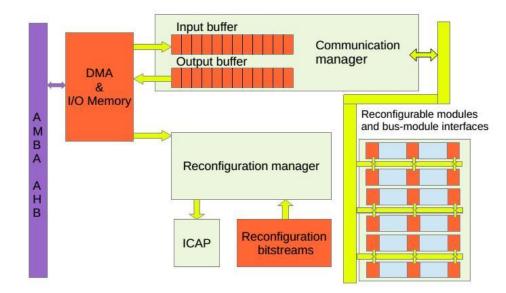

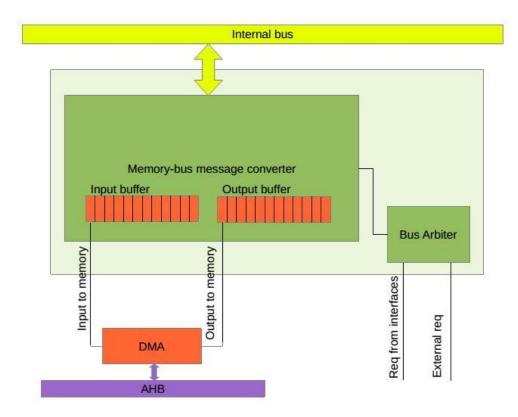

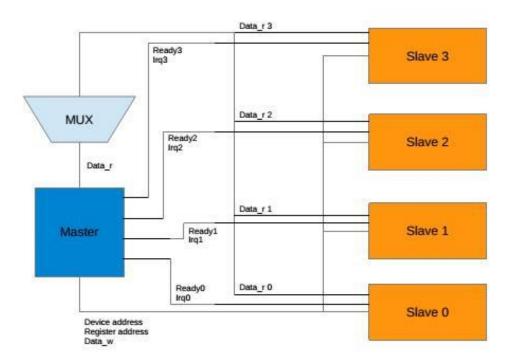

HI PROF is a Hardware Interface for Pipelined Reconfguration of FPGAs. HI PROF, as shown in Figure 11, consists of different blocks which have different functions. The main components are: the configuration manager, the communication manager and the bus-module interfaces. Configuration manager is responsible for reconfiguration, communication manager is responsible for communication among the main memory and the bus-module interfaces and bus-module interfaces are responsible for the data flow through the pipeline. Hereafter each module is presented in detail.

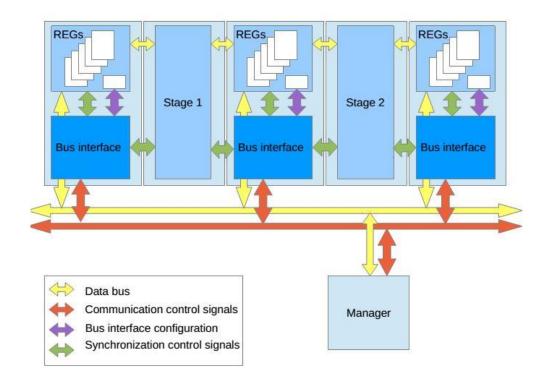

### 4.1.1 The bus-module interfaces

The heart of the proposed solution is the pipelined reconfiguration. In a pipeline reconfigurable scenario, the main task is divided into many sequential sub-tasks. Each sub-task is implemented as an IP-core (a sub-module). Sub-modules can be thought as independent modules that can be accessed every time they are needed or as a pipeline stage that provides partial results. In order to support a pipelined reconfiguration we have designed a sophisticated interface which has the task to manage data flow among reconfigurable modules instantiated

Figure 11. The structure of HI PROF