### Universal High-Frequency-Link Inverter for Renewable/Alternative Energy

BY

SIAMAK MEHRNAMI B.S., University of Tabriz, 2006 M.S., University of Tehran, 2009

## THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2015

Chicago, Illinois

Defense Committee:

Sudip K. Mazumder, Chair and Advisor Derong liu Sabri Cetinkunt, Mechanical & Industrial Engineering Tomy Sebastian, Halla Mechatronics Byeong Mun Song, Argonne National Laboratory This Dissertation is dedicated to my mother (Negar) who has always bestowed me with love, support and passion to work hard, and my father (Samad) who showed me the way in life, and my grandmother (Aziz) who raised me and my uncle (Iraj), who help me to make right decisions during my academic life. I would also like to appreciate my M.Sc. advisor (Dr. S. Farhangi) whose impact on my life has been invaluable and my memories of him will be everlasting.

### **ACKNOWLEDGMENTS**

First and foremost, my special thanks go to my PhD advisor Prof. Sudip K. Mazumder. I also acknowledge the support and assistance of my Committee Members. Professor Mazumder has been helping me and supporting my Dissertation work since 2011. Without his guidance, this Dissertation work would not be accomplished. I would also like to thank my lab mates specially Hossein Riaz Montazer, Alireza Tajfar and Alireza Mojab for their help and guidance during the course of my Dissertation work.

## **TABLE OF CONTENTS**

## <u>CHAPTER</u>

| I.   | INTF      | RODUCTION                                                                                                           | 1        |

|------|-----------|---------------------------------------------------------------------------------------------------------------------|----------|

|      | A.        | Background                                                                                                          | 1        |

|      | B.        | Power electronics interface (PEI)                                                                                   | 1        |

|      | C.        | Configurations of PEI                                                                                               |          |

|      | 1.        | Single-stage single-phase topologies                                                                                |          |

|      | 2.        | Three-phase PEI configurations                                                                                      |          |

|      | D.        | Motivation and objectives of this doctoral Dissertation                                                             | 11       |

| II.  |           | MODULATION SCHEME FOR SINGLE-PHASE DIFFERENTIAL MODE ĆUK                                                            |          |

| INV  | 'ERTE     | ER AND RESULTS                                                                                                      | 14       |

|      | A.        | DMCI                                                                                                                |          |

|      | B.        | Modulation of the DMCI                                                                                              | 16       |

|      | 1.        | Continuous modulation scheme (CMS)                                                                                  | 16       |

|      | 2.        | Discontinuous modulation scheme (DMS)                                                                               | 20       |

|      | C.        | Analysis of DMS and CMS                                                                                             | 25       |

|      | 1.        | Circulating power                                                                                                   |          |

|      | 2.        | Device rating                                                                                                       |          |

|      | 3.        | Distortion                                                                                                          |          |

|      | D.        | Experimental results                                                                                                |          |

|      | E.        | Nonlinearity Compensation of DMS based DMCI with Grid Connection                                                    |          |

|      | 1.        | SLDMS Scheme                                                                                                        |          |

|      | 2.        | SLDMS Sentine                                                                                                       |          |

|      | F. 2.     | Conclusions                                                                                                         |          |

| III. | MOE<br>A. | DULATION SCHEME FOR DIFFERENTIAL-MODE THREE PHASE ĆUK INVERTER<br>Differential-Mode Three-Phase Ćuk Inverter (DTCI) | 45<br>45 |

|      | В.        | Modulation Schemes for the Differential-Mode Three-Phase Ćuk Inverter (DTCI)                                        |          |

|      | 1.        | Continuous Modulation Scheme (CMS)                                                                                  | 46       |

|      | 2.        | Discontinuous Modulation Scheme (DMS)                                                                               | 50       |

|      | C.        | Analysis                                                                                                            | 54       |

|      | 1.        | Circulating Power                                                                                                   |          |

|      | 2.        | Device Rating                                                                                                       |          |

|      | 3.        | Distortion                                                                                                          |          |

|      | D.        | Non-linearity and closed loop                                                                                       |          |

|      | E.        | Experimental Results                                                                                                |          |

|      |           |                                                                                                                     |          |

| IV.  | CON       | CLUSIONS AND FUTURE WORKS                                                                                           | 83       |

|      | A.        | Conclusions                                                                                                         | 83       |

|      | B.        | Future Works                                                                                                        | 84       |

|      | APPI      | ENDIX                                                                                                               | 85       |

|      | REFI      | ERENCES                                                                                                             | 90       |

|      | VITA      | ١                                                                                                                   | 95       |

|      |           |                                                                                                                     |          |

# LIST OF FIGURES

| FIG | <u>URE</u> <u>PAGE</u>                                                                                                                                                                                                                                   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

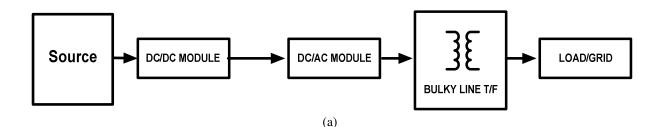

| 1.  | Possible configurations for PEI topologies4                                                                                                                                                                                                              |

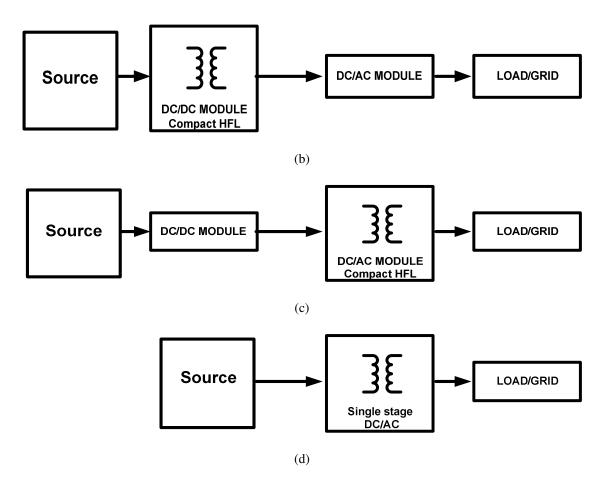

| 2.  | Topology of a differential-mode boost inverter [18]                                                                                                                                                                                                      |

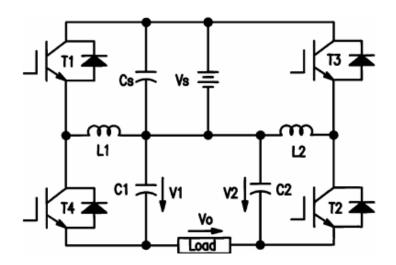

| 3.  | Topology of a differential-mode buck-boost inverter [19]                                                                                                                                                                                                 |

| 4.  | Topology of a differential buck-boost inverter[20]                                                                                                                                                                                                       |

| 5.  | Topology of a single-stage flyback inverter [21]7                                                                                                                                                                                                        |

| 6.  | Topology of modified single-stage flyback inverter [22]7                                                                                                                                                                                                 |

| 7.  | Topology of a single-stage full-bridge buck-boost inverter [23]8                                                                                                                                                                                         |

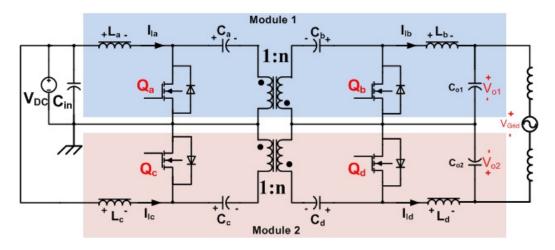

| 8.  | Topology of single-stage buck-boost PWM power inverter [24]9                                                                                                                                                                                             |

| 9.  | Topology of a transformerless voltage boosting inverter [25]9                                                                                                                                                                                            |

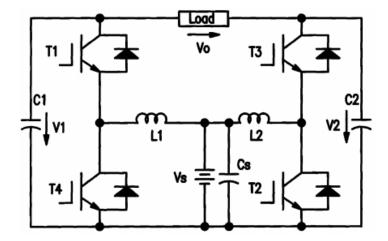

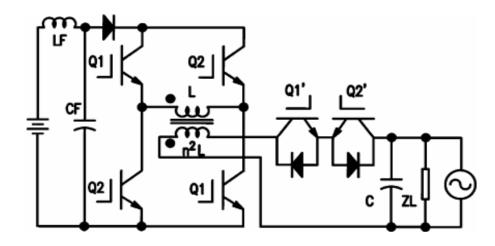

| 10. | Topology of a single-stage differential-mode Ćuk inverter [27], [28]10                                                                                                                                                                                   |

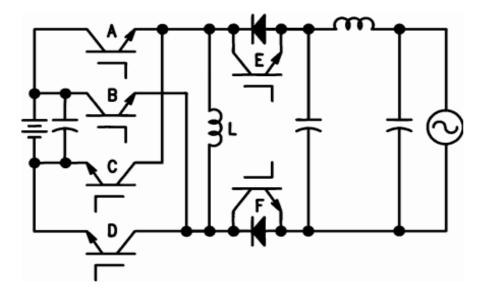

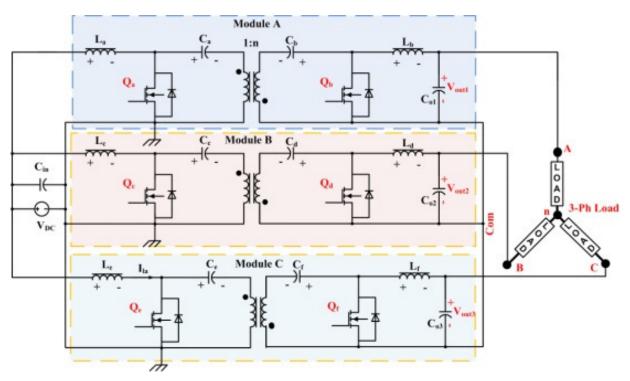

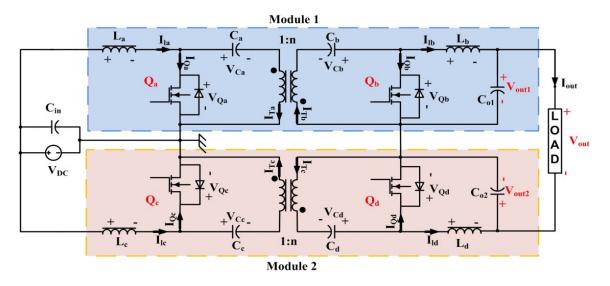

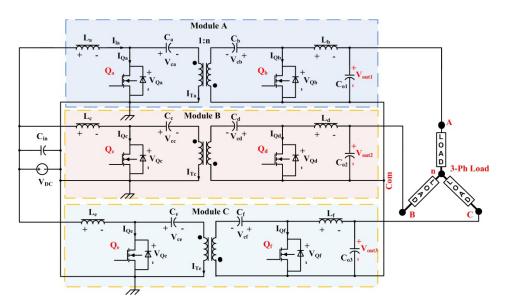

| 11. | Illustration of the DTCI topology, which comprises three modules (Module A, Module B and Module C)11                                                                                                                                                     |

| 12  | DMCI connected to the grid                                                                                                                                                                                                                               |

| 13. | Modes of operation of the DMCI with CMS                                                                                                                                                                                                                  |

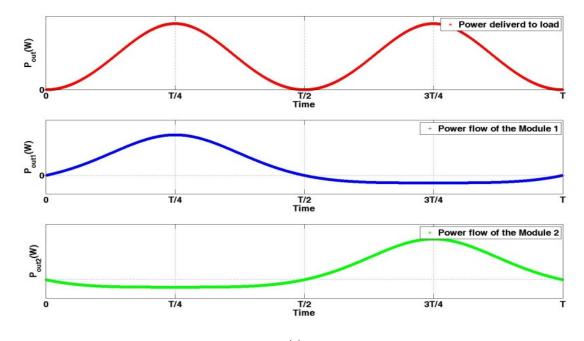

| 14. | (a) Illustration of realization of the CMS for the DMCI. (b) Illustration of the modulating signal, duty cycles of the switches Qa (Qd), output voltages (Vout1 and Vout2) of Modules 1 and 2, and output voltage (Vout) of the DMCI using the CMS       |

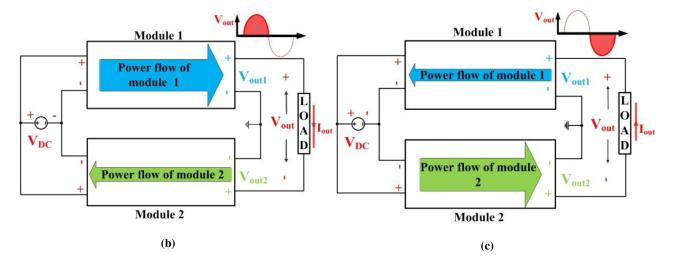

| 15. | (a) Instantaneous output powers of the DMCI and its two modules when the DMCI is operated using CMS. (b) and (c) Illustrations of power-flow mechanisms of Modules 1 and 2 during the positive and negative halves of a line cycle                       |

| 16. | Modes of operation of the DMCI using DMS                                                                                                                                                                                                                 |

| 17. | Illustration of realization of the DMS for the DMCI and the corresponding signals for modulation, switching, and output voltage.                                                                                                                         |

| 18. | (a) Instantaneous output power of the DMCI and its individual modules using DMS. (b) and (c) Mechanisms of power flow for the modules of the DMCI during the positive and negative halves of the line cycle24                                            |

| 19. | For Module 1, the ratio of the reactive (circulating) power to the active power for varying peak normalized dc-<br>voltage gain for the DMCI when the inverter is operated using CMS. The DMCI has no circulating-power<br>when it is operated using DMS |

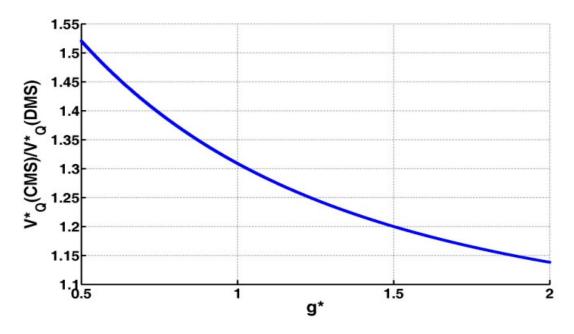

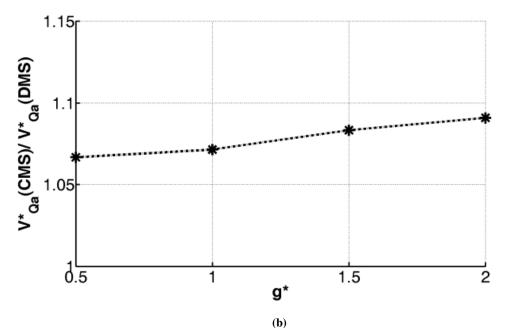

| 20. | VQa * (CMS)/VQa * (DMS) as a function of $g *$                                                                                                                                                                                                           |

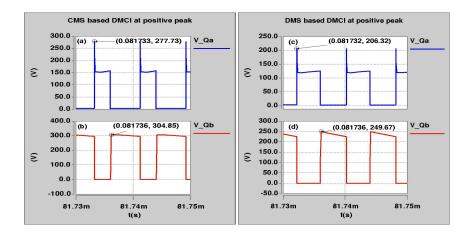

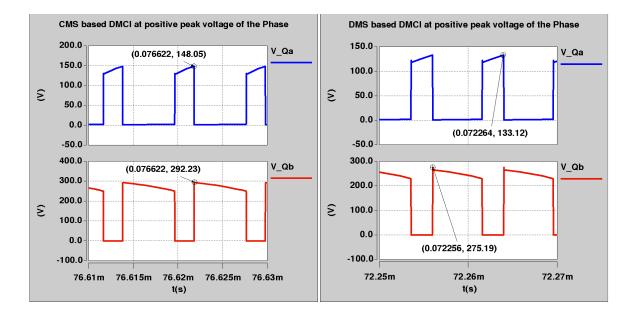

| 21. | Simulation results for $V_{Qa}$ and $V_{Qb}$ obtained using CMS and DMS when the output voltage attains maximum positive value                                                                                                                           |

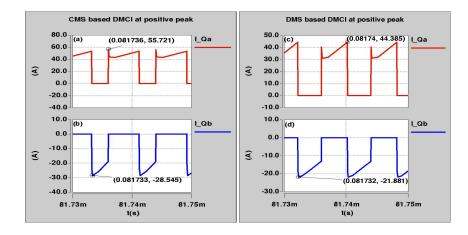

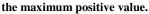

| 22. | Simulation results for <i>IQa</i> and <i>IQb</i> obtained using CMS and DMS when the output current attains maximum positive value                                                                                                                       |

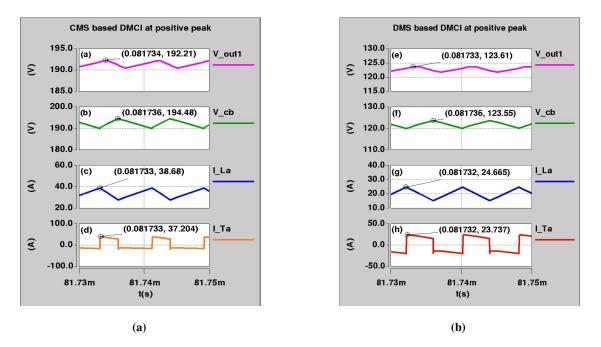

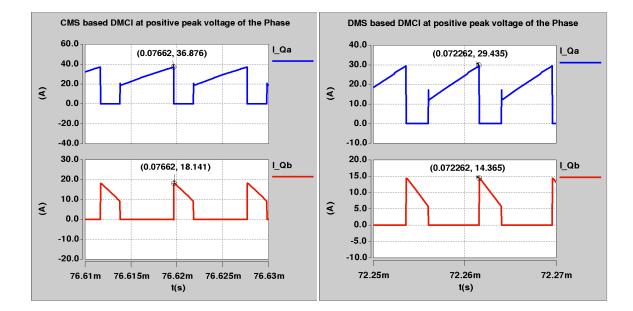

| 23. | Simulation results showing $V_{out1}$ , $V_{cb}$ , $I_{La}$ , and $I_{Ta}$ for the DMCI shown in Fig. 10 when the inverter is operated using CMS and DMS and when the output voltage attains maximum positive value                                      |

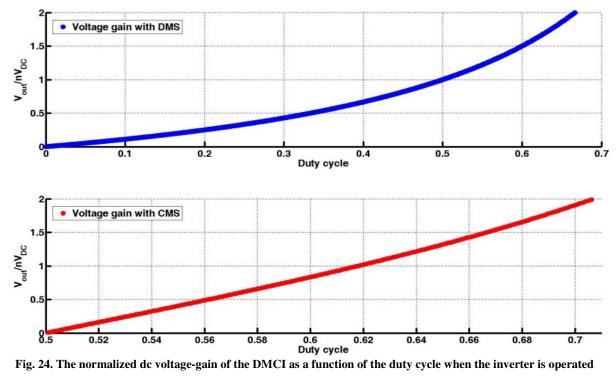

| 24. | The normalized dc voltage-gain of the DMCI as a function of the duty cycle when the inverter is operated using DMS and CMS                                                                                                                               |

# LIST OF FIGURES (continued)

| <u>FIG</u> | <u>URE</u> <u>PAGE</u>                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

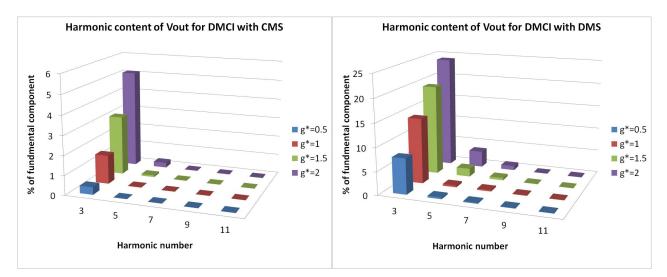

| 25.        | Harmonic analysis of the output-voltage distortion caused by the nonlinearity in the dc voltage gain of the DMCI operated with (a) CMS and (b) DMS. Magnitudes of the 3 <sup>rd</sup> , 5 <sup>th</sup> , 7 <sup>th</sup> , 9 <sup>th</sup> and 11 <sup>th</sup> harmonics are shown as a percentage of the magnitude of the fundamental-frequency component of the DMCI output voltage for different peak-voltage gains |

| 26.        | Experimental prototype of the DMCI. It shows the TMS320F28335 DSP based digital controller on the top feeding the DMCI power stage at the bottom                                                                                                                                                                                                                                                                         |

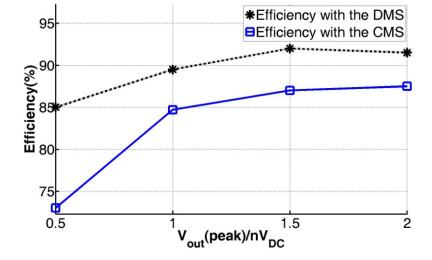

| 27.        | Experimental efficiency of the DMCI for varying normalized dc peak voltage gain obtained using DMS and CMS                                                                                                                                                                                                                                                                                                               |

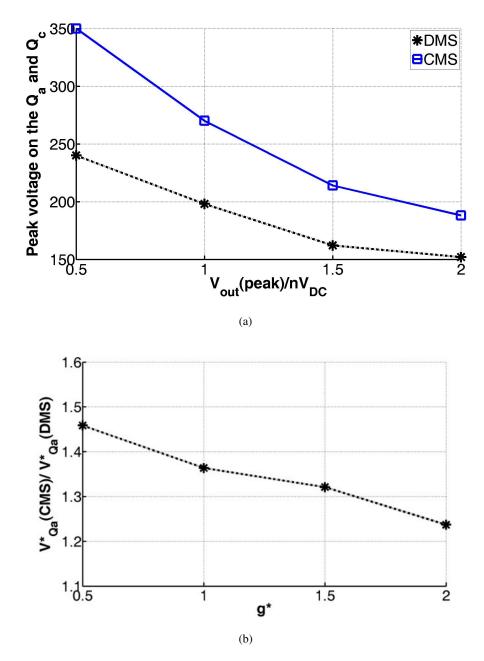

| 28.        | (a) Experimentally-determined peak voltage of the primary-side switches of the DMCI with CMS (solid line) and DMS (dotted line). (b) Ratios of the two traces in (a)                                                                                                                                                                                                                                                     |

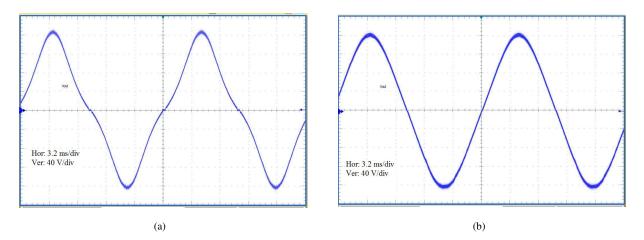

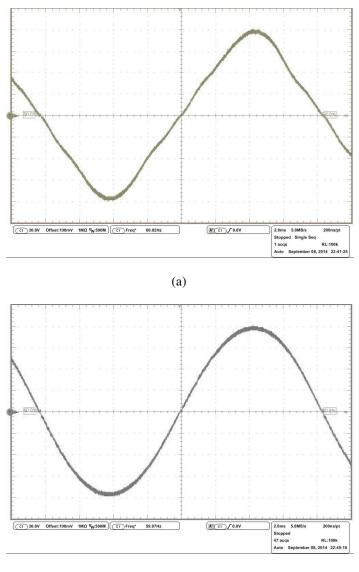

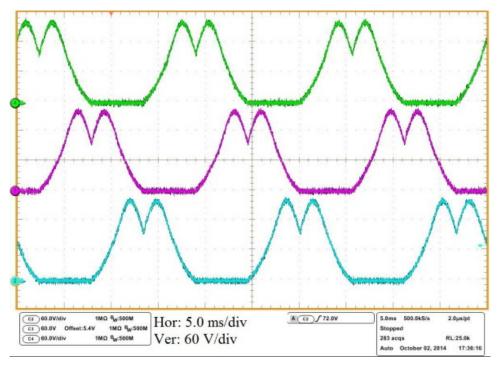

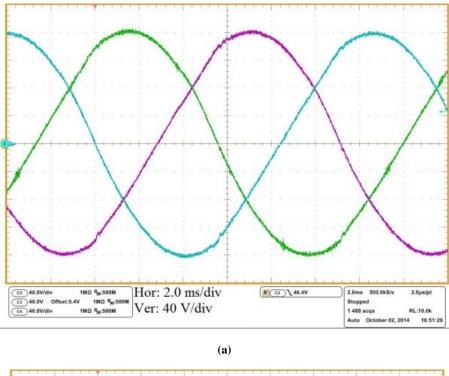

| 29.        | Experimentally obtained output voltage of the open-loop DMCI operated using (a) DMS (yielding a THD of 22%) and (b) CMS (yielding a THD of 4%). Horizontal scales for both the results are set 3.2 ms/div while corresponding vertical scales are set at 40 V/div                                                                                                                                                        |

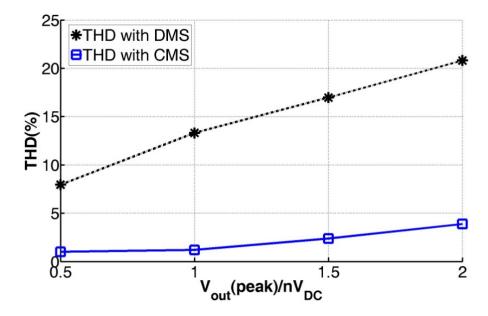

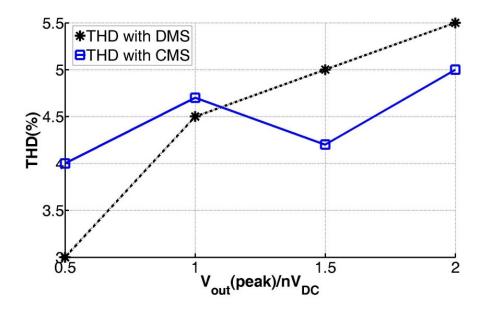

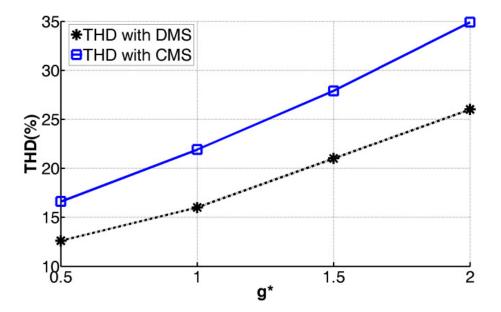

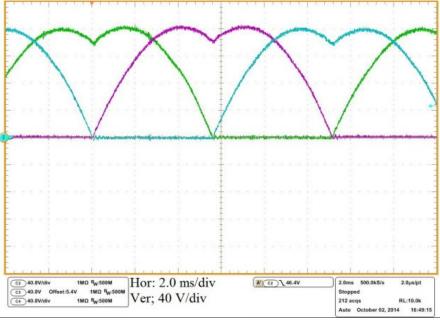

| 30.        | Experimentally obtained THD of the output voltage of the open-loop DMCI obtained using DMS and CMS as a function of the normalized dc voltage gain                                                                                                                                                                                                                                                                       |

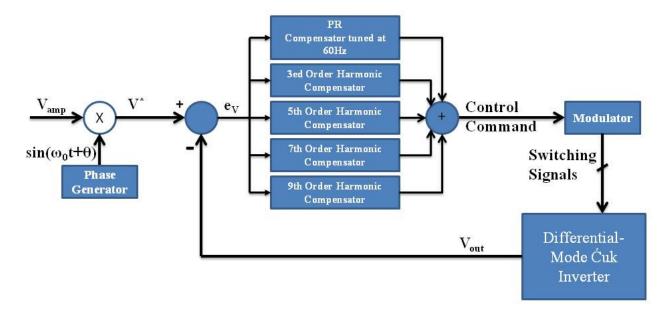

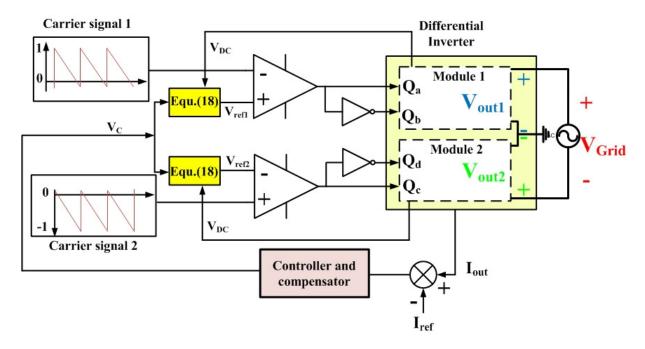

| 31.        | Architecture of the closed-loop controller for the DMCI                                                                                                                                                                                                                                                                                                                                                                  |

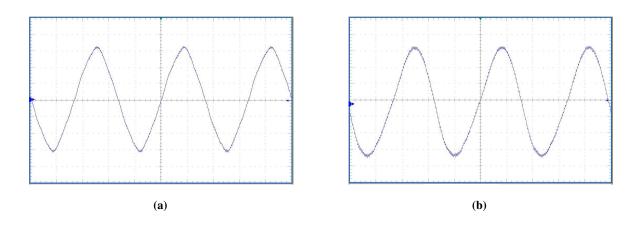

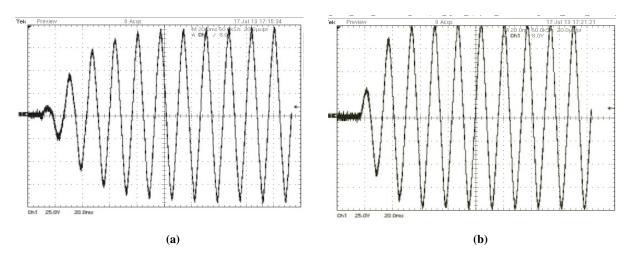

| 32.        | Experimentally obtained output voltage of the closed-loop DMCI operated using (a) DMS (yielding a THD of 5.5 %) and (b) CMS (yielding a THD of 5%). Horizontal scales for both results are set 5 ms/div while corresponding vertical scales are set at 50 V/div                                                                                                                                                          |

| 33.        | Experimentally obtained THD of the output voltage of the closed-loop DMCI operated using DMS and CMS as a function of the normalized peak dc voltage gain of the inverter. It shows a marked improvement in the THD of the closed-loop DMCI using DMS                                                                                                                                                                    |

| 34.        | Transient start-up response of the closed-loop DMCI when it is operated using (a) DMS and (b) CMS.<br>Horizontal and vertical scales for (a) and (b) are set at 20 ms/div and 25 V/div, respectively                                                                                                                                                                                                                     |

| 35.        | Realization method of the SLDMS                                                                                                                                                                                                                                                                                                                                                                                          |

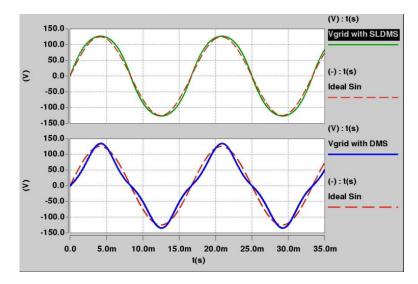

| 36.        | Comparison of the SLDMS and DMS with open loop SPWM                                                                                                                                                                                                                                                                                                                                                                      |

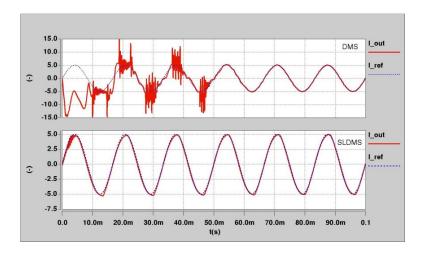

| 37.        | Startup current in grid connection mode with DMS and SLDMS                                                                                                                                                                                                                                                                                                                                                               |

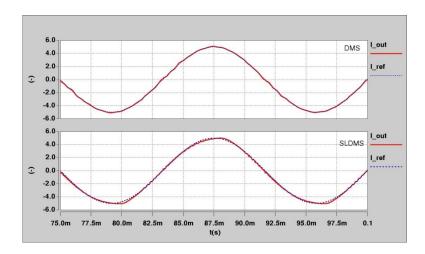

| 38.        | Injected current in grid connection mode at steady-state with DMS and SLDMS                                                                                                                                                                                                                                                                                                                                              |

| 39.        | Experimental output waveforms of DMCI with (a) DMS and (b) SLDMS. Horizontal axes are 2.0ms/div and Vertical axes are 30V/div                                                                                                                                                                                                                                                                                            |

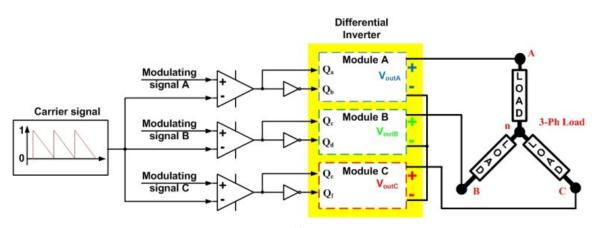

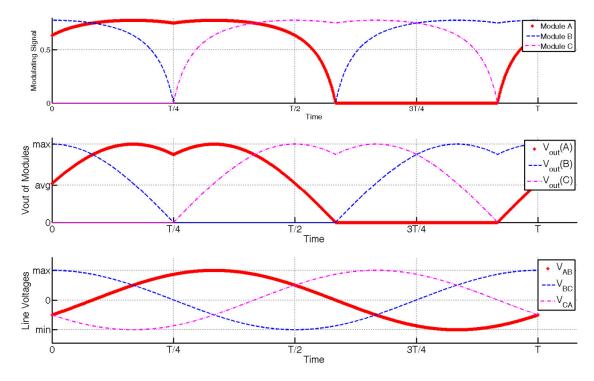

| 40.        | (a) Illustration of realization of the CMS for the DTCI. (b) Illustration of the modulating signal of the primary side switches (duty cycle), terminal voltages ( $V_{out1}$ , $V_{out2}$ and $V_{out3}$ ) of Modules A, B and C, and line voltages ( $V_{AB}$ , $V_{BC}$ and $V_{CA}$ ) of the DTCI using the CMS.                                                                                                      |

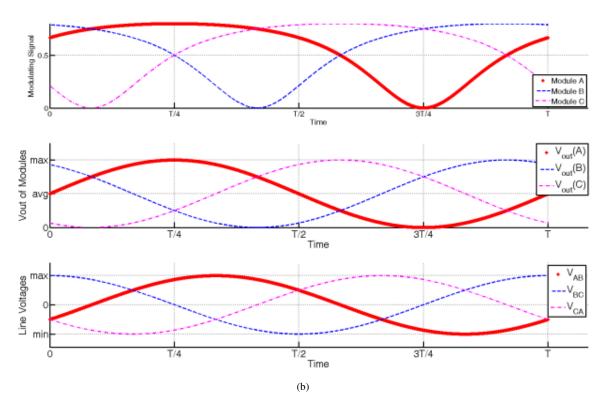

| 41.        | Instantaneous output powers waveforms of the DTCI when the DTCI is operating with CMS, and the piecewise power flow illustration of modules in half a line cycle                                                                                                                                                                                                                                                         |

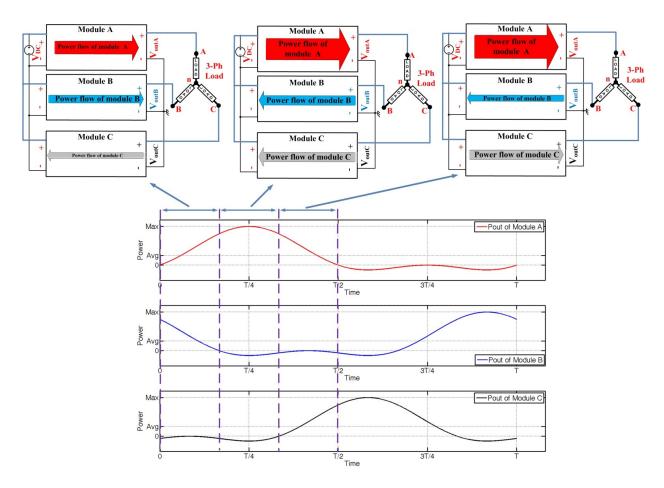

| 42.        | The three phases of the output terminal voltages of ideal DTCI assuming no offset. The yellow curve shows the minimum of the three phase voltages                                                                                                                                                                                                                                                                        |

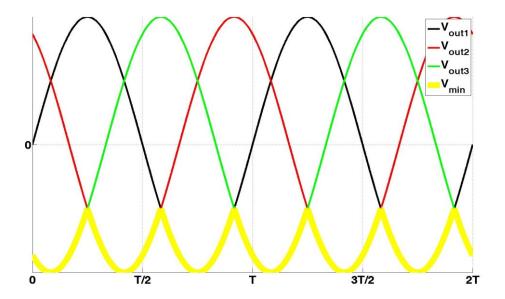

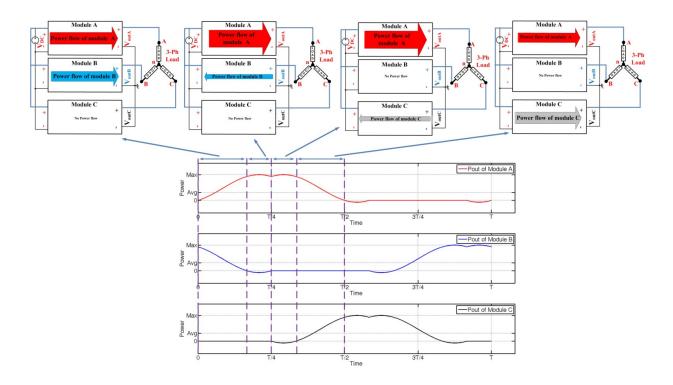

| 43.        | Illustration of the modulating signal (representing the duty cycle) of the primary side switches, terminal voltages ( $V_{out1}$ , $V_{out2}$ and $V_{out3}$ ) of Modules A, B and C, and line voltages ( $V_{AB}$ , $V_{BC}$ and $V_{CA}$ ) of the DMS-based DTCI                                                                                                                                                       |

| 44.        | Instantaneous output powers waveforms of the DMS-based DTCI, and the piecewise power-flow illustration of the three modules during the first half of a line cycle                                                                                                                                                                                                                                                        |

# LIST OF FIGURES (continued)

| <u>FIG</u> | <u>URE</u> <u>PAGE</u>                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

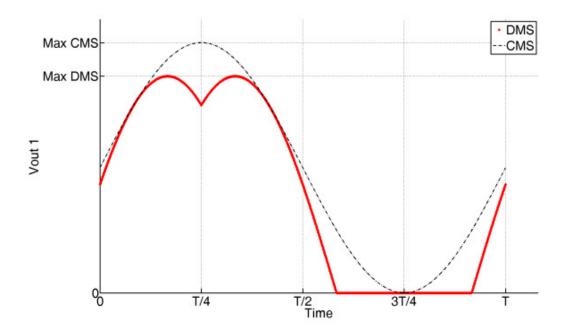

| 45.        | Comparison of the output terminal voltages of DTCI operating with CMS and DMS. The CMS-based DTCI results in higher peak for the output terminal voltage; even though the line voltage of the DTCI remains the same for both cases                                                                                                                                                                                         |

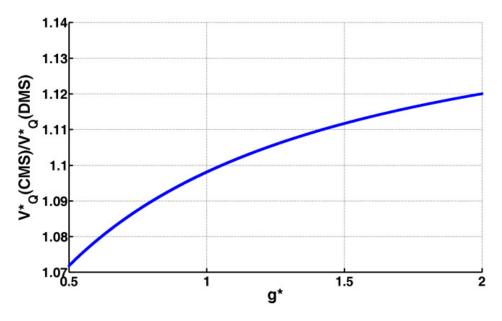

| 46.        | VQa * (CMS)/VQa * (DMS) as a function of $g *$                                                                                                                                                                                                                                                                                                                                                                             |

| 47.        | Simulation results for $V_{Qa}$ and $V_{Qb}$ obtained using CMS (left) and DMS (right) when the output voltage attains the maximum positive value                                                                                                                                                                                                                                                                          |

| 48.        | Simulation results for <i>IQa</i> and <i>IQb</i> obtained using CMS (left) and DMS (right) when the output current attains the maximum positive value                                                                                                                                                                                                                                                                      |

| 49.        | Simulation results showing $V_{outA}$ , $V_{cb}$ , $I_{La}$ , and $I_{Ta}$ for the DTCI shown in Fig. 11 when the inverter is operated using (a) CMS and (b) DMS and when the output voltage attains the maximum positive value60                                                                                                                                                                                          |

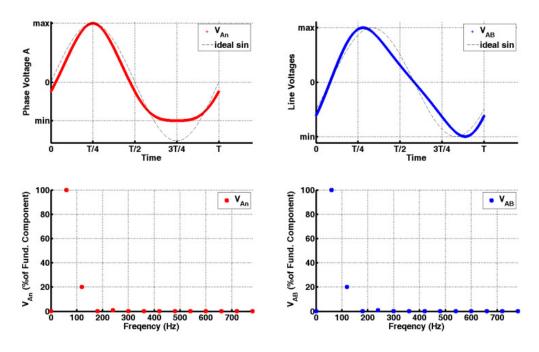

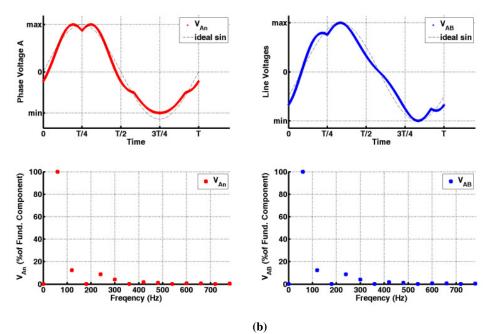

| 50.        | The phase voltage and line voltage of DTCI operating with (a) CMS and (b) DMS, and their normalized magnitude harmonics as a percentage of the magnitude of fundamental-frequency (60Hz) component                                                                                                                                                                                                                         |

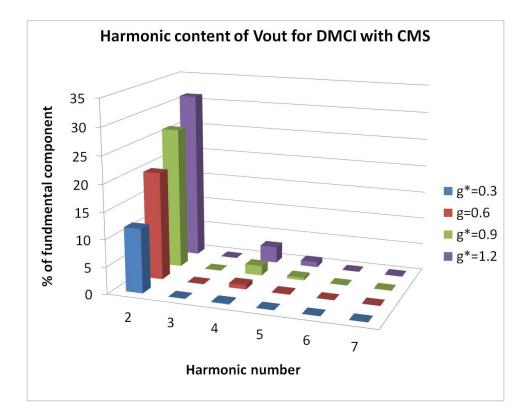

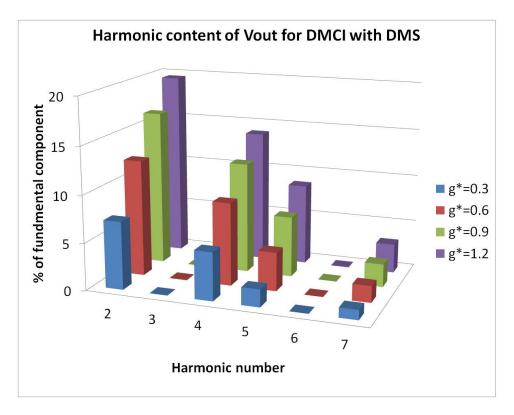

| 51.        | Harmonic analysis of the line-voltage distortion caused by the nonlinearity in the static voltage-gain of the DTCI operated with CMS (top) and DMS (bottom). Magnitudes of the 2 <sup>ed</sup> , 3 <sup>rd</sup> , 4 <sup>th</sup> , 5 <sup>th</sup> , 6 <sup>th</sup> and 7 <sup>th</sup> harmonics are shown as a percentage of the fundamental-frequency (60-Hz) component magnitude versus peak phase-voltage gain. 63 |

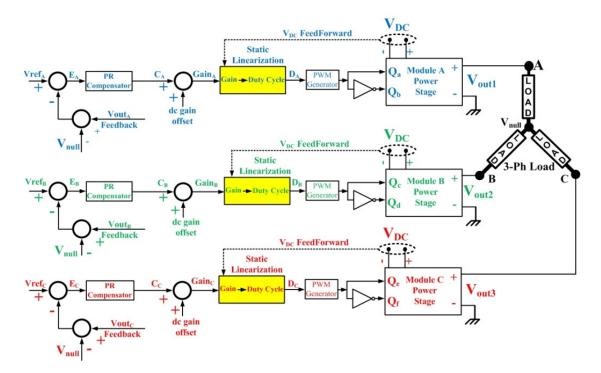

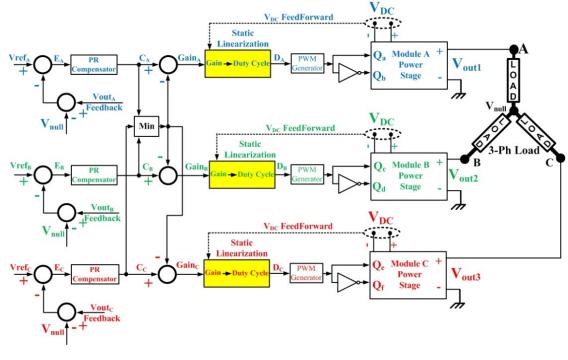

| 52.        | Proposed architecture of the closed-loop controller for DTCI operating with (a) CMS and (b) DMS67                                                                                                                                                                                                                                                                                                                          |

| 53.        | Experimental prototype of the DTCI. It shows the TMS320F28335 DSP based digital controller on the top right, three transformers in the middle, and primary side filter inductors and capacitors to the left                                                                                                                                                                                                                |

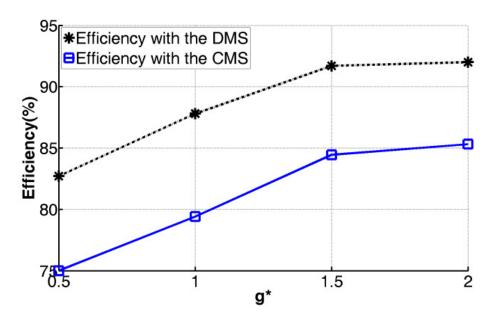

| 54.        | Experimental efficiency of the DTCI for varying normalized peak phase-voltage gain obtained using DMS and CMS                                                                                                                                                                                                                                                                                                              |

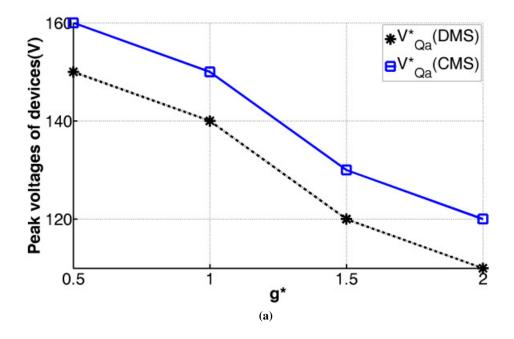

| 55.        | (a) Experimentally-determined peak voltage of the primary-side switches of the DTCI with CMS (solid line) and DMS (dotted line). (b) Ratios of the two traces in (a)                                                                                                                                                                                                                                                       |

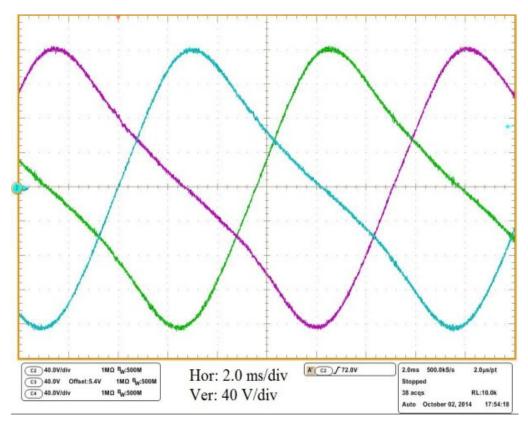

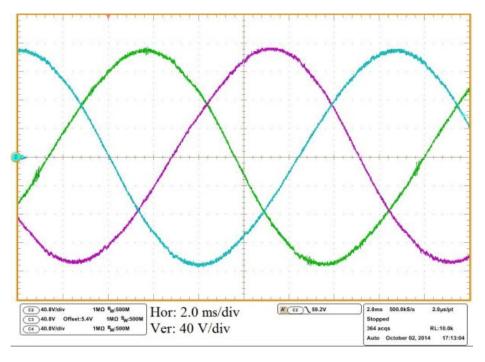

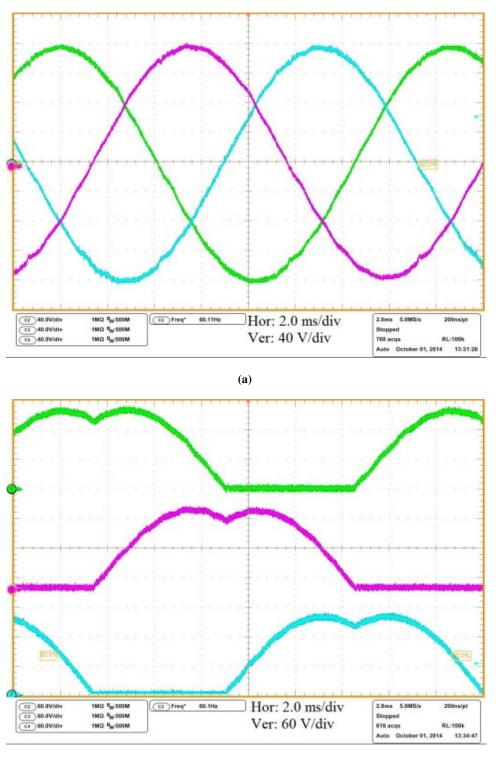

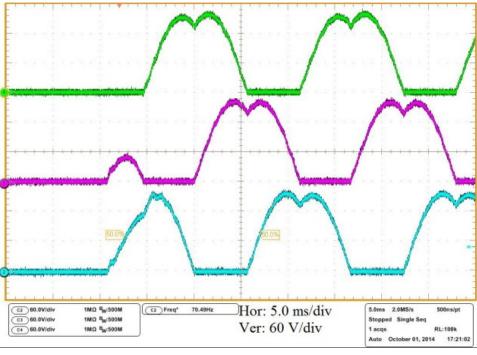

| 56.        | The open-loop (a) line-voltages and (b) terminal voltages of DTCI, operating with CMS. The inverter is excited with sinusoidal signals without SLB                                                                                                                                                                                                                                                                         |

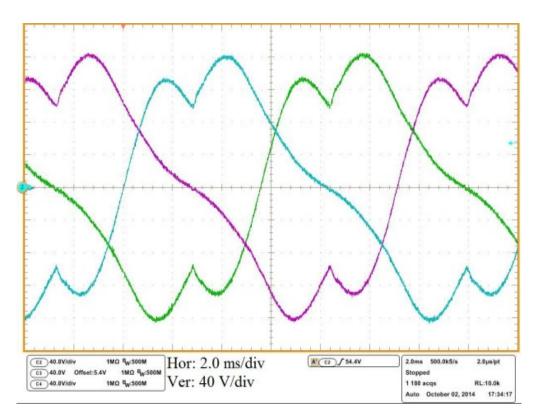

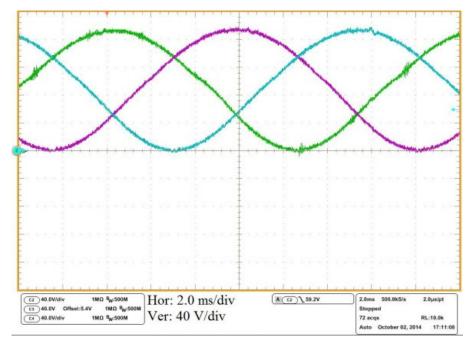

| 57.        | The open loop (a) line-voltages and (b) terminal voltages of DTCI, operating with DMS. The inverter is excited with sinusoidal signals without SLB                                                                                                                                                                                                                                                                         |

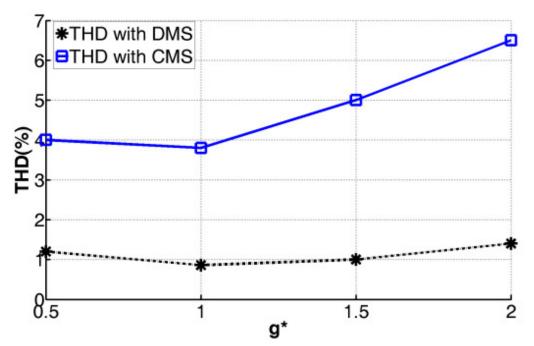

| 58.        | The line-voltage THD results for open loop DTCI without SLB operating with CMS (solid line) and DMS (dotted line), versus peak line-voltage gain                                                                                                                                                                                                                                                                           |

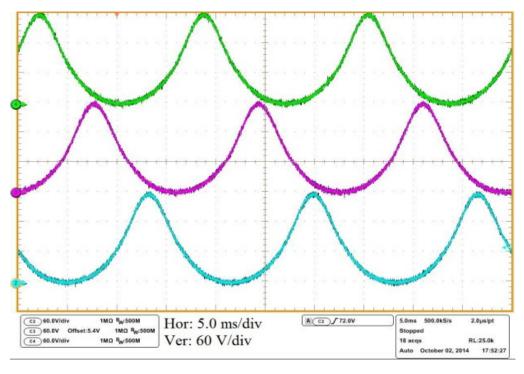

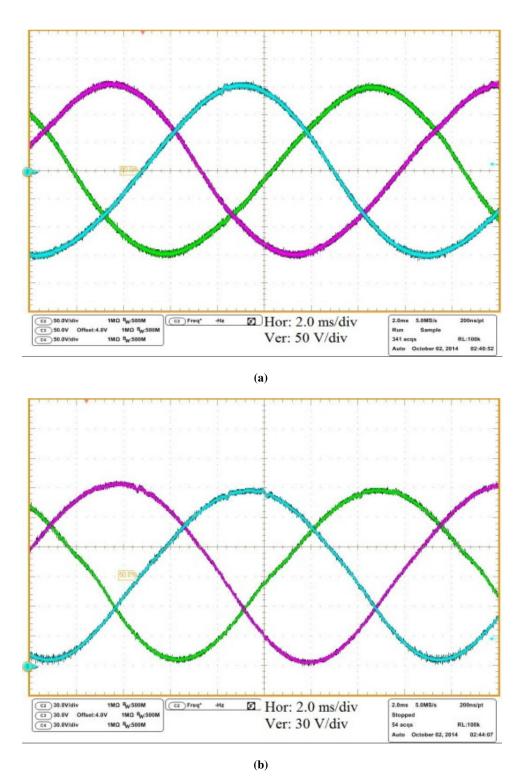

| 59.        | The open-loop (a) line-voltages and (b) phase-voltages of DTCI, operating with CMS. The inverter is excited with sinusoidal signals applied to SLB                                                                                                                                                                                                                                                                         |

| 60.        | The open loop (a) line-voltages and (b) phase-voltages of DTCI, operating with DMS. The inverter is excited with sinusoidal signals applied to SLB                                                                                                                                                                                                                                                                         |

| 61.        | The line-voltage THD results for the open-loop DTCI along with SLB. The DTCI operating with CMS is solid line and DMS-based DTCI is represented by dotted line, versus peak line-voltage gain. It shows a marked improvement in the THD of DTCI using SLB                                                                                                                                                                  |

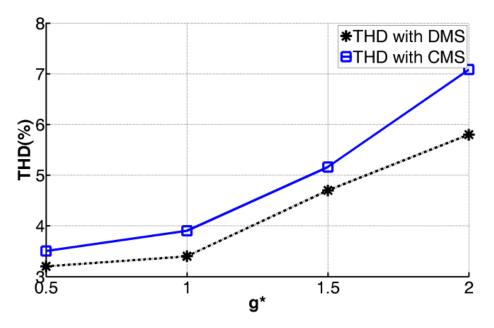

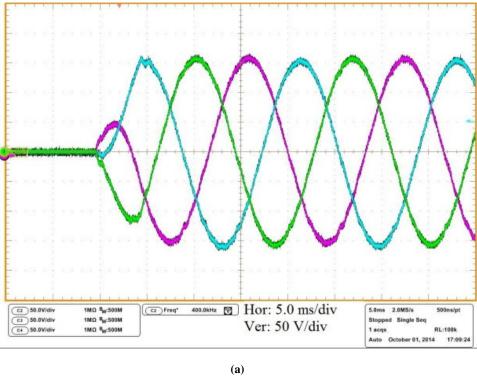

| 62.        | Experimentally-obtained closed-loop (a) line-voltages and (b) phase-voltages of DTCI, operating with CMS. The implemented control scheme is illustrated in Fig. 52(a)                                                                                                                                                                                                                                                      |

| 63.        | Experimentally obtained closed loop (a) line-voltages and (b) phase-voltages of DTCI, operating with DMS. The implemented control scheme is illustrated in Fig. 52(b)                                                                                                                                                                                                                                                      |

| 64.        | Experimentally-obtained THD of the line voltage as a function of the normalized peak line-voltage gain of the closed-loop DTCI when it is operated using DMS (dotted line) and CMS (solid line)                                                                                                                                                                                                                            |

# LIST OF FIGURES (continued)

| FIGURE                                                                                                 | PAGE |

|--------------------------------------------------------------------------------------------------------|------|

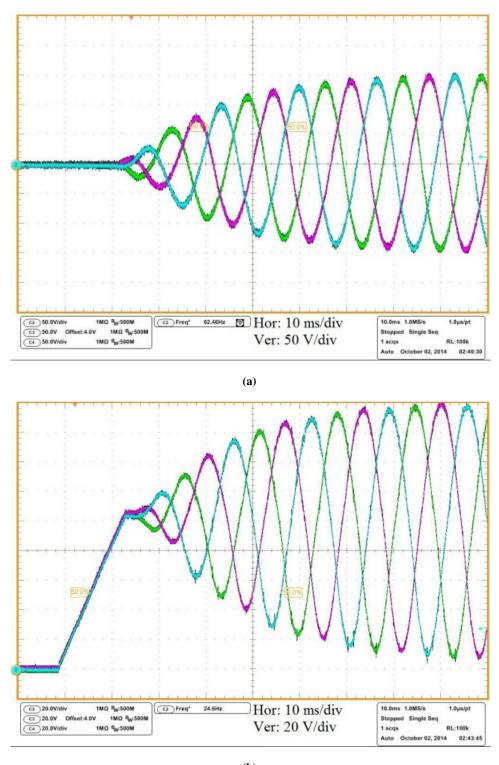

| 65. Experimentally-obtained start-up (a) line and (b) phase-voltages of the closed-loop CMS-base DTCI  | 81   |

| 66. Experimentally-obtained start-up (a) line and (b) phase voltages of the DMS-based closed-loop DTCI | 82   |

## LIST OF ABBREVIATIONS

- CMS Continuous Modulation Scheme

- DMCI Differential-Mode Ćuk Inverter

- DMS Discontinuous Modulation Scheme

- DTCI Differential-mode Three-phase Ćuk Inverter

- HC Harmonic Compensator

- HFL High-Frequency Link

- PEI Power Electronic Interface

- PR Proportional Resonant

- SLB Static Linearization Block

- THD Total Harmonic Distortion

#### **SUMMARY**

This Dissertation introduces new modulation schemes for single-phase differential-mode Cuk inverter (DMCI) and differential-mode three-phase Cuk inverter (DTCI) to improve inverter efficiency by reducing its circulating power.

The DMCI is a single-stage inverter with low device count. It offers advantages over other topologies because of compactness, higher power density, and reduced cost. It is a promising topology configuration for renewable-/alternative-energy applications encompassing both isolated and non-isolated configurations. The continuous modulation scheme (CMS), which was introduced originally for DMCI, activates all of the modules of the DMCI. The new discontinuous modulation scheme (DMS) deactivates one module in each half line-cycle leading to discontinuous operation of the inverter modules. Chapter 2 outlines the DMS and a mechanism to realize it. The experimental open-loop and closed-loop results of the DMCI using CMS and DMS are provided along with comparisons of their performances. It is shown that, the DMS reduces the circulating power and mitigates the losses of the DMCI, the voltage ratings of the devices of the DMCI are also reduced with the DMS. In contrast, the CMS-based DMCI exhibits wider linearity in its normalized dc-voltage gain and yields reduced harmonic distortion of the output voltage. For DMS, to achieve comparable linearity in normalized dc-voltage gain and distortion, harmonic compensation under closed-loop control is a pathway that has been demonstrated.

The DTCI is introduced in Chapter 3. The DTCI has some advantage over other differential-mode and threephase topologies, including fewer switches, bidirectional power flow capability, and galvanic isolation. It is a promising configuration for renewable-/alternative-energy applications with isolated as well as non-isolated structures.

The CMS, which was introduced originally for DTCI, activates all of the three modules of the DTCI. This modulation scheme increases the circulating power in modules and hence increases the inverter power loss. Chapter 3 introduces DMS for DTCI. DMS deactivates one module at a time resulting in a discontinuous operation of DTCI modules. It also outlines DMS and its implementation with a proper control mechanism. The proposed implementation of the DMS is straight forward. The experimental open-loop and closed-loop results of the DTCI using CMS and DMS are provided along with comparisons of their performances. It is shown that, the DMS reduces the circulating power and hence mitigates the losses.

## **SUMMARY** (continued)

The voltage ratings of the DTCI devices also are reduced with the DMS for the same reason. DTCI exhibits a nonlinear voltage-gain with both CMS- and DMS-based modulations. It has been demonstrated that by feed-forwarding the input voltage and incorporating a static linearization method, the harmonic distortion of the DTCI output is considerably reduced.

### INTRODUCTION

#### A. <u>Background</u>

Increasing cost of the energy and the environmental impact of the fossil fuels encourage the use of renewable energy [1]. The global consumption of electrical energy is increasing steadily in an ever-growing economy due to industrialization leading to a pressing need for an increase in the power generation capacity. Renewable energy sources offer the promise of clean, abundant energy gathered from resources such as sun, wind, earth, hydro power, geothermal, bio-fuels [2], [3]. Renewable energy technologies show promising benefits compared to those of the conventional energy sources [4]. Most of these systems are modular and have the flexibility for growth in energy consumption [2]. They are usually located close to consumer and they don't need long distance transmission line. The interface between a renewable energy source and consumer which is utility grid or a stand-alone load are power electronic interface (PEIs) such as dc/ac converters (or inverters) [5]. The major obstacles for expansion of renewable energies are their commercial cost and reliability. The PEI is an inseparable part of renewable energy industry and has a significant role in both cost and reliability of the whole system. Such interfaces control power to the load as well as optimize source (e.g. photovoltaic source) energy utilization. Also, considering the efficiency of the inverter as a critical parameter, the inverters show a key role in amount of the harvested and delivered power from the renewable energy sources to the application loads or the power grid. The inverter is also a considerable part of overall system cost [6]-[8]. All the above factors affect the overall cost energy generation from renewable energy sources. The inverter has a major effect on the reliability of the system as well. Experience with existing renewable energy sources indicate that inverters are often responsible for bottleneck system failures [9]. Along with advances in renewable/alternative energy sources, research in power electronics to achieve cheaper, efficient and reliable PEI is essential for development and expansion of cleaner energy sources in USA and globally.

## B. <u>Power electronics interface (PEI)</u>

The reliability, power density, cost, and efficiency are important for PEI designer and manufacturers for the renewable/alternative energy industry. Reliability can be enhanced by increasing the modularity of the PEI, reducing

the stresses in the components, reduced system complexity and by increasing the efficiency. Power density can be increased by decreasing the size of inductors, capacitors, and transformers by increasing the system frequency. It can be further increased by integrating the magnetics. Efficiency of the system is enhanced by reducing the conduction and switching losses of the system while the cost of the system is reduced by using fewer and cheaper components and by implementing modularity. So topology and operating frequency are the important factors, which essentially affect all of the above-mentioned parameters. This increases the scope of the PEI to be modified to suit the application. Few advantages of modularity are as follows: a) ease of system configuration and flexibility; (e.g. if the application requirements are three-phase, additional modules can be incorporated in the system to cater the needs of the consumer); and b) reduction in engineering and manufacturing cost and time. The frequency of the PEI also plays a major role to attain higher power density. Typically, the higher the switching frequency of a PEI, the smaller and lighter the magnetics and the capacitors embedded in the PEI. Further, the dynamic characteristics of the PEI improve with increasing switching frequency and so does the control-loop response and disturbance rejection capability.

## C. <u>Configurations of PEI</u>

Depending on the application need, PEI can be isolated or non-isolated. Isolation may be required due to safety or technical needs. For instance in a PV application, a non-isolated PEI causes leakage currents due to the presence of parasitic capacitances in distributed PV modules. With regard to interconnection, this is an important issue since it leads to safety, reliability, protective coordination, electromagnetic compatibility, and PV module lifetime issues [10]. Transformer-less (i.e., non-isolated) inverters show some advantages such as high efficiency and simple schematic [11], [12]. However, majority of these topologies are not able to provide isolation for PEI. Besides, ground current and noise issues make these topologies less attractive for distributed generation (DG). Finally, transformer-less inverter cannot adapt the voltage level of the energy source and the load. Therefore, they may not be suitable for energy sources with low output voltage such as photovoltaic and full-cell sources.

Galvanic isolation is normally implemented by a transformer. Line-frequency (LF) transformers are conventionally employed to provide galvanic isolation and voltage scalabilities for PEIs [13]–[15]. But, such low-frequency transformers are bulky and heavy. This also leads to an increase in the cost of manufacturing and maintenance of the LF transformers. Therefore, the LF transformers are the main obstacle to towards realizing PEIs and/or PEI-based systems with high power densities.

Advancements in power semiconductors devices and high-frequency magnetic cores [16], has enabled the usage of high-frequency (HF) transformers instead of the traditional LF transformers. Consequently, the power densities of the high-frequency-link (HFL) inverters [17] have increased multifold. Thus, HFL inverters provide the required galvanic isolation and voltage scalability while yielding reduced footprint. However, HFL inverters usually require more conversion stage (and hence more switches) than the conventional inverters, which results in higher switching losses. As such, the losses of the HFL inverters need to be decreased to increase the overall efficiency of the PEIs.

The isolated PEIs are implemented in multiple different ways as illustrated in Fig. 1. The architecture in Fig. 1(a) represents a conventional approach that requires bulky, expensive, and high-footprint LF transformer. The architectures shown in Fig. 1(b) and Fig. 1(c) incorporate the galvanic isolation using a HF transformer in the dc/dc or dc/ac stage. This yields high power density but increase the number of power stages. As such, for low power applications the single-stage architecture shown in Fig. 1(d) is a viable candidate. The direct power conversion (DPC) in this architecture also precludes the need for an intermediate dc-link capacitor.

Most configurations have a dc/dc power-conversion stage followed by a dc/ac power-conversion stage. The basic functions of the dc/dc converter are boosting and regulating the low output from the renewable energy source. Some basic criteria for choosing a dc/dc converter for a renewable energy source input are as follows: a) large step-up ratio, b) low input current ripple, and c) galvanic isolation between the source and the load. The dc/dc converters are either voltage-fed or current fed and can be either a half-bridge or a full-bridge topology. Half-bridge topologies are used for low- and medium-power applications while full-bridge topologies are typically used for higher-power applications. The voltage-fed converters require a high winding ratio between primary and secondary sides of the HF transformer since boosting action in voltage-fed converters is only performed by the transformer.

Fig. 1. Possible configurations for PEI topologies.

#### 1. Single-stage single-phase topologies

A single-stage inverter is an inverter that performs the power conversion from dc to ac- both stepping up the low dc voltage and modulating the sinusoidal load current and voltage, in a single stage. Many single-stage inverters, both isolated and non-isolated inverters have been proposed in the literature.

One of the single-stage topologies proposed earlier was the differential-boost topology [18]. This topology achieves dc-ac conversion by connecting the inputs of two identical dc-dc boost converters in parallel with a dc source and the load is connected across the outputs of the two dc-dc converters. As opposed to the conventional buck voltage-source inverters (VSIs), this topology can generate an output voltage higher than the input voltage. Fig. 2 shows the single-stage differential boost topology. The major advantages of this topology are the reduced number of switches and a simple topology. The disadvantages of the differential boost topology are : a) the topology is non-

isolated; b) the switches are operated at a low switching frequency; c) the size of the magnetics are large leading to a larger footprint for a non-isolated topology; d) there is amount of circulating power in circuit.

Fig. 2. Topology of a differential-mode boost inverter [18].

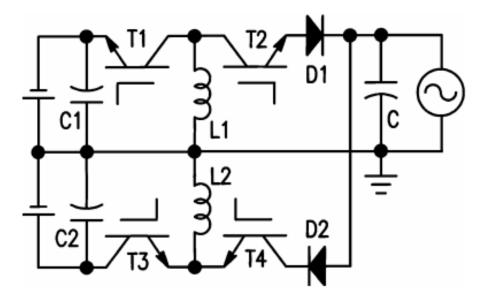

A differential buck-boost inverter, proposed in [19] is shown in Fig. 4. This operates similar to the differential boost inverter shown in Fig. 3. This inverter can produce an output voltage either higher or lower than the input dc voltage.

Fig. 3. Topology of a differential-mode buck-boost inverter [19].

Another single-stage buck-boost inverter topology, described in [20], is shown in Fig. 4. This topology overcomes the disadvantage of low input voltage range of the buck-boost topology proposed in [19]. But, this inverter requires a split input dc voltage source. Two sets of input voltage sources and buck-boost chopper type

circuits are connected in anti-parallel to the output capacitor, which generates the output topology. Both the chopper circuits are operated at fixed-frequency in discontinuous-conduction mode (DCM). Both the buck-boost topologies do not provide a HF galvanic isolation though they have lower component count. They also operate at a lower switching frequency and incur switching losses.

Fig. 4. Topology of a differential buck-boost inverter[20].

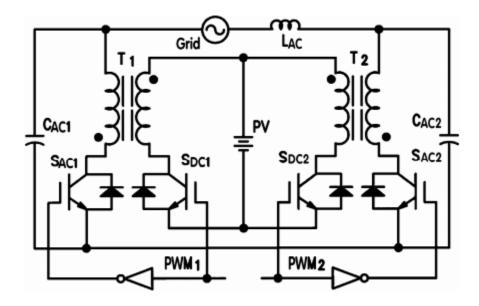

Fig. 5 shows the topology of a single-stage flyback inverter. In [21], two bidirectional flyback converters are connected in parallel to the input voltage source and the load is connected across the two converters. The main advantage of this topology over the above-mentioned topologies is the galvanic isolation provided by the HF transformers in both the flyback converters. But the galvanic isolation in this topology has increased foot print. The switches also incur switching losses and hence are limited to low-switching-frequency operation.

Reference [22] introduces a single-stage and single-phase inverter with three controlled devices (with two of them being high-side devices) and three diodes based on a modified flyback topology. It is shown in Fig. 6. This inverter can achieve ripple mitigation. However, the inverter does not have bi-directional power-flow capability.

Fig. 5. Topology of a single-stage flyback inverter [21].

Fig. 6. Topology of modified single-stage flyback inverter [22].

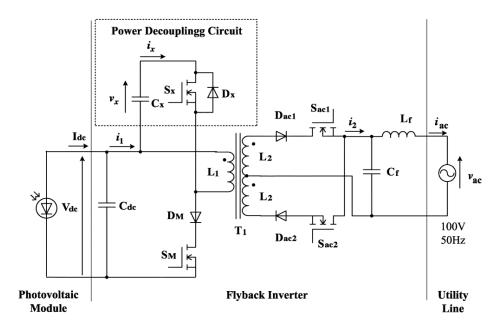

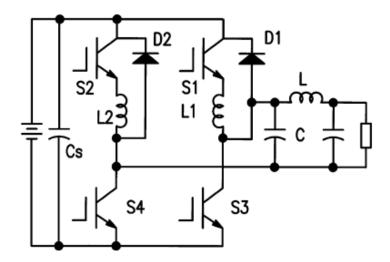

Fig. 7 represents a single-stage full-bridge buck-boost inverter outlined in [23]. This inverter has a full-bridge inverter with a LC resonant tank. The inverter has four main switches ( $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$ ), two diodes ( $D_1$  and  $D_2$ ), two resonant inductors ( $L_1$  and  $L_2$ ), one resonant capacitor (C), one filter inductor (L) and capacitor. The positive half-cycle at the output is generated with the switches  $S_1$ ,  $S_3$  and diode  $D_2$  and the negative half-cycle is generated

Fig. 7. Topology of a single-stage full-bridge buck-boost inverter [23].

with the remaining three devices. Though the inverter topology has only four power switches and two diodes, only two switches are soft switched. Also, the generated sinusoidal waveform consists of quasi sinusoidal pulse robes. This topology also does not isolate the source and the load or grid.

A single-stage buck-boost PWM power inverter proposed in [24] is given in Fig. 8. This inverter topology has two buck-boost choppers forming a four switch bridge and an additional two more power switches for synchronous commutation in each half cycle of the output. The major advantage of this topology is the galvanic isolation provided by the HF transformer. But, this topology is only suitable for low-power applications with a reported maximum power of 140 W.

Fig. 9 shows the topology of a transformer-less voltage boosting inverter proposed in [25]. This topology is a buck-boost derived topology and has six power switches and an energy storage inductor, *L*. This topology was proposed for low power applications. The ac output is synthesized by charging the inductor, L from different directions in each half cycle. This topology is highly compact without any huge magnetics but is only suitable for very low power applications (50 W). The absence of a galvanic isolation and the higher device for count for even low power applications are the major disadvantages of the topology.

The buck-boost derived topologies prevent direct connection between the source and the load, which is a key advantage. However, the main issue with the buck-boost derived topologies is the high peak inductor current stress due to the sudden transfer of energy through the inductors from source to load during each switching cycle. The buck-boost topologies also have lower boost capability when compared to the boost-derived topologies. The

Fig. 8. Topology of single-stage buck-boost PWM power inverter [24].

Fig. 9. Topology of a transformerless voltage boosting inverter [25].

differential-mode boost inverter demonstrated in [18] and the inverter proposed in [26] are free from the high inductor current stress but are non-isolated topologies.

Another single-stage converter based on a differential-mode Ćuk topology, is outlined in [27] and illustrated in Fig. 10. This topology achieves direct dc/ac conversion by connecting the load differentially across two bidirectional dc/dc Ćuk converters and modulating them sinusoidally with 180° phase difference. This topology utilizes only four main switches, making the inverter topology simple and yield reduced the cost. The differential-mode Ćuk inverter also has room for magnetics integration, thereby reducing the foot print of the inverter.

Fig. 10. Topology of a single-stage differential-mode Ćuk inverter [27], [28].

### 2. Three-phase PEI configurations

Many topologies have been introduced for three-phase inverters in literatures [29], [30]. A typical transformerless topology has a bridge architecture [31], [32]. This topology can be cascaded with boost converter on the dc side to achieve a peak gain higher than unity [33]. This topology may yield common-mode leakage current for some application [34]. For some other applications, higher peak voltage gains requirement may give rise to the need for a transformer. Given the need for low-cost inverter with galvanic isolation, HFL inverters have emerged as a potential front runner [35]–[40]. The simplest HFL topology often has a multi-stage topological architecture to accommodate the high-frequency transformer. The stages of multi-stage topology may be decoupled by a dc-link capacitor or dclink inductor [41]. That may add to system cost, reliability, loss, and power density. Slightly modified topologies have been presented [10], [12]. They remove the dc link capacitor/inductor by using special modulation techniques [14]–[16] while they may achieve reduction in switching loss. Overall, for low-power applications the cost-benefit tradeoff of a multi-stage HFL inverter topology requires careful attention. As such, for low-power three-phase HFL inverter applications, there is an enhanced thrust to seek single-stage topological solutions [42]–[45].

Single-stage topologies are categorized, reviewed and compared in [29]. References [46], [47] introduce inputseries-output-parallel topologies. Differential-modes single-phase Ćuk inverter is introduced in [48], and its design and modulation are presented by [28], [49]. Reference [46], [50] shows that topological embodiment of the differential inverter with Ćuk converter has some advantages. Reference [51] discusses the general concept of polyphase differential inverters and introduces the differential-mode three-phase Ćuk inverter (DTCI) topology

originally. The isolated DTCI as shown in Fig. 11. Reference [52] presents the DTCI control and design with continuous modulation scheme (CMS).

Fig. 11. Illustration of the DTCI topology, which comprises three modules (Module A, Module B and Module C).

#### D. Motivation and objectives of this doctoral Dissertation

One topological embodiment for the single-stage HFL inverter is the differential-mode Cuk inverter (DMCI) topology, shown in Fig. 10. The DMCI topology [27], [28] comprises two modules, which are connected in parallel at the dc side and connected in series at the ac side. The DMCI topology is promising one among the different topologies introduced in the Section 1. The DMCI yields several useful features [46] that directly impact the cost, reliability, and power density too. To begin, with the DMCI comprises limited number of switches all of which are low-side driven. Further, the DMCI has the ability to support bi-directional power flow using the same set of switches and a seamless control. Yet another feature of the DMCI is its ability to support voltage step-up and step-down functionalities that also enables the utility of the basic differential-mode topology for even non-isolated applications. An added capability of the DMCI is its ability to support LF ripple current without a large isolation transformer. Due to the presence of the two blocking capacitors on the primary and secondary sides of the transformer, the magnetizing current of the transformer is essentially devoid of any line-frequency current

component. Finally, the possibility of coupled inductors and transformer has been introduced in [48], which enhances the compactness of the inverter and leads to reduced input and output ripples. The modular structure of the each Ćuk converter can be used to extend the application to three-phase or even poly-phase systems, or multilevel inverters. The motivation of this research is to study and explore the possible modulation and controller schemes for single-phase and multi-phase structures of this converter, aiming to reduce the cost, losses and size.

This doctoral dissertation outlines a discontinuous modulation scheme (DMS) for a single-phase DMCI in Chapter 2 and presents an experimental realization of it for a single-phase DMCI. The experimental open-loop and closed-loop results of the DMCI using DMS are compared to those obtained using a conventional modulation scheme referred to as the CMS for various inverter performance and design parameters. It is shown that DMS reduces the circulating power and hence mitigates the inverter losses. The voltage ratings of the DMCI devices also reduce with this scheme. However, the CMS yields more linear behavior and causes reduced distortion. It is demonstrated in Chapter 2 that DMS results in a practically viable inverter; however, proper controller design and nonlinear and harmonic compensation are essential to avoid harmonic distortion of the output waveforms [49] and address nonlinearity in behavioral response [53].

Chapter 3 presents the isolated DTCI as shown in Fig. 11. The isolated DTCI topology comprises three modules, which are connected in parallel at the dc side and connected to common ground at the ac side. Three phase load is connected differentially to the positive terminal of each module. The DTCI yields several useful features [52] that directly impact the cost, reliability, and power density. The DTCI comprises limited number of switches all of which are low-side driven. Further, the inverter has the ability to support bi-directional power flow using the same set of switches and a seamless control. Yet another feature of the inverter is its ability to support voltage step-up and step-down functionalities that also enables the utility of the basic differential-mode topology for even non-isolated applications. An added capability of the HFL Ćuk inverter is its ability to support line-frequency ripple current without a large isolation transformer. Due to the presence of the two blocking capacitors on the primary and secondary sides of the transformer, the magnetizing current of the transformer is essentially devoid of any line-frequency current component. Finally, the possibility of coupled inductors and transformer has been introduced by [54], which enhances the compactness of the inverter and leads to reduced input and output ripples. The DTCI topology originally outlined with a continuous modulation scheme (CMS) [24] in which primary devices have three-phase sinusoidal modulating signals with a dc offset. The secondary side devices are complementary with respective

primary side switch and considering a proper dead time. The dc offset of the output terminal voltages cancel each other because the load is connected differentially across the output-voltage terminals. However, this modulation scheme leads to circulation of power or reactive power flow through modules even with resistive load. This yields higher switching and conduction losses. Further, the dc offset voltage on output terminals of modules increases the peak voltages on the devices [55].

There is hardly any discussion on the need for proper modulation scheme for DTCI in literatures [24], [25]. As such this Doctorate Dissertation outlines a DMS for the DTCI along with a description of the CMS in Chapter 3. Further, the chapter provides analytical insight into the performance comparison of DMS-based and CMS-based DTCI. The nonlinear behavior of DTCI leads to distortion of DTCI output operating with either CMS or DMS. A static linearization method with input voltage feed-forward is proposed to address the problem. It has been shown that by using this method, the total harmonic distortion (THD) is reduced significantly below the acceptable level. Closed loop control system is designed based on proportional resonant (PR) controller [56] and experimentally implemented. Chapter 3 also presents the experimentally obtained results of efficiency, device peak voltages, closed loop transient and THD. The experiments are carried out with proposed structures in the Dissertation for both CMS and DMS. These results verify the analytical/simulation results and show the significant superiority of DMS over CMS. Appendix outlines the design aspects of the experimental DTCI prototype.

# NEW MODULATION SCHEME FOR SINGLE-PHASE DIFFERENTIAL MODE ĆUK INVERTER AND RESULTS

### A. <u>DMCI</u>

Common single-phase inverters have two stages: 1) The dc-dc stage, 2) The dc-ac stage. The dc-dc converter usually boosts the input voltage. The second stage is usually an H-bridge inverter [57]. The two stages are connected through a decoupling dc-link. The galvanic isolation can be realized in two ways. One possible architecture is a bulky line-frequency transformer at the ac side and the other approach is the use of dc-dc converter with high-frequency transformer isolation.

The alternative topologies has been proposed [18]- [27], which can do the voltage step up and inversion within one stage. The details of these alternative topologies have been shown in previous chapter. A class of single-stage topologies developed by parallel-series connection of two dc-dc converters [46], which also known as differential inverters. The differential-mode inverters are modular and can be extended for three phase inverters as well [58]. The boosting function can be realized either by step-up transformer [59] or boosting capability of the converter. Among various dc-converters for differential mode configuration, the Ĉuk converter is advantageous [47] because it fulfills the following conditions:

1) Low number of switches, which leads to smaller size and robustness [60].

2) All switches are low side driven and it makes the design and the fabrication simpler and reduces the cost.

- 3) Bi-directional power flow capability simply achieved by using switch at both sides of the converter.

- 4) Buck-boost ability of the converter, so it can be used in transformer-less configuration.

5) The converter can be easily extended to have high frequency transformer with interstice rejection of line frequency components of the magnetizing current.

6) The possibility of coupled inductors and transformer which has been introduced in [48], [54], reduces the size further and gives less ripple on input and output, which means less EMI.

The differential-mode Ĉuk topology [48], [54] is single-stage inverter and composed of two modules. Each module is a single Ĉuk converter, which can be configured in both isolated and non-isolated structures. The two

modules are connected in parallel at the dc side and they are in series at the ac side as shown in with grid connection.

Fig. 12 DMCI connected to the grid.

The original DMCI topology [54] outlined switching of the inverter using a continuous modulation scheme (CMS), in which diagonal devices switch simultaneously and continuously. Reference [54] has mentioned that the structure could be used as switched mode power supply (SMPS), but it did not discuss anything about its modulation and control. The linearity between duty cycle and output voltage is essential for the power amplifiers, which are used in analog circuit design. The power loss is more important for SMPS rather than class B signal amplifier. This Scheme is proposed for a C-class switching power amplifier. In CMS, one module pulls the power while the other one pushes it. This leads to enhanced circulation of power yielding higher switching and conduction losses. Thus, it does not suit the SMPS application. Further, the continuous modulation of all of the switches implies that a control system for this inverter sees an eight-order dynamics under all operating conditions which has adverse implications of control complexity and bandwidth. References [46], [47] mention the discontinuous operation of the modules depending on voltage polarity, but they do not present anything about control or modulation scheme and its realization. Reference [60] introduces similar topology, which includes two additional switches. It demonstrates the standalone operation with one module at a time modulation and sliding mode control. Further, either of these two papers does not provide any insight into the performance comparison between DMS and CMS operation of the DMCI.

This chapter of dissertation outlines a discontinuous modulation scheme (DMS) for the DMCI along with a description of the CMS. It builds on the abridged work outlined in [49], [53] by the author. A detailed analysis on the performance of the DMCI operating with DMS as well as CMS is provided in the Section C based on theoretical and experimental results. The results indicate the positive impact of DMS on the DMCI with regard to efficiency and reduction in device breakdown voltage rating and the need for nonlinear closed-loop compensation in DMS to achieve satisfactory harmonic distortion and linearity in voltage gain.

### B. Modulation of the DMCI

#### 1. Continuous modulation scheme (CMS)

The output voltage  $(V_{out})$  of the inverter is the differential of the output voltages  $(V_{out1} \text{ and } V_{out2})$  of the two dcdc converter modules. This results in the following normalized dc-voltage gain relationship:

$$\frac{V_{out}}{n \times V_{DC}} = \frac{V_{out1}}{n \times V_{DC}} - \frac{V_{out2}}{n \times V_{DC}} = \left(\frac{D_1}{1 - D_1} - \frac{D_2}{1 - D_2}\right).$$

(1)

In (1),  $V_{DC}$  is the dc input voltage and *n* is turns ratio of the transformers. The duty ratios ( $D_1$  and  $D_2$ ) of Modules 1 and 2 (operating using CMS) are related by  $D_1 = 1 - D_2$ , so the normalized dc-voltage gain (*g*) in terms of  $D_1$  is described by the following:

$$g = \frac{V_{out}}{n \times V_{DC}} = \left(\frac{2D_1 - 1}{D_1(1 - D_1)}\right).$$

(2)

As will be demonstrated later, depending on n, CMS-based DMCI exhibits relatively linear normalized dcvoltage gain over a finite range of duty cycle.

For CMS, the diagonal switches (i.e.,  $Q_a(Q_b)$  and  $Q_d(Q_c)$ ) of the two modules are fed with the same gating signals while the two switches ( $Q_a(Q_b)$  and  $Q_c(Q_d)$ ) in each of the modules are fed with complementary gating signals. Because the inverter operates in a differential mode, the inductor currents flow from one Ćuk module to the

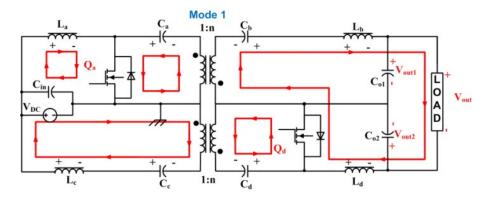

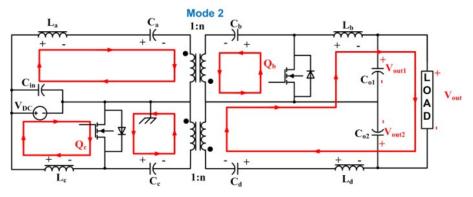

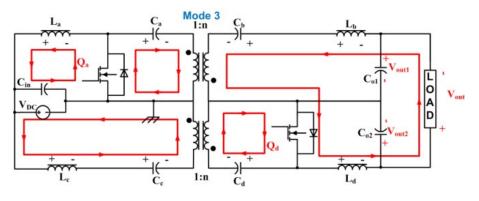

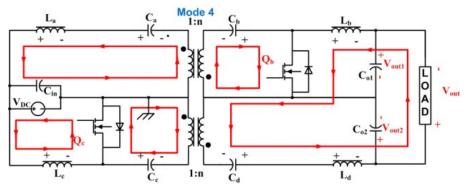

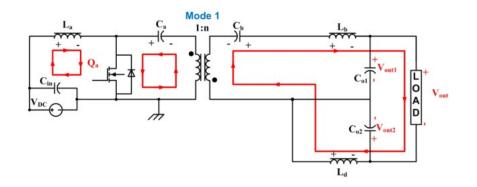

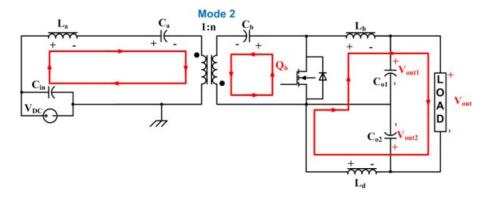

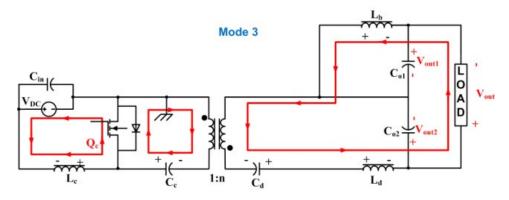

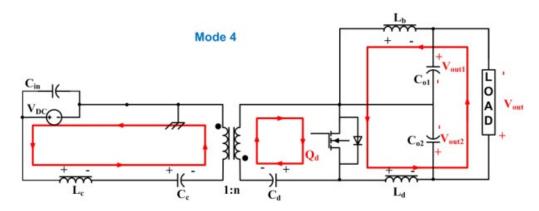

other. There are 4 modes in all. Modes 1 and 2 are for the positive half of the line cycle while Modes 3 and 4 are for the negative half of the line cycle. Fig. 13 illustrates the four modes of the inverter using CMS.

#### Fig. 13. Modes of operation of the DMCI with CMS.

In Mode 1, switches  $Q_a$  and  $Q_d$  are turned on while switches  $Q_b$  and  $Q_c$  are turned off. The current flowing through the input inductor  $L_a$  increases and the inductor stores energy. The capacitor  $C_a$  discharges through switch  $Q_a$  resulting in a transfer of energy from the primary to the secondary side of the top transformer. The energy stored in the capacitor  $C_b$  is discharged to the circuit formed by  $L_b$ ,  $C_2$ , and the load R. During this time interval, the inductor  $L_d$  stores energy leading to an increase in its current. The capacitor  $C_d$  discharges through switch  $Q_d$ . For Module 2, power flows from the secondary to the primary side. The capacitor  $C_c$  is discharged to provide the power. In Mode 2, switches  $Q_a$  and  $Q_d$  are turned off while switches  $Q_b$  and  $Q_c$  are turned on. Capacitors  $C_a$  and  $C_d$  and  $C_b$ and  $C_c$  are charged using the energy which was stored in the inductors  $L_a$  and  $L_d$  while switches  $Q_a$  and  $Q_d$  were on. During this time interval, inductors  $L_b$  and  $L_c$  release their stored energy. Finally, Modes 3 and 4 are similar to Modes 1 and 2 with the exception that the load current is negative.

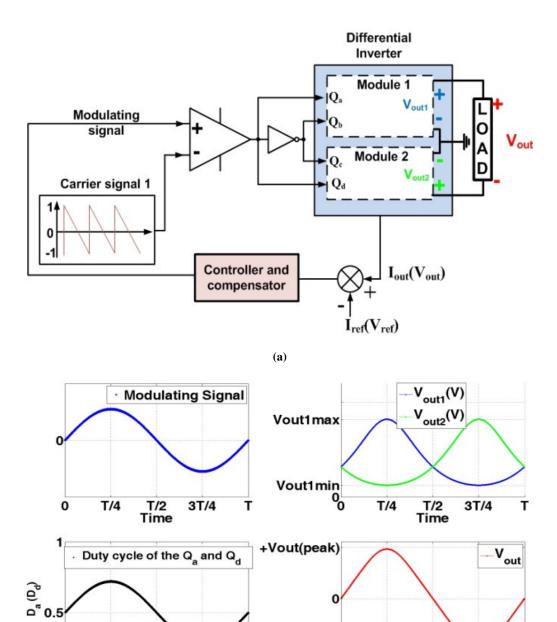

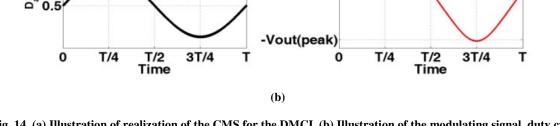

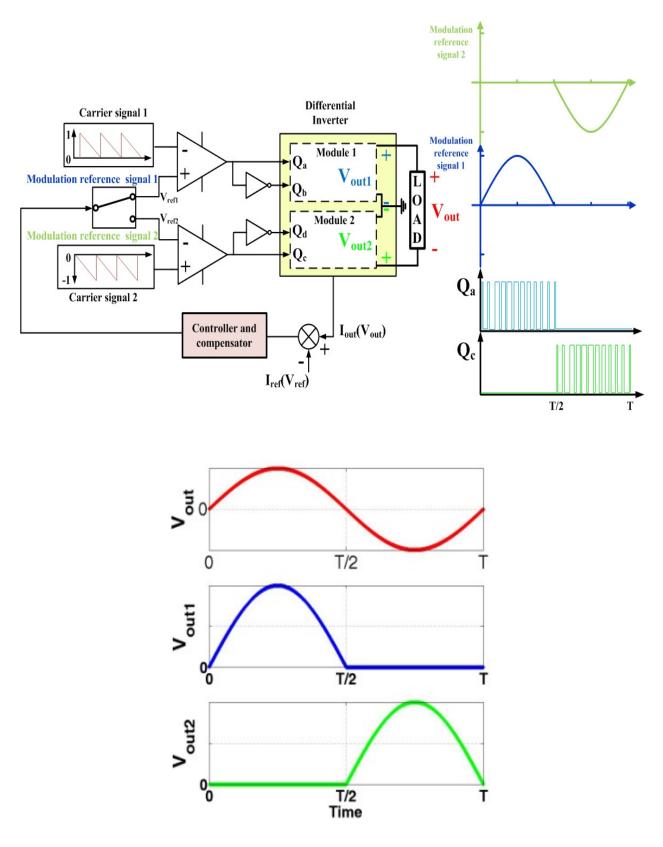

Fig. 14 (a) illustrates the realization of the CMS with control loop. The output voltage of the inverter ( $V_{out}$ ), the output voltage of each module ( $V_{out1}$  and  $V_{out2}$ ), the modulating signal and the duty cycle of  $Q_a$  are shown in Fig. 14(b). The output voltages of both modules are always positive and the minimum voltage depends on amplitude of the modulating signal, with the CMS. The instantaneous power ( $p_{out}(t)$ ) delivered to the load and the instantaneous powers ( $p_{out1}(t)$  and  $p_{out2}(t)$ ) flowing through the two modules are shown in Fig. 15(a), assuming a unity powerfactor load. Module 1 delivers positive power from the source to the load in the positive half line-cycle, while Module 2 returns part of it from the load to the source. A part of the delivered power returns to the source through Module 1 in the negative half of the line cycle. The power flow diagrams in the positive and negative halves of the line cycles are illustrated in Fig. 15(b) and Fig. 15(c), respectively.

0

Fig. 14. (a) Illustration of realization of the CMS for the DMCI. (b) Illustration of the modulating signal, duty cycles of the switches Qa (Qd), output voltages (Vout1 and Vout2) of Modules 1 and 2, and output voltage (Vout) of the DMCI using the CMS.

Fig. 15. (a) Instantaneous output powers of the DMCI and its two modules when the DMCI is operated using CMS. (b) and (c) Illustrations of power-flow mechanisms of Modules 1 and 2 during the positive and negative halves of a line cycle.

#### 2. Discontinuous modulation scheme (DMS)

The CMS was originally introduced for the low-power amplifiers of analog circuits [54] with reduced focus on power loss. For DMCI, and as evident from the illustration in Fig. 15, one of the main drawbacks of the CMS is that it leads to circulating power in the converter yielding enhanced loss. Moreover, this circulating power also enhances the peak current and peak voltage of the switching devices. Therefore, the main motivation for developing the DMS

is to mitigate the circulating power by activating only one of the two modules of the DMCI along with the ac-side switch of the inactive module in negative or positive halves of a line cycle. As such, and as evident in (3), the dc voltage-gain relation of the inverter is dependent in a piecewise manner on  $D_1$  and  $D_2$ .

$$\frac{V_{out}}{n \times V_{DC}} = \left(\frac{D_1}{1 - D_1}\right) \quad \text{(for } V_{out} > 0\text{)} \quad \text{or} \quad \frac{V_{out}}{n \times V_{DC}} = \left(\frac{D_2}{1 - D_2}\right) \quad \text{(for } V_{out} < 0\text{)}$$

(3)

Fig. 16 shows the modes of operation with DMS. Modes 1 and 2 are for positive half of the line cycle while Modes 3 and 4 are for the negative half of the line cycle. For each of the modes, a section of the inverter which is inactive is not shown. The capacitor voltage and inductor current in the inactive part of the inverter is zero.

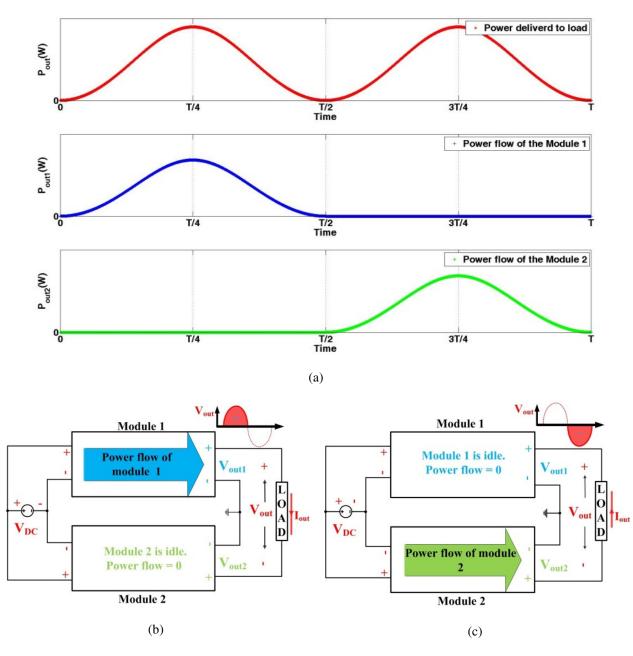

Fig. 17 illustrates the closed-loop realization of the DMS based DMCI. The output voltage (or current) error signal is fed back to the controller, which in turn generates the reference signal for modulation. The modulating signal is bipolar because the output voltage (or current) is bipolar. This signal is fed to the two modules alternately depending on the polarity of the output voltage. Consequently, the resultant modulating reference signals for each module is discontinuous in nature, as illustrated in Fig. 17. As evident in Fig. 17, even though the resultant output voltages ( $V_{out1}$  and  $V_{out2}$ ) of the modules are discontinuous in nature, the differential output voltage ( $V_{out1}$  of the DMCI is continuous in form. Assuming a unity-power-factor load (for illustration only), the instantaneous power delivered to the load ( $P_{out1}$ ) and the instantaneous power flowing through each of the two modules ( $P_{out1}$  and  $P_{out2}$ ) is shown in Fig. 18a. The flow of power flow in the DMCI in the positive and negative halves of the line cycle are illustrated, respectively, in Fig. 18b and Fig. 18c.

Fig. 16. Modes of operation of the DMCI using DMS.

Fig. 17. Illustration of realization of the DMS for the DMCI and the corresponding signals for modulation, switching, and output voltage.

Fig. 18. (a) Instantaneous output power of the DMCI and its individual modules using DMS. (b) and (c) Mechanisms of power flow for the modules of the DMCI during the positive and negative halves of the line cycle.

## C. Analysis of DMS and CMS

This section provides the theoretical evaluation and comparison of the CMS and the DMS assuming ideal switching condition. In Section D, validating experimental results are provided.

#### 1. <u>Circulating power</u>

As explained in Section 1, there is no circulating power with the DMS operated DMCI. In contrast, the CMSbased DMCI incorporates active as well as circulating reactive power, as illustrated in Fig. 15(a). Using the Fryze's definition [61], one can calculate the reactive power of each module of the DMCI. Because both modules have the same power ratings, only one module (i.e., Module 1) is selected here for the calculation of the active and the reactive powers as outlined below:

$$P_{out1} = \langle p_{out1}(t) \rangle_{avg} = \frac{1}{T} \int_0^T V_{out1}(t) \times I_{out}(t) dt$$

$$\tag{4}$$

$$S_{out1}^2 = P_{out1}^2 + Q_{out1}^2 = V_{out1}^2(rms) \times I_{out1}^2(rms) = \frac{1}{T} \int_0^T V_{out1}^2(t) dt \times \frac{1}{T} \int_0^T I_{out1}^2(t) dt.$$

(5)

In (4) and (5),  $p_{out1}(t)$  is the instantaneous power,  $P_{out1}$  is the active power,  $Q_{out1}$  is the circulating reactive power,  $S_{out1}$  is the apparent power, and  $V_{out1}$  and  $I_{out}$  are output voltage and output current of Module 1. Using (4) and (5), the ratio of the reactive to the active power can be derived to be the following:

$$\frac{Q_{out1}}{P_{out1}} = \sqrt{\frac{\frac{1}{T} \int_{0}^{T} V_{out1}^{2}(t) dt \times \frac{1}{T} \int_{0}^{T} I_{out}^{2}(t) dt}{[\frac{1}{T} \int_{0}^{T} V_{out1}(t) \times I_{out}(t) dt]^{2}}} - 1 .$$

(6)

Assuming a unity-power-factor load and negligible total harmonic distortion (THD) for the load voltage and the load current, we obtain

$$\begin{cases} I_{out} = I_{out}^* \sin(\omega t) \\ V_{out} = V_{out}^* \sin(\omega t) = n V_{DC} \times g^* \sin(\omega t) \end{cases}$$

(7)

where  $g^*$  represents the peak normalized dc-voltage gain and is defined to be equal to  $\frac{v_{out}^*}{n \times v_{DC}}$ . The dc-voltage gains of the DMCI is defined by (2) while the dc-voltage gain of Module 1 (i.e.,  $g_1$ ) is defined by (8) for operation of the DMCI using the CMS:

$$g_1 = \frac{V_{out1}}{n \times V_{DC}} = \left(\frac{D_1}{1 - D_1}\right) \tag{8}$$

Using (2) and (8), the relation between g and  $g_1$  is found to be the following:

$$g_1 = \frac{g}{2} + \sqrt{\left(\frac{g}{2}\right)^2 + 1}.$$

(9)

Using (8) and (9), Vout1 is found to be the following:

$$V_{out1} = nV_{DC} \left( \frac{g^* \sin(\omega t)}{2} + \sqrt{\left(\frac{g^* \sin(\omega t)}{2}\right)^2 + 1} \right).$$

(10)

Substituting  $V_{out1}$  from (10) and  $I_{out}$  from (7) into (6) and simplifying the resultant expression yields:

$$\frac{Q_{out1}}{P_{out1}} = \sqrt{\frac{\int_{0}^{T} \left(\frac{g^* \sin(\omega t)}{2} + \sqrt{\left(\frac{g^* \sin(\omega t)}{2}\right)^2 + 1}\right)^2 dt \times \int_{0}^{T} \sin^2(\omega t) dt}{[\int_{0}^{T} \left(\frac{g^* \sin(\omega t)}{2} + \sqrt{\left(\frac{g^* \sin(\omega t)}{2}\right)^2 + 1}\right) \times \sin(\omega t) dt]^2}} - 1 = \sqrt{\frac{\int_{0}^{T} \left(\frac{g^*^2 \sin^2(\omega t)}{2} + 1\right) dt \times \int_{0}^{T} \sin^2(\omega t) dt}{[\int_{0}^{T} \frac{g^*}{2} \sin^2(\omega t) dt]^2}} - 1}$$

(11)

$$\frac{Q_{out1}}{P_{out1}} = \sqrt{\frac{g^{*2} + 8}{g^{*2}}}.$$

(12)

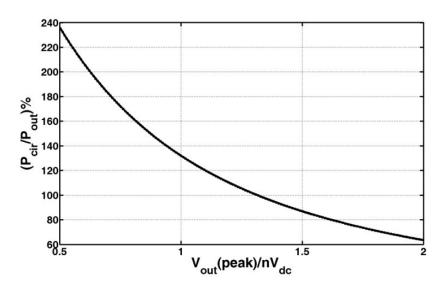

Note that,  $V_{out}$  using CMS is a sinusoidal waveform while  $V_{out1}$  is a non-sinusoidal waveform. Fig. 19 plots the ratio of  $Q_{out1}$  and  $P_{out1}$  as a function of the normalized peak dc-voltage gain as captured in (12). The circulating power is significant for lower peak dc-voltage gains leading to additional power loss.

Fig. 19. For Module 1, the ratio of the reactive (circulating) power to the active power for varying peak normalized dc-voltage gain for the DMCI when the inverter is operated using CMS. The DMCI has no circulating-power when it is operated using DMS.

### 2. Device rating

Following Fig. 12, the off-state voltage of each device in the DMCI ( $V_{Qa}$ ,  $V_{Qb}$ ) is given by the following set of expressions:

$$\begin{cases} V_{Qa} = V_{ca} + \frac{V_{cb}}{n} \\ V_{Qb} = nV_{ca} + V_{cb} \end{cases}$$

(13)

In the steady state, using  $V_{ca} = V_{DC}$  and  $V_{cb} = V_{out1}$ , (13) translates to the following expression:

$$\begin{cases} V_{Qa} = V_{DC} + \frac{V_{out1}}{n} \\ V_{Qb} = nV_{DC} + V_{out1} \end{cases}$$

(14)

The voltage ratings of the devices should be designed for the worst case, which happens at the peak output voltage.

For the DMS-based DMCI, the peak output voltages of Modules 1 and 2 ( $V_{out1}^*$  and  $V_{out2}^*$ ) equal  $V_{out}^*$ . However, when DMCI is operated using CMS, the peak output voltage of each module is higher than the  $V_{out}^*$ . These can be expressed as follows:

$$\begin{cases} V_{out1}^* = V_{out2}^* = V_{out}^* & \text{for DMS} \\ V_{out1}^* = V_{out}^* + V_{out2}(min) & \text{for CMS} \end{cases}$$

(15)

where  $V_{out2}(min)$  is always positive. Equations (15) and (16) show that the voltage ratings of the devices of the DMCI when operated using CMS are higher than those obtained using DMS. The ratio of the peak voltage of the device using CMS to the peak voltage of the device with DMS can be obtained by substituting (15) into (14). This ratio is rewritten as a function of peak dc-voltage gain using (2) and (3):

$$\frac{v_{Qa}^{*}(CMS)}{v_{Qa}^{*}(DMS)} = \frac{v_{Qb}^{*}(CMS)}{v_{Qb}^{*}(DMS)} = \frac{v_{DC} + \frac{v_{out1}^{*}}{n}}{v_{DC} + \frac{v_{out1}^{*}}{n}}$$

(16)

where  $V_{Qa}^*$  and  $V_{Qb}^*$  are peak voltages of the primary side and the secondary side devices, respectively. It is noted that, (16) does not include any device voltage spike, which is dependent on the load, leakage inductance of the transformer, the off-state voltage of the device, and printed-circuit-board (PCB) layout. As such, the actual peak voltages are slightly higher and (16) indicates an approximate value. Using (2), (8) and (9) and (16), the device voltage ratio can be written as a function of  $g^*$  as follows:

$$\frac{V_{Qa}^*(CMS)}{V_{Qa}^*(DMS)} = \frac{V_{Qb}^*(CMS)}{V_{Qb}^*(DMS)} \approx \frac{1 + \frac{g^*}{2} + \sqrt{(\frac{g^*}{2})^2 + 1}}{1 + g^*}$$

(17)