# Communication Scheduling and Buslet-based Design: New Paradigms for High Level Synthesis

$\mathbf{b}\mathbf{y}$

ENZO TARTAGLIONE Laurea, Politecnico di Torino, Turin, Italy, 2013

### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2015

Chicago, Illinois

Defense Committee:

Shantanu Dutt, Chair and Advisor John Lillis Mariagrazia Graziano, Politecnico di Torino To my parents

always near

despite the distance.

### ACKNOWLEDGMENTS

I would like to thank my advisor at the University of Illinois at Chicago, Prof. Shantanu Dutt, with whom I collaborated to perform the research described in this thesis. The work in this thesis is a result of this collaboration when I was a student at UIC from August 2014 to July 2015, as well as a funded research assistant from January 2015 to July 2015. This collaboration also allowed me to intellectually grow so much.

I would like to thank all my friends from Turin belonging to the group "The paladins of Medusa", old and new members, for letting me feel as I were in Italy despite the huge distance between us. A special thank goes to Massimo S., thanks to whom I was able to carry out part of the paperwork necessary to graduate.

Lastly, I deeply thank my parents for the vigorous and continuous support they have always given to me. Since my first year at the university they helped me to overcome difficult moments and certainly I was able to do whatever I did thanks to their continuous support.

### PREFACE

This project, as the final stage of my master's studies, gave me both the experience and abilities that I was willing to acquire in the field of VLSI CAD algorithms and tools development.

The chance of working with Prof. Dutt, in particular, provided me first with knowledge on state-of-the-art High Level Synthesis algorithms and then gave me the possibility of developing skills in problem solving and algorithm design. In the last three months the work was mainly focused on the study and design of interconnect models for dynamic power minimization. Furthermore, such an opportunity helped me to develop skills in object oriented coding.

The complexity of the analyzed problems, finally, gave me a brand new viewpoint on problem solving methods and approaches and enlarged my vision beyond a purely engineering perspective.

# TABLE OF CONTENTS

# **CHAPTER**

| <b>1</b> | INTRODU  | JCTION                                                    |

|----------|----------|-----------------------------------------------------------|

|          | 1.1      | Flexible buslets: a new interconnection paradigm          |

|          | 1.1.1    | Previous work using bus-like structures                   |

|          | 1.2      | Thesis outline                                            |

| <b>2</b> | MAIN ISS | SUES IN BUSLET WIRED DESIGNS                              |

|          | 2.1      | Maximization of wire efficiency                           |

|          | 2.2      | Dynamic power consumption and signal delay: constraint on |

|          |          | maximum cardinality of a buslet                           |

|          | 2.2.1    | Maximum fanin and fanout per FU                           |

| 3        | SCHEDU   | LING ALGORITHMS                                           |

|          | 3.1      | Introduction to the VLSI CAD flow                         |

|          | 3.2      | High level synthesis                                      |

|          | 3.2.1    | As-soon-as-possible scheduling algorithm                  |

|          | 3.2.2    | As-late-as-possible scheduling algorithm                  |

|          | 3.2.3    | Mobility range for an operation node                      |

|          | 3.3      | Force directed scheduling algorithm                       |

|          | 3.3.1    | Probability estimation for an operation node              |

|          | 3.3.2    | Distribution graph                                        |

|          | 3.3.3    | Force computation                                         |

|          | 3.3.4    | Predecessor and successor forces                          |

|          | 3.3.5    | Complexity                                                |

|          | 3.4      | Scheduling algorithm for buslet-based designs             |

|          | 3.4.1    | Communication with dedicated interconnections             |

|          | 3.4.2    | Force directed communication scheduling                   |

|          | 3.4.3    | Complexity                                                |

|          | 3.5      | Summary of scheduling algorithms                          |

| 4        | BINDING  | ALGORITHMS                                                |

|          | 4.1      | General concepts to be taken into account                 |

|          | 4.1.1    | Wirelength model                                          |

|          | 4.1.2    | Effect of fanin/fanout constraints on binding             |

|          | 4.2      | Chronological binding                                     |

|          | 4.2.1    | Reuse of already available hardware                       |

|          | 4.2.2    | Reduction of solution space                               |

|          | 4.2.3    | Complexity                                                |

# TABLE OF CONTENTS (Continued)

# **CHAPTER**

| 4.3.1       Justification of similarity-based pruning       70         4.3.2       Complexity       71         4.4       Chronological lookahead binding       72         4.1       Complexity       74         4.5       Simultaneous binding of iso-scheduled COMs       75         4.5.1       Improving the average computation time       79         4.5.2       Complexity       82         4.6       Force directed binding       83         4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of weight function for a given solution       84         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Kruskal's algorithm       92         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B                   |                                      | 4.3     | Chronological binding with similarity reduction   | 64  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------|---------------------------------------------------|-----|

| 4.3.2       Complexity       71         4.4       Chronological lookahead binding       72         4.4.1       Complexity       72         4.4.1       Complexity       72         4.4.1       Complexity       72         4.5       Simultaneous binding of iso-scheduled COMs       75         4.5.1       Improving the average computation time       79         4.5.2       Complexity       82         4.6       Force directed binding       83         4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of weight function for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spaning tree       91         5.2.1       Prim's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96                                               |                                      | 4.3.1   |                                                   | 70  |

| 4.4       Chronological lookahead binding       72         4.4.1       Complexity       74         4.5       Simultaneous binding of iso-scheduled COMs       75         4.5.1       Improving the average computation time       79         4.5.2       Complexity       82         4.6       Force directed binding       83         4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of probability for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102<                    |                                      | 4.3.2   |                                                   | 71  |

| 4.4.1       Complexity       74         4.5       Simultaneous binding of iso-scheduled COMs       75         4.5.1       Improving the average computation time       79         4.5.2       Complexity       82         4.6       Force directed binding       83         4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of weight function for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.6       MST-LOGD       106                              |                                      | 4.4     |                                                   | 72  |

| 4.5       Simultaneous binding of iso-scheduled COMs       75         4.5.1       Improving the average computation time       79         4.5.2       Complexity       82         4.6       Force directed binding       83         4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of weight function for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105                    | 4.4.1Complexity4.5Simultaneous bindi |         |                                                   |     |

| 4.5.1       Improving the average computation time       79         4.5.2       Complexity       82         4.6       Force directed binding       83         4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of weight function for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106 <t< td=""><td>4.5</td><td></td><td></td></t<>       |                                      | 4.5     |                                                   |     |

| 4.5.2       Complexity       82         4.6       Force directed binding       83         4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of weight function for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.7.1                                                          |                                      | 4.5.1   | 0                                                 |     |

| 4.6       Fore directed binding       83         4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of weight function for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Mininum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.7.1       Complexity       109         5.8 <t< td=""><td></td><td>4.5.2</td><td></td><td>82</td></t<> |                                      | 4.5.2   |                                                   | 82  |

| 4.6.1       Formulation of probability for a given solution       84         4.6.2       Formulation of weight function for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.7.1       Complexity       108         5.7.1       Complexity       109         5.8       MAX-D<                                                       |                                      | 4.6     |                                                   |     |

| 4.6.2       Formulation of weight function for a given solution       85         4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity </td <td></td> <td>4.6.1</td> <td></td> <td></td>       |                                      | 4.6.1   |                                                   |     |

| 4.6.3       Predecessor/successor forces       86         4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hi                                                                                                   |                                      | 4.6.2   |                                                   |     |

| 4.6.4       Efficacy of this algorithm       87         4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.7.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       108         5.7       MST-BF       108         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning                                                                                                           |                                      | 4.6.3   |                                                   |     |

| 4.6.5       Complexity       89         5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9.1       Complexity       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS                                                                                                           |                                      | 4.6.4   |                                                   |     |

| 5       BUSLET POWER MODELING       90         5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.9.1       Complexity       115         5.10       Hierarchical partitioning <td< td=""><td></td><td>4.6.5</td><td></td><td>89</td></td<>                                                     |                                      | 4.6.5   |                                                   | 89  |

| 5.1       Metrics involved in buslet power consumption       90         5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7.1       Placing tristate buffers       108         5.7.1       Complexity       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       115         5.10.1       Complexit                                                                                                   |                                      |         |                                                   |     |

| 5.2       Minimum spanning tree       91         5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.7.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                      | <b>5</b>                             |         |                                                   |     |

| 5.2.1       Prim's algorithm       92         5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                         |                                      |         | · ·                                               |     |

| 5.2.2       Kruskal's algorithm       92         5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                       |                                      |         |                                                   |     |

| 5.3       Standard buffer placement       93         5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       105         5.6       MST-BF       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                              |                                      | -       |                                                   |     |

| 5.3.1       Complexity       96         5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                    |                                      |         |                                                   |     |

| 5.4       MST-2B       96         5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8       MAX-D       109         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                |                                      | 5.3     |                                                   | 93  |

| 5.4.1       Shortest path problem: Dijkstra's algorithm       99         5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |         |                                                   |     |

| 5.4.2       Complexity       100         5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      | -       | MST-2B                                            |     |

| 5.5       MST-1B       102         5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |         |                                                   | 99  |

| 5.5.1       Placing tristate buffers       104         5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                      |         |                                                   |     |

| 5.5.2       Complexity       105         5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |         | MST-1B                                            |     |

| 5.6       MST-LOGD       106         5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.10       Hierarchical partitioning       115         5.10       Complexity       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |         | 0                                                 |     |

| 5.6.1       Complexity       108         5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.9.1       Complexity       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |         |                                                   | 105 |

| 5.7       MST-BF       108         5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.9.1       Complexity       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       112         119       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |         | MST-LOGD                                          | 106 |

| 5.7.1       Complexity       109         5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.9.1       Complexity       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |         |                                                   | 108 |

| 5.8       MAX-D       109         5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.9.1       Complexity       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       115         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.7 MST-BF                           | MST-BF  | 108                                               |     |

| 5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.9.1       Complexity       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       115         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      | 5.7.1   |                                                   | 109 |

| 5.8.1       Complexity       112         5.9       MAX-D-MAXHOP       115         5.9.1       Complexity       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       115         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      | 5.8     | MAX-D                                             | 109 |

| 5.9.1       Complexity       115         5.10       Hierarchical partitioning       115         5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | 5.8.1   | Complexity                                        | 112 |

| 5.10Hierarchical partitioning1155.10.1Complexity1196EXPERIMENTAL RESULTS120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      | 5.9     | MAX-D-MAXHOP                                      | 115 |

| 5.10.1       Complexity       119         6       EXPERIMENTAL RESULTS       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | 5.9.1   |                                                   | 115 |

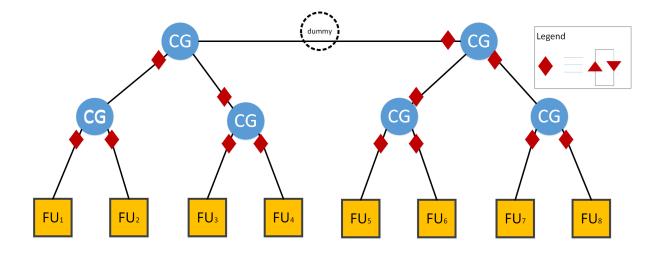

| 6 EXPERIMENTAL RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      | 5.10    | Hierarchical partitioning                         | 115 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      | 5.10.1  | Complexity                                        | 119 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                                    | EXPERIM | MENTAL RESULTS                                    | 120 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                    | 6.1     | Performance for scheduling and binding algorithms | 121 |

| 6.1.1 Comparison with another HLS algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      |         |                                                   |     |

# TABLE OF CONTENTS (Continued)

| <u>CHAPT</u> | CHAPTER        |                       |       |

|--------------|----------------|-----------------------|-------|

|              | $6.1.2 \\ 6.2$ | Discussion of results |       |

| 7            | CONCI          | LUSIONS               | . 141 |

|              | APPEN          | NDIX                  | . 143 |

|              | CITED          | LITERATURE            | . 148 |

|              | VITA .         |                       | . 153 |

# LIST OF TABLES

| TABLE |                                                                                 | PAGE |

|-------|---------------------------------------------------------------------------------|------|

| Ι     | AVERAGE RUNTIMES FOR DIFFERENT DFG SIZES                                        | 143  |

| II    | AVERAGE AREA                                                                    | 144  |

| III   | AVERAGE WIRELENGTH                                                              | 144  |

| IV    | AVERAGE WIRE EFFICIENCY                                                         | 144  |

| V     | AVERAGE WIRELENGTH FOR DIFFERENT BUSLET STRUC-<br>TURES                         | 145  |

| VI    | TOTAL DYNAMIC POWER CONSUMED BY INTERCONNECTS - WIRE CAPACITANCE CONTRIBUTION   | 145  |

| VII   | TOTAL DYNAMIC POWER CONSUMED BY INTERCONNECTS<br>- TRISTATE BUFFER CONTRIBUTION | 145  |

| VII   | TOTAL STATIC POWER CONSUMED BY INTERCONNECTS -<br>TRISTATE BUFFER LEAKAGE       | 146  |

| IX    | DYNAMIC POWER CONSUMED BY FUS                                                   | 146  |

| Х     | STATIC POWER CONSUMED BY FUS                                                    | 146  |

| XI    | TOTAL POWER                                                                     | 147  |

| XII   | PERCENTAGE CHANGE IN TOTAL POWER                                                | 147  |

| XII   | I MAXIMUM DISTANCE BETWEEN FUS                                                  | 147  |

# LIST OF FIGURES

| FIGURE |                                                                            | PAGE |

|--------|----------------------------------------------------------------------------|------|

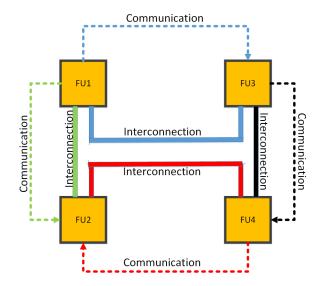

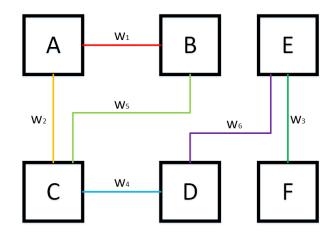

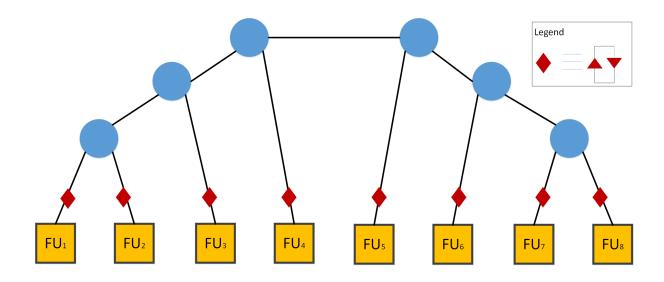

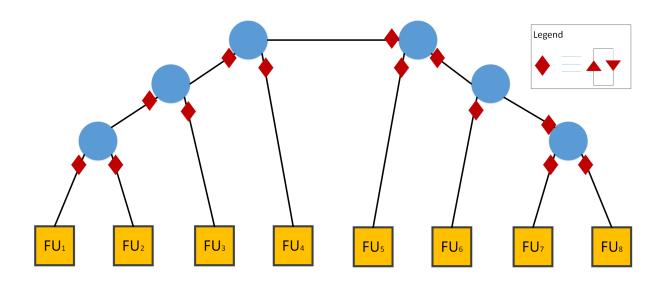

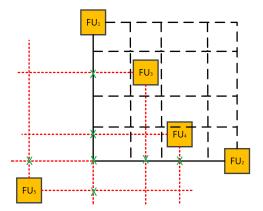

| 1      | Example of dedicated interconnections design                               | 12   |

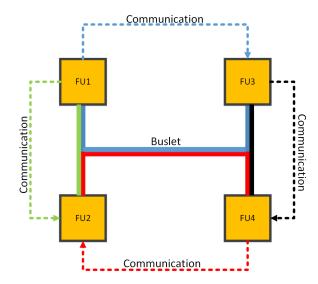

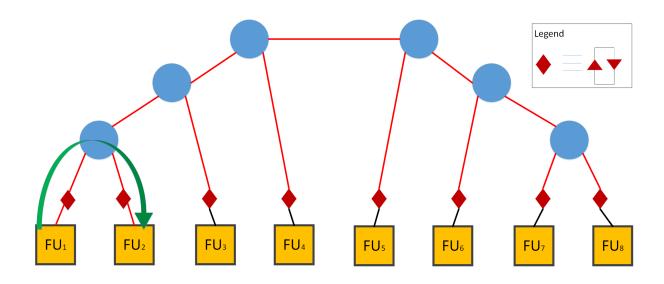

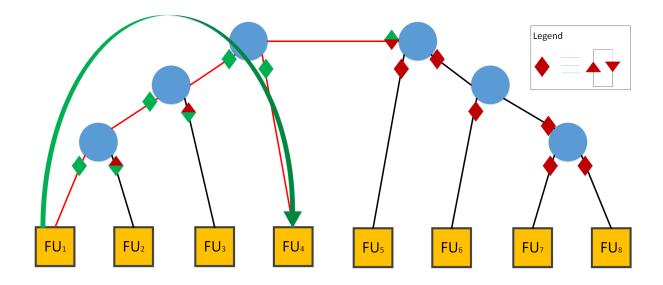

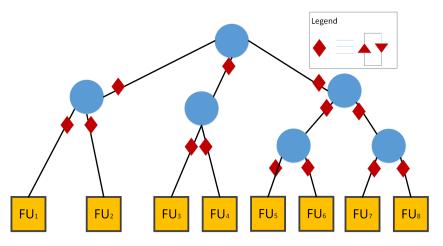

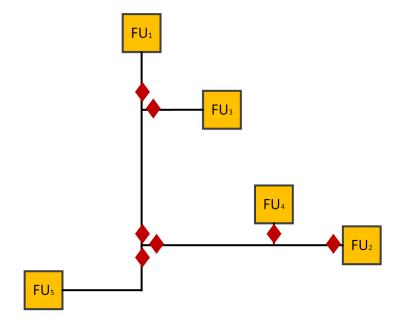

| 2      | Example of buslet design                                                   | 13   |

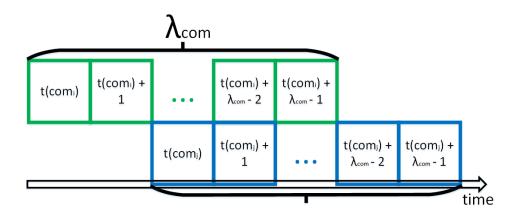

| 3      | Example of overlapping communications.                                     | 15   |

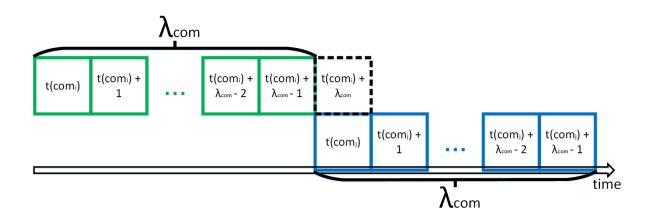

| 4      | Example of non overlapping communications                                  | 16   |

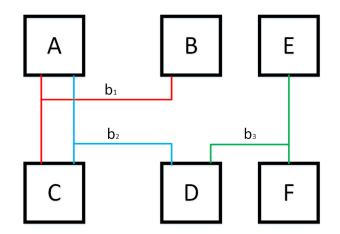

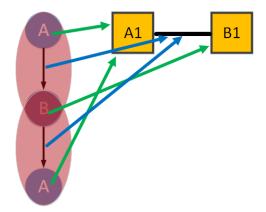

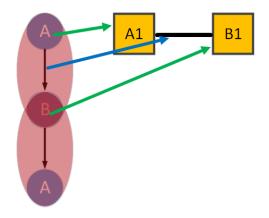

| 5      | Example of dedicated interconnects implementation                          | 17   |

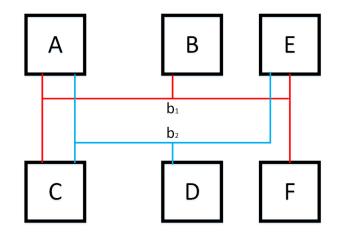

| 6      | Example of buslet implementation                                           | 17   |

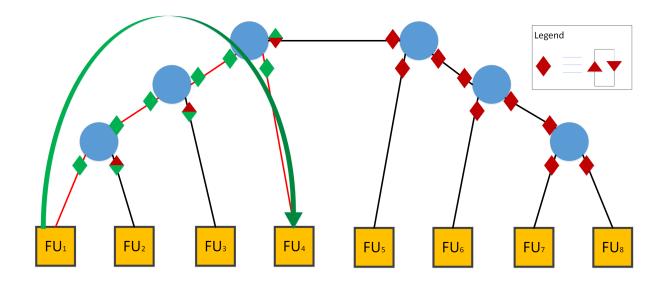

| 7      | Second example of buslet implementation                                    | 18   |

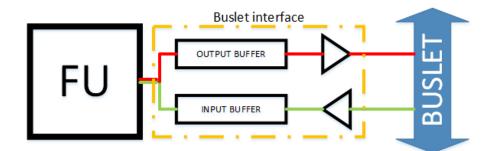

| 8      | Functional unit interface with the buslet                                  | 19   |

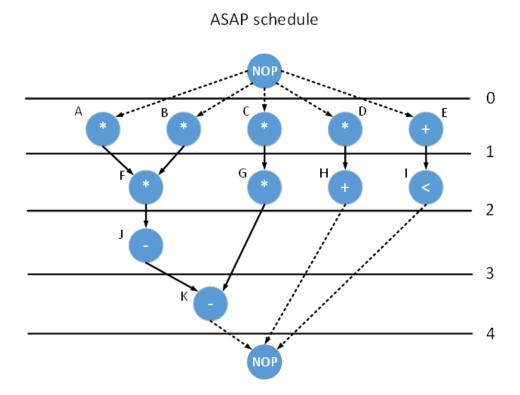

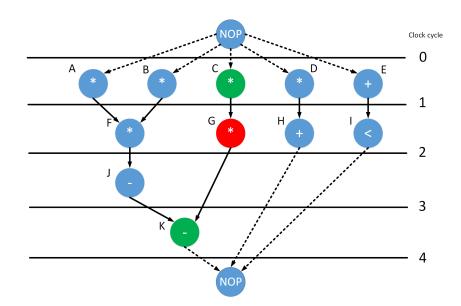

| 9      | Example of as-soon-as-possible schedule                                    | 28   |

| 10     | Example of as-late-as-possible schedule                                    | 31   |

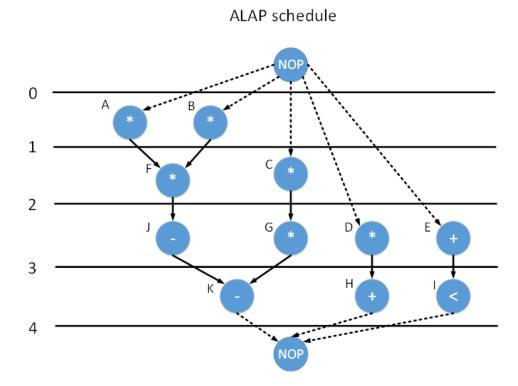

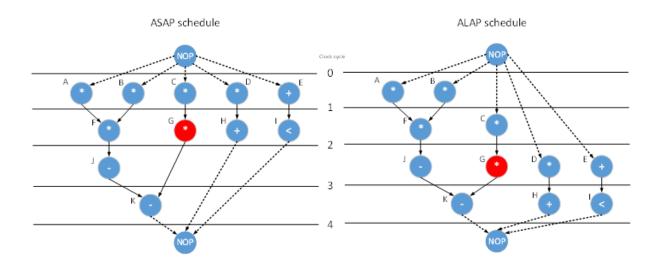

| 11     | Example of mobility range for a node in a data<br>flow graph $\ .\ .\ .$ . | 33   |

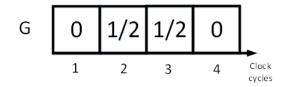

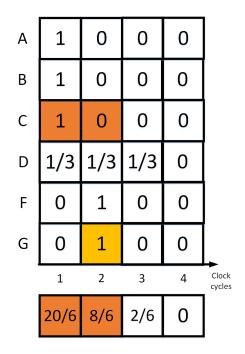

| 12     | Scheduling probability example                                             | 35   |

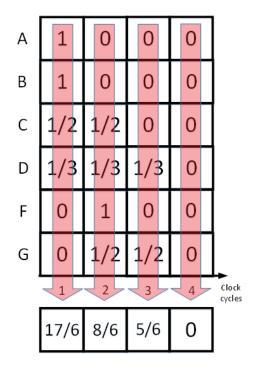

| 13     | Example of distribution graph                                              | 36   |

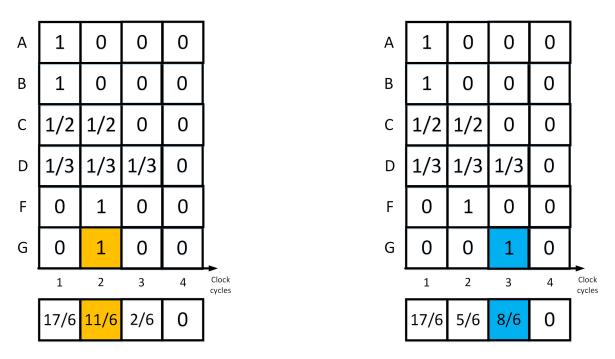

| 14     | Example of self force computation                                          | 38   |

| 15     | Example of self force computation                                          | 39   |

| 16     | Reduction of mobility range for predecessors                               | 40   |

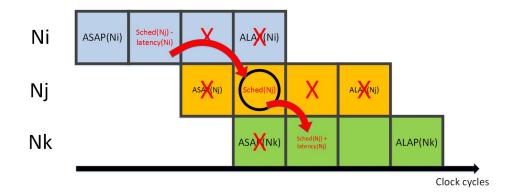

| 17     | Effect of scheduling node $N_j$ on predecessor $N_i$ and successor $N_k$   | 41   |

| 18     | Reduction of mobility range for predecessors                               | 43   |

# LIST OF FIGURES (Continued)

# FIGURE

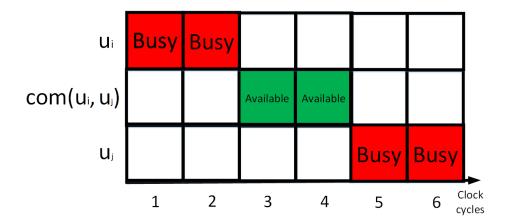

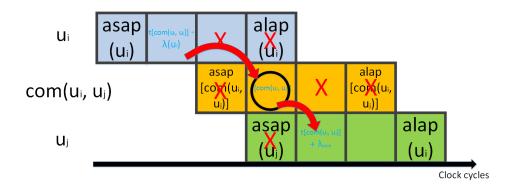

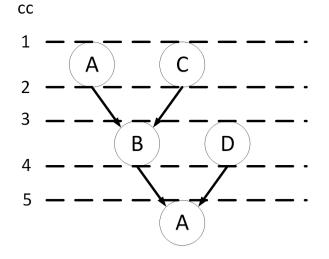

| 19 | Example of time frame in which the communication between $u_i$ and $u_j$ can happen $\ldots \ldots \ldots$ | 46  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

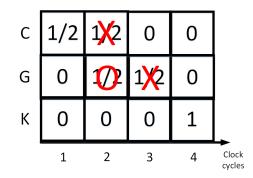

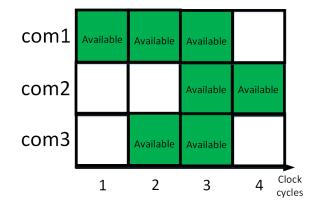

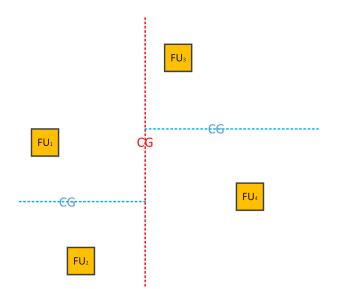

| 20 | Example of communications possible concurrency                                                                                                                                                                             | 47  |

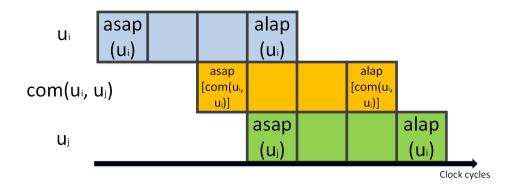

| 21 | Mobility range for communication between $u_i$ and $u_j$                                                                                                                                                                   | 49  |

| 22 | Example of communication scheduling and its effect on mobility ranges for functional units                                                                                                                                 | 50  |

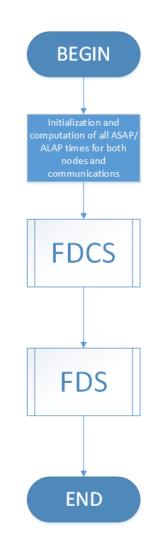

| 23 | General dataflow for the scheduling technique used                                                                                                                                                                         | 52  |

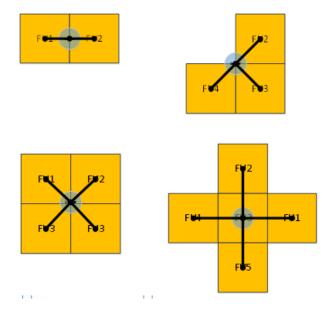

| 24 | Examples of computation of wirelength for buslet cardinalities from 2 to 5 $$                                                                                                                                              | 57  |

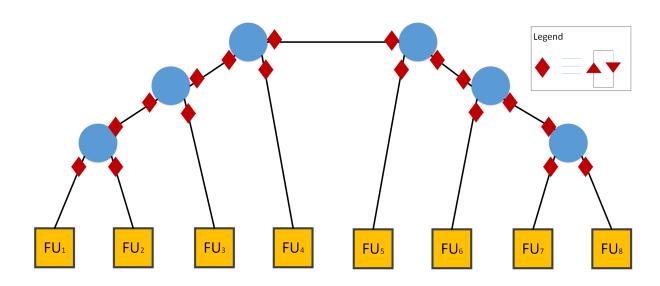

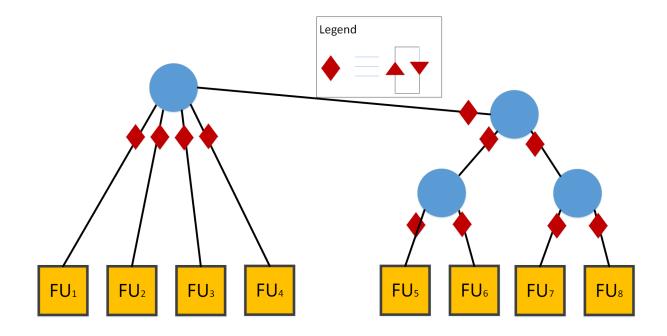

| 25 | Example of fanin/fanout constraint                                                                                                                                                                                         | 59  |

| 26 | Example of reuse of previously bound buslets                                                                                                                                                                               | 61  |

| 27 | Example of binding solution space reduction                                                                                                                                                                                | 63  |

| 28 | Example two solutions similar differing for buslets labels                                                                                                                                                                 | 65  |

| 29 | Example two solutions similar with different binding for both buslets and functional units                                                                                                                                 | 66  |

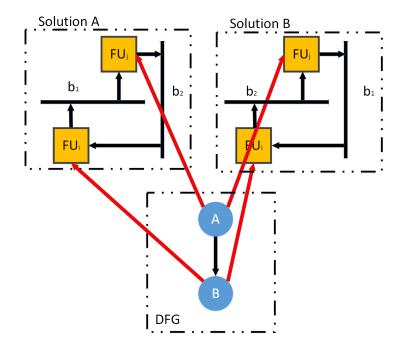

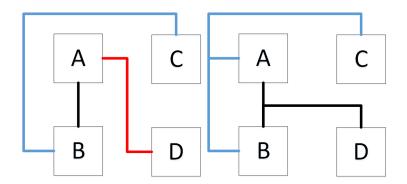

| 30 | Why simultaneous binding matters                                                                                                                                                                                           | 76  |

| 31 | Chronological binding vs. simultaneous binding of iso-scheduled coms<br>output                                                                                                                                             | 76  |

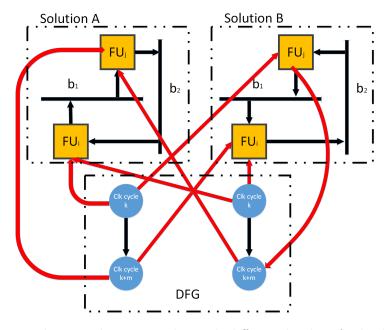

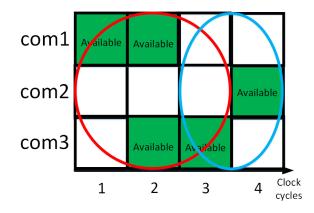

| 32 | Binding overlapping communications                                                                                                                                                                                         | 78  |

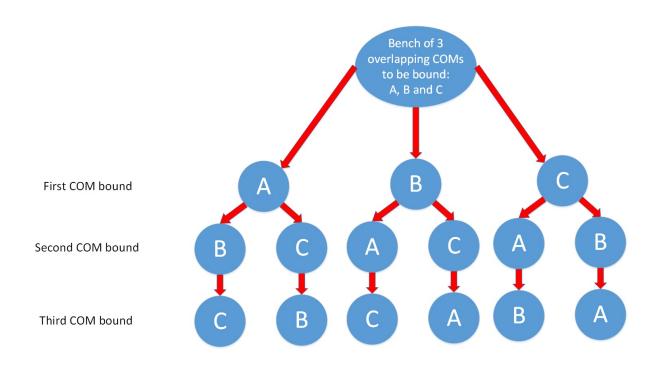

| 33 | Analysis of possibilities for 3 overlapping communications                                                                                                                                                                 | 80  |

| 34 | Example of SBP                                                                                                                                                                                                             | 94  |

| 35 | Communication in the SBP model                                                                                                                                                                                             | 97  |

| 36 | Communication in the MST-2B model                                                                                                                                                                                          | 98  |

| 37 | Example of MST-2B                                                                                                                                                                                                          | 100 |

# LIST OF FIGURES (Continued)

# FIGURE

| 38 | Example of MST-1B                                                            | 102 |

|----|------------------------------------------------------------------------------|-----|

| 39 | Communication in the MST-1B model                                            | 103 |

| 40 | Example of MST-LOGD                                                          | 107 |

| 41 | Example of MST-BF                                                            | 111 |

| 42 | MAX-D algorithm at work                                                      | 113 |

| 43 | Example of MAX-D                                                             | 113 |

| 44 | HP at work                                                                   | 117 |

| 45 | Example of hierarchical partitioning                                         | 118 |

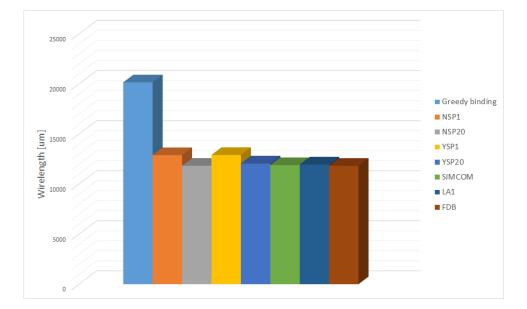

| 46 | Comparison between greedy-binding method and ours for buslet cardinality 2   | 122 |

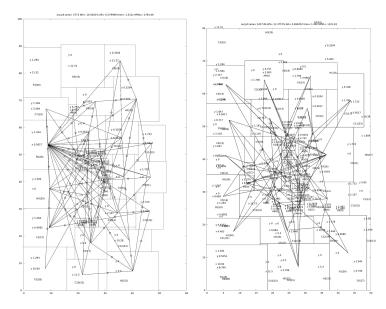

| 47 | Comparison between two different output chip layouts                         | 123 |

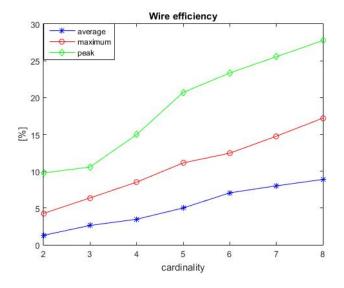

| 48 | Average, maximum and peak wire efficiencies                                  | 124 |

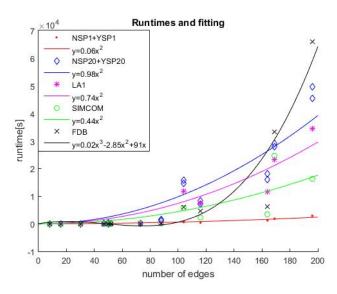

| 49 | Runtime data and curve fitting for the designed HLS algorithms $\ . \ . \ .$ | 124 |

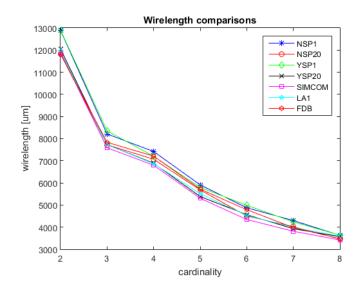

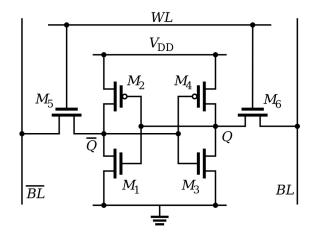

| 50 | Total wirelength averages                                                    | 127 |

| 51 | Total area averages                                                          | 128 |

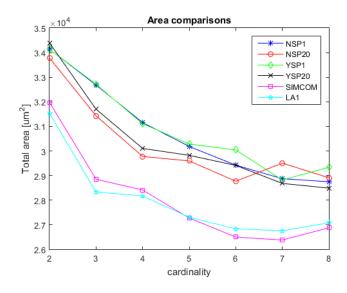

| 52 | Logic gates composing a FA                                                   | 130 |

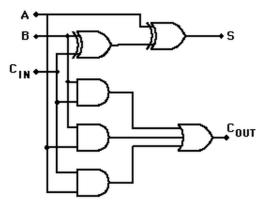

| 53 | SRAM cell                                                                    | 131 |

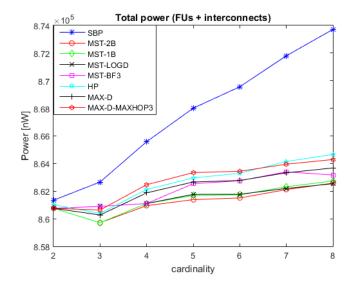

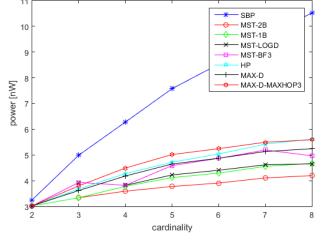

| 54 | Total power consumption                                                      | 133 |

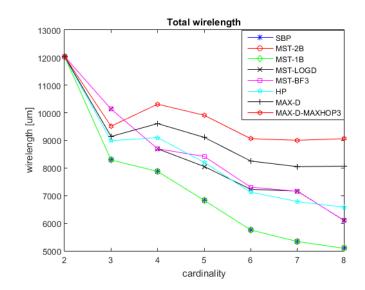

| 55 | Total wirelengths                                                            | 133 |

| 56 | Dynamic power contribution of FUs                                            | 134 |

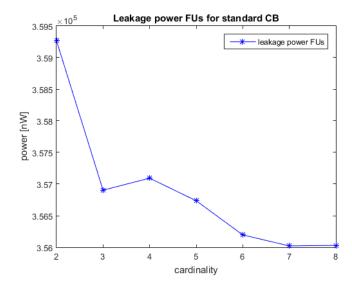

| 57 | Leakage power contribution of FUs                                            | 135 |

| 58 | Dynamic power contribution of wire                                           | 136 |

# LIST OF FIGURES (Continued)

# FIGURE

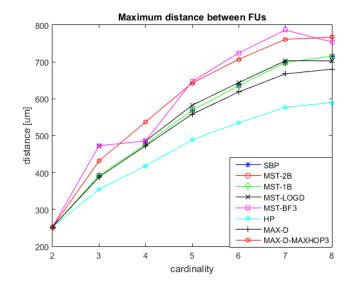

| 59 | Maximum distance between any two connected FUs                                   | 136 |

|----|----------------------------------------------------------------------------------|-----|

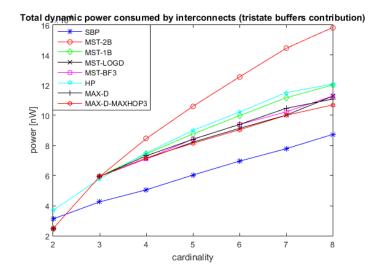

| 60 | Dynamic power contribution of tristate buffers input load $\ldots \ldots \ldots$ | 137 |

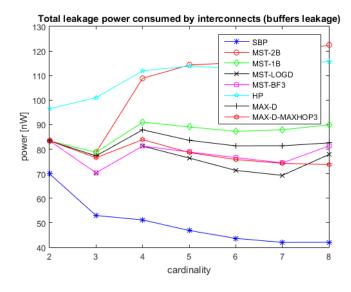

| 61 | Leakage power contribution of tristate buffers                                   | 138 |

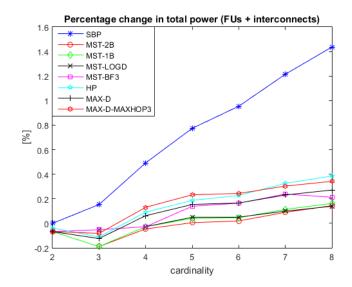

| 62 | Percentage change in total power                                                 | 138 |

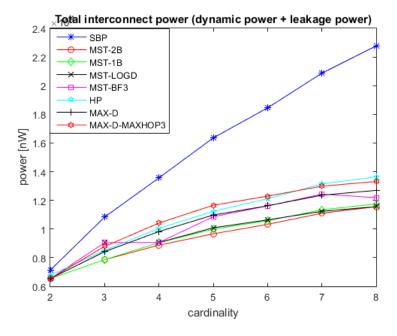

| 63 | Total interconnect power                                                         | 139 |

# LIST OF ABBREVIATIONS

| ALAP | As Late As Possible                             |

|------|-------------------------------------------------|

| ALU  | Arithmetic Logic Unit                           |

| ASAP | As Soon As Possible                             |

| ASIC | Application-Specific Integrated Circuit         |

| BP   | Binding Possibility                             |

| СВ   | Chronological Binding                           |

| CBSR | Chronological Binding with Similarity Reduction |

| DFG  | Data Flow Graph                                 |

| FDB  | Force Directed Binding                          |

| FDCS | Force Directed Communication Scheduling         |

| FDS  | Force Directed Scheduling                       |

| FSM  | Finite State Machine                            |

| FU   | Functional Unit                                 |

| HLS  | High Level Synthesis                            |

| HP   | Hierarchical Partitioning                       |

| LA   | Lookahead                                       |

# LIST OF ABBREVIATIONS (Continued)

| ML-RCS | Minimum Latency-Resource Constrained Sched- |

|--------|---------------------------------------------|

|        | ule                                         |

| MR-LCS | Minimum Resource-Latency Constrained Sched- |

|        | ule                                         |

| MST    | Minimum Spanning Tree                       |

| PF     | Predecessor Force                           |

| RCA    | Ripple Carry Adder                          |

| RTL    | Register Transfer Level                     |

| SF     | Self-Force                                  |

| SSI    | Small Scale Integration                     |

| UIC    | University of Illinois at Chicago           |

| VLSI   | Very Large Scale Integrated                 |

| WL     | Wirelength                                  |

### SUMMARY

Current nanoscale designs are highly interconnect dominated, taking about 70% of the chip area. Interconnects also consume a significant part of the dynamic power and are responsible of about the 60% of signal delays. It is, thus, important to be able to synthesize much lower interconnect-complexity designs than are possible with current high-level synthesis (HLS) tools and algorithms. Towards that end, we have developed the following new paradigms in the scheduling, binding and general architecture synthesis problems of HLS:

- Flexibly-structured that connect a few neighborhood functional units (FUs) instead of dedicated interconnects between pairs of FUs, thereby sharing interconnects among a number of FU pairs that need to communicate.

- Communication scheduling (followed by standard operation scheduling that respects the communication schedules) in which communications between FUs are scheduled at appropriate times to minimize the number of buslets needed, subject to buslet cardinality constraints (for the purpose of upper bounding signal delay).

- Buslet binding techniques, aiming to respect both buslet cardinality constraint and a constraint on maximum fanin and fanout for the functional units. These techniques will range from simple but effective approaches like chronological binding (CB) to more sophisticated ones, like the use of lookahead approaches and simultaneous binding of iso-scheduled communications (communications scheduled in the same clock cycle). Furthermore, in this direction, similar solutions detection mechanism was developed, in order to improve the

### SUMMARY (Continued)

final quality of the result. Finally, also a force directed approach was used to solve the binding problem (FDB). All these techniques were implemented and compared in terms of both performance and complexity.

• Buslet power modeling. A number of configurations with multiple tri-state buffers for interconnecting FUs through a buslet were implemented, aiming to minimize the total power consumed using buslets. These range from techniques using minimum spanning trees to more sophisticated structures with constraints on maximum graph distance between connected FUs to hierarchical partitioning.

Using the aforementioned techniques, we obtain significant wirelength (WL) reduction, ranging between 35% and 71%, compared to conventional designs with dedicated interconnects between communicating FU-pairs. The total chip area, including total FU area, also reduces in our designs compared to conventional designs. The power, on the other side of the coin, will increase with buslet size, but sublinearly. Empirical results show that we are able to limit the increment of power consumed by buslets compared to dedicated-interconnect designs, to a logarithmic function of the maximum buslet cardinality.

### CHAPTER 1

#### INTRODUCTION

Our world is full of integrated circuits. It is possible to find them practically everywhere, like in mobiles, cars, televisions etc.; hence, they are now the heart of the modern technology. The integrated circuit (IC) is a cluster embedding a number of very advanced electric circuits. In particular, it will contain a very large number of components like transistors, resistors and capacitors, all interconnected. Among these, the transistor is the fundamental electrical component, at the basement of modern technology. It was invented in 1947 by John Bardeen, Walter Brattain and William Shockley[1], it was revolutionary: it embedded together tiny dimensions, high speed, high reliability and efficiency. Decades after decades, larger and more complex circuits, but at the same time compact and efficient, were this way realized. From the first ICs commercialized in the early 60s, containing just a few of components on the same chip (for example, TAA320 by Philips had two transistors only) and, for this, called Small-Scale Integration devices (SSI), transistors scaling increased thanks to more accurate fabrication technologies (Medium-Scale Integration contained hundreds of transistors on the same chip, Large-Scale Integration hundreds of thousands). Nowadays, the most advanced ICs embed millions of components on an area no larger than a fingernail. The transistors on these chips are realized using up 14 nm technology (like for Intel Core i7-5550U). In order to understand these sizes, we can say that we could fit thousands of transistors inside a red blood cell<sup>1</sup>. This is the era of Very Large-Scale Integrated Circuits (VLSI).

A very famous prediction in this field was done in 1965 by Gordon Moore, head of the research and development office at Fairchild Semiconductor. He speculated [3] that:

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year. Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years."

G. Moore, 1965

Today we have reached physical limits of transistor scaling: we need to handle problems like leakage power consumption, limited range of gate metals, limited available materials for modeling the channel due to scaling degree and, most important, atomic dimension about to be reached<sup>2</sup>. Keep on scaling transistors (trend known as *More Moore*) is unsustainable. However, nowadays a huge work of research for allowing transistor scaling is done. One of the

<sup>&</sup>lt;sup>1</sup>A human blood cell (erythrocyte) has approximately a  $50\mu m^2$  area[2]. From this, we can see that we have three magnitude orders of difference between the size of an erythrocyte and a modern transistor.

$<sup>^{2}</sup>$ Nowadays the used technology is 14 nm (as stated before) while we know that a silicon atom has a Van Der Waals radius of 220 pm. This means that a transistor is realized with less than a hundred of silicon atoms. Furthermore, we can not have transistors too much close each other in order to avoid mutual electric field influence.

most promising among these relies on spin state electron usage, called *spintronics*[4], but there are also other possibilities like tunnel junctions[5][6][7] and new studies on nano-wire geometries[8][9]. The use of these new technologies in order to produce new ICs and, for this, making the transistor scaling trend keep on increasing is known as *More than Moore*.