Novel Discrete Optimization Techniques with Applications to Complex

Physical Synthesis Problems in EDA

BY

HUAN REN B.S., Zhejiang University, Hangzhou, China, 2005 M.S. University of Illinois at Chicago, Chicago, IL, 2011

## THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2012

Chicago, Illinois

Defense Committee:

Shantanu Dutt, Chair and Advisor Wenjing Rao Kaijie Wu John Lillis, Computer Science Prashant Banerjee, Mechanical and Industrial Engineering

## ACKNOWLEDGMENT

I would like to thank my advisor Prof. Shantanu Dutt for all the discussions, guidance and ideas on my Ph.D research during the past six and a half years (the last one year of which I was working full time, first at Intel, and then more recently at Synopsys; my interactions with Prof. Dutt continued during this time). This research and thesis could not possibly have been completed without his tremendous help. I would also like to extend my gratitude to my dissertation committee, Prof. Wenjing Rao, Prof. Kaijie Wu, Prof. John Lillis and Prof. Prashant Banerjee for valuable suggestions on shaping my thesis.

This thesis is dedicated to my parents. My family has always been the source of my strength and inspiration.

Thanks to all my former and current colleagues from the ECE department and DART Lab for their support within academics and beyond it.

HR

# TABLE OF CONTENTS

# **CHAPTER**

| 1        | INTROE  | DUCTION                                                         |

|----------|---------|-----------------------------------------------------------------|

|          | 1.1     | Physical Synthesis                                              |

|          | 1.2     | Design Metrics                                                  |

|          | 1.2.1   | Delay                                                           |

|          | 1.2.2   | Power                                                           |

|          | 1.2.3   | Yield                                                           |

|          | 1.2.4   | Area                                                            |

|          | 1.3     | Physical Synthesis Transforms                                   |

|          | 1.4     | Previous Work in Physical Synthesis                             |

|          | 1.4.1   | Methods for Applying A Single Transform                         |

|          | 1.4.2   | Methods for Applying Multiple Transforms                        |

|          | 1.5     | Contributions                                                   |

| <b>2</b> | MIN-CO  | ST NETWORK FLOW BASED PLACEMENT ALGO-                           |

|          | RITHMS  |                                                                 |

|          | 2.1     | Basics of Min-Cost Network Flow                                 |

|          | 2.2     | Timing Driven Incremental Placement    20                       |

|          | 2.2.1   | Network Structure                                               |

|          | 2.2.2   | Vertical Arc Structures                                         |

|          | 2.2.3   | Timing-Driven Cost Functions26                                  |

|          | 2.3     | Flow Discretization for Legal Incremental Placement Solution 27 |

|          | 2.3.1   | Discrete Flow Requirement in Vertical Arcs                      |

|          | 2.3.2   | Split Flows                                                     |

|          | 2.3.3   | Satisfying White Space Constraints                              |

|          | 2.3.4   | Violation and Thrashing Control Policies                        |

|          | 2.4     | Experimental Results                                            |

| 3        | THE DIS | SCRETIZED NETWORK FLOW METHOD 47                                |

|          | 3.1     | The Option Selection Problem                                    |

|          | 3.2     | Discretized Network Flow Concepts                               |

|          | 3.2.1   | The Network Flow Graph Substructure for DNF                     |

|          | 3.2.2   | The Complete Optimization Graph                                 |

|          | 3.2.3   | Valid Flow and Flow Cost                                        |

|          | 3.3     | Network Flow Graph for Constraint Satisfaction 60               |

|          | 3.3.1   | Flow Amount and Arc Capacity in Ct-subgraphs                    |

|          | 3.3.2   | Bin Capacity Constraints                                        |

|          | 3.3.3   | Circuit Delay Constraint                                        |

# TABLE OF CONTENTS (Continued)

# **CHAPTER**

| $3.4 \\ 3.4.1$    | Complete Option Selection Network Flow Model               |

|-------------------|------------------------------------------------------------|

|                   | PLYING DNF TO VARIOUS PHYSICAL SYNTHESIS PROB-             |

| <b>LEN</b><br>4.1 | Solving the Timing-Driven Physical Synthesis Problem Using |

|                   | DNF                                                        |

| 4.1.1             | 1                                                          |

| 4.2               | Solving Power-Driven Physical Synthesis Problems Using DNF |

| 4.3               | Satisfying Voltage Island Constraints                      |

| 4.3.1             |                                                            |

| 4.3.2             |                                                            |

| 4.4               | Experimental Results                                       |

| 4.5               | Solving the Yield-Driven Physical Synthesis Problems Using |

|                   | DNF                                                        |

| 4.5.1             |                                                            |

| 4.5.2             | v                                                          |

| 4.6               | Experimental Results                                       |

| DN                | F'S APPLICATION TO 0/1 ILP AND INLP PROBLEMS .             |

| 5.1               | DNF Modeling                                               |

| 5.2               | Experimental Results                                       |

| ΑN                | EW DYNAMIC PROGRAMMING METHOD WITH WEAK                    |

|                   | MINATION FOR TACKLING MANY CONSTRAINTS                     |

| 6.1               | Weak-Domination Based Dynamic-Programming                  |

| 6.1.1             |                                                            |

| 6.1.2             | 8                                                          |

| 6.1.3             |                                                            |

| 6.1.4             |                                                            |

| 6.2               | Results of Applying Dynamic Programming with WD to $0/1$   |

|                   | INLP Problems                                              |

| CIT               | ED LITERATURE                                              |

| VIT               | A                                                          |

| V I I             | <b>A</b>                                                   |

# LIST OF TABLES

| TABLE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Ι     | THE CRITICAL PATH DELAY CALCULATED USING THE $\gamma$ NET DELAY MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4          |

| II    | PERCENTAGE TIMING IMPROVEMENTS OF MAX-FLOW HEUD<br>TIC, MIN-COST HEURISTIC WITH DIFFERENT PATH LENGTH<br>LIMITS AND THE RANDOM SELECTION APPROACH FOR S-<br>PLIT FLOW PREVENTION                                                                                                                                                                                                                                                                                                                                                                                       | RIS-<br>32 |

| III   | PLACED BENCHMARK CIRCUIT CHARACTERISTICS. "CRIT.<br>LEN." IS THE # OF CELLS IN THE MOST CRITICAL PATH,<br>AND "AVG. LEN." IS THE AVERAGE NUMBERS OF CELLS<br>AMONG ALL CRITICAL PATHS. THE BENCHMARK NAMES<br>WITH TD AS THE PREFIX WERE PLACED BY TD-DRAGON<br>AND THE REST BY DRAGON. THE "DELAY" COLUMN GIVES<br>THE CRITICAL PATH DELAY                                                                                                                                                                                                                            | 41         |

| IV    | TIMING AND WL RESULTS OF OUR INCREMENTAL PLACER<br>FOR A 3% WS CONSTRAINT COMPARED TO INITIAL PLACE-<br>MENTS DONE BY DRAGON 2.23; SEE TABLE III FOR INITIAL<br>PLACEMENT RESULTS. THE 4'TH AND 5'TH COLUMNS ARE<br>THE GLOBAL PLACEMENT (TAN) RESULTS FOR A PURELY<br>TD COST. THE 6'TH AND 7'TH COLUMNS ARE THE FINAL<br>RESULTS (AFTER DETAILED PLACEMENT) FOR A PURE-<br>LY TD A COST. THE LAST TWO COLUMNS ARE THE RE-<br>SULTS WHEN USING A COMBINED WIRE LENGTH AND T-<br>D COST. POSITIVE NUMBERS MEAN IMPROVEMENT, AND<br>NEGATIVE NUMBERS MEAN DETERIORATION | 42         |

| V     | INCREMENTAL PLACEMENT RESULTS COMPARED TO INI-<br>TIAL PLACEMENT BY TD-DRAGON; SEE TABLE III FOR INI-<br>TIAL TD PLACEMENT RESULTS. POSITIVE NUMBERS MEAN<br>IMPROVEMENT, AND NEGATIVE NUMBERS MEAN DETERI-<br>ORATION.                                                                                                                                                                                                                                                                                                                                                | 43         |

# LIST OF TABLES (Continued)

# TABLE

# PAGE

| VI   | RESULTS USING THE SAME DELAY MODEL AS [1]. THE RUN-<br>TIME IS SIMILAR TO USING OUR DELAY MODEL. POSITIVE<br>NUMBERS MEAN IMPROVEMENT, AND NEGATIVE NUMBER-<br>S MEAN DETERIORATION                                                                                                                                                                                                       | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| VII  | COMPARING DFP TO THE NTU PLACER. POSITIVE NUM-<br>BERS MEAN IMPROVEMENT, AND NEGATIVE NUMBERS MEAN<br>DETERIORATION                                                                                                                                                                                                                                                                       | 44 |

| VIII | THE TRANSFORMS IN CT-SUBGRAPHS FOR DIFFERENT TYPE-<br>S OF P-TERMS IN THE TIMING CONSTRAINT FUNCTION                                                                                                                                                                                                                                                                                      | 70 |

| IX   | RESULTS FOR OUR METHOD DNF AND FOR A SEQUEN-<br>TIAL APPLICATION OF TRANSFORMS. THE COMPARISONS<br>ARE TO INITIAL PLACEMENTS BY DRAGON 2.23 (SEE TA-<br>BLE III FOR INITIAL PLACEMENT RESULTS). $\%\Delta T$ IS THE<br>PERCENTAGE TIMING IMPROVEMENT, $\%\Delta A$ AND $\%\Delta WL$<br>ARE THE PERCENTAGE CHANGES OF TOTAL CELL AREA<br>AND WL, RESPECTIVELY (A NEGATIVE VALUE INDICATES |    |

| Χ    | DETERIORATION)                                                                                                                                                                                                                                                                                                                                                                            | 79 |

|      | VOLTAGE ISLANDS GENERATED BY SEQ-STD IS ALWAYS 16.                                                                                                                                                                                                                                                                                                                                        | 90 |

## LIST OF TABLES (Continued)

TABLE

- XI THE AVERAGE POWER IMPROVEMENTS WITH FOUR TRANS-FORMS AND FOUR  $V_{DD}$ 'S FOR THE MULTIPLE  $V_{DD}$  TRANS-FORM. THE COMPARISONS ARE TO AN INITIAL DESIGN WITH SINGLE  $V_{DD}$  AND  $V_{TH}$  OBTAINED THROUGH "DESIGN COMPILER" FOR ISCAS'89 BENCHMARKS (SEE CAPTION OF TABLE X FOR DETAILS), AND GIVEN WITH THE BENCH-MARKS FOR FARADAY BENCHMARKS. A POSITIVE NUM-BER INDICATES IMPROVEMENT. THE NUMBER OF VOLT-AGE ISLANDS GENERATED BY THE SEQ-STD IS ALWAYS 16.

- XII DNF'S POWER AND DELAY IMPROVEMENTS OVER SYNOP-SYS'S IC COMPILER (ICC) FOR LARGE ISCAS'89 BENCHMARK-S USING DUAL  $V_{DD}$ 'S. BOTH SETS OF RESULTS ARE FOR POST DETAILED-PLACEMENT BUT PRE-ROUTING DESIGN-S. NEGATIVE VALUES MEAN DETERIORATION. "OUR REP." ("ICC'S REP.") IS DNF'S IMPROVEMENT CALCULATED US-ING OUR (ICC'S) DELAY/POWER MODELS. THE RUN TIMES OF BOTH METHODS ARE ALSO GIVEN, THOUGH THEY ARE PROBABLY NOT COMPARABLE FOR THE FOLLOWING REA-SON: ICC IS EVEN FASTER THAN THE SEQUENTIAL METH-ODS CODED BY US BY A FACTOR OF ABOUT 5, WHICH INDI-CATES THAT VARIOUS EFFICIENT DATA STRUCTURES AND COMPILER OPTIMIZATIONS HAVE PROBABLY BEEN USED FOR ICC THAT HAVE NOT BEEN USED IN OUR CODES, AND WHICH CAN POTENTIALLY REDUCE THE RUNTIME OF D-NF SIGNIFICANTLY.

- XIII YIELD IMPROVEMENT RESULTS FOR THREE STATISTICAL METHODS OVER THE DETERMINISTIC DESIGN (WHOSE YIELD IS 50%). THE DETERMINISTIC DESIGN IS OBTAINED BY OP-TIMIZING THE WORST CASE DELAY. THE  $\%\Delta Y$  COLUMNS GIVE THE PERCENTAGE YIELD IMPROVEMENTS. A POSI-TIVE NUMBER INDICATES IMPROVEMENT. THE TOTAL CEL-L AREA INCREASE CONSTRAINT FOR ALL METHODS IS 0%. THE LEAKAGE POWER CHANGE FROM THE DETERMINIS-TIC DESIGN IS LISTED IN THE  $\%\Delta P_L$  COLUMNS. . . . . . . . . 115

PAGE

93

# LIST OF TABLES (Continued)

# TABLE

PAGE

| XIV | THE RESULTS OF OUR DNF METHOD AND SEVERAL COM-          |     |

|-----|---------------------------------------------------------|-----|

|     | PETING METHODS FOR SOLVING VARIOUS 0/1 IP PROB-         |     |

|     | LEMS. THE "OPT. $GAP(\%)$ " IS THE PERCENTAGE DIFFER-   |     |

|     | ENCE COMPARED TO THE OPTIMAL SOLUTION VALUE. THE        |     |

|     | "SPDUP OVER OPT" IS [THE RUN TIME FOR OPTIMAL SO-       |     |

|     | LUTION]/[OUR RUN TIME], AND THE "SPDUP(10%)" IS [THE    |     |

|     | RUN TIME FOR THE NEAR OPTIMAL SOLUTION]/[OUR RUN        |     |

|     | TIME]. THE UPPER BOUND $\epsilon$ ON THE OPTIMALITY GAP |     |

|     | FOR (GUARANTEED) NEAR-OPTIMAL SOLUTIONS IS ALWAYS       |     |

|     | 10%.                                                    | 123 |

| XV  | THE RESULTS OF OUR METHOD, THE DP METHOD WITH           |     |

|     | WEAK DOMINATION, AND SEVERAL COMPETING METH-            |     |

|     | ODS FOR SOLVING CONVEX AND NON-CONVEX 0/1 INLP          |     |

|     | PROBLEMS.                                               | 134 |

|     |                                                         |     |

# LIST OF FIGURES

| <b>FIGURE</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PAGE |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

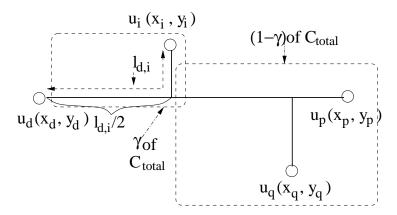

| 1             | The $\gamma$ net delay model for post-placement unrouted nets; $C_{total}$ is the total (net and load) capacitance seen by the driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3    |

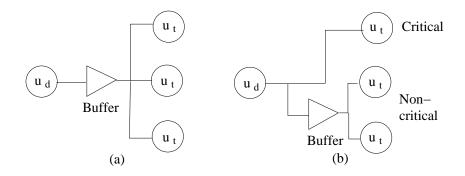

| 2             | Two types of buffers. (a) Type 1 buffer for improving drive capability.<br>(b) Type 2 buffer for isolating non-critical sinks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10   |

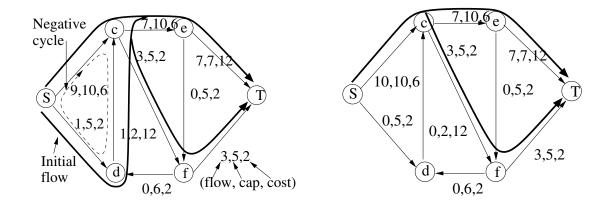

| 3             | (a) An initial flow of 10 units from source $(S)$ to sink $(T)$ is shown by curved dark lines. Arc labels are arranged as $(flow, capacity, cost)$ . (b) The new flow after flow augmentation in the negative cycle in [a]                                                                                                                                                                                                                                                                                                                                                                                      | 20   |

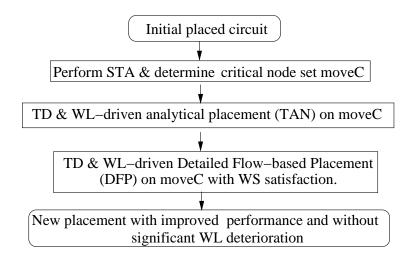

| 4             | The flow of our TD incremental placer FlowPlace. The detailed content<br>of each timing-driven step including WL consideration will be introduced<br>in different sections.                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21   |

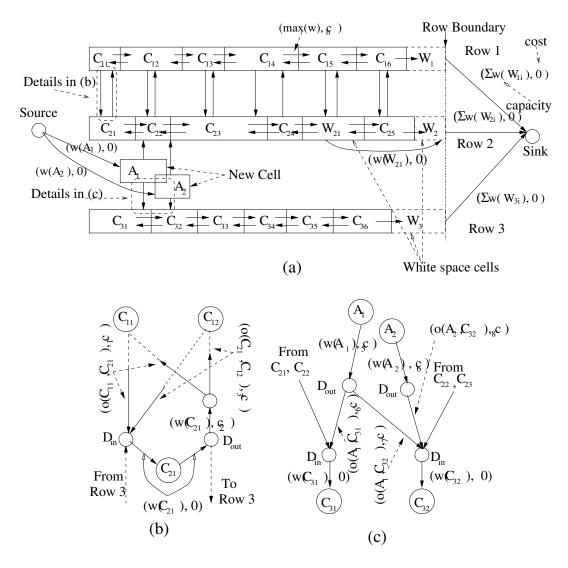

| 5             | (a) The high-level network flow graph for placing cells $A_1, A_2$ in legal positions; $w(u)$ is the width of a cell $u$ . (b) Details of flow graph structure for vertical flows between cell pairs $(C_{11}, C_{21})$ and $(C_{12}, C_{21})$ ; (c) Similar details of the flow graph structure for flows from the new cells into vertically adjacent row cells.                                                                                                                                                                                                                                               | 24   |

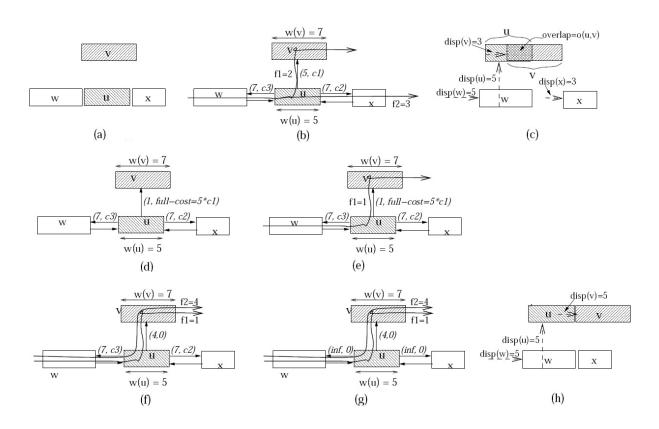

| 6             | (a) Initial placement. (b) "Regular" cost and capacity of vertical arc $(u, v)$ and two flows through cell $u$ . (c) The physical translation of this flow leading to inaccurate incremental placement of affected cells; $disp(v)$ is the displacement distance of $v$ . (d)-(h) New cost, capacity structure of arc $(u, v)$ with dynamic update, resulting in a flow more closely mimicking the corresponding physical movement of cells, and the final accurate incremental placement of affected cells in (h). The dashed arrows in (c) and (h) represent displacements of cells at the end of the arrows. | 28   |

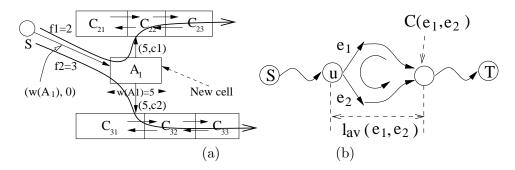

| 7             | (a) Split flow through new cell A1. (b) Diverting flow from $e_1$ to $e_2$ in a split flow situation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31   |

| 8             | Pseudo code of the violation policy check that is performed for each flow augmentation in a cycle in each network flow iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36   |

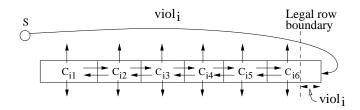

| 9             | The violation correction structure; $S$ is the source of the network graph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38   |

# LIST OF FIGURES (Continued)

# **FIGURE**

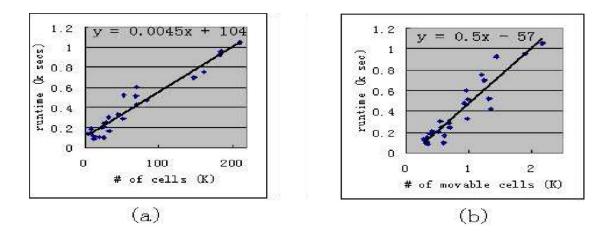

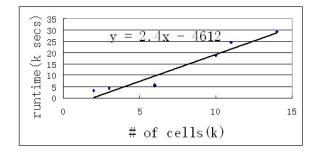

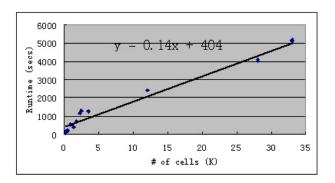

| 10 | (a) Run time versus total number of cells. (b) Run time versus total number of movable cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

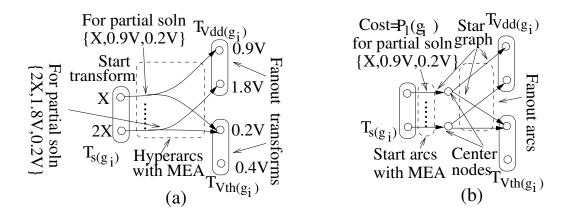

| 11 | (a) The conceptual structure of ot-subgraphs for p-term $P_l(g_i)$ . (b) Actual network flow graph implementation of the conceptual subgraph in [a], in which hyperarcs are modeled by star graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52 |

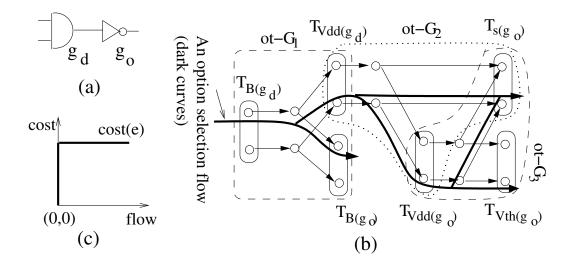

| 12 | (a) A simple net $n_i$ with gate $g_d$ driving gate $g_o$ . (b) The power OG for the net in [a]. An option selection flow is shown by dark curves. (c) The step cost function of an arc $e$ in the OG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55 |

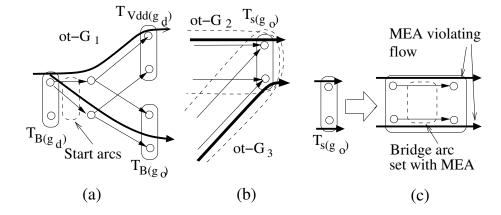

| 13 | Flows violating PSE and OE requirements. All flows are shown by dark<br>arcs. (a) A flow in an ot-subgraph that satisfies the option exclusivity<br>(OE), but violates the partial solution exclusivity (PSE). (b) Flows in<br>two ot-subgraphs ot- $G_2$ and ot- $G_3$ that select different options for the<br>common transform $T_{s(g_o)}$ . The PSE requirement is satisfied, but the OE<br>is violated. (c) Bridge arc structures and MEA constraints are used to<br>satisfy the OE requirement. The flow in [b] extended to the bridge arc<br>structure of $T_{i3}$ violates the MEA constraint on the bridge arcs, and<br>therefore will never occur.                                                                      | 58 |

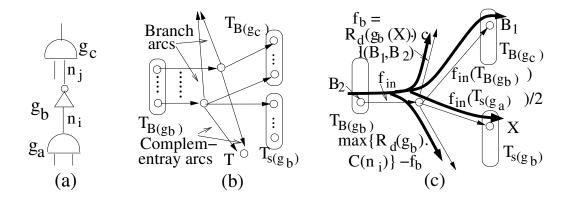

| 14 | (a) An example circuit. (b) The ct-subgraph for delay p-term $R_d(g_b)C(n_j)$ .<br>(c) The flow distribution in the ct-subgraph shown in [b].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63 |

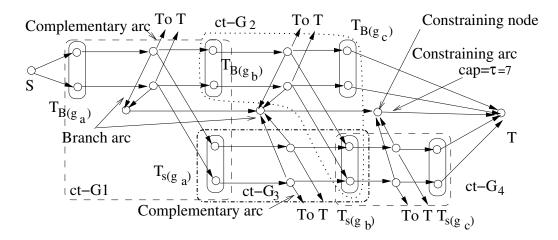

| 15 | The delay CG of the circuit in Figure 14(a) for the constraint $D(n_i) + D(n_j) \leq \tau$ . $ct$ - $G_1$ is for p-term $R_d(g_a)C(n_i)$ , $ct$ - $G_2$ is for p-term $R_d(g_b)C(n_j)$<br>( $ct$ - $G_2$ is shown in detail in Figure 14(b)), $ct$ - $G_3$ is for p-term $R_d(g_a)C(g_b)$ , and $ct$ - $G_4$ is for p-term $R_d(g_b)C(g_c)$                                                                                                                                                                                                                                                                                                                                                                                        | 65 |

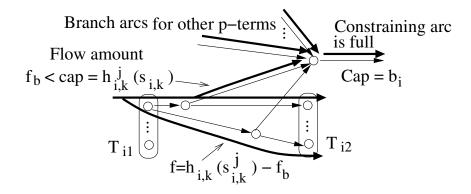

| 16 | A resulting invalid flow in a ct-subgraph when the selected options vio-<br>lates some constraint $H_i \leq b_i$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68 |

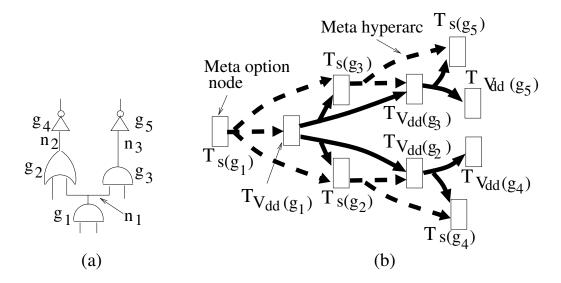

| 17 | (a) A subcircuit with three nets and five gates. (b) A part of the COSG for the subcircuit in [a] after combining the power OG and the circuit delay CG. For clarity we only show supply voltage and cell sizing transforms. Each meta option node represents the set of option nodes for a transform; each meta-hyperarc represents the set of hyperarcs in a subgraph. The dashed meta-hyperarcs are delay ct-subgraphs for circuit delay p-terms of type $R_d(n_k)C(g_k)$ for the three nets in [a], where $R_d(n_k)$ is the driving resistance of $n_k$ and $C(g_k)$ is the input capacitance of a sink cell in $n_k$ . The solid meta-arcs are power ot-subgraphs for power p-terms $P_c$ in Equation 1.7 for the three nets. | 71 |

|    | $\mathbf{p}$ terms $\mathbf{r}_c$ in Equation 1.1 for the three fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

# LIST OF FIGURES (Continued)

# **FIGURE**

# PAGE

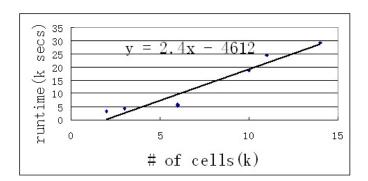

| 18 | Runtime plot of the DNF method versus the number of cells when applying four transforms to perform power optimization.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

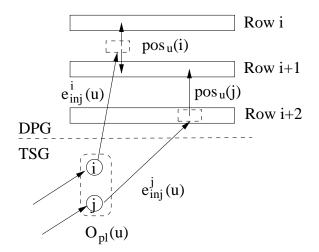

| 19 | Placement injection arcs from different placement options of a cell $\boldsymbol{u}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78  |

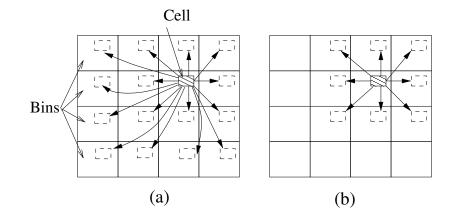

| 20 | (a) Possible inter-bin movement options for a cell. (b) In our implementation, cell movements are limited to adjacent bins.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82  |

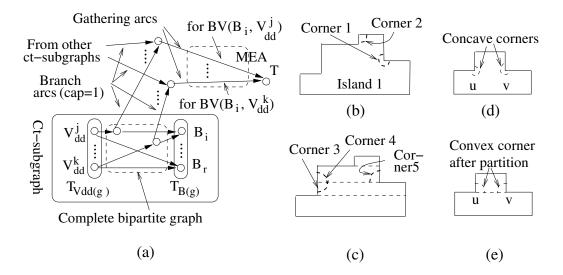

| 21 | (a) A ct-subgraph and associated structure for satisfying the iso-bin- $V_{dd}$ constraint. The branch arcs here have cap=1. (b) Zigzag shaped region formed by voltage boundaries. (c) Rectangular voltage islands generated in it. (d) Two concave corners at intersection points $u$ and $v$ in natural islands that are collinear. (e) After partitioning the two concave corners, two convex corners are generated.                                                                                                                                                    | 84  |

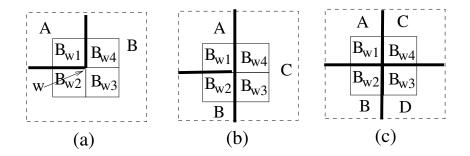

| 22 | Three possible intersection patterns of voltage boundaries (indicated by thick lines) at a bin corner $w$ . The four bins around $w$ are shown                                                                                                                                                                                                                                                                                                                                                                                                                              | 86  |

| 23 | Runtime plot of the DNF method versus the number of cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97  |

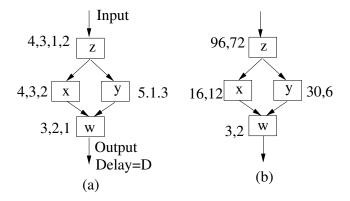

| 24 | (a) The local derivatives of each gate $g$ . They are shown in the order:<br>$\frac{d(A_o(g))}{d(p(g))}, \frac{d(A_o(g))}{d(A_i(g))}, \frac{d(A_i(g_{fo}))}{d(A_o(g))}$ . Note that the last element of this derivative<br>vector is repeated for every fanout gate $g_{fo}$ of $g$ ; thus $z$ with 2 fanout<br>gates has a 4-element derivative vector, while each of the other gates<br>(each with 1 fanout gate) has a 3-element vector. (b) The determined<br>derivatives for each gate $g$ . They are shown in the order: $\frac{dD}{d(p(g))}, \frac{dD}{d(A_i(g))}$ . | 102 |

| 25 | Yield optimization using iterative Taylor's series approximation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 104 |

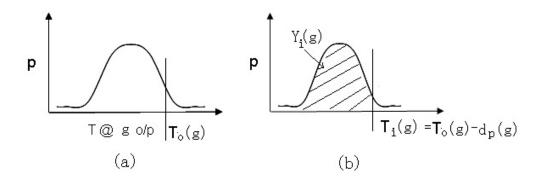

| 26 | The process for propagating $Y_o(g)$ to $Y_i(g)$ . (a) The delay PDF at the output of $g$ . (b) The propagated $T_i(g)$ and $Y_i(g)$ at the input of $g$                                                                                                                                                                                                                                                                                                                                                                                                                    | 105 |

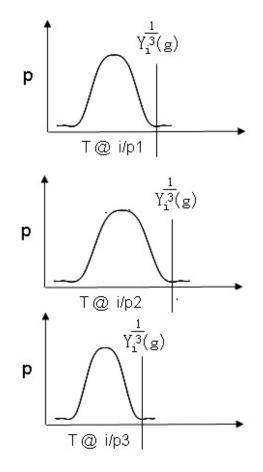

| 27 | The criticality comparison of three famins to gate $g$ . The delay PDFs at the three inputs i/p1, i/p2 and i/p3 of $g$ are shown. The middle input i/p2 has the largest delay at yield point $(Y_i(g))^{1/3}$ , and hence is critical.                                                                                                                                                                                                                                                                                                                                      | 117 |

| 28 | Yield optimization using an iterative Taylor's series approximation and optimization approach in a binary-search framework.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 118 |

| 29 | Runtime plot of the PBM method versus the $\#$ of cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 118 |

# LIST OF FIGURES (Continued)

# **FIGURE**

## PAGE

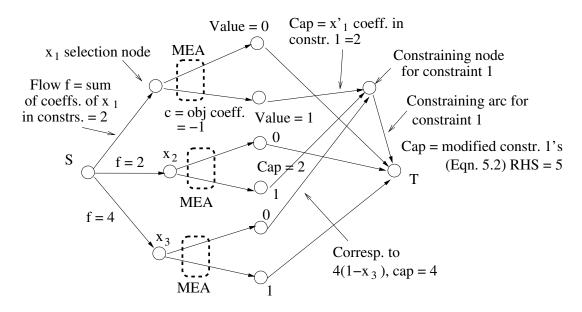

| 30 | A DNF structure for the ILP problem given in Equation 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                            | 120 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

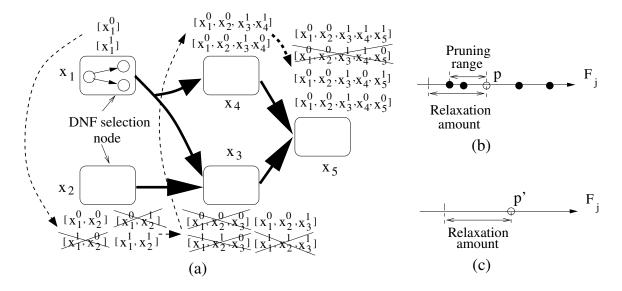

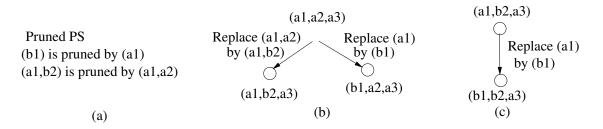

| 31 | (a) The DP process: The DNF optimization graph $G_{opt}$ shown at the level of MEA meta-nodes and meta-arcs (see Chapter 3). Dashed arcs indicate the processing order of variables. For each variable $x_i$ , the PS's option vectors after combining options of $x_i$ are shown. The pruned PS's are crossed off. (b) The weak domination condition: Dark nodes are the $F_j$ values of PS's pruned by PS $p$ . (c) For $p' \succ p$ , its relaxation amount must cover the pruning range of $p$ . | 125 |

| 32 | An example restoration process for a problem with three variables $v_1, v_2, v_3$ .<br>Each variable $v_i$ has two options $a_i$ and $b_i$ . (a) The pruned partial solutions that are recorded. (b) The restoration process on solution $(a_1, a_2, a_3)$ with the pruned PS's in [a]. (c) A further restoration process on a solution $(a_1, b_2, a_3)$ generated from the restoration in [b]                                                                                                      | 132 |

## SUMMARY

VLSI circuit designs are very challenging optimization problems in the electronic design automation (EDA) domain. There are usually 100K's to tens of millions of components in such circuits, and a wide range of metrics that need to be considered. A post place-and-route (P&R) phase called "physical synthesis" (PS) is a crucial stage where effective optimization of VLSI circuits can be performed using accurate interconnect metrics. Many design transforms have been developed to perform different types of optimizations in PS. These include cell replacement, cell sizing, cell replication, buffer insertion, supply voltage assignment and threshold voltage assignment. We have developed a novel and efficient method called "discretized network flow (DNF)" for the simultaneous application of multiple transforms on the entire circuit with tractable runtimes. This enables us to achieve an average of 10% and 16% improvement for delay and power, respectively, compared to the state-of-the-art academic or industry tools that apply the transforms sequentially. Application of DNF to the timing yield PS problem resulted in a relative yield improvement of about 16% over a state-of-the-art academic method.

DNF was also applied successfully to solve 0/1 integer linear programming problems, achieving an average speedup of 19X over the state-of-the-art academic tool SCIP with a similar optimality gap. Besides DNF, we also developed a dynamic programming method using the novel concept of weak domination for solving 0/1 integer non-linear programming problems with a guaranteed optimality gap. Compared to a state-of-the-art academic tool Bonmin with the same optimality gap, our method achieves a speedup of about 2X.

## CHAPTER 1

## INTRODUCTION

## 1.1 Physical Synthesis

As the sizes of cells in an integrated circuit keep shrinking and the number of cells keeps increasing, the length of physical interconnects between cells on a chip are becoming much larger than the dimensions of cells. Therefore, interconnects are taking more and more important roles in determining many critical metrics for integrated circuits. As a result, a design that satisfies various constraints after logic synthesis will not necessarily meet these constraints after placeand-route due to wire delay and wire power. To handle this problem, *physical synthesis* has emerged as a necessary tool for design closure. Physical synthesis begins with a placed or routed netlist, in which more accurate interconnect info is available than in the logic synthesis stage. It tries various optimization methods to the netlist, and the goal is to satisfy constraints on a set of important metrics, and optimize another set of metrics. It uses the optimization methods that are used in the logical synthesis stage as well as methods that are only applicable in placeand-route stage like changing cell position. One main difference between physical synthesis and logical synthesis is that physical synthesis will take available interconnect information into account when performing optimization.

In current industry place-and-route flow, to ensure design closure of complex circuits, physical synthesis is usually performed multiple times, one after each major step that changes the physical interconnects. Typical times that a physical synthesis is performed are after placement, after clock tree synthesis, and after routing. Each time, the physical synthesis is performed to eliminate the constraint violations produced in the previous stage.

In the next section, we will first go through the important design metrics that are usually considered in physical synthesis.

### 1.2 Design Metrics

Modern integrated circuit is a very complex system. In order for it to function as expected, many different metrics need to be considered. We will provide the definitions and calculation methods for these metrics in this section.

## 1.2.1 Delay

The delay of a path in a circuit can be divided into two parts: the cell internal delay, and the net delay. The cell internal delay is usually given in the library. For post-route design, the net delay can be calculated using the Elmore delay model [2], or more accurately the Arnoldi [3] delay model. In post-placement but pre-route design, the capacitance, resistance and length of a net is usually estimated using the net's bounding box, and usually simple lumped capacitance and resistance model is used in delay calculation.

We have proposed a novel post-placement pre-route delay model called the  $\gamma$  net delay model in [4] that has better correlation to the post-route delay. In this mode, for an unrouted net, we assume the net routing pattern with a single trunk to the furthest sink with branches off this trunk to the other sinks, as shown in Figure 1. For a net  $n_j$  with driver  $u_d$ , and  $k-1 \ge 1$ sinks (k is the total number of pins in  $n_j$ ), let  $R_d$  be the driving resistance of  $u_d$ ,  $C_g$  the load

Figure 1. The  $\gamma$  net delay model for post-placement unrouted nets;  $C_{total}$  is the total (net and load) capacitance seen by the driver.

capacitance of a sink pin<sup>1</sup>, r(c) the unit wire resistance (capacitance),  $L(n_j)$  the total WL of  $n_j$ , and  $l_{d,i}$  the interconnect length connecting driver  $u_d$  to sink  $u_i$ ; see Figure 1. Referring to this figure and considering a sink  $u_i$  in  $n_j$ , the delay  $D(u_i, n_j)$  to it (using the Elmore delay model) from the driver  $u_d$ , consists of three parts:

$$D_1(n_j) = R_d(c \cdot L(n_j) + (k-1)C_g)$$

(1.1)

$$D_2(u_i, n_j) = \frac{rc}{2} \cdot l_{d,i}^2 + r \cdot l_{d,i}C_g$$

(1.2)

$$D_3(u_i, n_j) = r \cdot (l_{d,i}/2)((1 - \gamma + \gamma/2)(c \cdot L(n_j) + (k - 2)C_g)$$

(1.3)

<sup>&</sup>lt;sup>1</sup>For simplicity of exposition, we assume uniform loads for all sink pins, though clearly our net-delay model also applies to non-uniform loads.

| Circuit                   | mac32 | $\operatorname{matrix}$ | vp2 | mac64 | %error |

|---------------------------|-------|-------------------------|-----|-------|--------|

| routed delay (ns)         | 3.4   | 3.8                     | 4.3 | 6.7   | 0      |

| $\gamma$ delay model (ns) | 3.4   | 4.3                     | 4.5 | 7.0   | 5.6    |

| ΤA | BL | Æ | Ι |

|----|----|---|---|

|    |    |   |   |

### THE CRITICAL PATH DELAY CALCULATED USING THE $\gamma$ NET DELAY MODEL.

$$D(u_i, n_j) = D_1(n_j) + D_2(u_i, n_j) + D_3(u_i, n_j)$$

(1.4)

where  $\gamma \leq 1$ . Note that the  $D_1(n_j)$  delay component is common to all sinks of  $n_j$ , which is due to the driving resistance of the driver and total capacitance load of wire and sinks.  $D_2(u_i, n_j)$  is the wire RC delay from driver to a sink  $u_i$ . The idea behind the 3rd delay component  $D_3(u_i, n_j)$ is that without an exact route, we estimate that if  $u_i$  lies in the initial  $\gamma$  fraction of the HPBB of  $n_j$  starting from the driver position, then, on the average, half of the interconnect length  $l_{d,i}$ lies on the main trunk of the estimated route, and it "sees" the entire wire and sink capacitance of the rest of the  $(1 - \gamma)$  fraction of the net. Furthermore, this main trunk part of the  $(u_d, u_i)$ interconnect can also see incremental portions of the  $\gamma$  fraction of the net capacitance, i.e., from the branch point to  $u_i$ , which ultimately results in this interconnect seeing a  $\gamma/2$  fraction of the total (load + net) capacitance  $C_{total}$ .

The comparison between the delay estimation using our  $\gamma$ -delay model, and the actual routed delay is provided in Table I. The delay estimation error is only 5.6%, which shows the accuracy of our  $\gamma$  net delay model. Furthermore, our delay model shows 100% fidelity with routed delay.

### 1.2.2 Power

The power consumption of a circuit mainly consists of dynamic power consumption and leakage power consumption. The average dynamic power  $P_d(n_j)$  consumed by a net  $n_j$  with a driving gate  $g_d$  and a set of sink gates  $g_i$  is given by:

$$P_d(n_j) = 0.5f \cdot p_{sw}(n_j) \left(\sum_{g_i \in ip(n_j)} C(g_i) V_{dd}^2(g_d) + V_{dd}^2(g_d) C(n_j)\right)$$

(1.5)

where f is the clock frequency,  $p_{sw}(n_j)$  is the switching probability of the net,  $ip(n_j)$  is the set of sink gates in  $n_j$ ,  $C(g_i)$  is the input capacitance of sink gate  $g_i$ ,  $V_{dd}(g_d)$  is the supply voltage  $V_{dd}$  of drive gate  $g_d$  and  $C(n_j)$  is the total interconnect capacitance of  $n_j$ . The leakage power consumption  $P_l(g_i)$  of a gate  $g_i$  can be given as [5]:

$$P_l(g_i) = V_{dd}(g_i) W I_s \cdot e^{-V_{th}(g_i)/V_o}$$

(1.6)

where W is the transistor width and is proportional to the gate size,  $I_s$  is the zero-threshold leakage current and a constant,  $V_{th}(g_i)$  is the threshold voltage  $V_{th}$  of  $g_i$ , and  $V_o$  is the constant subthreshold slope. Hence,  $P_l(g_i)$  is linearly proportional to the gate size and  $V_{dd}$ , and inversely exponentially proportional to  $V_{th}$ .

It should be noted that when a low- $V_{dd}$  gate  $g_d$  drives a high- $V_{dd}$  gate  $g_i$ , a *level shifter/converter* needs to be inserted between them to avoid deterioration of the noise margin. Adding a level

shifter increases power consumption in three ways: 1) level shifters consume power, 2) the charging voltage for the interconnect between the level shifter and the sink cell  $g_i$  is increased, and 3) the charging voltage for the sink cell is increased; the last two increases are due to the charging voltage changing from  $V_{dd}(g_d)$  to  $V_{dd}(g_i)$ ). The second effect can be eliminated by putting the level shifter close to the sink cell so that the interconnect length between the level shifter and the sink cell is almost 0. Let the  $P_s$  be the power consumption of a level shifter given in the library. To account for the first and third effects, the power term for charging a sink gate  $g_i$   $(C(g_i)V_{dd}^2(g_d))$  in Equation 1.5 should be changed to the following formulation denoted by  $P_c(g_d, g_i)$ :

$$P_{c}(g_{d}, g_{i}) = \begin{cases} C(g_{i})V_{dd}^{2}(g_{d}) & \text{if } V_{dd}(g_{d}) \ge V_{dd}(g_{i}) \\ P_{s} + C(g_{i})V_{dd}^{2}(g_{i}) & \text{if } V_{dd}(g_{d}) < V_{dd}(g_{i}) \end{cases}$$

(1.7)

## 1.2.3 Yield

With the shrinking feature sizes of integrated circuits, it is becoming increasingly difficult to control critical device parameters during fabrication. Growing process variability has been observed in gate lengths, oxide thicknesses and doping both across dies and within the same die. Besides such process variations, temperature and supply voltage variability also causes significant performance and power variations to arise between chips with the same design. The *yield* of a design is the percentage of produced chips with the same design that can satisfy all requirements. It is important to develop design optimization techniques in logic synthesis and physical synthesis that optimize critical metrics (e.g., timing and power) that take these process/voltage/temperature based circuit parameter variations into account so that the yield of resulting chips (the percentage of chips that meet the desired metric goals) is maximized.

To show the delay calculation when variation is considered, let us take a simple lumped delay model. The delay  $d_o(g)$  at a gate g can be modeled as:

$$d_o(g) = d(g) + r(g) \times \sum fanoutsc(g_{fo})$$

(1.8)

where d(g) is the intrinsic gate delay of g, r(g) is the driving resistance of g, and  $c(g_{fo})$  is the input capacitance of a fanout gate  $g_{fo}$ . When random variations in these parameters are considered, the corresponding gate delay with variability  $d_v(g)$  can be written as:

$$d_v(g) = d_o(g) + \Delta d(g) + \Delta r(g) \times \sum fanoutsc(g_{fo}) + r(g) \times \sum fanouts\Delta c(g_{fo})$$

(1.9)

where  $\Delta d(g)$ ,  $\Delta r(g)$  and  $\Delta c(g_{fo})$  are the random variations on parameters d(g), r(g) and  $c(g_{fo})$ , respectively. In this thesis, we assume all random variations have a Gaussian distribution. Hence, the delay at a gate also assumes a Gaussian distribution, since according to the Central Limit Theorem [6], the sum of Gaussian distributions is also a Gaussian distribution.

The delay of a design is the max of delays of all paths in the design, and, obviously, is also a random value when the variation is considered. The technique for obtain the probability distribution function (PDF) of the design delay is called the *statistical timing analysis* (SSTA). In this thesis we are using the SSTA method proposed in [7]. This method approximates the distribution of the maximum of several Gaussian random variables as another Gaussian distribution based on the work in [8]. The detail of the approximation is given below:

Let A and B be two Gaussian variables, and  $(\mu_A, \sigma_A)$  and  $(\mu_B, \sigma_B)$  be their (mean, standard deviation). Also, let us define the following variables:

$$\phi(x) = \frac{1}{\sqrt{2}} e^{-x^2/2}$$

$$\Phi(x) = \int_{-\inf}^{y} \phi(x) dx$$

$$\theta = |\sigma_A - \sigma_B|$$

$$\alpha = (\mu_A - \mu_B)/\theta \qquad (1.10)$$

The mean and standard deviation for the approximating Gaussian distribution of  $\max\{A, B\}$ are:

$$\mu(\max\{A, B\}) = \mu_A \Phi(\alpha) + \mu_B \Phi(-\alpha) + \theta \phi(\alpha)$$

$$\sigma(\max\{A, B\}) = (\mu_A^2 + \sigma_A^2) \Phi(\alpha) + (\mu_B^2 + \sigma_B^2) \Phi(-\alpha)$$

$$+ (\mu_A + \mu_B) \theta \phi(\alpha) - \mu^2$$

(1.11)

Hence, with the above approximation the delay of a circuit also becomes a Gaussian random variable, whose  $\mu$  and  $\sigma$  depend on gate parameters. Given a delay constraint  $D_c$  the following yield objective function is used this thesis:

$$Yd = (D_c - \mu)/\sigma \tag{1.12}$$

It is proved in [7] that the actual yield percentage is a monotonically increasing function of Yd. Hence, optimizing Yd accurately optimizes the final yield.

## 1.2.4 Area

The area of a design can be measured by either the total area of cells in the design or the layout area of the design. The latter one also includes the area of whitespaces in the design that are reserved to alleviate congestion. It is an important metric, since the chip cost is usually proportional to its area.

#### **1.3** Physical Synthesis Transforms

Physical synthesis is usually done through trying various changes on a target design. Through out this thesis, we will call these changes *transforms*. The typical type of transforms include: incremental placement, cell sizing, multiple threshold voltages  $(V_{th})$  assignment, multiple supply voltages  $(V_{dd})$  assignment, two types of buffer insertion and cell replication.

*Incremental Placement* This method can reduce the critical and near critical path lengths by changing the position of cells on these paths. It can also reduce the dynamic power by reducing capacitive loads of high switching frequency wires. The advantage of incremental placement

Figure 2. Two types of buffers. (a) Type 1 buffer for improving drive capability. (b) Type 2 buffer for isolating non-critical sinks.

is that by only focusing on cells connected to critical, near-critical paths or on high switching frequency wires, the run time is greatly reduced compared to performing a new placement, and the optimization is more controllable.

*Cell Sizing.* The size of a cell controls its input capacitance and driving resistance. Changing input capacitances and driving resistances of cells are very effective in improving timing and power. If we are able to implement cells of any size, then the problem of choosing optimal cell sizes for timing can be solved by a convex programming approach. However, since in real standard cell designs, the available cell sizes in a library are limited, the problem is actually a discrete optimization problem, which can be solved by either a fastest descent method or dynamic programming.

Driver Buffer Insertion. Optimal buffer insertion has to take routing information into consideration. However, it is also useful to estimate the effect of buffers at the placement stage so that proper white-spaces can be allocated for adding buffers, and we can know earlier whether the design can meet timing requirements. There are two types of buffer insertions as shown in Figure 2. Type 1 buffer shown in Figure 2(a) is used for improving the drive capability of the driving cell  $u_d$  of a net, and thus is called *driver buffer* in this thesis.

*Isolating Buffer Insertion* The second type of buffers are shown in Figure 2 (b). Its purpose is to isolating non-critical sinks from critical ones.

*Cell Replication.* In cell replication, the driving cell of a net is replaced by two identical replicas, and the fanouts are partitioned into two groups for each replica. Its effect is similar to doubling the driving cell size, but it can also achieve the purpose of separating the non-critical fanouts of a net from its critical ones by connecting them to different replicas. This makes it more effective in improving delay than up-sizing driving cells when a net has large non-critical load.

$V_{th}$  Assignment. Reducing the threshold voltage of a cell is very effective in reducing its leakage power, as the leakage power is exponentially proportional (Equation 1.6) to the threshold voltage. However, a cell with a high threshold voltage also suffers from the increase in driver resistance and internal delay. Hence, in most current cell libraries, a set of different  $V_{th}$ implementations is provided for each cell with certain type and size. Appropriate selection of cells'  $V_{th}$ 's can help satisfy the delay constraint with the least leakage power.

$V_{dd}$  Assignment. Reducing the supply voltage of a cell reduces both its leakage power and switching power efficiently. Since these powers are quadratically and linearly proportional to the supply voltage(Equation 1.5,Equation 1.6). However, reducing the supply voltage also increases the cells driver resistance. Furthermore, using multiple  $V_{dd}$ 's brings in the need for level shifters and the issue of forming voltage island (we will explain this in Chapter 4). This also causes increase in delay, power and area. Hence, smart choices need to be made to satisfy the delay, power and area requirements at the same time.

### 1.4 Previous Work in Physical Synthesis

#### 1.4.1 Methods for Applying A Single Transform

Physical synthesis has been a critical research area in recent years. Many methods have been proposed for efficiently using a single transform.

For cell sizing, it is used to optimize many different metrics like delay, power, area and yield. There are mainly three different types of sizing algorithms: mathematical programming based methods, e.g., [9], dynamic programming based methods, e.g., [10], and sensitivity based techniques, e.g., [11]. The latter two are more suitable for discrete cell sizing. In a recent work, Hu et. al. [10] proposed a dynamic programming method for discrete cell sizing. Their goal is to optimize area under timing constraint. In order to reduce complexity, partial solutions generated go through a similarity check. For each set of similar partial solutions, only a representative partial solution is kept, and others are eliminated. Agarwal et. al. [12] proposed a sensitivity based cell sizing method for yield optimization. The method adjusts cell sizes iteratively based on the cells' yield to area change ratios (sensitivities), and in each iteration the size of the cell with the largest sensitivity is modified. The key issue in the methods is how to determine sensitivity for each cell efficiently. [12] proves that the perturbation caused by a cell size change in the delay CDF (cumulative distribution function) will keep decreasing as it propagates towards the primary outputs. Thus, an upper bound on the sensitivity for a cell size change can be estimated without propagating its corresponding delay perturbation to the outputs. Then, the upper bound is used to efficiently eliminate cells that cannot be the most sensitive cell.

For cell replication, [13] uses it to optimize the circuit delay. It proposed a method of dividing fanouts between the original cells and replicas when the cell is duplicated. The division is based on fanouts' criticalities. It will try to put as many critical fanouts to a separate driver as possible until the fanout load is too large and the delay is becoming worse.

For multiple  $V_{dd}$  assignment, it is usually used for power optimization. The two classic methods for  $V_{dd}$  assignment are: CVS [14], which does not allow low  $V_{dd}$  cells to drive high  $V_{dd}$  cells, and ECVS, which adds level shifters when low  $V_{dd}$  cells drive high  $V_{dd}$  cells. Wu et. al. [15] proposed a slack allocation based method for dual  $V_{dd}$  assignment after placement, in which slacks are assigned to adjacent cells in the layout that are physically distant from critical paths with high  $V_{dd}$  cells in order to facilitate formation of low  $V_{dd}$  islands among these adjacent cells.

For incremental placement, [1] proposed an incremental placement method for improving delay. The method uses mathematic programming to find the best position for cells on the critical path. Then these positions are refined in a detailed placement stage to ensure that there is no cell overlap and that no cell falls between rows.

The two types of buffer insertion is usually used to improving delay. van Ginneken [16] proposed a classical buffer insertion algorithm. It uses dynamic programming which finds the optimal solution for a given Steiner tree. The assumption of the algorithm is that there is only

a single kind of buffer cells. Lillis et al. [17] extends the algorithm to trade off solution quality with buffering resources and use a buffer library with inverters and repeaters

There are not many works that address  $V_{th}$  assignment as a single transform for power minimization, though a few [18–20] use this transform together with other transforms. For cell replication, [13] proposed a method of dividing fanouts between the original cells and replicas based on their criticality, so that the top critical fanouts use a separate driver.

#### **1.4.2** Methods for Applying Multiple Transforms

In order to achieve better physical synthesis quality, it is desirable that all these transforms be applied simultaneously rather than sequentially one after the other. Most combined algorithms simply apply them in sequential order. However, it has been proven in [21] that applying these methods sequentially will produce fairly non-optimal solutions. The simultaneous approach allows for a more globally optimal way of determining the transforms to be used across all cells (the transforms for each cell interact in determining power consumption, delay and other metrics), while the sequential approach, by definition, can at best obtain locally optimal solutions.

Considering multiple transforms simultaneously can, however, significantly increase the problem complexity. Hence, there have been few efforts along this approach, and most of those that consider multiple transforms simultaneously do so for only two transforms. Dhillon [18] and Liu [20] proposed two Lagrange relaxation based non-linear programming methods for power optimization under delay constraint under timing constraint. Multiple  $V_{dd}$ 's and  $V_{th}$ 's were applied in [18], and multiple  $V_{th}$ 's and cell sizing were used in [20]. Gao. et. al. [19] also

employed multiple  $V_{th}$ 's and cell sizing for the same problem. In this technique, linear programming is used, and the non-linear timing and power functions are approximated by piecewise linear functions. To reduce time complexity, both [18] and [19] relax the discrete voltage level and cell size constraints initially when solving the mathematical programming model of the problems. After that, [18] clusters the continuous voltage solutions to several discrete values, and [19] rounds the continuous solution to the nearest available discrete options provided by the library. On the other hand, [20] solves the discrete optimization problem using dynamic programming under the relaxation that different sizes and  $V_{th}$ 's can be selected for the same cell to optimize delays at its different fanouts. Such conflicts are then solved heuristically. In [22], the placement transform is applied, to some degree, simultaneously with other synthesis transforms to improve circuit delay. This is done by incorporating synthesis transforms into different intermediate partition levels of a partition based placement process according to the amount of their potential perturbation to the placement.

To the best of our knowledge, there are only two works that consider more than two transforms. They are both targeting power optimization. The three transforms employed by them are cell sizing, dual  $V_{dd}$ 's, and dual  $V_{th}$ 's. Among them, [23] by Srivastava et al. essentially applies these transforms sequentially rather than simultaneously. On the other hand Chinnery et al. [24] formulated the problem as an ILP problem, with a 0-1 variable indicating whether to switch a cell in the initial design to a possibly good alternative of different size,  $V_{dd}$  and/or  $V_{th}$ . The alternative is chosen based on local incremental improvement, and the ILP is solved with simple rounding-like heuristic. In the industry side, even the state-of-the-art industry tool can only handle these transforms one-by-one in certain sequential order

## 1.5 Contributions

In this thesis, we propose a novel discrete optimization algorithm called the *discretized network flow* (DNF) for solving physical synthesis problems. DNF is developed from the traditional min-cost network flow algorithm. The min-cost network flow problem is a very interesting problem. Though it is essentially a linear programming problem, it can be solved much faster than general linear programming problems [25]. We added novel discretization techniques to this continuous algorithm in order to satisfy various discrete constraints posed in the physical synthesis problems.

The DNF method has the following advantages as far as physical synthesis problems are concerned:

- It is a very general discrete optimization algorithm, and can be applied to solve the physical synthesis problem with almost any known set of transforms.

- It is particularly suitable for solving *option selection problems*. In an option selection problem, for each variable, a set of options a provided. The task is to chose one option for each variable from the set that optimize a given objective function while satisfy another set of constraint functions. Many EDA problems like physical synthesis, high level synthesis and floor planning can be formulated as option selection problems.

- It can handle a wide range of circuit design metrics. The range includes linear metrics like area, non-linear metrics like delay and power, and even metrics without closed form

expression like voltage island number (which we will talk about in Chapter 4). DNF can take these metrics as either an objective function or one of the constraints with upper or lower bounds.

• Most importantly, it inherits the runtime efficiency of the min-cost network flow problem. This enables DNF to tackle the very complex problem of simultaneous application of multiple transforms. We have successfully applied DNF to solve physical synthesis problem using up to five transforms (e.g. for timing optimization, we have used cell replication, two types of buffer insertion cell sizing and incremental placement). Note that previous works use at most three transforms.

Besides physical synthesis problems, DNF can also be applied in many other areas like 0/1 integer linear/non-linear programming, the bioinformatics problem of selecting gene markers for certain disease [26], traveling salesman problems [27] and Boolean satisfiability problems [28]. DNF has achieved high quality results for these problems, and its runtime is faster than the traditional branch-and-bound and branch-and-cut methods. For example, when applied to integer linear programming problem, we saw 1.3X to 86X speed compared to the state-of-the-art solvers with similar solution qualities (we discuss the results further in Chapter 5 and 6).

The rest part of thesis is organized as follows. In Chapter 2, we discuss the basics of the min-cost network flow, and how it can be used to solve the timing-driven incremental placement problem. Timing-driven incremental placement is a typical problem in physical synthesis which considers only the incremental placement transform. In Chapter 3, we gives a more detailed explanation of DNF. The two major issues we discuss there are: 1) how to model a general

physical synthesis problems as a network flow problem, and 2) how to satisfy various discrete requirements in physical synthesis in the continuous network flow model. In Chapter 4, we apply DNF to three different physical synthesis problems: timing optimization, power optimization and yield optimization, in which multiple transforms are considered simultaneously. In Chapter 5, we illustrate the application of DNF to solving the general 0/1 integer linear programming (ILP) problems, and 0/1 integer non-linear programming (INLP) problems. In Chapter 6, we propose an alternative way, dynamic programming using the novel concept of weak domination, to solve 0/1 integer non-linear programming problems. The advantage of this new method is that it can give a guaranteed near optimality bound.

## CHAPTER 2

### MIN-COST NETWORK FLOW BASED PLACEMENT ALGORITHMS

In this chapter, we will illustrate how to use the min-cost network flow to solve the timing driven incremental placement problem.

#### 2.1 Basics of Min-Cost Network Flow

The min-cost network flow problem is a classical network flow problem, which tries to send a given amount of flow through a network graph with the minimum cost. In a network graph, each directed arc has an associated unit flow cost and capacity. Flow on an arc cannot exceed its capacity or become negative. The flow cost of each arc is the flow amount on the arc times the unit flow cost of the arc. An example of the network flow graph and a flow in it is shown in Figure 3

Min-cost flow has found a wide range of applications from traffic system design in the macro scale to the signal routing in a NOC (network-on-chip) system. In practice, the commonly used method for solving min-cost network flow problems is the network flow Simplex method. It is not polynomial bounded in time, but gives the very good average run-time result [25].

The network flow Simplex method is an iterative improvement approach. It starts with an initial flow with the required amount which is not optimal as shown by the example in Figure 3(a). Then it will try to find cycles with negative cost in the graph and augment flows in them as shown in Figure 3(b). After each augmentation, the cost of the flow will be improved.

Figure 3. (a) An initial flow of 10 units from source (S) to sink (T) is shown by curved dark lines. Arc labels are arranged as (flow, capacity, cost). (b) The new flow after flow augmentation in the negative cycle in [a].

It terminates when there is no cycle with negative cost, or no more flow can be augmented in any of such cycles.

### 2.2 Timing Driven Incremental Placement

To illustrate how the min-cost network flow method can be applied in physical synthesis. We will first look at the increment placement transform. The problem we tackle here is to use the incremental placement to optimize the delay of a circuit. More details about this work can be found in [4].

The TD incremental placement problem can be stated as:

**Input:** A placed circuit  $\mathcal{PC}$ , a set *moveC* of new unplaced cells (the scenario of modified cells is handled by deleting them from  $\mathcal{PC}$  and adding them to *moveC*).

**Output:** A completely placed circuit  $\mathcal{PC}'$  in which: (1) there are minimal changes made to the existing placement  $\mathcal{PC}$  in terms of both movements of cells in  $\mathcal{PC}$  and deterioration of placement

Figure 4. The flow of our TD incremental placer FlowPlace. The detailed content of each timing-driven step including WL consideration will be introduced in different sections.

metrics like total wire length (WL), (2) the critical path delay in  $\mathcal{PC}'$  is significantly improved compared to the one in  $\mathcal{PC}$ , and (3) the given WS constraint of  $\epsilon\%$  is satisfied—this means that the maximum row width  $\leq (1 + \epsilon/100) \times l_{avg}$ , where  $l_{avg}$  is the average total cell width in a row and is defined as  $l_{avg} =$  (total cell width in the circuit)/(the number r of rows).

Figure 4 shows the flow of our Timing-driven (TD) incremental placer. We start from a placed circuit and identify all critical and near-critical paths using static timing analysis (STA). Let this set of paths be  $\mathcal{P}$  (we take paths with delay larger than 0.9 of the circuit delay as near-critical paths in our experiments). After  $\mathcal{P}$  is identified, we remove all cells in all nets that lie in  $\mathcal{P}$  from the layout. The removed cells form the cell set *moveC* that will be replaced by our TD incremental placer with the goal of reducing the critical path delay. As in standard placement

flows, our incremental placement method also consists of two stages, global and detailed. In the global stage, our TD analytical placer TAN is used in which moveC constitutes the set of moveable cells. TAN is essentially a sophisticated quadratic solver. It can find positions for cells in moveC that minimize the length of the critical paths.

However, the positions found by TAN will generally be an illegal placement for cells in moveC. The continuous solver of TAN cannot handle the discrete requirement on cell positions: 1) the position of a cell can not fall between rows, and 2) cells cannot overlap with each other. This is where our network flow based detailed placer kicks into the picture. It is able to find legal positions for cells moved in TAN, which minimizes the movement distance from the initial position provided by TAN. In the following sections, we will explain in detail how our timingdriven (TD) detailed flow-based placer (DFP) handles this discrete optimization problem

#### 2.2.1 Network Structure

Once a cell is moved by TAN to between rows, it needs to be moved upward or downward to adjacent rows. Once a cell is moved by TAN to a place with existing cells, to accommodate for the new incoming cell, existing cells need to be moved minimally. In a TD detailed placement, all cell movements are done based on the timing-driven costs. The timing-driven cost of moving a cell u is: a) proportional to the delay sensitivity, which is the delay change of the most critical nets with u per unit displacements of u, and b) inversely proportional to the allocated slack of the most critical net that includes u; further details are in Sec. 2.2.3.

Figure 5(a) shows the network flow graph used in DFP with arc costs and capacities. There is an arc from the source S to each new cell v (e.g. cells  $A_1$  and  $A_2$  in Figure 5(a)) that is moved by TAN. The capacity of the arc is equal to the width w(v) of v. For each such v, there are also two "vertical" arcs from it directed towards cells in rows immediately above and below it (there are more details to these "conceptual" arcs shown in Figure 5(c)); the capacity of each vertical arc is also w(v). A total flow of  $f = \sum_{v \in moveC} w(v)$  emanates from S. This flow will go through each new cell and one of its vertical arcs indicating it is moved in the corresponding vertical direction to an adjacent row.

From each row cell (i.e., existing cell such as cell  $C_{11}$  and  $C_{12}$  in Figure 5(a)), there are four arcs, one in each of the 2D directions (this is easily extended to 6 arcs, one in each of the 3D dimensions in case of 3D VLSICs). The vertical arcs from u go to cells in adjacent rows and model possible movement of u in the respective vertical directions; the capacity of these arcs is w(u), since only u can move along these arcs. The horizontal arcs from u model possible horizontal movement of u within its row, and are potentially of capacity equal to the width of the row from u to the corresponding end of the row, since u could be moved up to either end of the row. However, since arc cost estimates become more inaccurate for large displacements, a capacity equal to the maximum of the widths of the cell in adjacent rows and new cells that have vertical arcs into u is imposed on the horizontal arcs. This allows enough horizontal flow through u that causes its required movement to remove overlaps with cells vertically moved to its position (via vertical flows into u). There can be intermediate white space within rows and these are also modeled as nodes with incoming horizontal and vertical arcs, but only one outgoing arc to the total WS node  $W_i$  of the row; the arc's cost is zero and capacity equal to amount of the intermediate white space. When there is incoming flow to a row cell from new