High-Frequency Link Power Electronics Interface for Discrete Power and Data Transfer

$\mathbf{B}\mathbf{Y}$

### ANKIT GUPTA B.E., Delhi College of Engineering, 2011

#### THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2019

Chicago, Illinois

Defense Committee:

Sudip K. Mazumder, Chair and Advisor

Michael Stroscio

Danilo Erricolo

Inna Partin-Vaisband

Lina He

Juan Carlos Balda, University of Arkansas

Dedicated to my family

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my gratitude to my Ph.D. advisor Prof. Sudip K. Mazumder for his valuable guidance, feedback, and discussions. I want to thank him for giving me the opportunity to work and develop expertise in the design and development of wide band-gap device-based power electronics systems. His assistance made it possible to finish this research and dissertation. I would also like to thank my Ph.D. committee members, Professor Juan Carlos Balda, Michael Stroscio, Danilo Erricolo, Inna Partin-Vaisband and Lina He for their valuable support and guidance.

I want to acknowledge the help of many present and past colleagues at the Laboratory of Energy and Switching Electronics System (LESES). First, I will like to thank Nikhil for being an integral part of my engineering journey and being my friend right from the first day I joined Delhi College of Engineering in 2007. I am thankful for the countless times Nikhil provided me with moral and emotional support and guided me in the right direction. I will always cherish the time spent discussing technical and non-technical topics with Debanjan, Harshit, Sandeep, Abhijit, Moien, Soumya, Anik and Alireza for the rest of my life. Also, I will like to thank Siamak, and Naved, my seniors at LESES, for their valuable guidance when I started on with my graduate studies and in the job application process.

Lastly, but definitely not the least. I would like to thank my family, who have always been my pillar of strength. My parents, Poonam Gupta and Mahesh Chandra Gupta have been a constant source of support and encouragement, and without their blessings, I could not have achieved what little I have today. Also, I would like to thank my sister Charu Gupta for cheering me up with her beautiful smile and encouraging words whenever I was down.

AG

#### PREFACE

This dissertation is an original intellectual product of the author, A. Gupta. All the work presented here was conducted in the Laboratory for Energy and Switching-Electronics Systems (LESES) at the University of Illinois at Chicago.

The results of our research have been previously published as journal, conference, and workshop articles in:

- IEEE Transactions on Industrial Electronics (Gupta et al., 2018)

- IEEE Transactions on Industrial Informatics (Gupta and Mazumder, 2018)

- IEEE Transactions on Power Electronics (Kulkarni et al., 2018)

- IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA'18) (Gupta et al., 2018)

- IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA'17) (Gupta et al., 2017)

- IEEE Energy Conversion Congress and Exposition (ECCE'15) (Gupta et al., 2015)

The copyright permissions for reusing the published materials are given in Appendix A.

Ankit Gupta

March 7, 2019

#### **CONTRIBUTION OF AUTHORS**

Major parts of the results and discussions in this thesis are taken from my published or submitted papers with written permission from the journals (see Appendix A). Below, the contributions of all the co-authors are listed:

Authors' contributions in IEEE Transactions on Industrial Electronics, ECCE'15: A. Gupta, N. Kumar, and S. K. Mazumder conceived the main ideas and led the investigations. A. Gupta undertook the simulations and experimental study. N. Kumar contributed to the analytical analysis. A. Gupta, N. Kumar, and S. k. Mazumder contributed to the write-up of the manuscripts.

Authors' contributions in IEEE Transactions on Industrial Informatics, WiPDA'17, and WiPDA'18: A. Gupta, and S. K. Mazumder conceived the main idea and led the investigation. A. Gupta undertook the circuit design and performed the experimental analysis. A. Gupta and S. k Mazumder contributed to the review and write-up of the manuscript.

Authors' contributions in IEEE Transactions on Power Electronics: A. Kulkarni, A. Gupta, and S. K. Mazumder conceived the main idea and led the investigation. Analysis and experiments about issues with low-frequency harmonics in a grid-connected inverter were done by A. Kulkarni. A. Gupta undertook the study of high-frequency harmonics and designed a GaN-based 500 W grid connected DMCI. A. Kulkarni, A. Gupta, and S. K. Mazumder contributed to the review and write-up of the manuscript.

# TABLE OF CONTENTS

### CHAPTER

| I.   | INTRO | DDUCTION                                                                  | 1  |

|------|-------|---------------------------------------------------------------------------|----|

|      | A.    | Background                                                                | 2  |

|      | В.    | Overview of Distributed Power Systems                                     | 3  |

|      | C.    | Overview of Communication Networks in an HFDPS                            | 5  |

|      |       | 1. Wireless Communication Network                                         | 6  |

|      |       | 2. Wire-Based Communication Network                                       | 9  |

|      | D.    | Motivation and Objective of Doctoral Research                             | 17 |

| II.  | SEQU  | ENTIAL CO-TRANSFER OF HF POWER AND DATA                                   |    |

|      | A.    | Introduction                                                              |    |

|      | В.    | Proposed Approach for Sequential Co-Transfer of HF Power and Data Signals |    |

|      | C.    | HFDPS Following Sequential Co-Transfer Scheme                             |    |

|      |       | 1. Case I: SISO HFDPS Following Sequential Co-Transfer Scheme             |    |

|      |       | 2. Case II: SIMO HFDPS Following Sequential Co-Transfer Scheme            |    |

|      | D.    | Summary                                                                   |    |

| III. | IMPLI | EMENTATION OF SEQUENTIAL CO-TRANSFER SCHEME                               |    |

|      | A.    | Introduction                                                              | 30 |

|      | В.    | Design of the SPES and LPES                                               | 30 |

|      | C.    | Design of the Data Nodes                                                  |    |

|      |       | 1. Data-Transfer Protocol                                                 |    |

|      |       | 2. Implementation of Data-Transmitter and Data-Receiver Circuit           |    |

|      | D.    | Case I: Implementation of a SISO HFDPS                                    |    |

|      | _     | 1. Circuit Realization of a SISO HFDPS Feeding dc Load                    |    |

|      | E.    | Case II: Implementation of a SIMO HFDPS                                   |    |

|      |       | 1. HF Channel Access Protocol                                             |    |

|      |       | 2. Circuit Realization of a SIMO HFDPS Feeding Multiple dc Loads          |    |

|      |       | 3. Circuit Realization of a SIMO HFDPS Feeding ac Load                    |    |

|      | F.    | Resolving Practical Design Issues in SPES and LPES                        |    |

|      |       | 1. The Occurrence of HF Noise Due to PCB Layout                           |    |

|      |       | 2. The Occurrence of HF Noise Due to High Slew Rate                       |    |

|      | G.    | Summary                                                                   | 59 |

| IV.  |       | LTS AND DISCUSSION                                                        |    |

|      | A.    | Introduction                                                              |    |

|      | В.    | Experimental Validation of Sequential Co-Transfer Scheme in a SISO HFDPS  |    |

|      |       | 1. Experimental Setup                                                     |    |

|      |       | 2. Control Approach for Sequential Co-Transfer of Power and Data          |    |

|      |       | 3. Experimental Results for SISO HFDPS Feeding dc Load                    |    |

|      | C.    | Design Modifications in Data Circuit                                      |    |

|      |       | 1. Protection Design for the Data Nodes                                   |    |

|      |       | 2. Hardware Solution for Eliminating Erroneous Data Bit                   |    |

|      | D.    | Experimental Validation of Sequential Co-Transfer Scheme in a SIMO HFDPS  |    |

|      |       | 1. Experimental Setup                                                     |    |

|      |       | 2. Experimental Results for SIMO HFDPS Feeding Multiple dc Loads          |    |

|      |       | 3. Network Capacity for a SIMO HFDPS Feeding Multiple dc Loads            |    |

|      | -     | 4. Experimental Results for SIMO HFDPS Feeding ac Load                    |    |

|      | E.    | Summary                                                                   | 96 |

# **TABLE OF CONTENTS (Continued)**

| <u>CHAPTER</u> |                              | PAGE |

|----------------|------------------------------|------|

| V.             | CONCLUSIONS AND FUTURE WORKS |      |

|                | A. Summary and Contributions |      |

|                | B. Future Work               |      |

| VI.            | APPENDICES                   |      |

|                | APPENDIX A                   |      |

|                | APPENDIX B                   |      |

|                | APPENDIX C                   |      |

|                | APPENDIX D                   |      |

| VII.           | REFERENCES                   |      |

| VITA           |                              |      |

### LIST OF TABLES

| TABL | <u>TABLE</u> PAG                                                                                        |  |

|------|---------------------------------------------------------------------------------------------------------|--|

| I.   | SWITCH STATES OF VARIOUS SWITCHES IN A SISO HFDPS FOLLOWING SEQUENTIAL CO-TRANSFER SCHEME               |  |

| II.  | SWITCH STATES OF VARIOUS SWITCHES IN THE SIMO HFDPS FOLLOWING SEQUENTIAL CO-TRANSFER SCHEME             |  |

| III. | PARASITIC INDUCTANCE OF THE GATE-DRIVER CIRCUIT AT THE NOMINAL SWITCHING FREQUENCY OF 100 <i>k</i> HZ54 |  |

| IV.  | SPECIFICATIONS OF THE SPES AND LPES                                                                     |  |

| V.   | EFFECT OF THE FREQUENCY OF POWER TRANSFER ON THE DATA RATE                                              |  |

| VI.  | A TABLE LISTING THE POWER AND DATA NODES PARAMETERS OF THE EXPERIMENTAL SETUP                           |  |

### LIST OF FIGURES

| <u>FIGURI</u> | <u>E</u>                                                                                                                                                                                                                                                                                                                   | PAGE |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

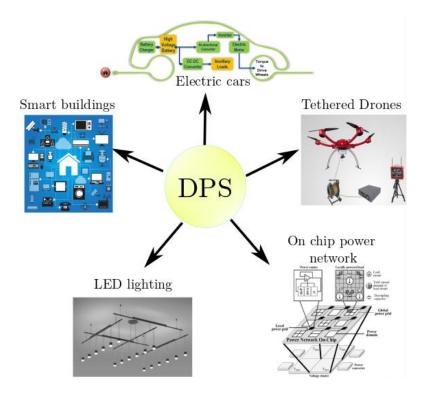

| 1.            | Various type of distributed power systems (DPS's).                                                                                                                                                                                                                                                                         | 2    |

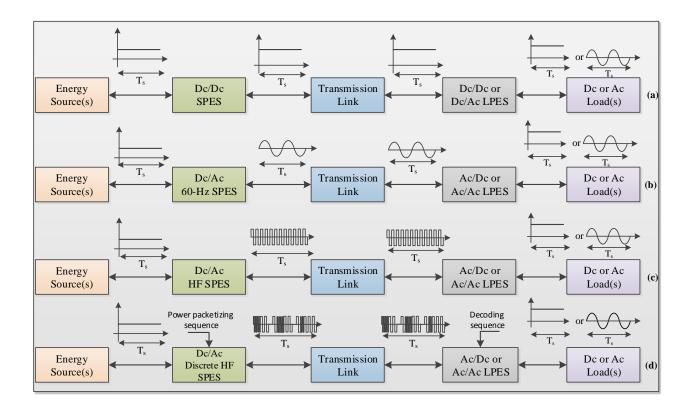

| 2.            | Illustration of (a) dc, (b) low-frequency ac, (c) HFDPS and (d) discrete HF DPSs architectures. The difference between (a), (b), (c) and (d) pertains to how the power signals are transmitted. (d) Can incorporate discontinuous power transfer whereas the rest incorporates continuous power transfer [10], ©2015 IEEE. | 4    |

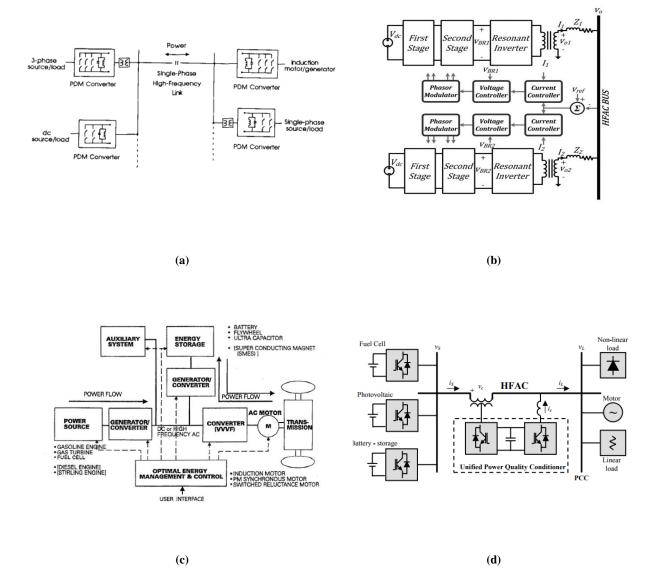

| 3.            | HFDPS architectures proposed in literature for (a) space station [14] ©1988 IEEE, (b) telecommunication applications [7] ©2014 IEEE, (c) automotive application [15] ©1996 IEEE, and (d) microgrid [16] ©2003 IEEE.                                                                                                        | 5    |

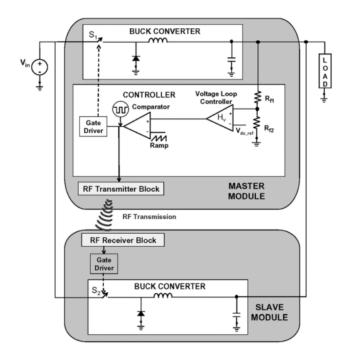

| 4.            | The wireless control scheme for parallel dc/dc converter [17] ©2008 IEEE.                                                                                                                                                                                                                                                  | 7    |

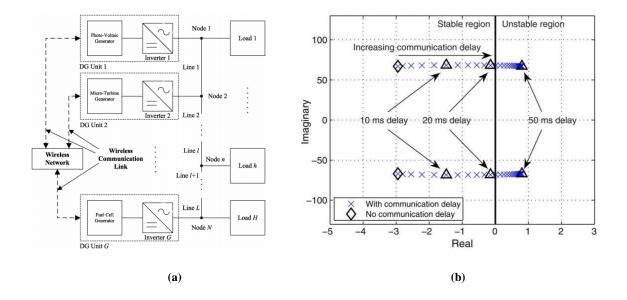

| 5.            | The configuration of a microgrid with wireless communication network between distributed generation units [20], and (b) Impact of communication delay on the location of different modes [20], ©2013 IEEE.                                                                                                                 | 8    |

| 6.            | Schematic design of a circuit used for wireless power and data transfer [21], ©2015 IEEE.                                                                                                                                                                                                                                  | 8    |

| 7.            | Illustration of a conventional PLC technique with simultaneous low-frequency power transfer (LFPT) and HF data transfer (HFDT) [29], ©2018 IEEE.                                                                                                                                                                           | 10   |

| 8.            | The underlying architecture of a PLC-based simultaneous power and data transfer network                                                                                                                                                                                                                                    | 10   |

| 9.            | Transmission characteristics of a typical PWM-inverter fed power line [34], ©1993 IEEE                                                                                                                                                                                                                                     | 12   |

| 10.           | (a) Schematic of the motor condition monitoring system using PLC as proposed in [34]. (b) Experimental plots of the transmitted data signal at the data input pin and signals at the primary terminal of the coupling transformer. (c) zoomed in version of the waveforms provided in (b), ©1993 IEEE.                     | 13   |

| 11.           | (a) Developed experimental setup for realizing PLC over PWM in [33], and (b) obtained experimental results showing PWM inverter output voltage and injected HF noise in the data circuit at every switching instant, ©2010 IEEE.                                                                                           | 13   |

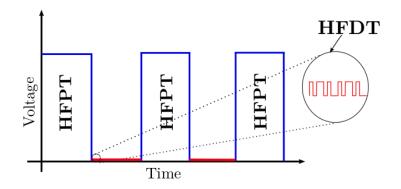

| 12.           | The basic structure of a power and data signal in a sequential power and data transfer scheme                                                                                                                                                                                                                              | 14   |

| 13.           | Schematic of the power packet dispatch system outlined in [39]                                                                                                                                                                                                                                                             | 16   |

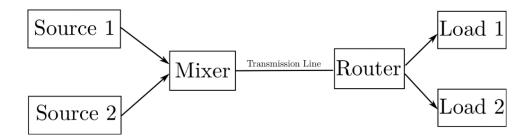

| 14.           | Schematic of power packet mixer and router units outlined in [39]                                                                                                                                                                                                                                                          | 16   |

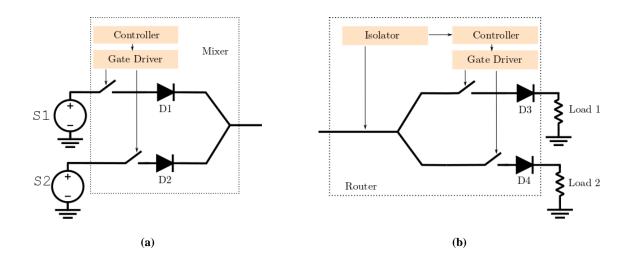

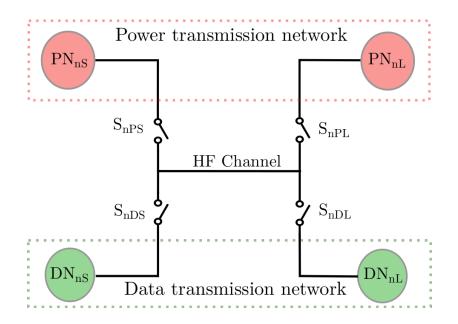

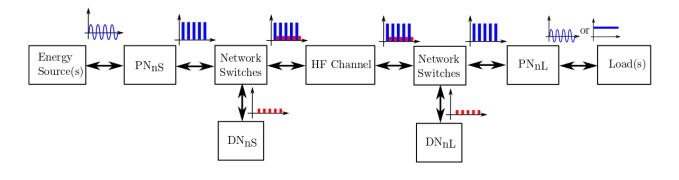

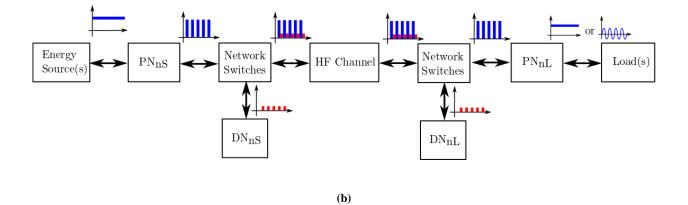

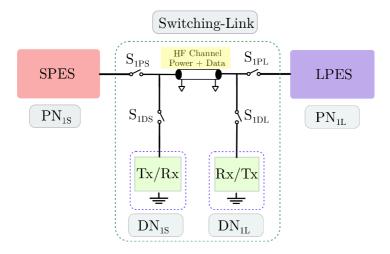

| 15.           | Overview of the network supporting sequential co-transfer of HF power and data over the common HF channel. <i>PNnS</i> and <i>PNnL</i> serve as the power transmitter and receiver nodes, while <i>DNnS</i> and <i>DNnL</i> represents data nodes corresponding to power nodes <i>PNnS</i> and <i>PNnL</i> , respectively  | 22   |

| 16.           | Illustration of the sequential co-transfer scheme for HF power and data (HFPT, HFDT) transmission [29], ©2018 IEEE.                                                                                                                                                                                                        | 23   |

| 17. | An HFDPS following the sequential co-transfer scheme for transferring power from (a) an ac source to an ac/dc load, and (b) a dc source to a dc/ac load. <i>PNnS</i> and <i>PNnL</i> represents <i>nth</i> power transmitter and receiver nodes, respectively. <i>DNnS</i> and <i>DNnL</i> represents data nodes corresponding to <i>PNnS</i> and <i>PNnL</i> , respectively.        | 24 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

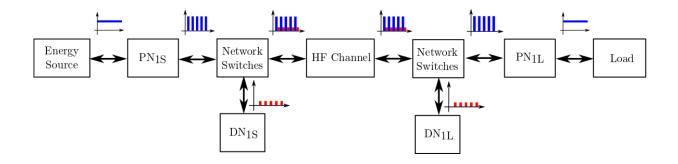

| 18. | A SISO HFDPS following sequential co-transfer scheme.                                                                                                                                                                                                                                                                                                                                | 26 |

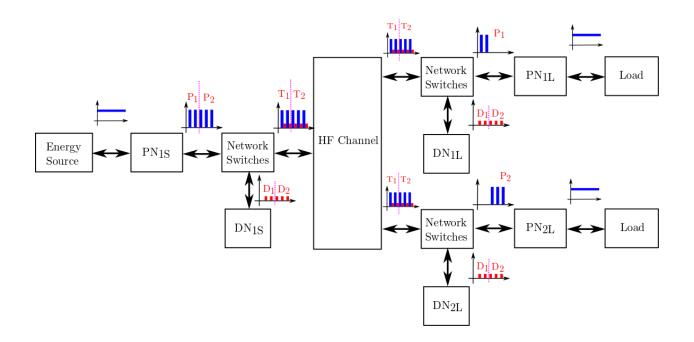

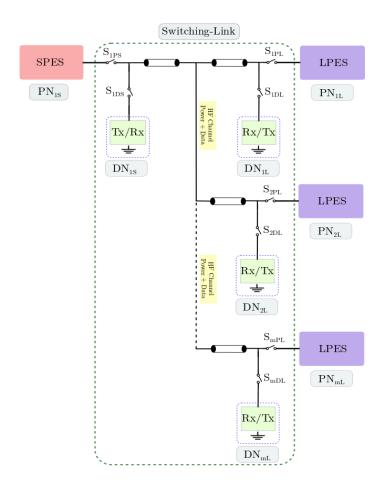

| 19. | A SIMO HFDPS following the sequential co-transfer scheme. HF Power and data packets can be routed to different power nodes and data nodes using the network switches.                                                                                                                                                                                                                | 27 |

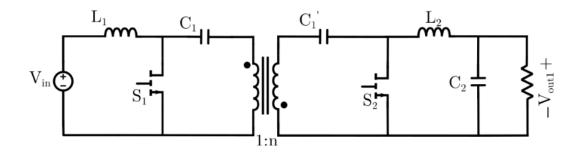

| 20. | Schematic diagram of an isolated Ćuk converter.                                                                                                                                                                                                                                                                                                                                      | 31 |

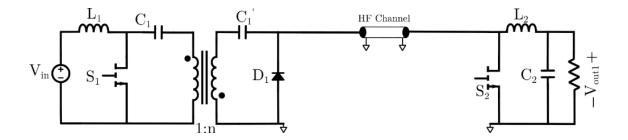

| 21. | Schematic representation of a distributed converter with an integrated HF channel                                                                                                                                                                                                                                                                                                    | 31 |

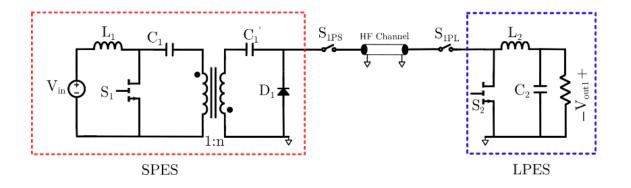

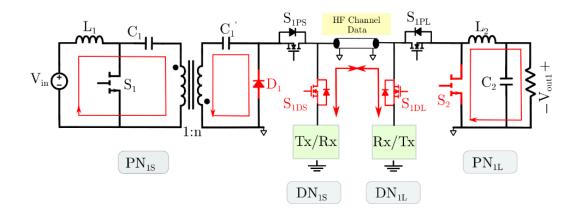

| 22. | Schematic representation of a distributed converter with an integrated HF channel and transfer switches <i>S1PS</i> and <i>S1PL</i> .                                                                                                                                                                                                                                                | 32 |

| 23. | Asynchronous SCI data frame format [29], ©2018 IEEE.                                                                                                                                                                                                                                                                                                                                 | 33 |

| 24. | Modified asynchronous SCI data frame format [29], ©2018 IEEE.                                                                                                                                                                                                                                                                                                                        | 34 |

| 25. | Inverting gate-driver IC is used as the data transmitter. Low voltage binary data is received from the DSP and amplified to a higher-voltage high-current signal for being transmitted through the HF channel.                                                                                                                                                                       | 34 |

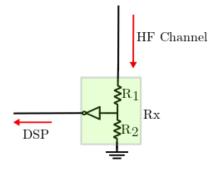

| 26. | Design of a simple resistive data-receiver circuit being implemented to sense the data frame transferred over the HF channel. Sensed data is transmitted to the <i>DSP</i> SCI RX channel for further processing.                                                                                                                                                                    | 35 |

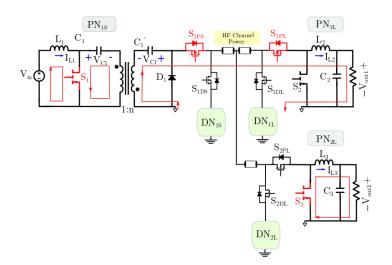

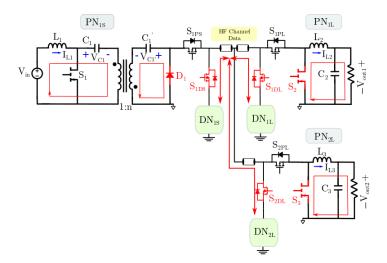

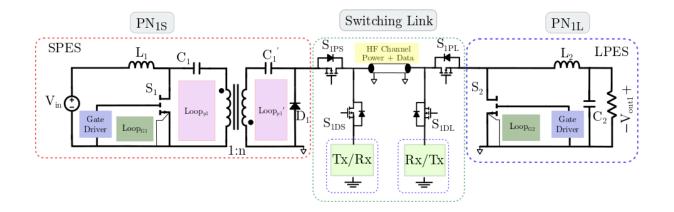

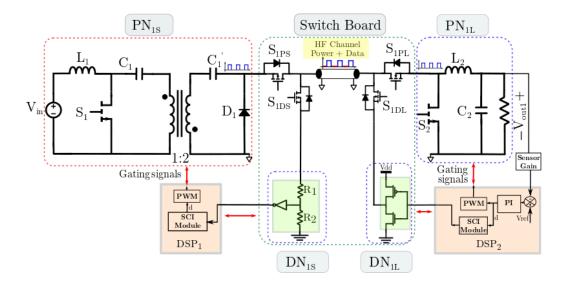

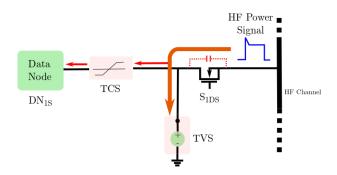

| 27. | Block diagram of a single transmitting and receiving node forming a SISO HFDPS. Here, SPES and LPES represents a power transmitter ( <i>PN1S</i> ) and receiver ( <i>PN1L</i> ), respectively. Data transmission nodes corresponding to SPES and LPES are marked as <i>DN1S</i> and <i>DN1L</i> , respectively                                                                       | 36 |

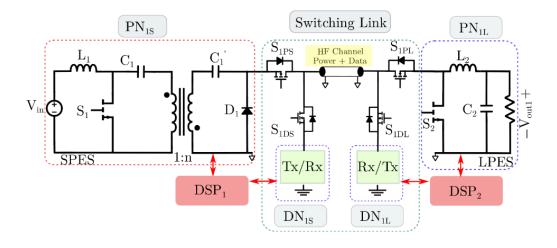

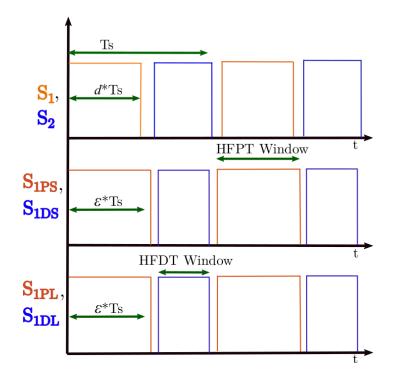

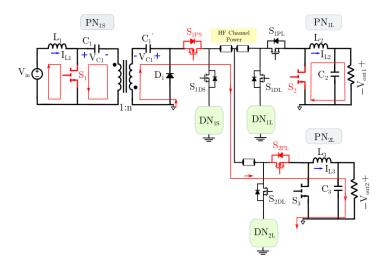

| 28. | A schematic representation of the SISO HFDPS, showing <i>PN1S</i> , <i>PN1L</i> , <i>DN1S</i> , <i>DN1L</i> , and the HF channel. <i>DSP1</i> ( <i>DSP2</i> ) coordinates locally with <i>PN1S</i> ( <i>PN1L</i> ) for gating and feedback signals, <i>DN1S</i> ( <i>DN1L</i> ) regarding data communication and switching link regarding sequential power and data co-transmission. | 37 |

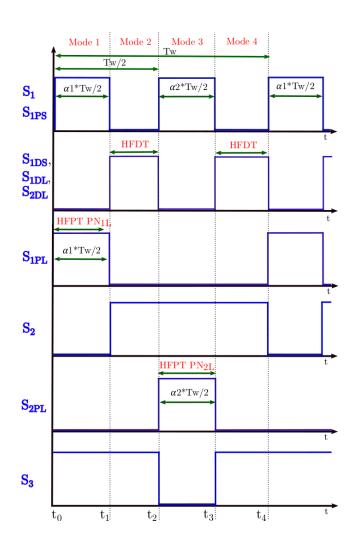

| 29. | A timing diagram for the SPES and LPES. It is noted that all the switches in SPES and LPES are synchronized to a common clock.                                                                                                                                                                                                                                                       | 37 |

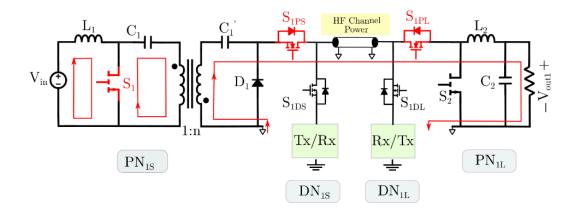

| 30. | Mode-1, during this mode of operation HF channel is used for HF power packet transmission                                                                                                                                                                                                                                                                                            | 38 |

| 31. | Mode-2, during this mode of operation HF channel is used for data transmission                                                                                                                                                                                                                                                                                                       | 39 |

| 32. | Block diagram representation of a single power transmitter and multiple power receiver nodes forming a SIMO HFDPS. SPES and LPES represents a power transmitter ( <i>PN1S</i> ) and receiver nodes ( <i>PN1L</i> , <i>PN2L PNmL</i> ), respectively. Source side and load side data nodes are marked as <i>DN1S</i> and <i>DN1L</i> . <i>DNmL</i> .                                  | 41 |

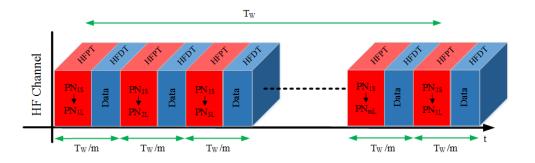

| 33. | The TDM frame structure for the sequential co-transfer of power and data signal over a common HF channel in a SIMO HFDPS. For transferring power packets to $m$ power receiver nodes, TDM frame is divided into $m$ equal sub-intervals which are further divide in HFPT and HFDT windows.                                                                                                                       | 42 |

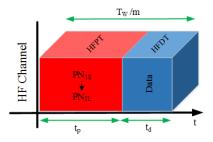

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 34. | A single time slot of the TDM frame designed for feeding $m$ power receiver nodes in a SIMO HFDPS. Each time-slot is further sub-divided in HFPT and HFDT windows having time durations $tp$ and $td$ , respectively.                                                                                                                                                                                            | 43 |

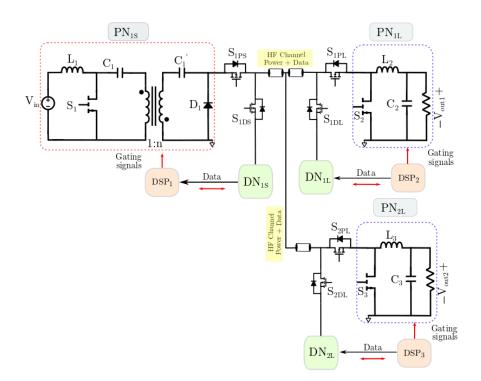

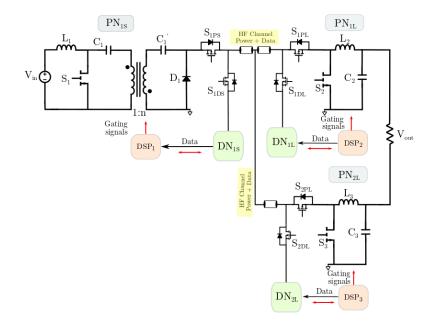

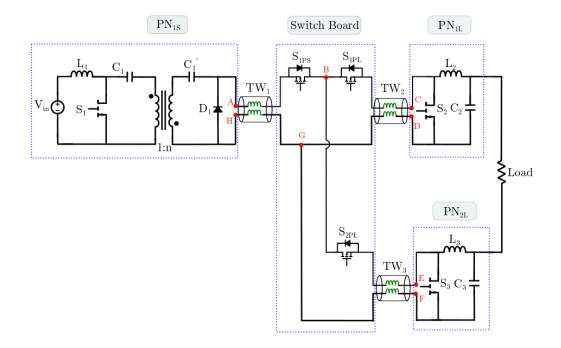

| 35. | Schematic representation of a SIMO HFDPS, with power nodes <i>PN1S</i> , <i>PN1L</i> , and <i>PN2L</i> , data nodes <i>DN1S</i> , <i>DN1L</i> , and <i>DN2L</i> , and the HF channel                                                                                                                                                                                                                             | 44 |

| 36. | A timing diagram for the SIMO HFDPS shown in Figure 35.                                                                                                                                                                                                                                                                                                                                                          | 45 |

| 37. | Mode-1 (t0 - t1), during this mode HF power packets are routed from <i>PN1S</i> to <i>PN1L</i> through the HF channel.                                                                                                                                                                                                                                                                                           | 46 |

| 38. | Mode-2 $(t1 - t2)$ and mode-4 $(t3 - t4)$ , during these modes of operation, HF channel is used for the exchange of data between the data nodes.                                                                                                                                                                                                                                                                 | 46 |

| 39. | Mode-3 ( <i>t</i> 2 - <i>t</i> 3), during this mode HF power packets are routed from <i>PN1S</i> to <i>PN2L</i> through the HF channel.                                                                                                                                                                                                                                                                          | 47 |

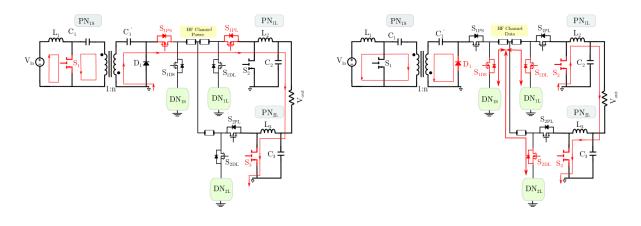

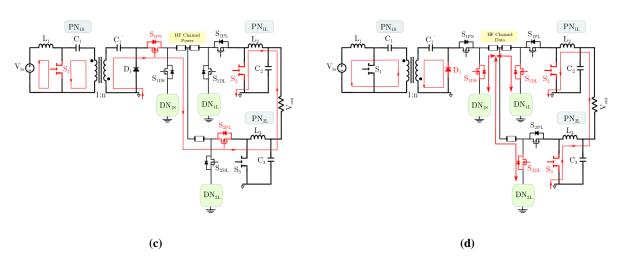

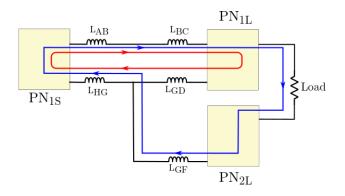

| 40. | Illustration of the SIMO HFDPS in a dc/ac mode of operation. The designed SIMO HFDPS consists of one power transmitter ( <i>PN1S</i> ) and two power receiver nodes ( <i>PN1L</i> and <i>PN2L</i> ) connected over a HF channel.                                                                                                                                                                                 | 48 |

| 41. | Modes of operation of the SIMO HFDPS in a dc/ac operation. During positive-half of the line cycle SIMO HFDPS follows (a) mode-1 (b) mode-2, and during negative-half of the line cycle, it follows (c) mode-3 and (d) mode-4                                                                                                                                                                                     | 49 |

| 42. | A single transmitter and receiver node of an HFDPS forming a SISO HFDPS, with marked gate loops <i>LoopG1</i> and <i>LoopG2</i> and HF power loops <i>LoopP1</i> and <i>LoopP1'</i>                                                                                                                                                                                                                              | 52 |

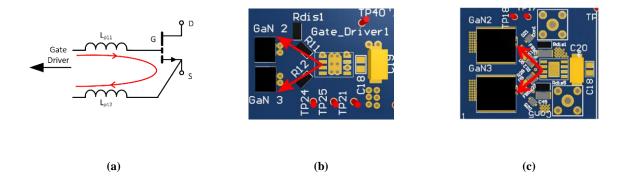

| 43. | Schematic drawing showing the location of HF parasitic inductance $Lp11$ and $Lp12$ in the gate driver loops $LoopG1$ and $LoopG2$ of the SPES and LPES, respectively. (b) Primary side gate driver PCB design for the SPES implemented using GaN Systems GS66506T and (c) GS66508P as the switching device. The direction of gate-driver current is marked in red during the event of turn on [55], ©2018 IEEE. | 53 |

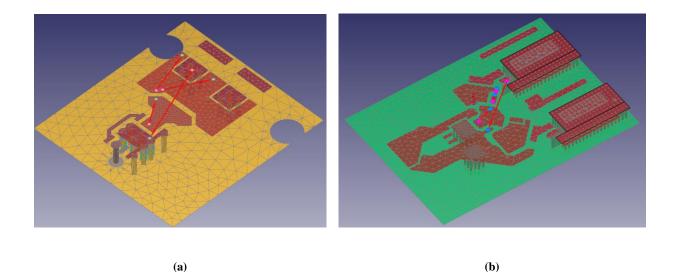

| 44. | Imported PCB gate-driver layout in EMCoS PCB VLab v.3.2 with trace definition between which parasitic elements need to be measured for designs using (a) GS66506T and (b) GS66508P as the switching device [56], ©2017 IEEE.                                                                                                                                                                                     | 54 |

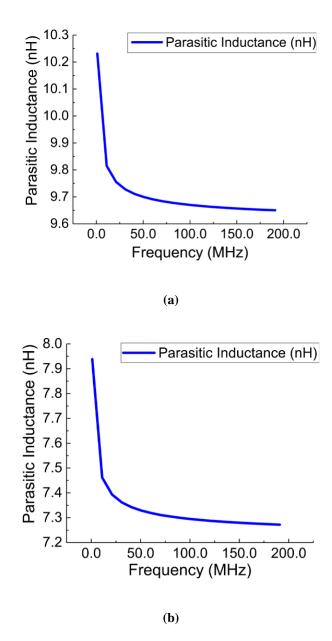

| 45. | Simulation results showing the variation of PCB parasitic track inductance in SPES as a function of signal frequency in the <i>LoopG1</i> for a design using (a) GS66506T and (b) GS66508P as the GaN-FET [55], ©2018 IEEE.                                                                                                                                                                                      | 55 |

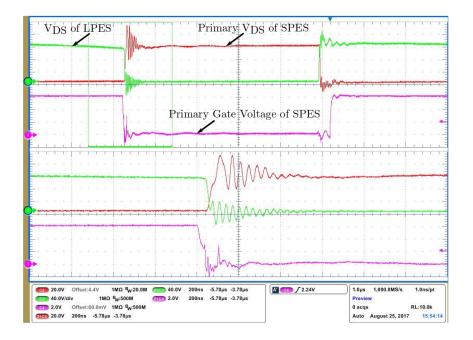

| 46. | Primary side SPES switching waveform on Ch. 4 and SPES and LPES <i>VDS</i> on Ch. 2 and Ch. 3, respectively, with a zoomed view, for the SPES and LPES PCB designs employing (a) GaN Systems GS66506T with gate loop parasitic inductance of 10.22 <i>n</i> H and (b) GaN Systems GS66508P with gate loop parasitic inductance of 8.12 <i>n</i> H                                                     | 56 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

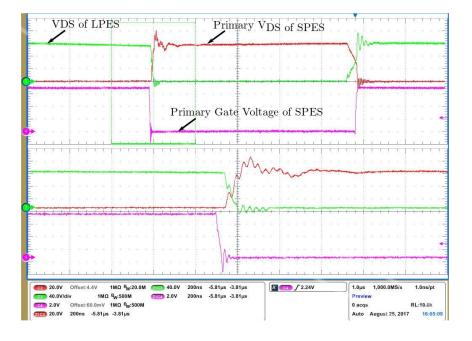

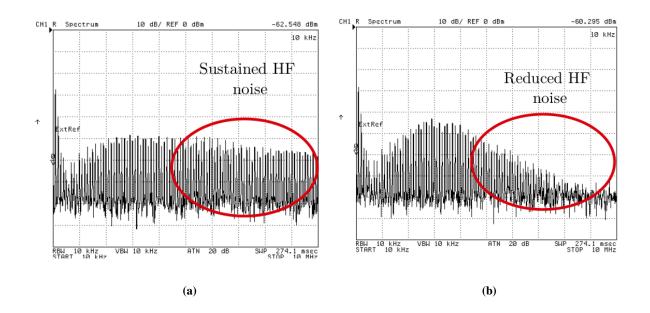

| 47. | Impedance magnitude and phase plot for (a) <i>C</i> 1 and (b) <i>C</i> 1' [55], ©2018 IEEE                                                                                                                                                                                                                                                                                                            | 58 |

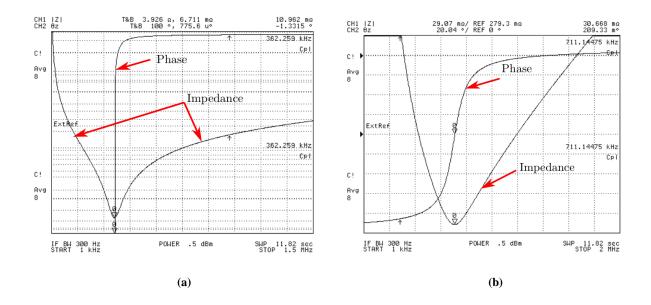

| 48. | Experimental spectrum analyzer results for the voltage across the primary side blocking capacitor in SPES (a) without a ceramic capacitor in parallel, (b) with a ceramic capacitor in parallel [55], ©2018 IEEE.                                                                                                                                                                                     | 59 |

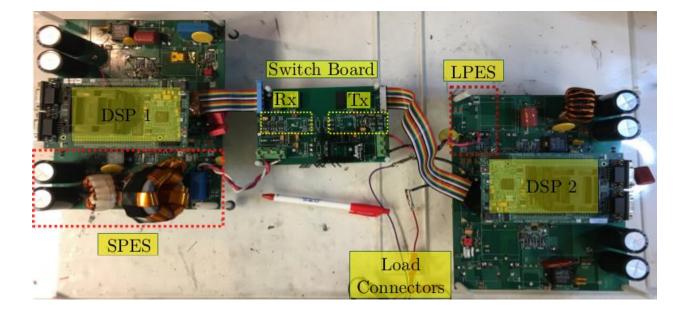

| 49. | The developed experimental prototype for the SISO HFDPS following sequential co-transfer scheme. HF channel, transfer and data switches are realized on the switch board. It is noted that only a small section marked as SPES and LPES is used on each power board which contains two modules of isolated Ćuk converter [29], ©2018 IEEE.                                                            | 63 |

| 50. | Schematic diagram outlining a single pair of SPES and LPES connected over the HF channel.<br>Control approach implemented in <i>DSP</i> 1 and <i>DSP</i> 2 are also illustrated, with <i>Vref</i> representing the reference for regulating the output voltage.                                                                                                                                       | 64 |

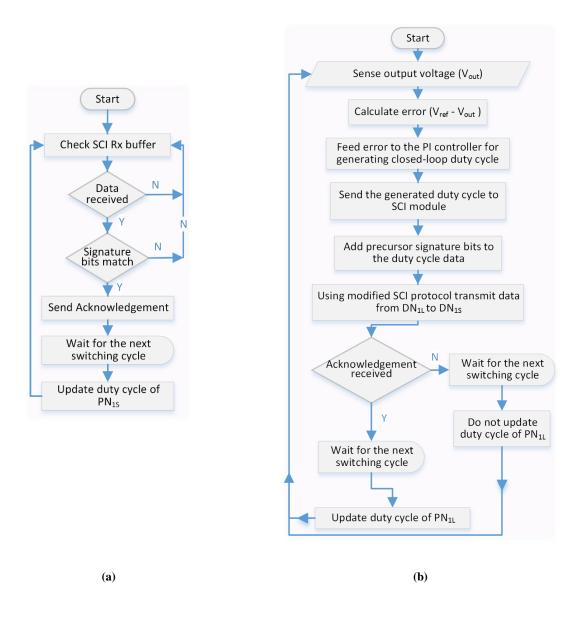

| 51. | Flowcharts outlining the control approach implemented in the controller of (a) data receiver module $(DN1S)$ (b) data transmitter module $(DN1L)$ .                                                                                                                                                                                                                                                   | 65 |

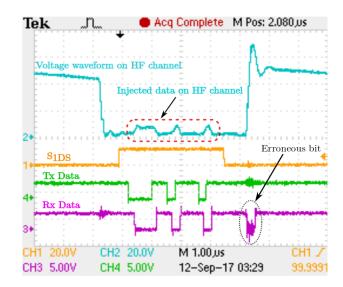

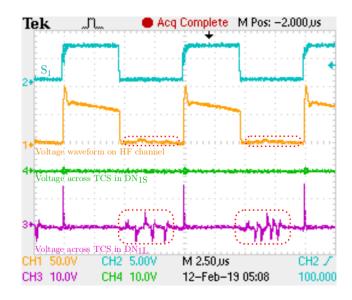

| 52. | Experimental waveform (Ch. 2) shows the sequential co-transfer of HF power and data over the HF channel. Embedded data signals (Ch. 3 and 4), which are transmitted from <i>DSP</i> 2, when <i>S1DS</i> (Ch. 1) is high, to <i>DSP</i> 1 are shown on Ch. 4 and 3, respectively                                                                                                                       | 66 |

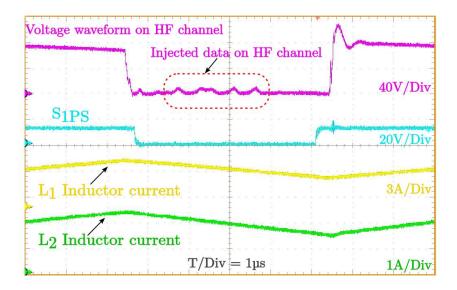

| 53. | Experimental waveform (Ch. 3) shows the sequential co-transfer of HF power and data over the HF channel. Only when <i>S1PS</i> (Ch. 2) is turned ON, the magnitudes of the input and output inductor currents (Ch. 1 and 4) increase indicating power transfer between SPES and LPES over the HF channel.                                                                                             | 67 |

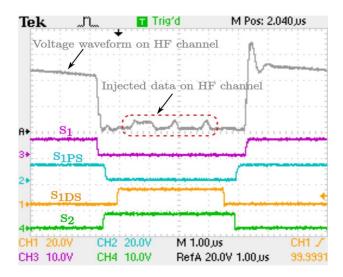

| 54. | Experimental waveform (Ref A) shows the sequential co-transfer of HF power and data over the HF channel, along with the gating signals for <i>S</i> 1, <i>S</i> 1 <i>PS</i> , <i>S</i> 1 <i>DS</i> and <i>S</i> 2                                                                                                                                                                                     | 68 |

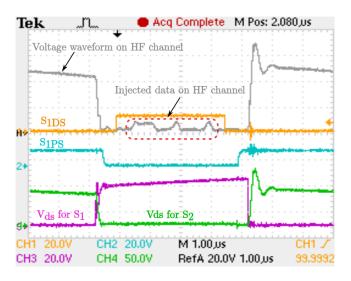

| 55. | Experimental waveform (Ref A) shows the sequential co-transfer of HF power and data over the HF channel, along with the <i>VDS</i> waveforms across switches <i>S</i> 1 and <i>S</i> 2                                                                                                                                                                                                                | 68 |

| 56. | Variable output voltage waveform obtained at the load connected to the output terminal of LPES. The applied duty cycle has sinusoidal modulation with a frequency of 1 $k$ Hz along with a dc offset. Constantly changing load demand is transferred to the data node of SPES over the HF channel in every switching cycle.                                                                           | 69 |

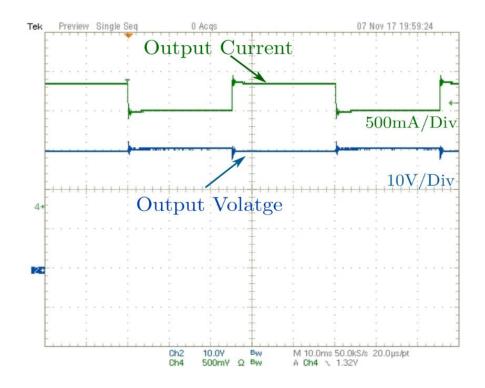

| 57. | Output-voltage and output-current waveforms of the load connected to the LPES during a cyclic 20 Hz load variation between 48 W and 36 W. A PI compensator is designed to track the output voltage of 30 V given an input voltage of 20 V. Load demand in terms of duty cycle variation is transferred from <i>DSP2</i> to <i>DSP1</i> in every switching cycle using the data nodes [29], ©2018 IEEE | 70 |

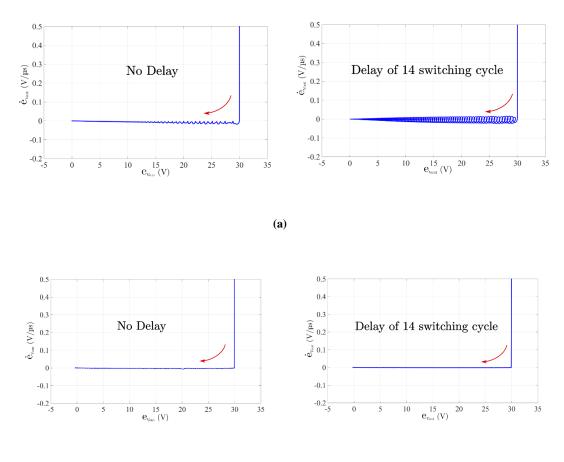

| 58. | (a) Simulated and (b) experimental results for the state error trajectories of the output voltage at LPES with no delay and a delay of 14 switching cycle. Converges of state error trajectory guarantees the reachability of the delayed and non-delayed system [29], ©2018 IEEE                                                                                                                                                                                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

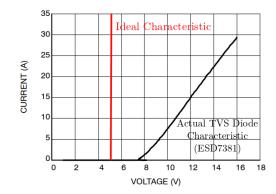

| 59. | Comparison between an ideal 5V TVS diode characteristic (Red) and actual TVS diode characteristic of ON Semiconductor 5V TVS diode, ESD7381 (Black)                                                                                                                                                                                                                                                                                                                 |

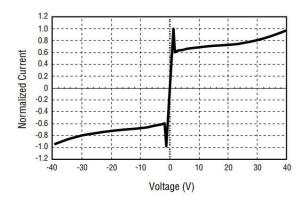

| 60. | Normalized V-I characteristics of a Bourns DL-series high-speed TCS under surge condition [67]73                                                                                                                                                                                                                                                                                                                                                                    |

| 61. | Implementation of a two-stage protection scheme with a TCS device in conjunction with a suitable over voltage limiting device (TVS diode) for providing comprehensive current and voltage limiting protection to the data node in surge conditions                                                                                                                                                                                                                  |

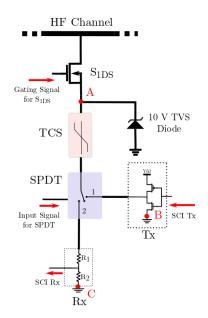

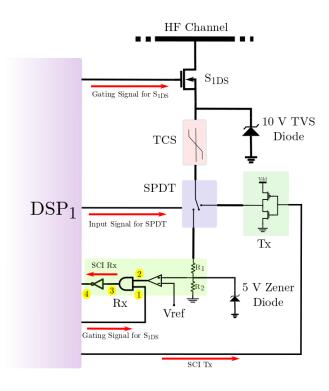

| 62. | Schematic representation of the data node with enhanced two-stage protection with <i>DN1S</i> as case illustration. During transitional coupling in Tx mode of operation, TCS device suppress transient current flow in path $A \rightarrow B$ . However, the enhanced protection features of the TCS device are precluded by the inherent higher impedance of the path $A \rightarrow C$ provided by resistors <i>R1</i> and <i>R2</i> in the Rx mode of operation |

| 63. | Experimental waveforms demonstrating the operation of protection designed for the data nodes.<br>Transitional coupling between the power and the data nodes occur when <i>S</i> 1 is turned ON (Ch. 2).<br>Voltage spikes equal to the clamping voltage of TVS diode appear across the TCS in <i>DN1L</i> (Ch. 3) validating its operation during transitional coupling. No significant voltage drop appears across TCS in <i>DN1S</i> (Ch. 4)                      |

| 64. | Schematic representation of the modified data node with integrated transient current protection and data correction circuit with <i>DN1S</i> as case illustration77                                                                                                                                                                                                                                                                                                 |

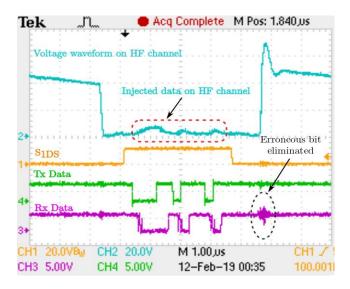

| 65. | Various signals in the Rx circuit with the positions as marked in Figure 64. The erroneous bit seen in the comparator output is removed from the SCI Rx signal by using a two-input AND gate                                                                                                                                                                                                                                                                        |

| 66. | Experimental waveform (Ch. 2) shows the sequential co-transfer of HF power and data over the HF channel with modified data node design. Embedded data signals, which are transmitted from <i>DSP</i> 2, when <i>S1DS</i> (Ch. 1) is high, to <i>DSP</i> 1 are shown on Ch. 4 and Ch. 3, respectively                                                                                                                                                                |

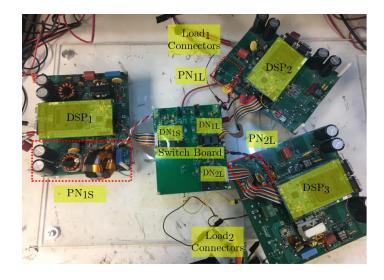

| 67. | The experimental prototype for the SIMO HFDPS comprising of one SPES ( <i>PN1S</i> ) and two LPESs ( <i>PN1L</i> and <i>PN2L</i> ). HF channel, transfer switches ( <i>S1PS</i> , <i>S1PL</i> , and <i>S2PL</i> ) and data switches ( <i>S1DS</i> , <i>S1DL</i> , and <i>S2DL</i> ) along with the data nodes ( <i>DN1S</i> , <i>DN1L</i> , and <i>DN2L</i> ) are realized on the switch board                                                                      |

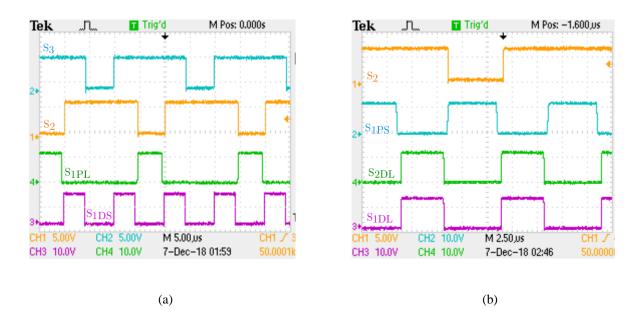

| 68. | Gating signals for various switches in the designed SIMO HFDPS81                                                                                                                                                                                                                                                                                                                                                                                                    |

| 69. | Experimental waveforms showing the transfer of HF data signals over the HF channel, along with the gating signals for $S1DL$ , $S1PL$ , and $S2$ with $Vin = 0$ at $PN1S$                                                                                                                                                                                                                                                                                           |

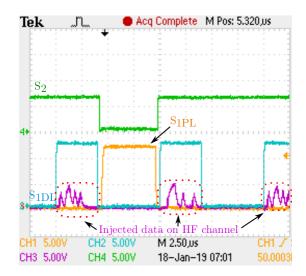

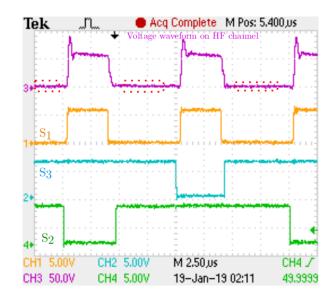

| 70. | Experimental waveform showing sequential co-transfer of HF power and data over the HF channel in a SIMO HFDPS (Ch. 3), along with the gating signals for <i>S</i> 1(Ch. 1), <i>S</i> 3 (Ch. 2), and <i>S</i> 2 (Ch. 4)                                                                                                                                                                                                                                              |

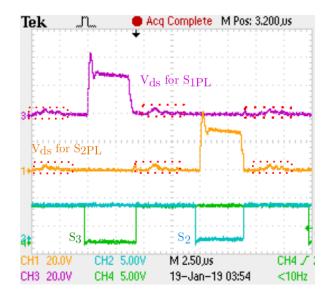

| 71. | <i>Vds</i> voltage waveforms across the transfer switches S2PL (Ch. 1), and S1PL (Ch. 3) and gating signals for S2 (Ch. 2) and S3 (Ch. 4)                                                                                                                                                                                                                                                                                                                           |

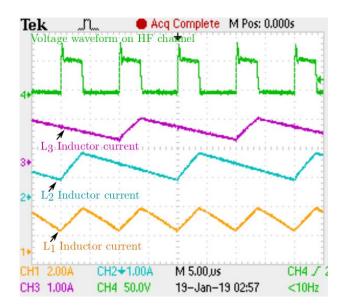

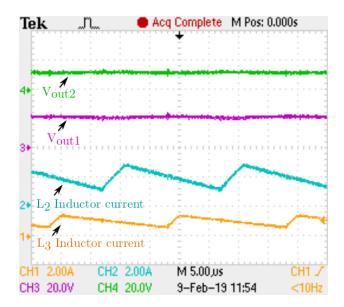

| 72. | Experimental waveforms showing sequential co-transfer of HF power and data over the HF channel (Ch. 4). Inductor currents for <i>L</i> 1, <i>L</i> 2, and <i>L</i> 3 are shown on Ch. 1, Ch. 2, and Ch. 3, respectively                                                                                                                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

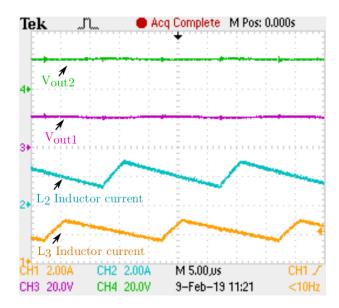

| 73. | The experimental result when HF power packets of equal size are routed to <i>PN1L</i> and <i>PN2L</i> from <i>PN1S</i> . Equal output voltage of 20 V is generated at <i>Vout1</i> and <i>Vout2</i> with <i>Vin</i> of 40 V85                                                                                                                          |

| 74. | The experimental result when HF power packets with different size are routed to <i>PN1L</i> and <i>PN2L</i> from <i>PN1S</i> . Output voltage of 20 V is generated at <i>Vout1</i> and 10 V is generated at <i>Vout2</i> with <i>Vin</i> of 40 V                                                                                                       |

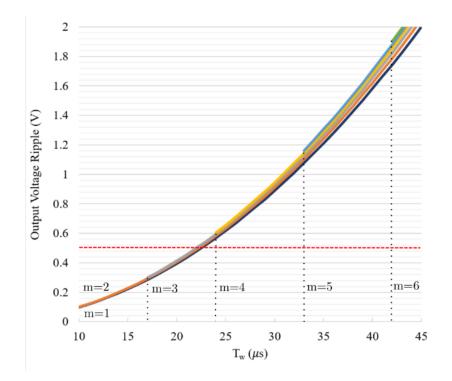

| 75. | Variation in the output voltage ripple at each LPES generating 10 V output with 40 V input at the SPES. HF power and data packets are transferred over the HF channel using TDM with a frame time of $TW. m$ represents the number of LPES nodes connected on the SIMO HFDPS                                                                           |

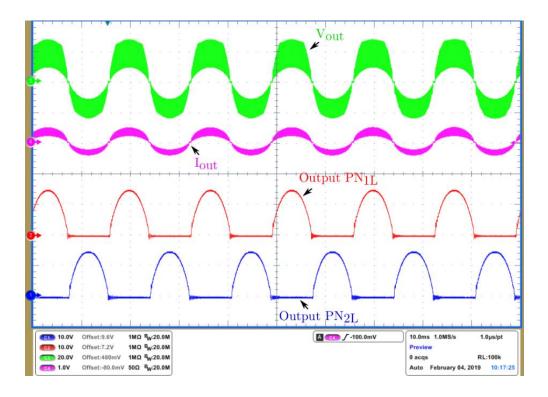

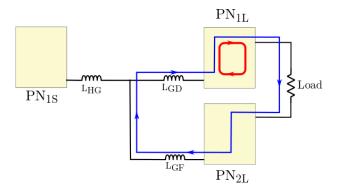

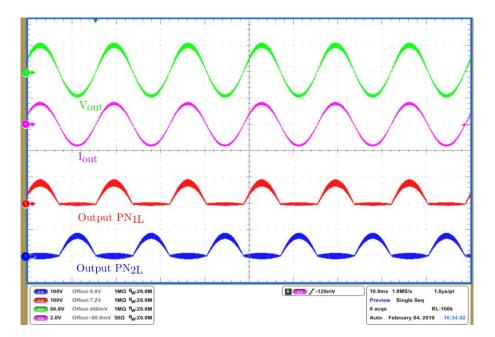

| 76. | Experimental result of the SIMO HFDPS feeding an ac load. HF oscillations can be observed in <i>Vout</i> and <i>Iout</i> waveforms                                                                                                                                                                                                                     |

| 77. | Simplified circuit representation of the experimental prototype shown in Figure 67, in a dc/ac mode of operation. <i>TW</i> 1, <i>TW</i> 2, and <i>TW</i> 3 represents the twisted-wires used for interconnecting <i>PN</i> 1 <i>S</i> , <i>PN</i> 1 <i>L</i> , and <i>PN</i> 2 <i>L</i> to the switch board                                           |

| 78. | HF (Red) and line-frequency (Blue) current flow paths through the switch board in a block diagram representation during mode-1 of the SIMO HFDPS in a dc/ac operation                                                                                                                                                                                  |

| 79. | HF (Red) and line-frequency (Blue) current flow paths through the switch board in a block diagram representation during mode 2 of the SIMO network operating in the microinverter mode of operation                                                                                                                                                    |

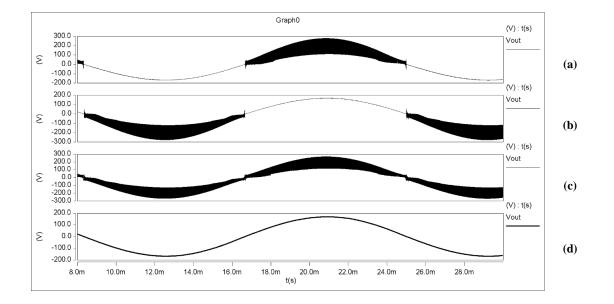

| 80. | Simulation result for <i>Vout</i> with the parasitic inductance values of (a) $LGD = 200 \text{ nH}$ and $LGF = 1pH$ , (b) $LGD = 1pH$ and $LGF = 200 \text{ nH}$ , (c) $LGD = 200 \text{ nH}$ and $LGF = 200 \text{ nH}$ , and (d) $LGD = 200 \text{ nH}$ , and $LGF = 200 \text{ nH}$ and a 10 $\mu$ F capacitor connected across the load terminals |

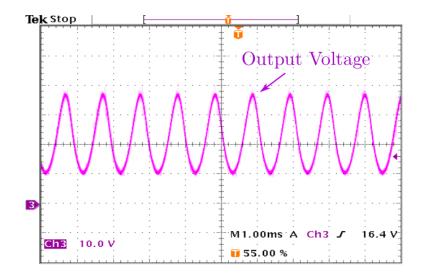

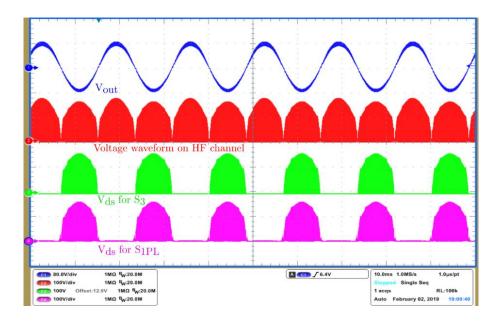

| 81. | Experimental result of SIMO HFDPS feeding an ac load with a $10\mu$ F capacitor connected across it.<br>HF oscillations in <i>Vout</i> and <i>Iout</i> waveforms are reduced                                                                                                                                                                           |

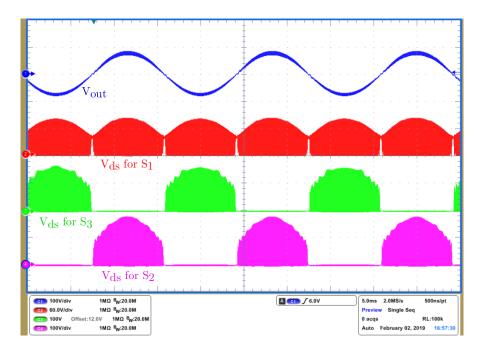

| 82. | <i>Vout</i> along with Vds waveforms across the power switches in the power nodes PN1S, PN1L, and PN2L. Result is captured with Vin= 40 V and $\alpha$ max= 0.51                                                                                                                                                                                       |

| 83. | Experimental voltage waveform on Ch. 2 captures the HF power and data packets that are being routed through the HF channel using sequential co-transfer scheme. HF power packets routed to <i>PN2L</i> are shown on Ch. 3. The same HF power packets are blocked from entering <i>PN1L</i> by <i>S1PL</i> and are shown Ch. 4                          |

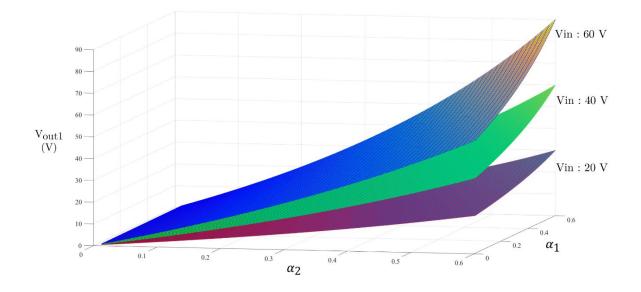

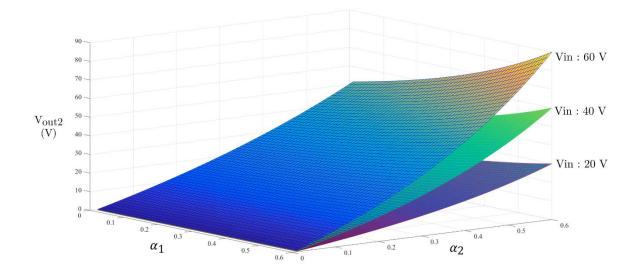

| 84. | Variation in <i>Vout</i> 1 with the time alocation $\alpha$ 1 and $\alpha$ 2 $\epsilon$ 0, 0.6 for <i>Vin</i> of 20 V, 40 V and 60V115                                                                                                                                                                                                                 |

| 85. | Variation in <i>Vout</i> 2 with the time alocation $\alpha 1$ and $\alpha 2 \epsilon 0, 0.6$ , for <i>Vin</i> of 20 V, 40 V and 60V115                                                                                                                                                                                                                 |

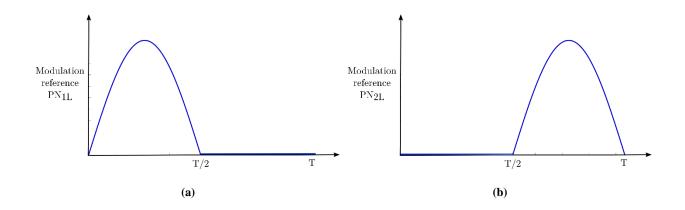

| 86. | The modulation reference signal for the power node (a) <i>PN1L</i> and (b) <i>PN2L</i> , when SIMO HFDPS |      |

|-----|----------------------------------------------------------------------------------------------------------|------|

|     | is feeding ac load using the sequential co-transfer scheme. T refers to the time of a full line cycle    | .117 |

|     |                                                                                                          |      |

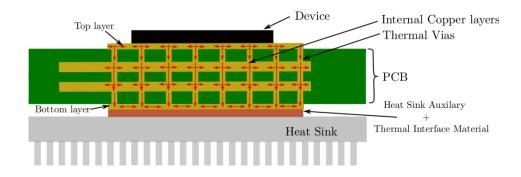

| 87. | Thermal design for a GaN <sub>PX</sub> package                                                           | .118 |

### LIST OF ABBREVIATIONS

| ASK   | Amplitude Shift Keying                  |

|-------|-----------------------------------------|

| CMOS  | Complementary Metal-Oxide-Semiconductor |

| DER   | Distributed Energy Resources            |

| DMCI  | Differential Mode Ćuk Inverter          |

| DMS   | Discontinuous Modulation Scheme         |

| DPS   | Distributed Power System                |

| DSP   | Digital Signal Processor                |

| EMI   | Electromagnetic Interference            |

| EMS   | Energy Management System                |

| ePWM  | Enhanced Pulse Width Modulator          |

| FET   | Field Effect Transistor                 |

| FSK   | Frequency Shift Keying                  |

| GaN   | Gallium Nitride                         |

| HF    | High Frequency                          |

| HFDPS | High-Frequency Distributed Power System |

| HFDT  | High-Frequency Data Transfer            |

| LPES  | Load-end Power Electronics System       |

| LF    | Low Frequency                           |

| LFPT  | Low-Frequency Power Transfer            |

| MAC   | Media Access Control                    |

| NRZ   | Non-Return-to-Zero                      |

| OEEN  | Open-Electric-Energy-Network            |

| EER   | Electric Energy Routers                 |

# LIST OF ABBREVIATIONS (Continued)

| OFDM  | Orthogonal Frequency-Division Multiplexing |

|-------|--------------------------------------------|

| РСВ   | Plastic Circuit Board                      |

| PES   | Power Electronics System                   |

| PLC   | Power Line Communication                   |

| POE   | Power Over Ethernet                        |

| PWM   | Pulse Width Modulation                     |

| RF    | Radio Frequency                            |

| Rx    | Receiver                                   |

| SCADA | Supervisory Control and Data Acquisition   |

| SCI   | Serial Communications Interface            |

| SISO  | Single-Input-Single-Output                 |

| SIMO  | Single-Input-Multi-Output                  |

| SPDT  | Single-Pole, Double-Throw                  |

| SPES  | Source-end Power Electronics System        |

| TCS   | Transient Current Suppressor               |

| TDM   | Time Division Multiplexing                 |

| TVS   | Transient Voltage Suppressor               |

| Tx    | Transmitter                                |

| WBG   | Wide-bandgap                               |

#### SUMMARY

In this dissertation, an approach for sequential transmission of high-frequency (HF) power and data signals over a common HF channel (i.e., co-transmission) is outlined. The proposed method is in contrast to conventional powerline communication (PLC), where the power and data co-transmission is simultaneous. Sequential co-transmission avoids data corruption by temporally distributing power and data signals over an HF channel and limiting their overlap. In this dissertation, a communication data-transfer architecture mechanism required to realize the sequential cotransfer approach has been outlined. Simple transmitter and receiver circuits, synthesized without the use of any analog-filtering circuitry, are designed, and an asynchronous serial-communication-interface (SCI) protocol is implemented. The sequential HF power and data co-transmission is experimentally achieved and validated on a singleinput-single-output (SISO) and a single-input-multi-output (SIMO) power electronics system. Various applications encompassing packetized power delivery empowered by the sequential co-transfer scheme are envisioned and experimentally verified. Additionally, an in-depth analysis of GaN-based power electronics system required for generating the HF power signals is undertaken, and specific design guidelines for reducing HF noise in the circuit are discussed.

# Chapter 1

# Introduction

Parts of this chapter, including figures and text, are based on my following papers:

#### © 2015-2018 IEEE

- A. Gupta, N. Kumar, and S. K. Mazumder, "Frequency-dependent criterion for mitigation of transmissionline effects in a high-frequency distributed power system," in 2015 IEEE Energy Conversion Congress and Exposition, ECCE 2015, 2015, pp. 4624–4631.

- A. Gupta and S. K. Mazumder, "Sequential Co-transmission of High-Frequency Power and Data Signals," in *IEEE Transactions on Industrial Informatics*, vol. 14, no. 10, pp. 4440–4445, 2018.

- A. Gupta, N. Kumar, and S. K. Mazumder, "Generalized Input Impedance Modeling of TL-Network-Based HFDPS for Validating Frequency-Dependent Criteria for Power-Signal Integrity," in *IEEE Transactions on Industrial Electronics*, vol. 65, no. 5, pp. 4114–4124, May 2018.

#### A. Background

Distributed power systems (DPSs) can be considered as a combination of distributed energy resources (DER) and distributed energy storage that are used for feeding power to load centers. They can range in size from as few as a couple of nodes to a system with a large number of distributed nodes. They have an ability to work off-grid and integrate communication network for information exchange. Which results in improved system efficiency, higher reliability, environmental benefits, harnessing untapped energy resources and enhanced system security. This has led to their increased interest in various flexible applications ranging from VLSI, smart buildings, electric vehicles to a tethered network of drones, etc., as are shown in Figure 1 [1]–[4]. However, these applications are coupled with an increase in size and complexity of DPSs and have resulted in a growing need for developing smart means of resource allocation and power delivery. For instance, as predicted by Moore's law, the number of transistors on an integrated circuit chip is on the rise, and so are their power requirements [5]. The existing power supplies and power distribution architecture might not be able to follow this rising trend. Thus, in this dissertation, a new scheme for transferring discrete power and data packets in a DPS is proposed.

Figure 1. Various type of distributed power systems (DPS's).

As will be discussed in the later sections, transferring power and data in discrete packets can address the manifold requirements of the DPS in the following ways,

- A higher number of loads can be managed (increase network utilization)

- Size of the energy storage can be reduced (high-speed power delivery)

- The efficiency of the DPS can be increased (reduce standby power consumption)

- Power can be delivered based on load demand (integration of information and power delivery)

#### B. <u>Overview of Distributed Power Systems</u>

Distributed power systems (DPSs) have gained widespread acceptance over the conventional power system in several flexible applications owing to its modularity, flexibility, scalability, resilience and reliable operation [6], [7]. Figure 2 illustrates various DPS mechanisms available for transferring power from the distributed energy resources (DERs) to the load(s). As outlined in Figure 2, a DPS usually comprises three functional stages. First, the energy from DER (mostly dc) is converted to slow-scale ac/dc or HF ac using source end power-electronics system (SPES). The second stage comprises of an ac/dc transmission link, which is used to transmit the power to the load(s) and also serves as an energy buffer due to the continuous availability of power. The final stage culminates in the application load(s) typically interfaced with a set of preceding power-electronics system (PES)-based active front-end(s), load end power-electronics system (LPES). However, unlike the conventional low-frequency ac or dc DPS's shown in Figure 2 (a) and Figure 2 (b), HF DPS (HFDPS) shown in Figure 2 (c) and Figure 2 (d) uses a HF link for power transmission and provides significant advantages over the latter with regard to system compactness, design simplicity, dynamic performance, lower cost, and enhanced system efficiency and reliability [8]–[12]. Because of the advantages as mentioned above, HFDPS architectures have been widely studied, and some of the proposed designs for space, telecommunication, automotive and microgrid applications are captured in Figure 3.

Although, all the DPS mechanisms outlined in Figure 2 follow the same basic structure; they mostly differ in their power delivery methodology. While, low-frequency ac, dc, and HFDPS as shown in Figure 2 (a) - Figure 2 (c) transmit continuous power, discrete HFDPS is shown in Figure 2 (d) can incorporate discontinuous power flow. This is because, unlike in the conventional HFDPS, in a discrete HFDPS modulation scheme can be discontinuous and guided

Figure 2. Illustration of (a) dc, (b) low-frequency ac, (c) HFDPS and (d) discrete HF DPSs architectures. The difference between (a), (b), (c) and (d) pertains to how the power signals are transmitted. (d) Can incorporate discontinuous power transfer whereas the rest incorporates continuous power transfer [11], ©2015 IEEE.

by network protocols which are dynamically determined based on existing load/source demand and dynamic priority assigned to each load/source by the energy management system (EMS) [13]. One of the critical advantages of incorporating a discrete HFDPS over the conventional HFDPS is that, in a discrete HFDPS, the utilization of the network can be optimized by addressing a higher number of loads/sources proficiently in an event-driven fashion guided by the dynamic-priority assigned to each load/source through the EMS [14]. The assigned dynamic priority can be based on the severity, amount and frequentness of the power required by the load. Additionally, a discrete HFDPS can also be used for shaping individual discrete HF power packets based on load requirement to reduce switching requirement at the LPES and enhance system efficiency. Moreover, by transferring power in discrete HF power packets, HFDPS can support a wide variety of sources and loads and thus can result in increased network utilization. Benefits of such a discrete HFDPS are realizable in applications ranging from nanogrids, picogrids, smartbuildings, electric vehicles, and telecommunication and are also extendable to micro and macrogrids.

Figure 3. HFDPS architectures proposed in literature for (a) space station [15] ©1988 IEEE, (b) telecommunication applications [8] ©2014 IEEE, (c) automotive application [16] ©1996 IEEE, and (d) microgrid [17] ©2003 IEEE.

### C. Overview of Communication Networks in an HFDPS

To realize the full potential of an HFDPS, a fast, reliable, and secure communication network is required to work alongside the HF power transfer network. Such a communication network can be used for implementing advanced network control algorithms by exchanging status information, control commands and sensor feedback between various PES located in the network. The present communication architecture used in the conventional power system is limited to small pockets and is mainly used for basic monitoring and surveillance tasks. Communication schemes like power line communication (PLC) and supervisory control and data acquisition (SCADA) systems, prevalent in the conventional power system, handle low data rate and use protocols designed to operate with large data overheads. Hence, they might not be capable of catering to the communication demands of an HFDPS. Typically, an HFDPS comprises of a wide variety of PESs located far from each other and connected through an HF transmission link. Thus, they will require a communication network capable of handling a high volume of real-time bi-directional data transfer between many PESs connecting various DERs to loads.

As per the above discussion, power and data network can be identified as the two main building blocks of an HFPDS. While the role of HF power network is to provide a mechanism for fast and reliable power delivery, a high-speed communication network provides flexibility and enable intelligent management of the available resources. In the past, a lot of work has been done in designing data networks that can assist in HF power delivery. They can majorly be subdivided into two categories, wireless and wire-based communication network.

#### 1. Wireless Communication Network

In a wireless communication network for an HFDPS, data is commonly transferred through a radio-frequency (RF) medium, while the power is transferred simultaneously using power transmission lines [18]–[21] or wirelessly through inductive or capacitive links [22], [23]. Wireless communication provides both flexibilities in terms of location of the data transmitter and receiver units and cost saving in deployment and maintenance. Sensors with wireless transceivers are low on maintenance and can function for an extended period using internal battery storage in harsh environments. Furthermore, wireless communication remains unaffected in case of faults on the power transmission line and serves as an excellent candidate for communication under such circumstances.

Advantages of employing wireless communication network in an HF distributed power converter have widely been explored. In [18], control of a parallel dc/dc buck converter has been demonstrated under transient and steady-state conditions using an RF-based communication network at a distance of 15 ft. As is shown in Figure 4, PWM

Figure 4. The wireless control scheme for parallel dc/dc converter [18] ©2008 IEEE.

control signals were transmitted from the master to the slave module wirelessly, ensuring equal load sharing between the two modules. Additionally, a bound on the maximum time delay in communication that the system can tolerate while ensuring system stability and performance is also provided.

Next, as shown in Figure 5 (a), a wireless communication architecture has been proposed for enhancing the stability of a droop based decentralized inverter control scheme [21]. Wireless network with the configurable delay has been used for transferring information related to real and reactive power generated at the distributed generation units. Authors in [21], reported the movement of low-frequency modes towards instability with increased delay. Further, a complete loss of stability has been reported for a communication delay higher than 20 *m*s. Numerical result outlining this finding are shown in Figure 5 (b).

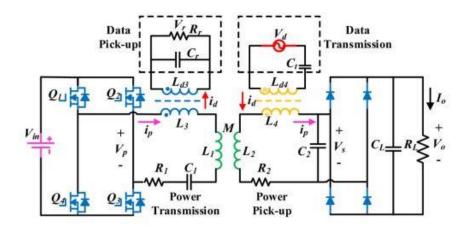

Lately, there have been significant efforts in developing methods for transmitting simultaneous wireless power and data efficiently using inductive links [22], [23]. In [22], an approach for integrating wireless bi-directional power and data transfer system has been outlined. Using the circuit shown in Figure 6, the authors reported achieving a maximum data rate of 20 *k*bps for a 500 W of power transfer between inductive coils with 7.5 cm. separation.

Figure 5. The configuration of a microgrid with wireless communication network between distributed generation units [21], and (b) Impact of communication delay on the location of different modes [21], ©2013 IEEE.

Figure 6. Schematic design of a circuit used for wireless power and data transfer [22], ©2015 IEEE.

Although attractive, integrating wireless communication network on power transmission system highly depends on its communication delay, bandwidth, environmental interference, scalability, and security [24]. Communication delay is the total of time incurred in modulating, transmitting, receiving and demodulating the data. Maximum delay handling capability of a DPS sets the communication network scheme that it can work with. For instance, in [19], the author reports that because of the delay incurred in communication, operating the parallel dc/dc converter with a 20 kHz switching frequency was not achievable. Next, the information transfer capacity of the channel is defined as its bandwidth. The rated bandwidth of a wireless network can be very different from the observed network throughput [25], due to various sources of environmental interference and cross coupling. Though wireless network may be able to provide reliable data transfer using re-transmission and error-correction coding, this may add to the communication delay and affect the overall network throughput. Moreover, there can be scenarios where setting up a wireless network for communication is related to its security. Since in a HFDPS large volume of application-critical information will be transferred wirelessly between various PESs. It is essential to develop robust cybersecurity protocols to protect the wireless communication network against such threats. As a result of all the aforementioned issues, while wireless communication networks can provide an easy and reliable communication solution, they are mainly used for short distance connection with comparatively low data rates [26].

#### 2. Wire-Based Communication Network

A wire-based communication network for an HFDPS can be further subdivided as simultaneous and sequential power and data delivery networks. In a simultaneous power and data delivery network, power and data signals are transferred together through a common waveguided medium. However, in a sequential power and data transfer network, power and data are distributed temporally.

#### <u>Simultaneous Power and Data Transfer</u>

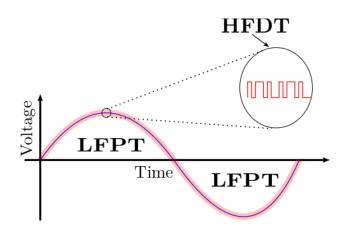

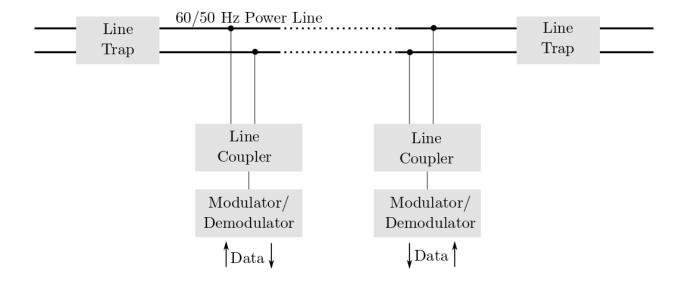

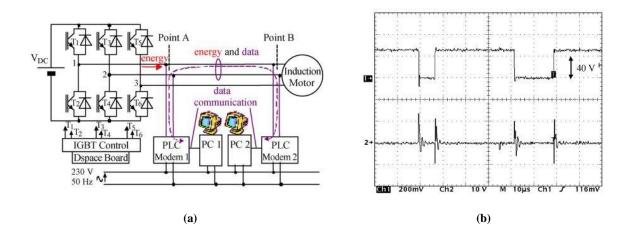

One of the most prevalent and widely researched wire-based technique for simultaneous data transmission in a DPS is the power line communication (PLC) [27]–[29]. In PLC, low voltage HF data signals are transmitted over a high voltage power transmission network which generally operates at a frequency of 50/60 Hz. Figure 7 illustrates the coupled HF data and LF power signals which are being transmitted simultaneously over the power lines. Conventional PLC architecture comprises of 4 essential components, line traps, modulator/demodulator, line couplers, and the transmission link. Figure 8 outlines the underlying architecture of a PLC-based sequential power and data transfer network. First, data to be transmitted is modulated to an HF signal using one of the various modulation techniques (FSK, ASK, OFDM, etc.) in a modulator unit. Later, inductive or capacitive line couplers are used to couple the HF modulated data to the high voltage power signals which are being transmitted over the power line. At the receiving end, line couplers and demodulator unit act as a receiver and are used to extract HF data from the power lines. Line

traps in the form of parallel resonant circuits are placed in the power lines to provide a high impedance to the HF modulated data signals and prevent them from traveling to unwanted locations.

Figure 7. Illustration of a conventional PLC technique with simultaneous low-frequency power transfer (LFPT) and HF data transfer (HFDT) [30], ©2018 IEEE.

Figure 8. The underlying architecture of a PLC-based simultaneous power and data transfer network.

PLC is widely used over LF sinusoidal network, this can mainly be attributed to the fact that the wide separation between the frequency spectrums of the two signals (LF power signals and HF data signals) being transmitted over the power line enables the construction of simple but large reactive couplers, line traps, and low-order analog-filtering circuitry. Furthermore, networking features like Power Over Ethernet (POE) have surfaced using PLC technology, which uses an ethernet cable for supplying power to network devices over the existing data connection. However, the power delivery capacity of a POE network is limited to 51 Watt by IEEE 802.3at-2009 [31]. This enables the integration of the PLC receivers and transmitters in small-sized packages for networked devices.

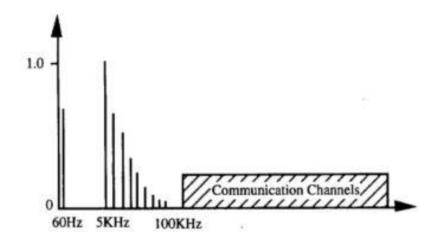

Recently, the use of PLC has been proposed for applications involving HF power transfer. Significant research efforts have been placed in application focusing on the design of a PLC network for PWM-inverter fed electric machines [30], [32]–[37]. Transmission characteristics of PWM-inverter-fed power lines are entirely different from that of a 50/60 Hz power transmission line. This is because the output voltage of a PWM inverter consist of pulses or square waves having sharp edges with variable frequency and duration. Thus, the power carried by such signal is distributed across a much broader frequency spectrum. For instance, the output voltage spectrum of a typical sinusoidal PWM inverter operating at a switching frequency of 12 kHz is provided in Figure 9 [35]. As evident from Figure 9, in comparison to the output of a 60 Hz power line, which only has the power transfer at the fundamental frequency, the output of a PWM inverter has a large amount of switching frequency harmonics which extend up to the *k*Hz range. Although, the power residing in the high-frequency components is low, it can be enough to corrupt the low-voltage data signals that are being transmitted in the communication band. Thus, the focus of the past research has mainly been on designing new PLC modems that can facilitate coupling/decoupling of the HF low-voltage data signals on the HF high-voltage power signals with high slew rates effectively.

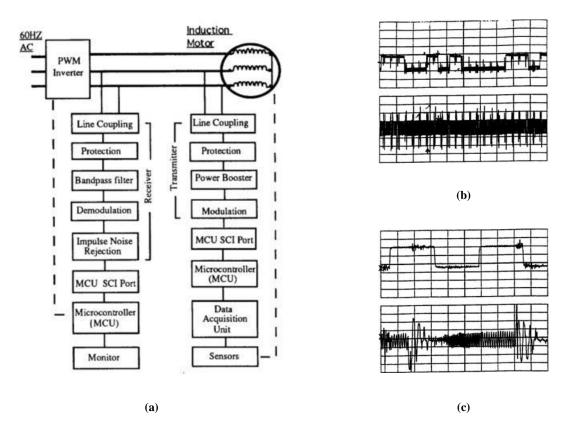

In [35] Chen et al. proposed a PLC-based approach for monitoring the winding temperature of a PWM-inverter fed induction motor. Schematic diagram of the developed motor condition monitoring system and reported experimental results are provided in Figure 10. A passive line coupling circuit consisting of HF transformer and capacitors was used to block the low-frequency PWM waves in the PWM-inverter fed power line from entering the data circuit. While at the same time coupling circuit provided a low impedance path for the HF communication carriers to the PWM-inverter fed power line. In the designed data circuit, Class B amplifier was used as a booster circuit for

Figure 9. Transmission characteristics of a typical PWM-inverter fed power line [35], ©1993 IEEE.

amplifying the low voltage FSK modulated data signals. A high order (ten poles) Butterworth bandpass filter centered at the communication frequency was employed at the receiver side to extract the HF data from the noisy power line. As can be seen from the experimental results of [35] provided in Figure 10 (b) and Figure 10 (c), for every PWM switching action, impulse noise was introduced in the data signals and caused data corruption. Finally, it has been reported that using a modified high-order low-pass filtering circuit and digital data recovery techniques; the authors were able to establish a satisfactory PLC network operating with a maximum data rate of 9600 bps (bauds per second) over power line feeding PWM signals to the motor. Similar observations were reported in [38], where the authors were able to achieve a maximum data rate of 40 kbps by avoiding data transfer during the event of switch transitions.

Further, in [33], [34], the authors presented a scheme for realizing PLC over HF PWM network using OFDM modulated data signals. Effect of PWM switching frequency, output voltage magnitude and length of power cable on PLC data transfer rate were studied. In this study, up to 90 % reduction in data rate was reported at a higher noise level and long transmission lengths. The main reason for the reduced data rate was reported as the increased magnitude of HF switching noise at higher voltage levels and attenuation of the HF data signals. The experimental setup and obtained results in [34] are shown in Figure 11 (a) and Figure 11 (b), respectively. Moreover, the authors reported that even with an LCL low-pass filter connected to the inverter output terminal (used for reducing PWM-inverter output voltage slope), significant voltage spikes were observed in the communication circuit.

Figure 10. (a) Schematic of the motor condition monitoring system using PLC as proposed in [35]. (b) Experimental plots of the transmitted data signal at the data input pin and signals at the primary terminal of the coupling transformer. (c) zoomed in version of the waveforms provided in (b), ©1993 IEEE.

Figure 11. (a) Developed experimental setup for realizing PLC over PWM in [34], and (b) obtained experimental results showing PWM inverter output voltage and injected HF noise in the data circuit at every switching instant, ©2010 IEEE.

#### • Sequential Power and Data Transfer

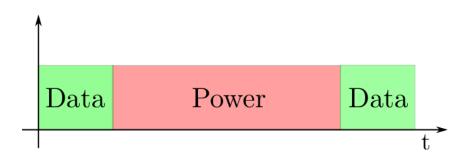

Another technique for power and data transfer through a wired-medium is the sequential transmission of power and data signals which is mainly employed in DPSs using packetized energy transfer [30], [39]–[42]. In this scheme, power and data signals are transmitted sequentially (as shown in Figure 12.), thereby ideally eliminating any spectral overlap between the two [30]. Sequential transfer of power and data was first conceptualized by Toyoda and Saitoh in terms of an open-electric-energy-network (OEEN) [43], [44]. In an OEEN, electric power was treated as a mail packet with its source and destination information attached to it in the form of data tags. Further, a network of multiple electric-energy-routers (EER's) was conceptualized to distribute the energy packets from various DER's to loads based on the tagged information. However, details about the shape, size, and frequency of the energy packets and the data tags were not discussed. Additionally, the research was ahead of its time, and the technological limitations restricted the practical realization of the mechanism required for generating these energy packets, data tags, and EER.

Figure 12. The basic structure of a power and data signal in a sequential power and data transfer scheme.

Owing to the advancements in the semiconductor industry, recently, sequential transfer of power and data signals has been proposed for HFDPS. In it, in contrast to a conventional DPS, where energy flow is constant, energy is transferred in the form of small energy packets along with information tags. In some applications, the attached information tag is used for ensuring system safety [39], while in others it is used for routing the energy packets through a network of energy routers from their source to destination [40]–[42]. Packetized energy transfer gives rise to multiple possibilities concerning how energy and information can be exchanged in an HFDPS. It forms the cornerstone for the research in digital grids, where the packetized energy transfer in a power network is envisioned as the data packet transfer in a computer network [45]. Additionally, packetized power transfer makes it possible for controlling the shape, size, and frequency of the power packets, which can now be tailor-made to cater to various time/event-driven

15

applications. However, the realization of such a system requires the development of highly sophisticated power and communication architecture that can coordinate and optimize the flow of energy and data packets in an HFDPS.

In recent days, various architectures for HFDPS supporting packetized power transfer have surfaced. Voltserver came up with the concept of "Digital Electricity" [39], [46], where power and data are transferred in packetized format from a transmitter unit to a receiver unit at a rate of 700 packets per second through a pair of conductor cables [46]. Although minimal information is available about the transmitter and receiver units, it is stated that the transmitter unit can be connected to any source with ac or dc output and transmit energy packets in the form of high-voltage dc signals over the conductor cable [39]. Once the high-voltage dc energy packets arrive at the receiver unit, they are converted back to an analog format at the correct voltage and power level required by the load. Data packets transmitted sequentially with the energy packets are used for monitoring system safety, by ensuring proper delivery of each energy packet from the transmitter to the receiver units. Each transmitter unit is said to have 24 line-cards that can support up to 24 receiver units in a single-input-single-output (SISO) configuration [46]. Though beneficial, "Digital Electricity" fails to realize the full potential of packetized power transfer concerning an HFDPS. This is because the developed system requires a dedicated transmitter for a dedicated receiver which as in a conventional HFDPS needs devoted power cables that leads to an increase in overall system cost and restricts the possibility of energy packet routing from multiple sources to multiple loads.

To enable the routing of energy packets in an HFDPS between various DER's and loads, in [40], [41] designs for power packet mixer and router units were provided. In the arrangement presented in [40], multiple DERs and loads were connected through the mixer, transmission line, and a router. Mixer unit had the role of connecting various DERs to a common transmission line, while, the router unit which was connected to the same transmission line, was used to connect/disconnect the loads. Information tags were physically attached to the power packet and contained information about the address of its source and destination load [40]. A pictorial representation of the prototype system as provided in [40], is presented in Figure 13. Additionally, circuit representation of the proposed mixer and router units in [40] are provided in Figure 14 (a) and Figure 14 (b), respectively.

Figure 13. Schematic of the power packet dispatch system outlined in [40].

Figure 14. Schematic of power packet mixer and router units outlined in [40]

As can be observed from Figure 14 (a) and Figure 14 (b), designed mixer and router units had a diode in their forward path. It was used for avoiding the reverse flow of energy in the developed prototype. However, apart from inducing additional losses (which will be significant at high power levels), the diode also restricts the ability of the developed prototype in [40] to support the bi-directional transfer of the energy packets through the common TL connecting mixer and router. This limitation restricts the adoption of such mixer and router prototypes in HFDPS that require bi-directional power flow for applications encompassing energy storage systems, motor drives, etc. Moreover, the channel for power and data transfer is not decoupled, this results in HF data signals to be transmitted to the load. This can be observed in the experimental results provided in [40, Fig. 12]. Additionally, in experimental results provided in [41, Fig. 5] for a sub-1W system, large magnitude HF voltage spikes are visible at the load terminal during the time data is transmitted on the TL. This can lead to deterioration of closed-loop dynamics of the system as slower-