## Algorithm-Hardware Co-design for Low-Power Smart Home AI Devices

BY

NIKOLAI ILIEV B.Sc., Northwestern Univ., 1986 M.Sc., University of California Irvine, 1988

#### THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2020

Chicago, Illinois

Defense Committee:

Amit Trivedi, Chair and Advisor Igor Paprotny Wenjing Rao Vitali Metlushko Zhao Zhang Arun Subramanian, Mechanical and Industrial Engineering Copyright by

Nikolai Iliev

2020

to my parents and to my family

## ACKNOWLEDGMENTS

I'm indebted to many people for their continuing support leading to this dissertation. First, I would like to thank my adviser, Amit Trivedi, for his support and trust. His supportive guidance helped me navigate through the problems in neuromorphic systems and his trust gave me enough freedom to enjoy exploring the field. I would also like to thank Igor Paprotny for introducing me to the field of Smart-Dust sensor networks and their self-localization and implementation problems. I enjoyed being exposed to his insights and benefited from our discussions. I would also like to thank Wenjing Rao and Zhao Zhang for commenting on my research and providing valuable feedback on different VLSI architectural topics.

Being a member of the AEON lab at the University of Illinois at Chicago (UIC) was a great experience for me. The collaborations and discussions over the years helped me grow, personally and intellectually. I thank my co-authors, Alberto Gianelli, Shama Nasrin, Ahish Shylendra, and Mahdi Salarian, for their contributions in the projects. Many of the ideas in our work emerged from our discussions and teamwork. Also many thanks go to my labmates : Abhinaya Ganesh, Edoardo Roba, Andrea Ciccardi, and Priyesh Shukla.

To my parents, Dr. Kirilka Petrova Chureva-Ilieva, MD Ph.D. 1962 Medical Academy Sofia, Bulgaria, and Yuli Nikolov Iliev, PE M.S. 1959 Civil and Mech. Eng., MEI Technical Univ. Sofia, Bulgaria, thank you for all your support and encouragement. To Ivan Petrov Churev, mathematician, Ph.D. 1980, Institute of Mathematics BAN, Shumen, Bulgaria, thank you for sparking my interest in advanced mathematics. To my wife Magdalena and son Johnny, thank you for putting up with my endless theoretical discussions at home and for making it all possible.

# ACKNOWLEDGMENTS (Continued)

NI

## PREFACE

This dissertation is an original intellectual product of the author, N. Iliev. All of the work presented here was conducted in the AEON Lab at the University of Illinois at Chicago.

The main theme in this work is hardware algorithm acceleration for sensor-equipped embedded hardware/software System-on-Chip, SoC, as found in indoor mobile platforms such as indoor robotic assistants. The accelerators are designed to assist the SoC in platform self-localization in indoor space, in human voice control of the platform, and in neural network processing of data acquired by the platform's sensors.

The project has been partially supported by UIC College of Engineering.

The results of these works have previously appeared (or is appearing) as journal and conference publications (Iliev and Trivedi, 2019) IEEE Sensors Letters, (Iliev et al., 2019) IEEE Embedded Systems Letters, (Iliev and Trivedi, 2017) IEEE International Conference on Computer Design, ICCD, (Iliev and Paprotny, 2015) IEEE Sensors Journal, (Gianelli et al., 2019) IEEE Symposium on Low-Power and High-Speed Chips and Systems, (Salarian et al., 2018) IEEE Transactions on Multimedia, and (Salarian et al., 2016) IEEE International Symposium on Multimedia (ISM).

The copyright permissions for reusing the published materials have been presented in Appendix A.

Nick Iliev April 15, 2020

## **CONTRIBUTION OF AUTHORS**

A version of Chapter 4 and Chapter 5 has been published in IEEE ICCD 2017 Conference and in 2019 IEEE Sensors Letters journal. Amit Trivedi, my adviser, was the lead investigator in the spatial self-localization project. I was responsible for building and developing the majority of the ideas, implementing the FPGA and ASIC based spatial self-localization, SSL, accelerator, collecting and analyzing the data and finally, composing the manuscript. Igor Paprotny was involved in the early stages of concept formation of optical Angle of Arrival sensors for localization and localization of mobile platforms in general. A version of Chapters 8 and 9 has been published in IEEE Embedded Systems Letters journal. Amit Trivedi, my adviser, was the lead investigator in this project. I was responsible for building and developing the majority of the ideas, implementing the FPGA and ASIC speaker-recognintion, Sp-krRec, accelerator, collecting and analyzing the data and finally, composing the manuscript. Alberto Gianelli was involved in the early stages on the definition of the SpkrRec interface to a generic Gaussian Mixture Model, GMM, LUT-free architecture for speaker recognition. A version of Chapters 12 and 13 has been submitted for publication to IEEE Transactions on Computers.

# TABLE OF CONTENTS

| <u>CHAPTER</u> |         |                                                                    | PAGE |

|----------------|---------|--------------------------------------------------------------------|------|

| 1              | INTRO   | DUCTION                                                            | 1    |

|                | 1.1     | Spatial Self-Localization                                          | 1    |

|                | 1.2     | Speaker and or Command Recognition                                 | 1    |

|                | 1.3     | Fully Connected Layers for Neural-Network Processing               | 2    |

|                | 1.4     | Thesis Organization                                                | 3    |

| 2              | SSL INT | <b>ΓRODUCTION</b>                                                  | 9    |

| 3              | SSL BA  | CKGROUND AND NOTATION                                              | 11   |

|                | 3.1     | RNN formulation of AOA-based 3D Localization                       | 13   |

|                | 3.1.1   | Complexity of Primal-Dual Linear Program Solution                  | 17   |

| 4              | SSL DE  | SIGN FEATURES AND PARAMETERS                                       | 18   |

|                | 4.1     | Low Power Digital Microarchitecture for RNN-based Localization .   | 18   |

|                | 4.1.1   | Matrix-vector product with sub-matrix scheduling                   | 20   |

|                | 4.1.2   | Low Power Comparator Unit                                          | 21   |

| 5              | SSL SIN | AULATION AND IMPLEMENTATION RESULTS                                | 23   |

|                | 5.1     | Simulation Results                                                 | 23   |

|                | 5.1.1   | Functional Simulations                                             | 23   |

|                | 5.1.2   | FPGA Implementation Results                                        | 25   |

|                | 5.1.3   | PDK45 ASIC Implementation                                          | 27   |

|                | 5.2     | Conclusion                                                         | 28   |

|                | 5.2.1   | Comparison to Cholesky decomposition with forward/backward sub-    |      |

|                |         | stitution                                                          | 30   |

|                | 5.2.2   | Comparison to QR (QRD) Decomposition using Householder trans-      |      |

|                |         | formation                                                          | 30   |

|                | 5.2.3   | Comparison wih Adjoint Matrix method for matrix inversion to solv- |      |

|                |         | ing Linear System                                                  | 31   |

|                | 5.2.4   | Comparison with Cayley – Hamilton Method for NxN matrix inversion  | 31   |

|                | 5.2.5   | Comparison with EKF                                                | 32   |

|                | 5.2.6   | Comparison with EIF                                                | 32   |

|                | 5.2.7   | Comparison with SPKS                                               | 33   |

|                | 5.2.8   | Comparison with Particle filter                                    | 33   |

| 6              | SPEAK   | ER RECOGNITION INTRODUCTION                                        | 36   |

# TABLE OF CONTENTS (Continued)

## **CHAPTER**

| 7  | 7 BACKGROUND IN POWER SAVING TECHNIQUES FOR GMM C<br>SIFIERS OF SPEAKERS |                                                             | 39 |

|----|--------------------------------------------------------------------------|-------------------------------------------------------------|----|

|    | 7.1                                                                      | Complexity of online k-Means clustering (Lloyd's algorithm) | 40 |

| 8  | SPKRR                                                                    | EC DESIGN FEATURES AND PARAMETERS                           | 41 |

|    | 8.1                                                                      | Online k-Means Clustering Architecture                      | 41 |

|    | 8.1.1                                                                    | Squared Euclidean Distance Computation Unit                 | 41 |

|    | 8.1.2                                                                    | Nearest Centroid Identification Unit                        | 42 |

|    | 8.1.3                                                                    | Centroid Update Unit                                        | 44 |

| 9  | SPKRR                                                                    | EC SIMULATION AND IMPLEMENTATION RESULTS                    | 46 |

|    | 9.1                                                                      | Simulation Setup                                            | 46 |

|    | 9.2                                                                      | Functionality Characterization                              | 48 |

|    | 9.3                                                                      | Energy Efficiency Characterization                          | 48 |

|    | 9.4                                                                      | Comparison to alternative frame reduction approaches        | 52 |

|    | 9.5                                                                      | CONCLUSION                                                  | 53 |

| 10 | 10 INTRODUCTION TO ACCELERATION OF FULLY CONNECTED LAY-                  |                                                             |    |

|    | ERS .                                                                    |                                                             | 56 |

| 11 | BACKG                                                                    | ROUND ON FULLY CONNECTED LAYERS IN CNNS                     | 62 |

| 12 | DESIGN                                                                   | N FEATURES AND PARAMETERS OF FC-ACCEL                       | 68 |

|    | 12.1                                                                     | HBM Data-Prefetch Unit and On-chip Buffer, DPR-BUF          | 69 |

|    | 12.2                                                                     | Matrix-Vector Multiplier Unit                               | 72 |

|    | 12.3                                                                     | Vector Accumulator Unit                                     | 75 |

|    | 12.4                                                                     | ReLU and Bias Addition Unit                                 | 76 |

|    | 12.5                                                                     | Main Processing Sequence                                    | 77 |

| 13 | SIMULA                                                                   | ATION AND ASIC IMPLEMENTATION RESULTS OF FC-ACCEL           |    |

|    | FOR FC                                                                   | CLAYERS IN ALEXNET AND VGG16                                | 80 |

|    | 13.1                                                                     | CMOS ASIC Implementation                                    | 83 |

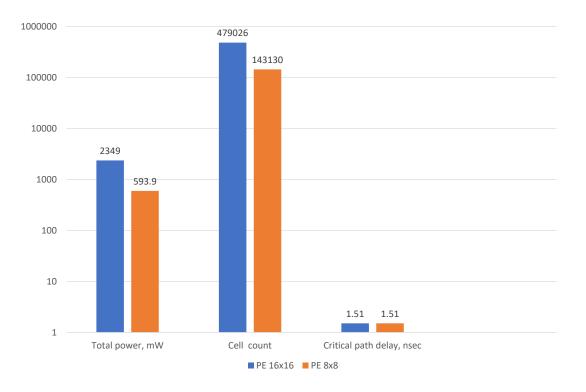

|    | 13.2                                                                     | Characterization of a pipelined 16x16 PE                    | 85 |

|    | 13.3                                                                     | FC8 Latency for 1 HBM Shared by 128 PEs                     | 87 |

|    | 13.4                                                                     | FC-Accel Complexity Analysis                                | 88 |

|    | 13.5                                                                     | Up-Scaling to Larger FC Layers                              | 89 |

| 14 | OPEN P                                                                   | PROBLEMS AND ACCELERATOR EXTENSIONS FOR THEM                | 94 |

|    | 14.1                                                                     | Spatial Localization - SSL Extensions                       | 94 |

|    | 14.1.1                                                                   | Non-Linear Cost Function for AOA based Estimation           | 94 |

|    | 14.1.2                                                                   | Multi-Modal methods                                         | 97 |

|    | 14.2                                                                     | Speaker Recognition - SpkrRec Extensions                    | 98 |

# TABLE OF CONTENTS (Continued)

## **CHAPTER**

## PAGE

|    | 14.2.1      | Learning the Optimal Number of Clusters                                                  | 98  |

|----|-------------|------------------------------------------------------------------------------------------|-----|

|    | 14.2.2      | Simulated Anealing schedule                                                              | 99  |

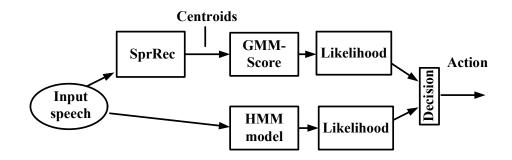

|    | 14.2.3      | 2.3 Integration with a GMM-scoring block and Command Recognition for Robotic Arm control |     |

|    | 14.3        | Fully Connected layers in DNNs - FC-Accel Extensions                                     | 101 |

| 15 | CONCLUS     | SION                                                                                     | 109 |

|    | APPENDIX    | κ                                                                                        | 113 |

|    | CITED LI    | TERATURE                                                                                 | 121 |

|    | <b>VITA</b> |                                                                                          | 127 |

# LIST OF TABLES

| <b>TABLE</b> |                                                                                                                                                | PAGE |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Ι            | FC8 LATENCY FOR 8X8 AND 16X16 PE WITH 1 HBM AND 128 PE<br>MODULES. THE NUMBER OF READ ACCESSES TO THE HBM ARE<br>LISTED FOR EACH PE DIMENSION. | 87   |

| Π            | FC8 LATENCY FOR 8X8 AND 16X16 PE WITH 1 HBM AND 128 PE<br>MODULES. THE NUMBER OF READ ACCESSES TO THE HBM ARE<br>LISTED FOR EACH PE DIMENSION. | 93   |

# LIST OF FIGURES

| <b>FIGURE</b> |                                                                                                                                                                                                                                                                                                                                                                                | PAGE |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1             | Sensor localization in 3D with 4 anchors and Angle-of-Arrival (AOA) mea-<br>surements.                                                                                                                                                                                                                                                                                         | 13   |

| 2             | RNN-based co-processor for 3D localization with <i>M</i> anchors. $\theta(n+1)$ represents the predicted target location at step $n+1$ .                                                                                                                                                                                                                                       | 19   |

| 3             | Distributed arithmetics for vector-vector multiplication.                                                                                                                                                                                                                                                                                                                      | 20   |

| 4             | Comparator unit for three 16-bit signed two's complements                                                                                                                                                                                                                                                                                                                      | 22   |

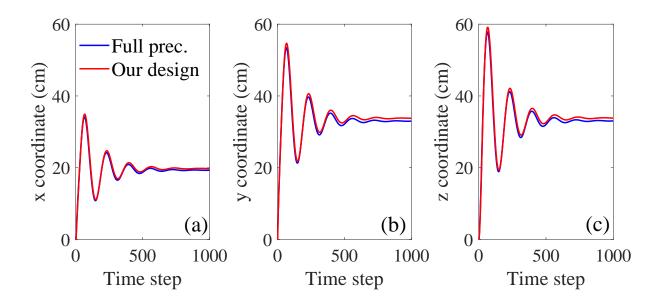

| 5             | The comparison of functional simulations against fixed-point Verilog. Ver-<br>ilog simulations are done in $Q(10,17)$ format                                                                                                                                                                                                                                                   | 24   |

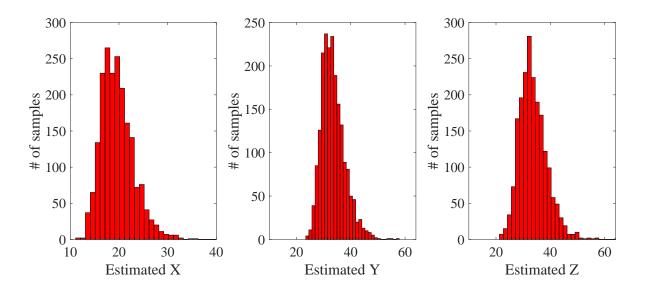

| 6             | Histogram of the estimated coordinates. In each subplot, two thousand samples from the fixed point Verilog simulations are used.                                                                                                                                                                                                                                               | 25   |

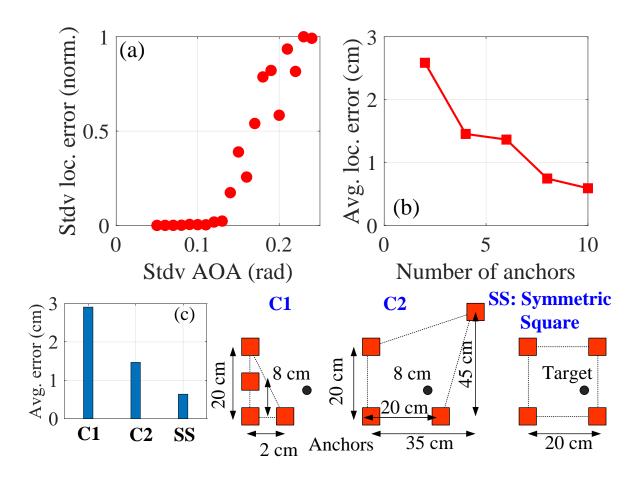

| 7             | (a) Standard deviation of localization error at increasing standard deviation<br>of AOA noise. (b) Average localization error for thousand runs computed as<br>Euclidean distance from the ground truth at varying number of anchors. (c)<br>Localization error at various anchor configurations considering four anchors.<br>Results in (a) and (b) are for configuration C2. | 26   |

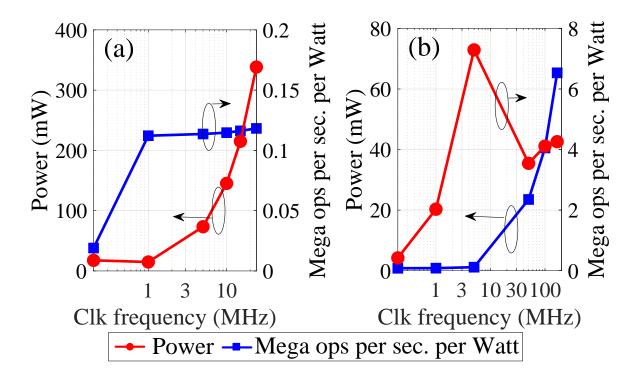

| 8             | Power characterization of (a) FPGA and (b) ASIC implementation. FPGA is implemented in 180 nm technology. ASIC is implemented using 45 nm predictive technology models.                                                                                                                                                                                                        | 27   |

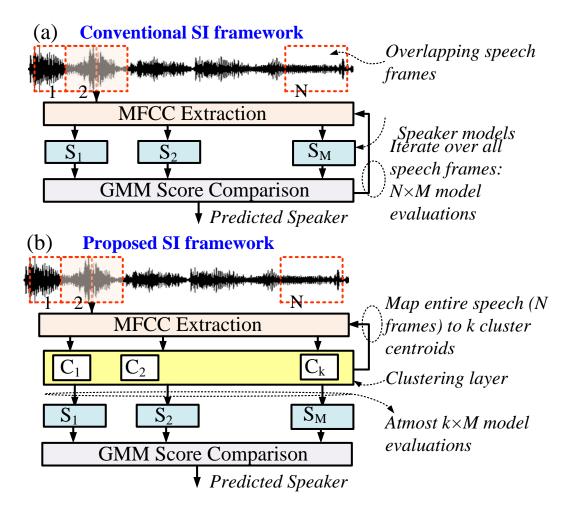

| 9             | SI computations flow: (a) The standard architecture where all $N$ frames of MFCC vectors are processed, for a total of $N \times M$ GMM evaluations. (b) The proposed architecture adds a clustering layer (CL) to map MFCC frames to $k$ centroids which reduces the total GMM evaluations to atmost $k \times M$                                                             | 37   |

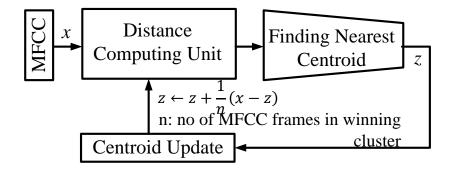

| 10            | Overview of our clustering approach.                                                                                                                                                                                                                                                                                                                                           | 40   |

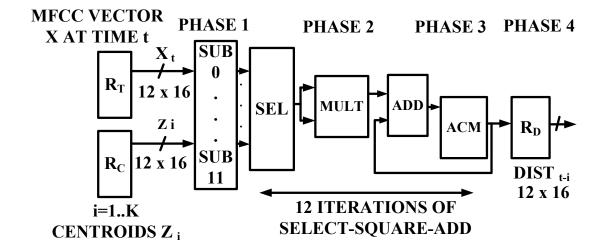

| 11            | Datapath for computing the squared Euclidean distance between a new MFCC feature vector $x_i$ and all $k$ centroids $z_i$ .                                                                                                                                                                                                                                                    | 42   |

# LIST OF FIGURES (Continued)

# **FIGURE**

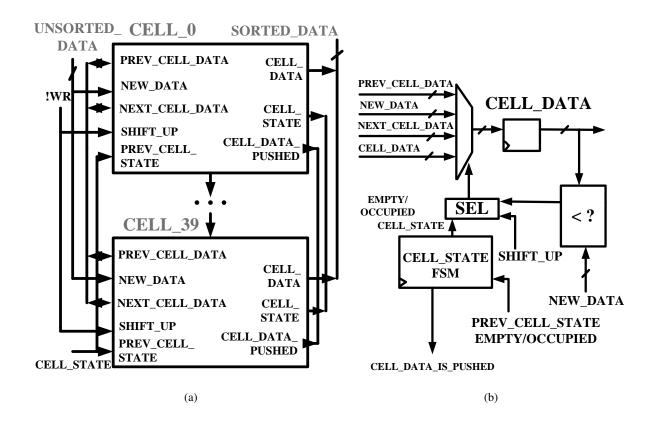

| 12 | (a) Systolic array for sorting a serial input stream of M words in M clock cycles. (b) Processing cell in the array.                                                                                                                                                                                                                                                                        | 43 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

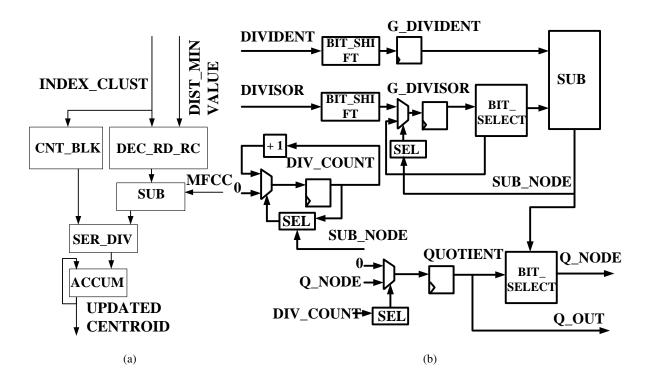

| 13 | (a) Centroid update unit for updating only the winning centroid. (b) Bit-<br>serial divider for dividing an element from <i>SUB</i> by the current value from <i>CNT_BLK</i> . Only the quotient is used in the downstream processing                                                                                                                                                       | 45 |

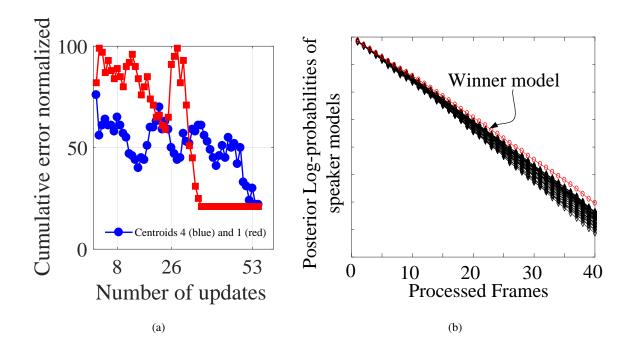

| 14 | (a) Convergence of the cumulative error for centroids 1 and 4. Note that the residual value of 20 is reached after 35 frames (iterations) for centroid 1 and after 54 frames for centroid 4. Different centroid estimates converge to their residual values for a different number of frames. (b) Evolution of posterior log-probabilities of 38 test speakers.                             | 47 |

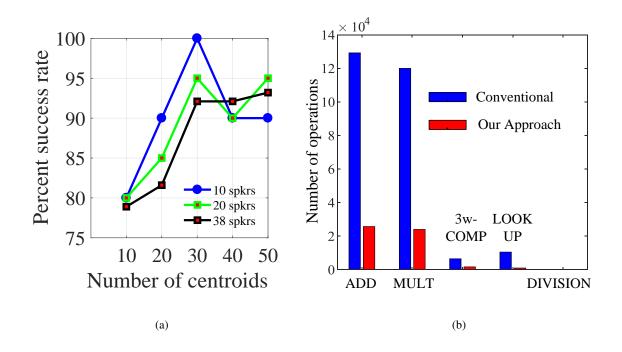

| 15 | <ul> <li>(a) Success rate vs. number of speakers and number of centroids per speaker</li> <li>10 speakers (blue) 20(green) 38(black). (b) Reductions in number of operations: blue for GMM scoring with non-clustered frames; orange for the proposed GMM scoring with forty centroids.</li> </ul>                                                                                          | 49 |

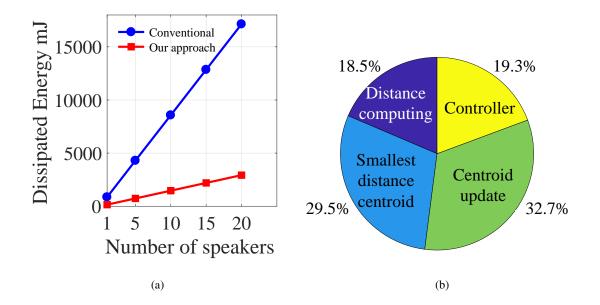

| 16 | (a) Energy dissipation vs. number of speakers. Blue trace is scoring all 500 MFCC test frames with all GMM models. Red trace is scoring forty centroids with all GMM models. (b) Breakdown of power dissipation for the centroid estimator architecture.                                                                                                                                    | 52 |

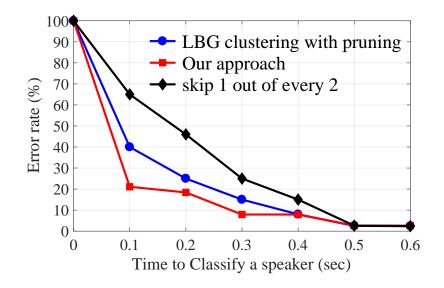

| 17 | Error rate vs. time to classify a test speaker.                                                                                                                                                                                                                                                                                                                                             | 54 |

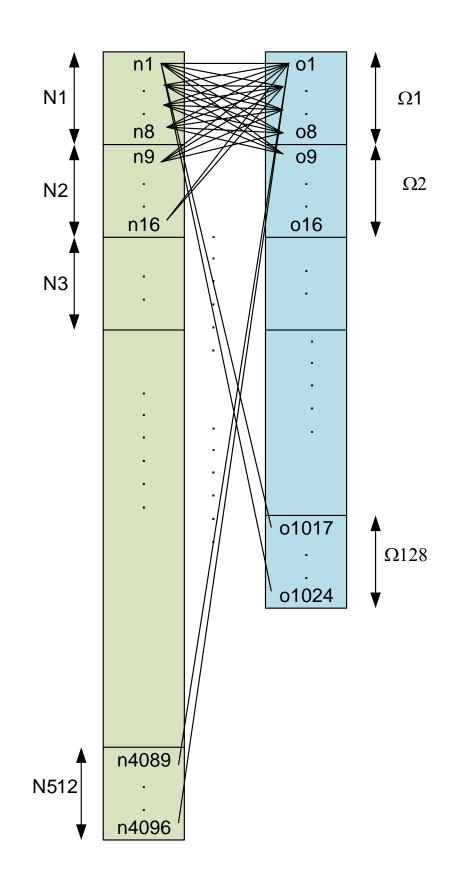

| 18 | Fully Connected FC8 layer in AlexNet or VGG-16: 4096 input and 1000 outputs. Groups of 8 are indicated in the input and output vectors respectively.                                                                                                                                                                                                                                        | 60 |

| 19 | The equivalent matrix-vector multiplication for the FC layer in Fig. 1. The weights are grouped in 8x8 sub-matrices (tiles) W1, W2, etc. Each column of sub-matrices is mapped, during its time-slot, to a set of 128 MACs and 128 PEs. This is the columnwise block(tile) decomposition used in FC-Accel. The same set of MACs and PEs is reused for all 512 time-slots during processing. | 61 |

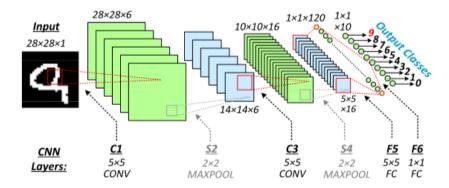

| 20 | Fully Connected layer FC F5-F6 in a typical CNN. F5 is a 1D vector of 120 input scalar features and F6 is a 1D vector of 10 output scalar features.                                                                                                                                                                                                                                         | 63 |

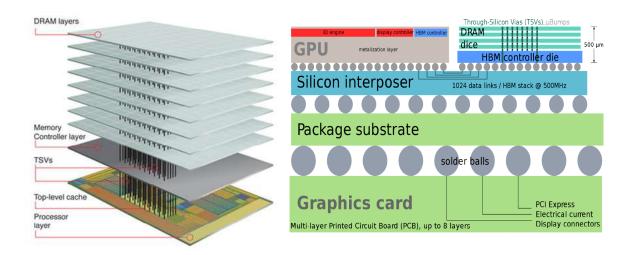

| 21 | HBM 3D SDRAM memory stack technology (left) and GPU or general purpose (FC Accelerator instead of GPU) application (right).                                                                                                                                                                                                                                                                 | 65 |

# LIST OF FIGURES (Continued)

# **FIGURE**

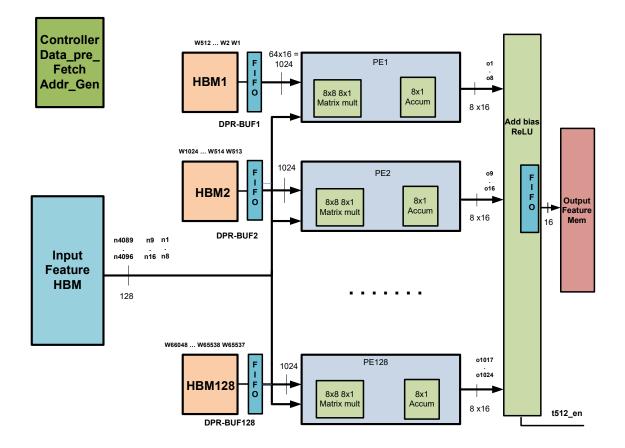

| 22 | High level architecture block diagram. Each HBM has a dedicated data-<br>pre-fetch and on-chip buffer unit, DPR-BUF, with 8 rate matching FIFOs. An<br>HBM's DPR-BUF ensures that 1024 bits of weights, stored in the on-chip<br>buffer, are aligned for a single cycle read by the PE. Input and output mem-<br>ories have dedicated address generators. One top-level controller schedules<br>the data flow in all 128 PE channels.                                                                                                                    | 70 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

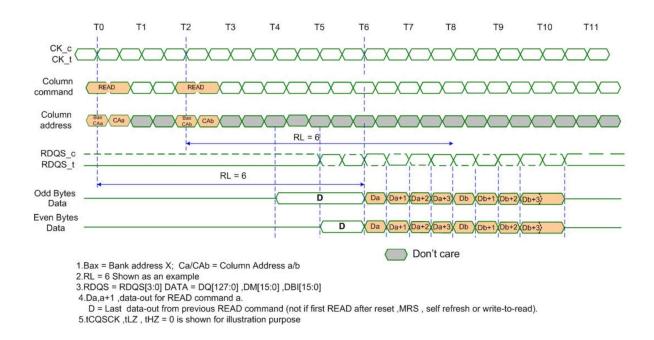

| 23 | Read access timing from JESD235C. The access starts with the first read request to column address Ca. After R T-cycles (T0 to T6 for R=6 example) a burst of 4 128-bit words, Da to Da+3, is available on DQ[127:0]. Similarly, the second read request to column address Cb generates a burst of 4 128-bit words, Db to Db+3. The DPR-BUF combines the 8 128-bit words and writes them into 8 corresponding FIFOs. The 8 FIFOs are then read into the 1024 bit on-chip buffer.                                                                          | 72 |

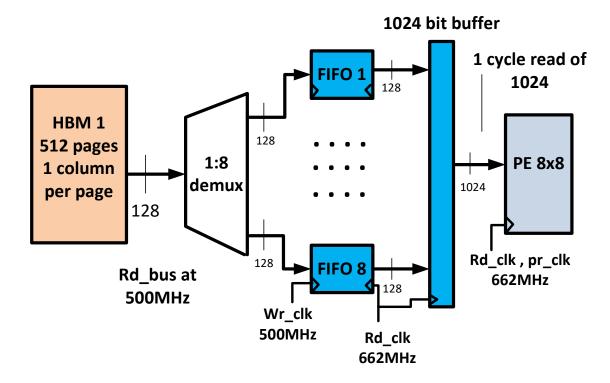

| 24 | Data prefetcher and on-chip buffer for HBM read accesses. One HBM is<br>shown driving weights to its PE. The main contoller issues two read requests to<br>column addresses Ca and Cb. Each request generates a burst of 4 128 bit trans-<br>actions on DQ. The pefetcher write 8 128 bit DQ values into 8 corresponding<br>FIFOs. A read request is then issued to all FIFOs, and their output is stored<br>in a single 1024 bit register. This aligns the weights read-out cycle with the<br>HBM-IN read out of the next 8 16-bit input feature values | 73 |

| 25 | DPR-BUF HBM memory read out cycles m1 to m8 in the 500MHz domain<br>and FIFO write cycles wr1 to wr8. FIFO read cycle Rd and PE processing<br>cycles P1 to P3 are in the 662 MHz domain. The FIFO is read every 4th cycle.                                                                                                                                                                                                                                                                                                                               | 74 |

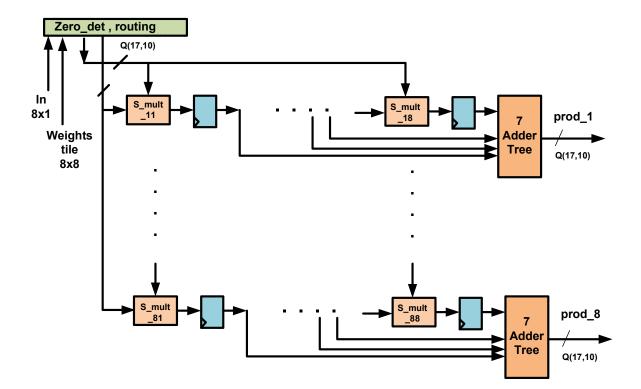

| 26 | MV-mult micro-architecture for 8x8 tile of weights.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75 |

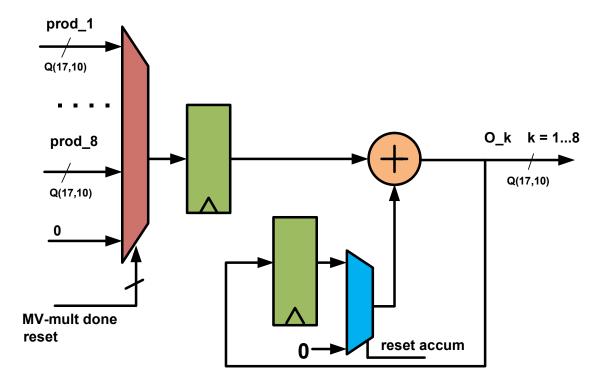

| 27 | Vector accumulator V-Accum datapath.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76 |

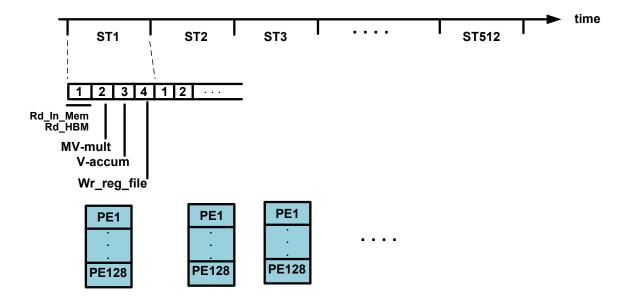

| 28 | Main controller sequence. All 128 PEs are processing a new 8x1 feature vector from In-MEM in each state ST1 ST512. In each state an 8x8 tile of weights is read from the HBM corresponding to each PE.                                                                                                                                                                                                                                                                                                                                                   | 77 |

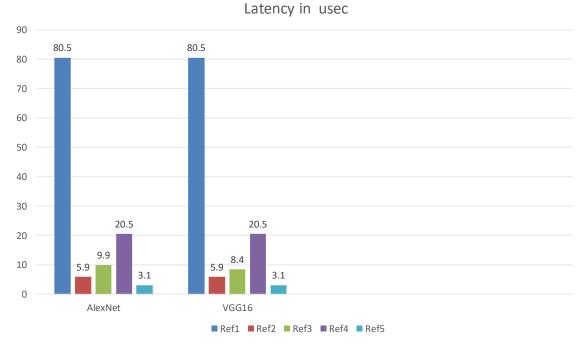

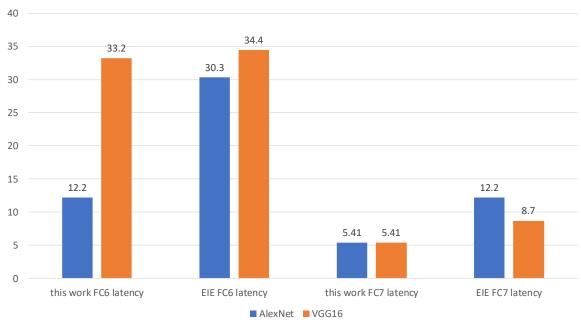

| 29 | Processing latency for FC8 in usec for several benchmarks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81 |

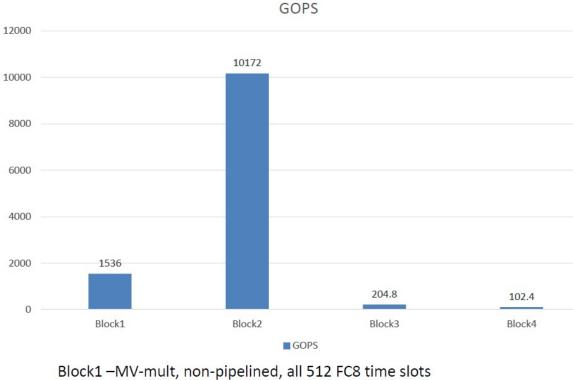

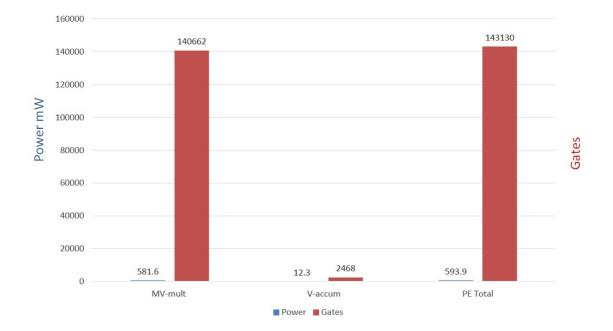

| 30 | Processing Blocks performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 82 |

| 31 | Power per PE processing block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83 |

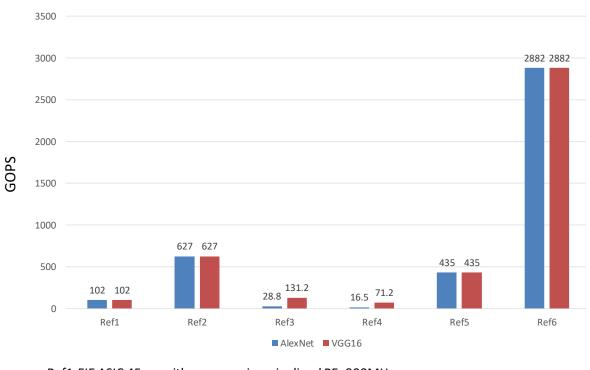

| 32 | GOPS comparison with ASIC and FPGA platforms for FC8 acceleration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84 |

# LIST OF FIGURES (Continued)

# **FIGURE**

## PAGE

| 33 | FC-Accel with 128 PEs. PDK 45mm standard cells implementation                                                                                                                          | 85  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

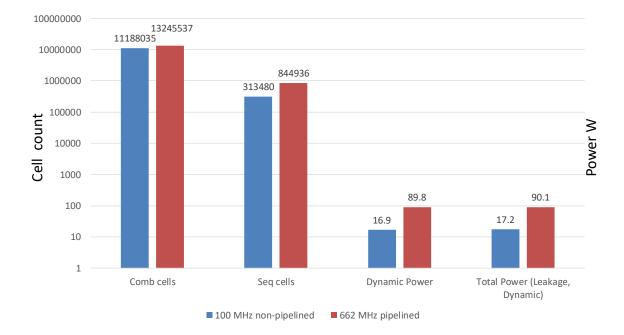

| 34 | Implementation data for pipelined 16x16 PE at 662 MHz. The y axis is log() base 10.                                                                                                    | 86  |

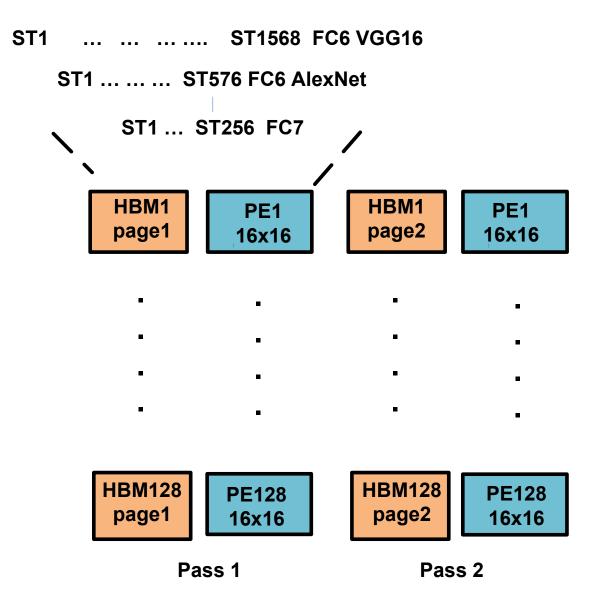

| 35 | Up-scaling the propsed micro-architecture for handling FC6 and FC7 layers. In each pass 128 HBMs and 128 16x16 PEs are reused. The input and output memories are connected as in Fig.3 | 91  |

| 36 | Estimated performance of FC6 and FC7 layer acceleration with FC-Accel 128x1 array of pipelined 16x16 PEs and two passes over the array.                                                | 92  |

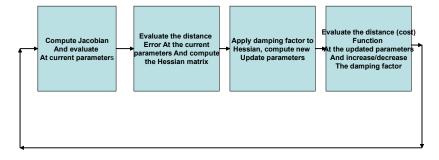

| 37 | NLS-LM processing pipeline for 3D AOA measurements. The processing iterations continue until parameters updates (3D coordinate updates) become smaller than a threshold value.         | 96  |

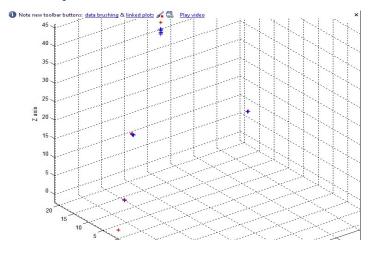

| 38 | Matlab simulation of NLS-LM processing pipeline and a possible systolic array realization.                                                                                             | 103 |

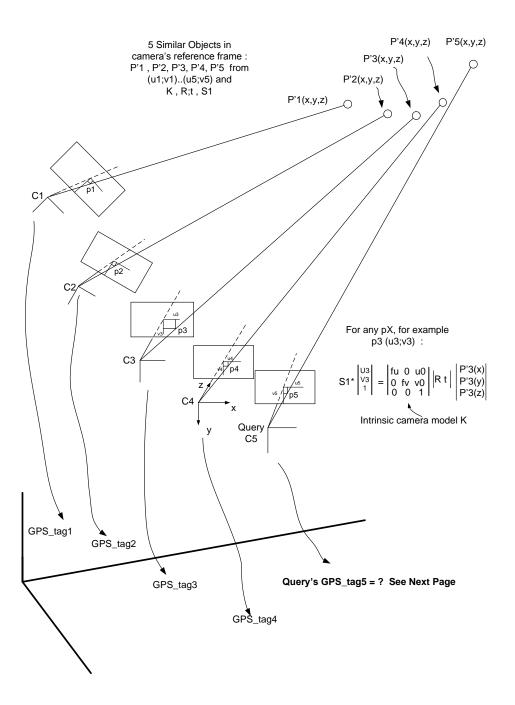

| 39 | RNN architecture extension for solving a constrained Quadratic Program, QP, as well as an LP.                                                                                          | 104 |

| 40 | SFM processing to generate P'1P'5 in local camera coorinate system                                                                                                                     | 105 |

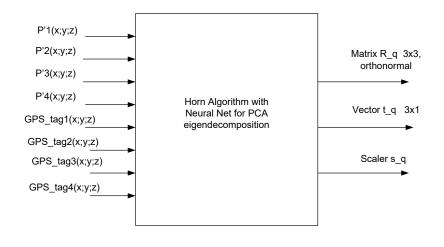

| 41 | Module for Horn acceleration, with neural network for PCA and eigenvalue decomposition.                                                                                                | 106 |

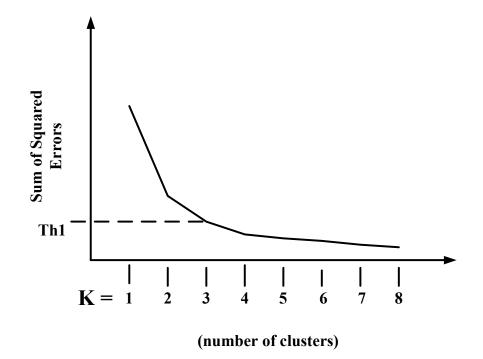

| 42 | The elbow method for optimal K selection                                                                                                                                               | 107 |

| 43 | Spotted word recognition for control of diadic manipulator robotic arm TR45.                                                                                                           | 108 |

# LIST OF ABBREVIATIONS

| ANOVA   | Analysis of Variations               |

|---------|--------------------------------------|

| SSL     | Spatial Self-Localization            |

| НММ     | Hidden Markov Model                  |

| SpkrRec | Speaker Recognition                  |

| FC-NN   | Fully Connected Neural Network layer |

| GMM     | Gaussian Mixture Model               |

| RNN     | Recurrent Neural Network             |

| RMSE    | Root-Mean-Square Error               |

| UIC     | University of Illinois at Chicago    |

## **SUMMARY**

Recent advances in CMOS VLSI technology have enabled the tremendous growth of devices at the edge of the cloud and in indoor environments: IoT indoor appliances, mobile indoor medical assistants, mobile indoor manufacturing platforms, indoor drone assistants, and others. As anticipated, this growth (in edge-device numbers and capabilities) is generating large communications and data processing work-loads for the servers in the cloud. One approach to help manage this trend is to make the edge-nodes more intelligent and able to process more data onboard (within the edge-node) before communicating with the servers. This thesis proposes hardware accelerator solutions to three types of onboard (within platform) processing: Spatial Self-Localization (SSL) which localizes the platform in space, Speaker Recognition (SpkrRec) which allows human voice control of the platform and authentication of the human speaker, and Fully-Connected layer evaluation in Neural Networks (FC-NN) for accelerated neural network processing withing the platform. Onboard processing is assumed to include a multi-core SoC (CPU/GPU), conventional SRAM and DRAM memory as well as high bandwidth memory, HBM or 3D-DRAM, and communication and sensing subsystems. The SSL, SpkRec, and FC-NN accelerators can be integrated with the SoC's peripheral bus structures such as AXI-Stream, AXI-Lite, AXI-HBM, JESD235A, JESD235B, GPMC, DMA, and similar high-speed processor interfaces.

## **CHAPTER 1**

## **INTRODUCTION**

This research has been motivated by three important problems in real-time integrated hardwaresoftware implementations of indoor mobile robotic platforms at the edge of the cloud:

#### 1.1 Spatial Self-Localization

Spatial self-localization (in 2D or 3D space) is performed within the device. Example applications include simultaneous localization and mapping (SLAM) and navigation for autonomous mobile robots. We focus on optical angle-of-arrival, AOA, localization based on fixed known position LEDs or infrared, Ir, beacons or anchors mounted in an indoor environment and photodetectors built in the mobile plat-form. These are lower cost localization systems when compared to 3D camera or image sensor based AOA detection, but can offer comparable performance in most indoor cases. Recent implementations include (Popoola and et al, 2019), (Arafa et al., 2015), and (Navarrro and et al, 2017).

#### 1.2 Speaker and or Command Recognition

Speaker and or command recognition is performed within the device to allow human control of the device and speaker identification. Example applications include a limited number of voice commands from a set of known speakers, which are used to control indoor drones as in (Fuhrman and et al, 2019) , (Sugadev and et al, 2016). Another application is spotted word (command) recognition for control of diadic manipulator robotic arm (Elemary, 2011).

#### 1.3 Fully Connected Layers for Neural-Network Processing

Fully connected layers processing, for embedded neural-networks, is performed within the device to achieve real-time inferencing with the DNN. Example applications include deep CNN processing such as AlexNet or VGG-16, where a typical fully-connected layer has 4096 input features and 1000 output neuron activations, and can increase up to 250088 input features and 4096 output neuron activations, as in (Krizhevsky and et al, 2017) and (Simonyan and et al, 2014). Another application is bounding-box object localization in an image using reinforcement learning for training and a Q-Network for inferencing with several fully-connected layers as implemented in (Caicedo and et al, 2015).

The main contribution for the spatial self-localization problem is a block Least-Squares formulation of the 3D or 2D Angle-of-Arrival (AOA) equations for increasing number of anchors. An incoming stream of 3D or 2D AOA sensor measurements is used to define the overdetermined system of equations. The AOA equations are then used to formulate a primal-dual linear program and solved via a novel Recurrent Neural Network (RNN) hardware accelerator which does not use matrix inversion. Key results for FPGA and CMOS ASIC implementations have been published in (Iliev and Trivedi, 2019) for the 3D case and in (Iliev and Trivedi, 2017) for the 2D case.

The main contribution for the speaker recognition problem is a novel online K-means cluster generator for the following Gaussian Mixture Model (GMM) evaluation (scoring). Online Euclidean distances and K-means centroids (for incoming MFCC frames) are computed with novel low-power pipelined datapaths. Key results for FPGA and CMOS ASIC implementations have been published in (Iliev et al., 2019). The main contribution for the fully connected (FC) layers problem is a novel online accelerator based on 8x8 processing elements (PEs) for matrix-vector multiplication, a column of blocks (tiles) decomposition of the weights matrix, and 128 multiply-accumulate (MAC) units integrated with 128 High Bandwidth Memory (HBM) units for storing the pre-trained weights. On chip routing such as 2D mesh routing with Network on Chip, NoC, is not required. Compression of the DNNs features or weights is not required either. The architecture can be scaled to 16x16 PEs for handling larger FC6 and FC7 layers in AlexNet and in VGG16. Key results for CMOS ASIC implementations of the FC8 layer accelerator have been published in the journal of IEEE Embedded Systems Letters.

#### 1.4 Thesis Organization

This thesis is organized into four parts and 15 chapters. Descriptions of each part and each chapter of the dissertation are as follows:

**Part I, Spatial Self-Localization:** This part contains an introduction to the 2D or 3D AOA spatial self-localization (SSL) research problem, a review of the existing works and a description of the key design features and parameters of the SSL-Accel accelerator for edge node devices.

**Chapter 2:** This chapter provides the reader with the motivation for the spatial self-localization problem and identifies the research questions that the work is focused on such as handling an increased number of anchors with low latency and keeping circuit power consumption withing limits. Our approach to these problems is explained and a list of related contributions is included in this chapter, as well.

- **Chapter 3:** In this chapter we review some background on AOA localization systems that will be referenced later in the thesis.

- **Chapter 4:** This chapter presents the key design features and parameters of the SSL accelerator, SSL-Accel, and FPGA and ASIC implementations. Datapath flow and controller (scheduler) diagrams and state machines are covered as well as the RNN operation with fixed-point data types for all layers.

- **Chapter 5:** Simulation results are presented, and FPGA and CMOS ASIC PDK 45 nm implementation details and performance are covered as well. A conclusion follows with complexity comparisons of the SSL-Accel RNN dual-LP approach to various matrix-inversion architectures for solving overdetermined systems as well as Kalman filter based and particle filter based localizers.

**Part II, Speaker Recognition:** This part contains a background on speaker recognition based on Gaussian Mixture Models (GMMs), and a description of key design features and parameters of the online k-Means clustering accelerator SpkrRec-Accel for edge node devices.

**Chapter 6:** This chapter provides an overview of speaker identification using GMM models of a set of enrolled speakers.

- **Chapter 7:** This chapter introduces the research problem of reducing the dimensionality of speech features for a collection of speakers so that overall identification latency and circuit power are reduced to meet implementation constraints.

- **Chapter 8:** This chapter presents the key design features and parameters of the SpkrRec-Accel accelerator. Datapath flow and controller (scheduler) timing diagrams and state machines are covered as well as novel distance computing and centroid update datapaths with fixed-point data processing.

- **Chapter 9:** Simulation results are presented, and FPGA and CMOS ASIC PDK 45nm implementation details and performance are covered in this chapter. A comparison with other approaches is also presented.

**Part III, Fully Connected Layers in Deep Neural Networks:** This part presents current solutions to the FC layers problem in deep CNNs and DNNs such as AlexNet and VGG-16. It then details a novel, higher performance, accelerator architecture FC-NN-Accel and its key design features and parameters for edge node devices.

- **Chapter 10:** This chapter provides an introduction on the impact of FC (or dense) layers to overall CNN and DNN performance. Current solutions for edge node devices, implemented as CMOS ASIC or FPGAs, are reviewed and possible areas of improvement are identified.

- **Chapter 11:** This chapter contains some background information on FC layers in DNNs, their relation to convolutional layers, and other FC specific features relative to their hardware

acceleration. Parallel matrix-vector multiplication algorithms are also reviewed including rowwise block decomposition, columnwise block decomposition, and checkerboard block decomposition of the FC layer's weights matrix.

- **Chapter 12:** In this chapter, a novel solution is proposed to address the areas for improvement. The FC-NN-Accel architecture is presented in detail with its key design parameters such as tile size for decomposition of the weigths matrix into tiles; array of High Bandwith Memory (HBM JESD235A) for driving an array of processing elements (PEs) in a maximally parallel organization using column of blocks (tiles) decomposition; PE design with novel matrixvector multiplier, accumulator, and ReLU and biasing circuits; streaming data-prefetching from the HBM array and streaming address-generation for the output memory. A CMOS ASIC PDK45 nm implementation is described as well.

- Chapter 13: This chapter presents an ASIC implementation of FC-Accel as well as simulated performance results for FC-NN-Accel with 128 HBM weights memories (1 MB eaech), a 4KB input features memory (FC layer only), and compares achieved results with other AlexNet and VGG-16 implementations with published FC layer performance results.

**Part IV, Conclusion:** This part contains open problems and possible extensions of the SSL, SprkRec, and FC-NN accelerators to address some of the problems. Example problems are robust location estimation in noisy environments with multi-modal methods such as AOA and image-based methods, joint speaker and command recognition accuracy, and power consumption and scalability in fully connected layer inference. Finally concluding remarks are presented.

**Chapter 14:** This chapter discusses a few possible extensions of our work and also reviews related open problems which can be addressed by these extensions.

Chapter 15: A concluding summary of the thesis is presented in this chapter.

# Part I Spatial Self-Localization

## **CHAPTER 2**

#### SSL INTRODUCTION

In this chapter I discuss a novel low power circuit to self-localize a mobile sensor node in threedimensional (3D) space using a passive optical receiver. Self-localization of sensors, where a sensor node computes its spatial location by itself, reduces transmission demand, and improves real-time conformity of mobile wireless sensor systems. Our approach forms an over-determined system of angles-of-arrival (AOAs) to mobile sensor received from an optical anchor grid. Optical AOA based localization algorithms have shown a lot of advantages for indoor localization, over RF RSSI power, optical RSSI power, ultrasound time-of-flight, and other method as shown in our recent survey on spatial localization (Iliev and Paprotny, 2015). The AOA system is solved with a linear program (LP) solver, which is implemented using a non-linear feedback recurrent neural network (RNN). To solve the primal and dual LP optimization problems in the AOA system, we show a single multi-functional data path that does not require matrix inversions; thereby, enables within-sensor low power computations to self-localize. Additionally, unlike other optical indoor positioning architectures, our approach does not require measurements of received signal strength (RSS) and, thereby, is insensitive to power and alignment imbalances in the anchor grid. We show proof-of-concept FPGA and ASIC simulations of our approach and validate its operation under noisy AOA data and for different numbers of anchors. An FPGA implementation in 180

nm CMOS achieves a peak  $\sim$ 0.12 mega localization operations per second per Watt (MOPS/W), while ASIC design in 45 nm CMOS shows a peak  $\sim$ 7.7 MOPS/W.

## **CHAPTER 3**

### SSL BACKGROUND AND NOTATION

Many emerging mobile wireless sensor networks such as mobile robotics, indoor positioning for pick-and-place robotics, and smartphone localization in visible light communication (VLC) systems rely on the indoor spatial localization of sensors. However, spatial-localization of sensors faces several challenges in indoor environments. Radio frequency (RF)-based localization suffers from multipath reflections, fading, and shadowing of the radio signals (Tang and Dodds, 2007). Similarly, localization based on received signal strength (RSS) from optical beacons suffers from power imbalances and fading (Harnilovic, 2004). Contrarily, indoor localization based on angle-of-arrival (AOA) measurements, such as using a passive corner-cube photoreceiver or an image sensor, has shown more promising performance by being insensitive to signal power (Bergen et al., 2018), (Arafa et al., 2015). Moreover, optical localization based on AOA also obviates synchronization between transmitter and receiver or between co-operating transmitters as needed in optical time-difference-of-arrival (Wang et al., 2013).

While optical localization based on AOA measurements is promising for indoor applications, a *self-localization*, where a sensor node can estimate its spatial position on its own, is also critical. Unlike traditional schemes, where a server collects data from all sensors to estimate and communicate their positions, self-localization can significantly suppress communication demand and

associated energy-overheads. Therefore, in this work, we focus on low power architectures to self-localize a sensor based on its AOA measurements.

Our approach uses a recurrent neural network (RNN) to perform all computations necessary for self-localization within the sensor node. Unlike localization methods such as Kalman filter (EKF) (Gasparri and Pascucci, 2010) and extended information filter (EIF) (Taparugssanagorn et al., 2013), our approach doesn't require matrix inversions. Meanwhile, implementation of matrix inversion methods (Yan et al., 2010), (Karkooti et al., 2005) can add significant latency to the prediction. We discuss a digital CMOS micro-architecture for the RNN using fixed-point arithmetic comprising time-multiplexed matrix-vector and vector-scalar multiplications along with other arithmetic operations. The proposed micro-architecture uses a core 3×3 matrix-vector multiplier unit to solve the 3D localization problem with measurements from M anchors, where M is in a multiple of two. Average localization error based on optical AOA measurements decreases with an increase of available anchors. While our preliminary conference paper in (Iliev and Trivedi, 2017) showed RNN-based self-localization in 2D, in this work, we expand the scheme for 3D self-localization. Unlike (Iliev and Trivedi, 2017), the proposed 3D micro-architecture is reconfigurable to a number of anchors. We also discuss novel datapaths based on distributed matrix-vector arithmetic with dynamic bit-plane selections. Sec. II discusses our RNN formulation of AOA-based 3D localization. Sec. III presents the proposed micro-architecture for 3D localization. Sec. IV presents simulation results for FPGA and ASIC implementations. Sec. V concludes. We use bold lowercase English and Greek letters for vectors and bold uppercase letters for matrices.

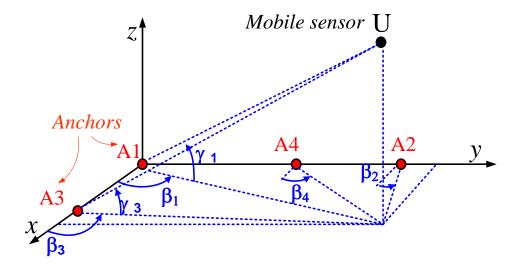

Figure 1: Sensor localization in 3D with 4 anchors and Angle-of-Arrival (AOA) measurements.

#### 3.1 RNN formulation of AOA-based 3D Localization

Fig. 1 shows a test-case where an optical receiver U is localized using an anchor grid  $A_1$ – $A_4$ . We derive a system of linear equations to localize U using an arbitrary number of anchors. The angle-of-arrival (AOA)-based localization has been analyzed in (Gavish and Weiss, 1992) in its most general form. The problem can be solved with a Maximum Likelihood (ML) algorithm (Vaghefi et al., 2010) when the exact positions of anchors are available and the measurement noise follows a Gaussian distribution. In this case, the ML problem yields to a nonlinear minimization as

$$\theta_{ML} = \arg\min_{\alpha} (\tilde{\alpha} - \alpha)^T \times C \times (\tilde{\alpha} - \alpha).$$

(3.1)

Here, the spatial coordinates of *U* are estimated by  $\theta_{ML}$  and  $\tilde{\alpha}$  is the AOA measurements vector from *M* anchors given as

$$\tilde{\alpha} = [\tilde{\alpha}_1 \tilde{\alpha}_2 \dots \tilde{\alpha}_M]^T = \tilde{\alpha}_0 + n, \qquad (3.2)$$

with  $\tilde{\alpha}_0$  as the true angle (in radians) and *n* is the measurement noise. *C* in Eq. 3.1 is the inverse covariance matrix of *n*.

Notice that each  $\alpha_i$  in Eq. 14.2 corresponds to two angle measurements (longitude and latitude) from an anchor  $A_i$ , as shown in Fig. 1; therefore,  $\alpha_i = (\beta_i, \gamma_i)$ . Here,  $\beta_i$  and  $\gamma_i$  depend on the location of  $A_i$ , i.e.,  $(x_i, y_i, z_i)$ , and the estimate for U, i.e.,  $(x_T, y_T, z_T)$ , as

$$\beta_i = \tan^{-1} \left( \frac{y_T - y_i}{x_T - x_i} \right) \& \gamma_i = \tan^{-1} \left( \sin \beta_i \times \frac{z_T - z_i}{y_T - y_i} \right).$$

(3.3)

For small measurement errors, (Vaghefi et al., 2010) shows that Eq. 3.1 can be reduced to the following Least Squares problem

$$D \times \begin{bmatrix} x_T & y_T & z_T \end{bmatrix}^T = b, \tag{3.4a}$$

$$D = \begin{bmatrix} \tan(\beta_{1}) & -1 & 0\\ \tan(\beta_{2}) & -1 & 0\\ 0 & \tan(\gamma_{1}) & -\sin(\beta_{1})\\ \vdots & \vdots & \vdots\\ \tan(\beta_{M-1}) & -1 & 0\\ \tan(\beta_{M}) & -1 & 0\\ 0 & \tan(\gamma_{M-1}) & -\sin(\beta_{M}) \end{bmatrix}, \qquad (3.4b)$$

$$b = \begin{bmatrix} x_{1} \times \tan(\beta_{1}) - y_{1}\\ x_{2} \times \tan(\beta_{2}) - y_{2}\\ y_{1} \times \tan(\beta_{2}) - y_{2}\\ y_{1} \times \tan(\beta_{1}) - z_{1} \times \sin(\beta_{1})\\ \vdots\\ x_{M-1} \times \tan(\beta_{M-1}) - y_{M-1}\\ x_{M} \times \tan(\beta_{M}) - y_{M}\\ y_{M-1} \times \tan(\gamma_{M-1}) - z_{M-1} \times \sin(\beta_{M-1}) \end{bmatrix}. \qquad (3.4c)$$

Therefore, with adequate anchors, Eq. 4 forms an overdetermined system where each pair of anchors adds three additional equations. We reformulate the system of equations as a set of primal-dual constrained linear programs shown below

**Primal problem:**

$$\min_{\theta} c^T \theta \quad \forall D \times \theta = b,$$

(3.5a)

**Dual problem:**

$$\max_{\phi} b^T \phi \quad \forall D^T \times \phi \le c.$$

(3.5b)

Here,  $\theta = [x_T \ y_T \ z_T]$  is the objective variable of the primal problem and corresponds to the unknown target location; and  $\phi$  is the corresponding variable of the dual problem. The cost function *c* can be selected arbitrarily since the main goal is to satisfy the constraints and the cost function simply rejects spurious solutions. For the optimizations, the anchor coordinates are translated to the first quadrant.

Constrained linear programs such as the one in Eq. 3.5 can be efficiently solved using a RNN as discussed in (Oskoei and Amiri, 2006). The corresponding neuron equations are shown below

$$\frac{d}{dt} \begin{bmatrix} \theta \\ \phi \end{bmatrix} = \begin{bmatrix} \theta - (\theta + D^T \phi - c)^+ \\ D \times (\theta + D^T \phi - c)^+ - b \end{bmatrix}$$

(3.6)

The respective discrete time RNN equations for solving the primal-dual constrained programs are shown below

$$\begin{bmatrix} \theta(n+1) \\ \phi(n+1) \end{bmatrix} = \begin{bmatrix} \theta(n) + dt \times (r(n) - \theta(n)) \\ \phi(n) + dt \times (b - D \times r(n)) \end{bmatrix}$$

(3.7a)

$$r(n) = \max[(\theta(n) + D^{T}\phi(n) - c), 0]$$

(3.7b)

Here, r(n) is the output activation of recurrent neurons. In Eq. 7, we use Euler's forward method for numerical integration of the continuous time variant with dt as the time step for controlling the rate of convergence.

## 3.1.1 Complexity of Primal-Dual Linear Program Solution

The number of iterations of primal-dual algorithms for solving constrained linear programs is given by

$$O(\sqrt{N} * \log \frac{N}{\varepsilon}) \tag{3.8}$$

were N is the dimension of  $\theta$  and  $\varepsilon$  is the desired accuracy with  $\varepsilon > 0$  (epsilon away solution), (Cai and et al, 2014).

In the proposed SSL-Accel architecture the number of operations, per iteration, is

$$O(2*N^2) \tag{3.9}$$

multiplications with N the dimension of  $\theta$  and an additional O(N) number of add, sub, and compare-vs-zero operations. Note that since batch Least Squares is used (with a batch size of N) generating a corresponding primal-dual linear program for each batch, an increase in the number of nodes does not affect the above complexity.

## **CHAPTER 4**

### SSL DESIGN FEATURES AND PARAMETERS

Parts of this chapter have been presented in (Iliev and Trivedi, 2017) and (Iliev and Trivedi, 2019). Copyright © 2017-2019, IEEE.

This chapter presents the key design features and parameters of the SSL accelerator, SSL-Accel. Datapath flow and controller (scheduler) timing diagrams and state machines are covered as well as the RNN operation with fixed-point data types for all layers. Simulation results are presented, and FPGA and CMOS ASIC PDK 45 nm implementation details and performance are covered as well.

#### 4.1 Low Power Digital Microarchitecture for RNN-based Localization

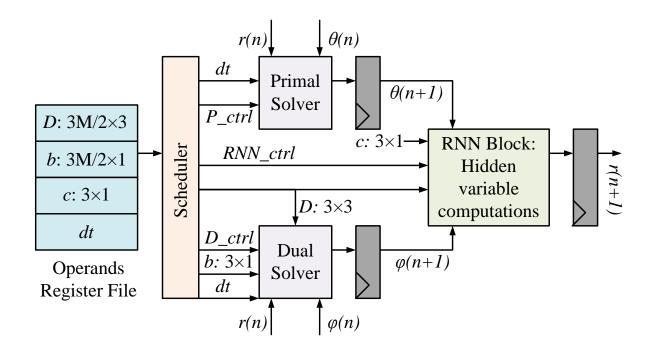

We have implemented a programmable digital fixed-point arithmetic co-processor, as shown in Fig. 2 for RNN-based localization using Eq. 3.7. The co-processor works with the main processor and AOA sensors. Measured AOA values for  $[\tilde{\alpha}_1 \cdots \tilde{\alpha}_M]$  and the anchor's known coordinates are used by the main processor to compute the matrix D and column vector b using Eq. 3.4. The cost vector c in Eq. 3.7 is set as the first three elements in the column vector of b to avoid spurious outputs. The main processor writes D and b to the co-processor's internal registers. The RNN block is scalable to the number of anchors M. The value of M is a multiple of two in the current implementation. An overdetermined D [dimension:  $(3M/2) \times 3$ ] is handled by time-sharing  $3 \times 3$  submatrices of D and  $3 \times 1$  subvectors of b. The scheduler feeds each submatrix of D and each  $3 \times 1$  subvector of b to the downstream solvers.

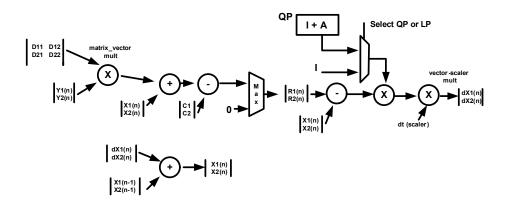

Figure 2: RNN-based co-processor for 3D localization with *M* anchors.  $\theta(n+1)$  represents the predicted target location at step n+1.

In the co-processor in Fig. 2, the primal-dual data paths and RNN block include a matrix vector multiplier, a vector-scalar multiplier, and five add/subtract blocks. A single vector comparator Max(x,0) implements the neuron's activation function. The primal variables at time step n are  $\theta(n) = [x_T(n) y_T(n) z_T(n)]$ ; the dual variables are  $\phi(n) = [(\phi_1(n) \cdots \phi_{3 \times M/2}(n))]$ ; and D, c, and b are the constants for a given set bearing (angle) measurements. Time step dt (programmed by the main processor) controls the rate of convergence and the number of iterations. Fixed point two's complement *Q*17.10 representation is used for all arithmetic operations.

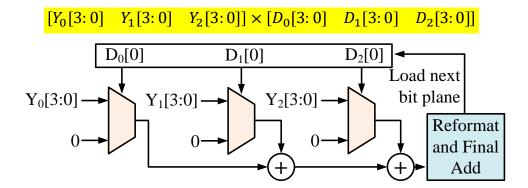

Figure 3: Distributed arithmetics for vector-vector multiplication.

The dual data path shown in Fig. 2 generates dual variables  $(\phi_1(n), ..., \phi_{3 \times M/2}(n))$  which are used in the RNN block. The matrix-vector and vector-scalar multipliers are reused; this data path also uses Q17.10 fixed-point representation for all its arithmetic operations. A dedicated fifteen state FSM controller schedules all operations in both data paths, samples the input registers (*D* submatrices, *b* and *c* sub-vectors, *M*, and *dt*), and drives all updates to the output registers [ $x_T(n)$  $y_T(n) z_T(n)$ ] and [ $(\phi_1(n) \cdots \phi_{3 \times M/2}(n))$ ]. The following subsections describe the main new processing blocks contributed in the proposed micro-architecture.

### 4.1.1 Matrix-vector product with sub-matrix scheduling

The matrix-vector product operation in the above equations is implemented by reusing a core  $3 \times 3$  matrices and  $3 \times 1$  vector multiply unit implemented using distributed arithmetic for lower power. Using 45 nm CMOS predictive development kit, the implementation of the units has been optimized for 1 V supply voltage (VDD) using 8388 combinatorial cells. An operands register

file holds  $3\times3$  submatrices of *D* and corresponding  $3\times1$  subvectors of *b*. A scheduler selects the submatrices and respective subvectors in a time slot for the single-cycle matrix-vector product operation. Vectors are multiplied using distributed arithmetic operations on each bit-wise element of the data values. This is shown in Fig. 3 where for simpler illustration four-bit signed arithmetic is used. Note that distributed bitplane arithmetic in the figure obviates power hungry multipliers and uses cyclic iterations over the bitplane to compute the vector product. In Fig. 3, each  $3\times1$  subvector of *Y* and  $3\times3$  submatrix of *D* is a 4-bit two's complement fixed point fraction in the Q<4,0,t> format. The final  $D^T \times Y$  product is read out from the products register file in N/3 time slots. A similar datapath is used for the matrix-vector product of the  $N\times3$  *D* matrix and the  $3\times1$  r(k) vector in Eq. 3.7.

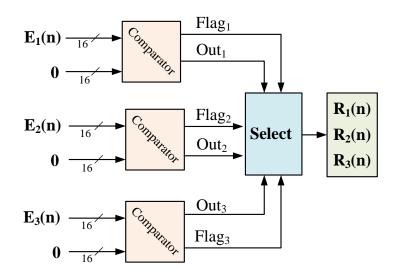

# 4.1.2 Low Power Comparator Unit

The max() operator needed in the computation of vector r(n) in Eq. 3.7 is optimized for low power since it's a fully combinatorial circuit. Each 16-bit two's complement element of the  $3 \times 1 r(n)$ vector is generated as shown in Fig. 4. The  $E_1(n)$ ,  $E_2(n)$ , and  $E_3(n)$  busses are driven by three bit-parallel subtractors for the difference terms in r(n). The ASIC implementation of the units is optimized to 255 combinatorial cells, with 7.7  $\mu$ W of leakage power and 6.8  $\mu$ W of dynamic power at 200k kHz processing rate.

Figure 4: Comparator unit for three 16-bit signed two's complements.

# **CHAPTER 5**

# SSL SIMULATION AND IMPLEMENTATION RESULTS

*Parts of this chapter have been presented in (Iliev and Trivedi, 2017) and (Iliev and Trivedi, 2019). Copyright* © 2017-2019, IEEE.

# 5.1 Simulation Results

# 5.1.1 Functional Simulations

The proposed RNN co-processor for low power self-localization is evaluated using functional simulations and post-implementation fixed-point Verilog simulations using a benchmark setup for 3D optical AOA localizations in (Bergen et al., 2018). Using the setup, we observe correct convergence to spatial coordinates in all cases with varying numbers of anchors. An example of four anchors is shown in Fig. 5. Verilog simulations follow the trajectory of functional simulations. The coordinate estimates converge to stable values in about 600-time steps. The estimation error is  $\sim$ 3.18 cm. Our average localization error also compares favorably with the 3–5 cm average localization error published in (Bergen et al., 2018), (Arafa et al., 2015) for four anchors in a one m<sup>3</sup> working area. Note that the proposed architecture uses only six measured angles instead of all eight possible angles and therefore is also a more compact solution for an embedded implementation.

Histograms of the estimated 3D coordinates under varying Gaussian noise are shown in Fig. 6. The average Euclidean distance for the error is  $\sim 3.1$  cm as computed over all simulated test cases.

Figure 5: The comparison of functional simulations against fixed-point Verilog. Verilog simulations are done in Q(10,17) format.

The combined error in all three coordinate estimates increases with each increase in measurement noise power, as shown in Fig. 7(a). Fig. 7(b) shows the localization error against increasing number of anchors. In one  $m^3$  working area all anchors have the same *z* coordinate. The target is above the *z* plane of all anchors. The Gaussian noise for measured AOAs is simulated with unit degree variance. In Fig. 7(b), error decreases as the number of anchors increases. The figure also shows that increasing the number of anchors from two to four decreases the localization error by 42%. In (Bergen et al., 2018), authors reported a similar decrease in the error by 30% when the number of anchors is increased from three to six for AOA based positioning. Fig. 7(c) shows

Figure 6: Histogram of the estimated coordinates. In each subplot, two thousand samples from the fixed point Verilog simulations are used.

localization error at various anchor configurations where symmetric square shows the least error similar to (Bergen et al., 2018).

#### 5.1.2 FPGA Implementation Results

We also implemented the coprocessor using FPGA with the Microsemi (Actel) ProASIC3E A3PE3000 device (180 nm process) and Libero SoC v11.8 toolset. ModelSim Verilog simulations were done by setting the internal registers with pre-computed values of D, b, c, dt, and setting a max iteration limit. A statistical power analysis tool in Libero SoC (SmartPower) was also used to generate the worst possible switching activity on all inputs and derive the resulting total static and dynamic power dissipation. The design's clock gating and resource scheduling for the primal

Figure 7: (a) Standard deviation of localization error at increasing standard deviation of AOA noise. (b) Average localization error for thousand runs computed as Euclidean distance from the ground truth at varying number of anchors. (c) Localization error at various anchor configurations considering four anchors. Results in (a) and (b) are for configuration C2.

and dual distributed arithmetic datapaths are utilized to minimize power dissipation of the design. Fig. 8(a) shows the power consumption and the number of mega operations per second per Watt (MOPS/W) at the varying clock frequency. At the maximum characterization frequency, 24 MHz,

Figure 8: Power characterization of (a) FPGA and (b) ASIC implementation. FPGA is implemented in 180 nm technology. ASIC is implemented using 45 nm predictive technology models.

the design consumes 236 mW power and does  $\sim$ 167 thousand localization operations per second per Watt. Notably, the required localization performance of typical sensor applications is much lower (typically hundreds of operations per second). At a moderate clock speed of 200 KHz, the design consumes 38 mW power and performs eight thousand operations per second per Watt.

# 5.1.3 PDK45 ASIC Implementation

We have also implemented the proposed coprocessor in 45 nm CMOS predictive technology models using Cadence RTL Compiler (RC) and Encounter EDI. Clock gating was used in the

RC tool. Fig. 8(b) summarizes the achieved worst-case power and performance in terms of MOPS/W at the varying clock frequency. The gate-level netlist from RTL compiler was analyzed for the worst case power using RTL Compiler's statistical power analysis tool. The dynamic power dissipation can be reduced even further if static RAM cells are used instead of register files for *D* and the other vectors in the datapaths. Compared to FPGA, ASIC design achieves higher energy efficiency due to scaled technology and customized computing cells. At the maximum characterized frequency, 167 MHz, the design consumes 65 mW power. The design achieves a peak  $\sim$  7.7 MOPS/W at 5 MHz clock speed.

# 5.2 Conclusion

This work has proposed a novel micro-architecture for 3D indoor localization which allows a flexible number of anchors to achieve the smallest possible localization error. We enable low power computations by avoiding matrix inversions using an RNN to map localization computations. We also use a distributed arithmetic matrix-vector multiplier without look-up tables with dynamic bit-plane selections of each operand. Our FPGA implementation in 180 nm technology achieves a peak ~0.12 MOPS/W, while ASIC implementation in 45 nm technology achieves a peak ~7.7 MOPS/W.

There are several matrix inversion algorithms used in embedded hardware for solving the pseudoinverse problem of overdetermined least-squares (LS) systems [1-3] below. Specifically, we refer to the methods developed for smaller size non-sparse matrices like in our case, unlike those designed for larger sparse matrices, often used in image processing. We find two competitive implementation to our case, namely: (i) fixed-point Cholesky Decomposition [1], and (ii) QRD- RLS [2]. We qualitatively compare our approach against Cholesky Decomposition-based matrix inversion. Prior work [1] has discussed fixed-point Cholesky Decomposition for matrix inversion. In our CMOS 45 nm implementation, RNN-based solver operates at clock frequency of 167 MHz and requires 600 cycles to converge. Therefore, total computing time for localization is 3.6 s. Our present solution is for 3D localization using four anchors which is equivalent to 63 matrix inversion (see Eq. (4a) above). Comparatively, in [1] at Table I, a total of 748 clock cycles are needed for solving 4 x 4 matrix inversion alone when using fixed-point Cholesky decomposition method. Therefore, at the same clock frequency, our implementation will incur lower localization latency. Note that our implementation also handles a larger matrix size 6 3 than the 4 4 in [1]. Our method achieves such computational efficiency by only using matrix-vector multiplication, vector addition/subtraction, and vector comparison (element-by-element greater-than-zero comparison). Meanwhile, Cholesky decomposition requires matrix-vector multiplication, vector scaling (element-by-element division by scalar), scalar square root, matrix-matrix multiplication, and matrix-matrix subtraction. Similarly, in [2], authors have discussed FPGA implementation of QRD-RLS method. In [2], to invert a 4 4 matrix, generating the upper triangular matrix requires 777 cycles and back substitution requires 156 cycles. Therefore, even as compared to QRD-RLS, our method is less computationally expensive.

[1] Yan, Mingjian, Brighton Feng, and Tommy Song. "On matrix inversion for LTE MIMO applications using texas instruments floating point DSP," IEEE 10th INTERNATIONAL CON-FERENCE ON SIGNAL PROCESSING PROCEEDINGS. IEEE, 2010. [2] Karkooti, Marjan, Joseph R. Cavallaro, and Chris Dick. "FPGA implementation of matrix inversion using QRD- RLS algorithm," Asilomar Conference on Signals, Systems, and Computers. 2005. [3] Yang, Depeng, et al. "An FPGA implementation for solving least square problem," 2009 17th IEEE Symposium on Field Programmable Custom Computing Machines. IEEE, 2009. We now present O () complexity analysis for our RNN – LP architecture in the following., For a N x N matrix D and Linear system D \* x = b where x is the 3 x 1 vector of coordinates.

Our RNN-LP approach needs O ( $2*N^2$ ) multiplication operations and O (N) add, sub, comparevs-zero operations. For N = 3, we then have O ( $2*(3)^2$ ) + O (3) = 18 + 3 = 21 total operations ( fixed-point mult, add,sub,compare). N=3 and a 3 x 3 D matrix is the core matrix in the hardware architecture. In summary, our RNN – LP approach takes 21 total operations for a N = 3 matrix and resulting 3 x 3 linear system.

# 5.2.1 Comparison to Cholesky decomposition with forward/backward substitution

To solve D \* x = b (N x N system), first decompose D to D = L \* L then forward/backward substitution Cholesky takes O ( $(N^3) / 3$ ) operations to decompose the matrix into L \* L format After L is found, forward substitution takes O ( $N^2$ ) operations. Backward substitution also takes O ( $N^2$ ) operations. For N = 3, this is O ( $(3^3)/3$ ) + O (9) + O (9) = 9 + 9 + 9 = 27 total operations, greater than our total of 21 operations.

#### 5.2.2 Comparison to QR (QRD) Decomposition using Householder transformation

To solve D \* x = b, we decompose D to D = Q \* R This takes O (N<sup>3</sup>) total operations, using the Householder transformation. We don't consider a Givens rotation (transformation) since it typically requires a systolic array architecture, to avoid square-root and division operations. Our RNN-LP architecture is not based on a systolic array (but can be).

For N = 3, this is O ( $3^3$ ) = 27 total operations, greater than our total of 21 operations.

#### 5.2.3 Comparison wih Adjoint Matrix method for matrix inversion to solving Linear System

We quote complexity analysis results from: "An Approach to Design a Matrix Inversion Hardware Module using FPGA" G. A. Kumar et al. 2014 IEEE ICCICCT conference. This Adjoint-Matrix inversion method needs  $2*N^2 + N$  multiplications,  $N^2$  divisions, and  $N^2 + N + 1$  adds/subs (arithmetic operations). For N = 3, solving a 3 x 3 linear system via the Adjoint-Matrix method takes 21 mults + 9 divisions + 13 arith ops = 43 ops in total. Again this is larger than our 21 operations.

# 5.2.4 Comparison with Cayley – Hamilton Method for NxN matrix inversion

The above reference also quotes the Cayley-Hamilton method's complexity for the N=3 case: For N=3, Cayley-Hamilton needs 45 mults + 9 divisions + 20 arith ops = 74 ops in total; larger than our 21 operations.

In the following we also compare our RNN LP architecture to several within-sensor localizer/tracker implementations of EKF (Extended Kalman Filter), EIF (Extended Information Filter), and SPKS (Sigma-point, or unscented, Kalman Smoother), all based on CPU and/or GPU processors with some hardware acceleration for scalar mathematical operations. We'll cover a particle filter ( within-sensor ) implementation after this section on Kalman-based methods. The main motivation

for our RNN dual linear-program solver is that it avoids completely any matrix inversions, scalar divisions, scalar square-root operations, matrix-matrix multiplications, Jacobian matrix computations, and random variable generation (sampling from PDFs). We therefore have a much lower hardware complexity for solving the localization problem in 3D then Kalman-based of particle-filter based methods. We summarize the main differences in computational complexity below:

# 5.2.5 Comparison with EKF

The work by A. Taparugssanagorn st al. IEEE Computer Society 2013 "A Hexagonal Coverage LED-ID Indoor Positioning Based on TDOA with Extended Kalman Filter "builds an EKF inside the sensor node, and in addition to one matrix-inversion and 6 matrix-matrix multiplications, requires two types Jacobian matrix computations: 1 - Ak-1 is the Jacobian matrix of the partial derivaties of f (target motion law) with respect to R (error covariance of the state ) 2 - Lk is the Jacobian matrix of the observation function 1 around the priori state estimate. It is clear that the complexity of this EKF method for localization exceeds our RNN LP method by a considerable amount.

# 5.2.6 Comparison with EIF

A recent EIF work by A. Gasparri et al., IEEE TRANSACTIONS ON MOBILE COMPUT-ING, VOL. 9, NO. 10, OCTOBER 2010 "An iterlaced Extended Information Filter for Self-Localization in Sensor Networks", implements an Extended (Kalman) Information Filter inside a sensor node: as shown in their Tables 8, 9 and 10, this requires multiple matrix inversions, matrixmatrix multiplications, and matrix-matrix additions/subtractions. In contrast, our method uses only matrix-vector multiplication, vector addition/subtraction, and vector comparison (elementby-element greater-than-zero comparison). This is a total of 3 types of operations. Computing Cholesky decomposition, for matrix inverse, requires matrix-vector multiplication, vector scaling (element-by-element division by scalar), scalar square root, and matrix-matrix multiplication and matrix-matrix subtraction. This is total of 5 types of operations. This further illustrates the lower complexity of our RNN LP method which does not use matrix inversion.

#### 5.2.7 Comparison with SPKS

The work by A. Paul et al. IEEE JOURNAL OF SELECTED TOPICS IN SIGNAL PROCESS-ING, VOL. 3, NO. 5, OCTOBER 2009 "RSSI-Based Indoor Localization and Tracking Using Sigma-Point Kalman Smoothers "The SPKS, a type of unscented Kalman filter, is implemented as forward and backward filters, followed by a smoothing step in the sensor node; the algorithm's steps are listed on page 867 - 869 of the reference and include: 6 matrix inversions, 3 x N square-root operations for sigma-point calculation, when N is the number of iterations, and 11 matrix-matrix multiplications. The complexity of this SPKS method again exceeds our RNN LP method by a considerable amount.

### 5.2.8 Comparison with Particle filter

The work by M. Peasegood, Proceedings of the IEEE International Conference on Mechatronics Automation Niagara Falls, Canada • July 2005 " Localization of Multiple Robots with Simple Sensors ", builds a particle filter localizer in a node (robot) with 800 particles to represent the state (coordinate) in each direction. The main 3 steps, done at each iteration are: 1 - sampling: basically 800 random variables have to be generated in hardware, or selected from a previous set of 800 (previous iteration). This requires a hardware random number generator, for a uniform or other distribution 2 - state update: the state of each particle (800 total) is updated to reflect the motion of the robots since the last iteration of the algorithm: this is vector-scalar multiplications, and vector-vector additions/subtractions 3 - Weighting: For each particle (800 total), a weighting is applied representing the degree of belief in the the position estimate of the particle. The weighting factor is computed using a scalar divider, and a scalar square-root module.

In conclusion, even though the PF method does not require matrix-inversion and Jacobian matrices, the large number of particles (needed for good approximation of the coordinates posterior distribution) makes the PF complexity quite high. Our RNN LP method has a lower complexity since at each iteration it does not have to generate and process large numbers (800 or more) of random variables for each x, y, z dimension.

# Part II Speaker Recognition

# **CHAPTER 6**

# SPEAKER RECOGNITION INTRODUCTION